JP2010097114A - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP2010097114A JP2010097114A JP2008269671A JP2008269671A JP2010097114A JP 2010097114 A JP2010097114 A JP 2010097114A JP 2008269671 A JP2008269671 A JP 2008269671A JP 2008269671 A JP2008269671 A JP 2008269671A JP 2010097114 A JP2010097114 A JP 2010097114A

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- display area

- crystal display

- display device

- signal line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Liquid Crystal (AREA)

Abstract

素子が形成された液晶表示装置を提供すること。

【解決手段】本発明の液晶表示装置10のアレイ基板は、表示領域DAの周囲の非表示領

域NDに形成された走査線12又は信号線16に屈曲部が形成され、この屈曲部に沿って

複数のスイッチング素子としての保護TFT30が形成されており、これらの複数の保護

TFT30は互いに並列に接続されて保護TFT30のドレイン電極Dはコモン電位に接

続されている。

【選択図】図2

Description

の静電気保護用のスイッチング素子が形成された液晶表示装置に関する。

素子として薄膜トランジスタTFT(Thin Film Transistor)を用いたアクティブマトリ

クス型の液晶表示装置は、携帯電話機、携帯端末から大型テレビに至るまで幅広く利用さ

れている。しかしながら、液晶表示装置は、製造工程中や使用中に、表示領域内に静電気

が浸入すると、液晶表示装置としてでき上がった段階で表示欠陥が生じる。特に中小型機

種においては高精細化が進むにつれて今まで以上に静電気不良が発生しやすくなっている

。静電気は、製造工程においても、パネルを搬送する際にも、他のものと接触するだけで

発生してしまう。また、配向膜のラビング時には摩擦により最も静電気が発生しやすい。

したがって、液晶表示装置の製造技術分野では、静電気による表示欠陥が生じないように

することが要求されている。

領域の周辺部にダミー画素を形成し、このダミー画素内に静電気保護用の複数個の微小な

ダミー画素電極とスイッチング素子を形成した液晶表示装置の発明が開示されている。こ

こで、下記特許文献1に開示されている液晶表示装置のダミー画素部分の構成を図8〜図

10を用いて説明する。

る。図9は図8のIX部分の拡大平面図である。図10は図9のX−X線の断面図である。

にゲート絶縁膜を挟んでマトリクス状に設けられた複数の走査線及び信号線が設けられて

いる。なお、図8には走査線としては走査線Xn−2、Xn−1、Xn、Xn+1、Xn

+2の部分のみ、信号線としてはY1、Y2・・・Ymの部分のみが示されている。この

うち、複数の走査線X1、X2・・・Xn及び信号線Y1、Y2・・・Ymで囲まれた領

域が表示領域であり、複数の走査線Xn、Xn+1、Xn+2及び信号線Y1、Y2・・

・Ymで囲まれた領域が非表示領域となっている。

素電極52及び反射板65が設けられている。また、TFT54においては、そのソース

電極Sは信号線Y1、Y2・・・Ymに接続され、ゲート電極Gは走査線X1、X2・・

・Xnに接続され、さらに、ドレイン電極Dはコンタクトホール(図示せず)を介して画

素電極52及び反射板65に電気的に接続されている。また、ドレイン電極Dの下部には

補助容量電極53が設けられている。このような構成の液晶表示装置50の動作原理は、

既に周知のものであるので、その詳細な説明は省略する。

信号線Y1、Y2・・・Ymで囲まれた非表示領域が形成され、この非表示領域には、T

FT66及び表示に寄与しないダミー画素電極67を有するダミー画素がそれぞれの信号

線Y1、Y2・・・Ym毎に複数個設けられている。このダミー画素のTFT66のソー

ス電極Sは、各信号線Y1、Y2・・・Ym毎に並列に接続され、ゲート電極Gは各走査

線Xn+1、Xn+2毎に並列に接続され、更にドレイン電極Dは、図10に示すように

、コンタクトホール68を介して層間膜69上に設けられたダミー画素電極67に接続さ

れている。そして、このダミー画素のTFT66は、表示に寄与する画素電極52に接続

されているTFT64のチャネル幅及びチャネル長よりも小さくなっており、それによっ

て表示に寄与する画素電極52に接続されているTFT54よりも優先的に静電破壊され

るようになっている。

2及び反射板65の面積を合わせたものよりも小さくされている。なお、図8及び図9に

おいては、ダミー画素電極67のそれぞれの面積を表示領域における1画素分の表示に寄

与する画素電極52及び反射板65の面積の1/10とし、走査線XnとXn+1の間及

びXn+1及びXn+2の間にそれぞれ10個づつ、計20個設けたものが示されている

。

入すると、信号線用入力端子62に最も近いダミー画素領域のTFT661が静電破壊を

起こして静電気を放電する。その後、再度信号線用入力端子62から静電気が浸入すると

、最初に静電破壊を起こしたダミー画素領域のTFT661の隣りのTFT662が静電

破壊することにより静電気を放電する。そのため、この液晶表示装置50の製造工程時に

おいては、表示領域の薄膜トランジスタ54が破壊されるような静電気浸入は20回まで

許容できることになるから、実質的に表示欠陥が生じることがない半透過型液晶表示装置

50が得られるというものである。

ー画素は、平面視で表示領域の上下側の非表示領域に形成されているものである。そのた

め、平面視で表示領域の上下側の非表示領域では、1画素分の領域内に複数個のダミー画

素が形成されているので、信号線側からの複数回の静電気進入に対処することができる。

しかしながら、平面視で表示領域の左右側の非表示領域においては、1画素分の領域内に

複数個のダミー画素を形成し難いので、走査線側からの複数回の静電気進入に対処できる

ようにするためには、平面視で表示領域の左右の両側において外側に向かって複数のダミ

ー画素を形成する必要がある。そのため、平面視で表示領域の左右側の非表示領域の幅を

狭くすることは困難となる。加えて、上記特許文献1に開示されている液晶表示装置50

に示されているダミー画素は、TFT66とダミー画素電極67とを備えているために構

成が複雑となっている。

本発明は、全ての非表示領域においても1画素分の領域内に簡単な構成の静電保護素子を

複数個形成することができ、しかも、非表示領域の幅を増加させることなく、多数回の静

電気浸入に対処できる液晶表示装置を提供することを目的とする。

第1基板及び第2基板を有し、前記第1基板の液晶層側には、マトリクス状に配置された

複数の走査線及び信号線と、表示領域の前記各走査線及び信号線の交差部近傍に配置され

たスイッチング素子と、前記表示領域の前記各走査線及び信号線で囲まれた画素領域毎に

それぞれ配置されているとともに前記スイッチング素子に電気的に接続された画素電極と

、前記表示領域の周囲に非表示領域が形成された液晶表示装置において、前記非表示領域

には、前記走査線又は信号線に屈曲部が形成され、前記屈曲部に沿って複数のスイッチン

グ素子が形成され、前記複数のスイッチング素子は互いに並列に接続されて前記スイッチ

ング素子の電極の一つはコモン電位に接続されていることを特徴とする。

チング素子が複数個形成されている。すなわち、本発明の液晶表示装置は、平面視で表示

領域の列方向の両端側に位置する非表示領域にも、平面視で表示領域の行方向の両端側に

位置する非表示領域にも複数のスイッチング素子が形成され、前記複数のスイッチング素

子は互いに並列に接続され、前記スイッチング素子の電極の一つはコモン電位に接続され

ている。なお、非表示領域にダミー画素電極を形成してもよく、このダミー画素電極を、

絶縁層に形成されたコンタクトホールを介してスイッチング素子の電極と接続し、スイッ

チング素子の電極をコモン電位に接続するために利用してもよい。

るので、非表示領域内に位置している走査線ないし信号線の長さは長くなっている。その

ため、スイッチング素子の占める面積は1画素分の面積に比すると小さいから、非表示領

域内に多くのスイッチング素子を形成することができる。

走査線ないし信号線に沿って並んで形成されていることになる。しかも、複数個のスイッ

チング素子の電極の一つはコモン電位に接続されているから、走査線ないし信号線に静電

気が進入した場合、静電気の進入箇所に近いスイッチング素子から順に静電破壊され、こ

の静電気はコモン電位に流れて放電されるので、液晶表示装置の表示領域を有効に保護す

ることができる。しかも、静電気の進入は、複数個のスイッチング素子の全てが静電破壊

されるまで許容されるので、スイッチング素子の数を多くすることにより実質的に表示欠

陥が生じることがない液晶表示装置が得られる。

ド、ECB(Electrically Controlled Birefringence)モード等の縦電界方式の液晶表

示装置だけでなく、IPS(In-Plane Switching)モードや、FFS(Fringe Field Swi

tching)モード等の横電界方式の液晶表示装置に対しても適用可能である。また、本願発

明で使用できるスイッチング素子としては、薄膜トランジスタ(TFT:Thin Film Tran

sistor)、薄膜ダイオード(Thin Film Diode)、MIM(Metal Insulator Metal)素子

等を使用し得る。

前記画素領域に形成されたスイッチング素子と略同一の大きさであることが好ましい。

略同一の大きさであれば、特に非表示領域のスイッチング素子形成用のマスク等を起こす

必要がなくなり、しかも、液晶表示装置のスイッチング素子の形成時に同時に形成できる

。そのため、本発明の液晶表示装置は、非表示領域に複数個のスイッチング素子を備えな

がらも、簡単に製造できるようになる。なお、本発明における「略同一の大きさ」とは、

必ずしも同一の大きさでなくてもよいが、同一の大きさであることが好ましいという意味

で用いられている。

形成され、前記信号線は前記走査線の屈曲部の外周囲に沿って延びる分岐信号線が形成さ

れていることが好ましい。

非表示領域の行方向の幅に拘わらず、非表示領域内に容易に複数個のスイッチング素子を

形成することができる。そのため、本発明の液晶表示装置によれば、特に平面視で表示領

域の左右側の非表示領域の幅を広くしなくても複数個のスイッチング素子を走査線に沿っ

て形成できるので、平面視で表示領域の左右側の非表示領域の幅が狭くても液晶表示装置

の表示領域を有効に保護することができるようになる。走査線の屈曲形態としては、通常

は表示領域の画素の形状が走査線側が短辺の矩形状に形成されているため、平面視で表示

領域の左右側の非表示領域内で凸状ないし凹状に屈曲していることが好ましい。表示領域

の画素の形状が横長の矩形状であれば、走査線は平面視で表示領域の左右側の非表示領内

で「コ」字状にジグザグに屈曲していることが好ましい。何れの場合においても、走査線

を屈曲させる場合、信号線は走査線の屈曲部の外周囲に沿って延びる分岐信号線を形成す

ればよい。

形成され、前記走査線は前記信号線の屈曲部に交差するように延びる分岐走査線が形成さ

れていることが好ましい。

従来例のように平面視で表示領域の上下側の非表示領域の走査線間距離を狭くしなくても

、複数個のスイッチング素子を信号線に沿って形成できるようになる。そのため、本発明

の液晶表示装置によれば、特に平面視で表示領域の上下側の非表示領域の幅を大きくしな

くても、多くのスイッチング素子を形成できるので、液晶表示装置の表示領域を有効に保

護することができるようになる。なお、信号線の屈曲形態としては、通常は表示領域の画

素の形状が信号線側が長辺の矩形状に形成されているため、平面視で表示領域の上下側の

非表示領域内で「コ」字状にジグザグに屈曲させることが好ましい。表示領域の画素の形

状が横長の矩形状の場合には、信号線は平面視で表示領域の上下側の非表示領域内で凸状

ないし凹状に屈曲していることが望ましい。何れの場合においても、走査線は信号線の屈

曲部に交差するように枝状に延びているものとすればよい。

非表示領域に形成されているTFTは、それぞれソース電極が前記信号線に接続され、ゲ

ート電極が前記走査線に接続され、ドレイン電極が前記コモン電位に接続されていること

が好ましい。

そのため、本発明の液晶表示装置によれば、表示領域のスイッチング素子及び非表示領域

のスイッチング素子とともにTFTからなるものとしたので、これらのスイッチング素子

を同時にかつ容易に製造することができるようになる。

前記表示領域に形成されているTFTのチャネル幅及びチャネル長よりも小さくなってい

ることが好ましい。

ているTFTよりも小さくなっていると、より静電破壊され易くなる。そのため、本発明

の液晶表示装置によれば、外部から静電気が浸入しても確実に非表示領域に形成されてい

るTFTが先に静電破壊されるので、静電気が表示領域内に進入し難くなり、液晶表示装

置の表示領域を有効に保護することができるようになる。

以下に示す実施形態は、本発明をここに記載したものに限定することを意図するものでは

なく、本発明は特許請求の範囲に示した技術思想を逸脱することなく種々の変更を行った

ものにも均しく適用し得るものである。なお、この明細書における説明のために用いられ

た各図面においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層

や各部材毎に縮尺を異ならせて表示しており、必ずしも実際の寸法に比例して表示されて

いるものではない。

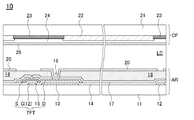

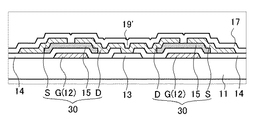

分の拡大平面図である。図3は図2の表示領域の1サブ画素分の拡大平面図である。図4

は図3のIV−IV線の断面図である。図5は図2の表示領域の左右側の非表示領域の1画素

分の領域の拡大平面図である。図6は図5のVI−VI線の断面図である。図7は変形例の表

示領域の左右側の非表示領域の1画素分の領域の拡大平面図である。

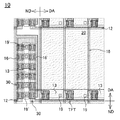

実施形態にかかる液晶パネル10を図1〜図6を用いて説明する。実施形態にかかる液

晶パネル10は、図4に示すように、液晶層LCをアレイ基板AR及びカラーフィルタ基

板CFとの間に挟持している。液晶層LCの厚みは図示しない柱状スペーサによって均一

に維持される。また、アレイ基板ARの背面及びカラーフィルタ基板CFの前面にはそれ

ぞれ偏光板(図示省略)が形成されている。そして、アレイ基板ARの背面側からバック

ライト(図示省略)により光が照射されている。

周辺である非表示領域NDとを備えており、この非表示領域NDの一つの端部側にドライ

バICを載置するための第1端子部Drと、外部接続用の第2端子部Tpとが形成されて

いる。そして、非表示領域NDには、表示領域DAの走査線を第1端子部Drへ引き回す

走査線引き回し配線GL及び信号線を第1端子部Drへと引き回す信号線引き回し配線S

Lを備えている。また、非表示領域NDには、補助容量線13(図3及び図4参照)を第

1端子部Drへと引き回すためのコモン配線COMも形成されている。

きた静電気に対する静電保護手段が形成され、表示領域の左右側の非表示領域には走査線

引き回し配線GL側から進入してきた静電気に対する静電保護手段が形成されている。ま

た、表示領域の上下側の非表示領域と左右側の非表示領域と間の角部は、信号線引き回し

配線SL及び走査線引き回し配線GLの両者側から進入してきた静電気に対する静電保護

手段が形成されている。なお、これらの静電保護手段の詳細な構成については後述するが

、本発明においては、全ての1画素分の領域内の静電気保護手段の構成を同一とすること

ができるので、以下においては、一つの1画素分の領域内の静電気保護手段について説明

することとする。

及び図4に示すように、ガラスや石英、プラスチック等からなる第1基板11の液晶LC

側に、アルミニウム金属、アルミニウム合金、モリブデン等の不透明な金属からなる複数

の走査線12と、この走査線12間に平行に形成された補助容量線(幅が広くなっている

補助容量電極として作用する部分も含む)13と、非表示領域NDに形成されたコモン配

線COMを有している。このうち、走査線12及び補助容量線(幅が広くなっている補助

容量電極として作用する部分も含む)13は、表示領域DAだけでなく非表示領域NDに

も形成される。

走査線12側に沿って形成されている。また、この走査線12等の形成時に、非表示領域

NDの走査線引き回し配線GL部分には第1端子部Drに向かって伸びる複数のゲート配

線が形成され、信号線引き回し配線においても同じく第1端子部Drに向かって伸びる複

数のゲート配線が形成される(図示省略)。

が、表示領域DAの1画素分の領域の場合と同様に、走査線12側が短辺となる矩形状を

しているため、走査線12は凸状に屈曲した形状に折れ曲げられている。これらの走査線

12、補助容量線13、ゲート配線及びコモン配線COMは、第1基板11の表面全体に

亘ってアルミニウム金属、アルミニウム合金、モリブデン等の不透明な金属層を形成した

後、スピンコーティング法によってレジストを塗布し、所定のパターンとなるように露光

及び現像処理を行った後、不要部分をエッチングすることにより作製される。なお、非表

示領域NDの1画素分の領域内の補助容量線13は、中央部にベタ状に形成されており、

非表示領域NDの1画素分の領域内の走査線12とは、別途絶縁膜を介して走査線12の

表面を迂回され、表示領域DAの補助容量線13と電気的に接続されている。その後、走

査線12、ゲート配線、補助容量線13及び第1基板11の露出面を覆って、酸化ケイ素

ないし窒化ケイ素等の無機絶縁膜からなるゲート絶縁膜14が形成される。

形成される。この半導体層15も、ゲート絶縁膜14の表面全体に亘ってアモルファスシ

リコン層を形成した後、スピンコーティング法によってレジストを塗布し、所定のパター

ンとなるように露光及び現像処理を行った後、不要部分をエッチングすることにより作製

される。この半導体層15は、表示領域DAだけでなく非表示領域ND内のスイッチング

素子形成予定部分にも形成される。

対向する部分のゲート絶縁膜14に第1のコンタクトホール19'を形成する。その後、

半導体層15に一部乗り上げるようにして、ソース電極Sと、ドレイン電極Dとが形成さ

れる。この実施形態の液晶表示装置10では、表示領域DAにおいては、半導体層15は

ゲート絶縁膜14を介して走査線12の幅が部分的に広くされた箇所と対向配置されてお

り、この走査線12と平面視で重畳する部分がTFTのゲート電極Gを構成している。ソ

ース電極Sは信号線16から分岐した部分からなる。信号線16及びドレイン電極Dは、

それぞれアルミニウム金属、アルミニウム合金、モリブデン等の不透明な金属で形成され

、表示領域DAだけでなく非表示領域ND内にも形成される。そのため、非表示領域ND

の1画素分の領域内に形成されたドレイン電極D部分は、コンタクトホール19'を経て

、全て補助容量線13と電気的に接続された状態となる。

岐信号線16'は折り曲げられた走査線12の周囲に沿って延在されている。更に、信号

線16及びドレイン電極Dの形成時に、非表示領域NDの走査線引き回し配線GLには第

1端子部Drに向かって伸びる複数のソース配線が形成されると共に、信号線引き回し配

線SLにも同じく第1端子部Drに向かって延びるソース配線が形成される(図示省略)

。なお、本発明におけるゲート配線及びソース配線は、必ずしも液晶パネルの走査線12

ないし信号線16に接続されている配線を意味するものではなく、走査線12と同時に形

成された配線をゲート配線といい、信号線16と同時に形成された配線をソース配線とい

う。したがって、上記実施形態の液晶表示装置10では、ゲート絶縁膜14の下にある配

線部分がゲート配線となり、ゲート絶縁膜14の上にある配線部分がソース配線となり、

平面視では両者間に区別はない。

びゲート絶縁膜14の露出部を覆うように、表示領域DA及び非表示領域ND共に、酸化

ケイ素ないし窒化ケイ素等の無機絶縁膜からなるパッシベーション膜17が形成される。

更に、表示領域DAにおいては、パッシベーション膜17を覆って樹脂材料からなる層間

膜18が形成される。層間膜18としては、透明性が良好で、電気絶縁性に優れた感光性

レジスト材料を適宜選択して使用し得る。この層間膜18は、パッシベーション膜17の

表面にスピンコーティング法によってレジストを塗布し、所定のパターンとなるように露

光及び現像処理を行った後、不要部分をエッチングすることにより作製される。

うに第2のコンタクトホール19が形成される。更に、層間膜18を覆うように、表示領

域DAの画素領域毎にITO、IZO等の透明導電材料からなる画素電極20が形成され

る。この画素電極20は、第2のコンタクトホール19を経てドレイン電極Dと電気的に

接続されている。更に、画素電極20の表面を覆うように配向膜(図示省略)が形成され

て、実施形態の液晶表示装置10におけるアレイ基板ARが得られる。

石英、プラスチック等からなる第2基板21を有している。この第2基板21には、サブ

画素毎に異なる色の光(R、G、Bあるいは無色)を透過するカラーフィルタ層22と遮

光層23が形成されている。カラーフィルタ層22と遮光層23を覆うようにしてトップ

コート層24が形成されており、トップコート層24を覆うようにしてITOないしIZ

Oからなる共通電極25が形成されている。そして、共通電極25の表面には配向膜(図

示せず)が形成されて、実施形態の液晶表示装置10のカラーフィルタ基板が完成される

。

させ、周縁部をシール材(図示せず)によってシールし、液晶LCをアレイ基板ARとカ

ラーフィルタ基板CFの間に形成された密封エリア内に封止することにより実施形態の液

晶パネル10が得られる。

いて説明する。本実施形態の液晶表示装置10では、非表示領域NDは、表示領域DAの

上下側、表示領域DAの左右側及び表示領域DAの上下側と左右側の角部に形成されるが

、それぞれの1画素分の領域は全て同じ大きさ及び形状とされている。

で、走査線12は隣接する信号線12に沿うように細長く凸状となるように折り曲げられ

ている。そして、信号線16からは分岐信号線16'が折り曲げられた走査線12の周囲

に沿って、隣接する信号線16との間を占めるように延在されている。折り曲げられた走

査線12上にはゲート絶縁膜14を介して複数個、ここでは12個の半導体層15が形成

されており、この半導体層15に部分的に重なるようにして信号線16及び分岐信号線1

6'側にソース電極Sが、中央側にドレイン電極Dが形成されている。非表示領域NDの

1画素分の領域内の補助容量線13は、中央部にベタ状に形成されており、ドレイン電極

Dはゲート絶縁膜14に形成された第1のコンタクトホール19'を経て補助容量線13

と電気的に接続されている。なお、この非表示領域NDの1画素分の領域内の補助容量線

13は、凸状となるように折り曲げられた走査線12とは別途絶縁膜を介して走査線12

の表面を迂回され、表示領域DAの補助容量線13と電気的に接続されている。

内に複数個、ここでは6×2=12個の静電保護素子としてのTFT(以下、「保護TF

T」という。)30が形成されている。これらの保護TFT30は、表示領域DAに形成

されているTFTと同時に形成し易くするためにサイズは表示領域DAに形成されている

TFTと実質的に同一とされているが、チャネル幅及びチャネル長は表示領域DAに形成

されているTFTのものよりも小さくされている。そのため、保護TFT30は、表示領

域DAに形成されているTFTよりも静電的に弱くなるので、表示領域DAに形成されて

いるTFTよりも先に静電破壊される。

の領域内において、保護TFT30のゲート電極Gは同一の走査線12上に形成され、ソ

ース電極Sは同一の信号線ないし分岐信号線16'に電気的に接続され、更にドレイン電

極Dも同一の非表示領域NDの1画素分の領域内に形成されている補助容量線13に電気

的に接続されている。すなわち、それぞれの非表示領域NDの1画素分の領域内において

、複数個の保護TFT30は互いに並列接続されている。

Tpから信号線引き回し配線SL(図1参照)を経て信号線16に沿って静電気が進入し

た場合、最初に最も第1端子部Drないし第2端子部Tpに近い位置の信号線16ないし

分岐信号線16'に接続されている保護TFT30が静電破壊され、静電気は、第1のコ

ンタクトホール19'、補助容量線13を経てコモン電位に流れて放電される。

線12に沿って静電気が進入した場合においても、最初に最も第1端子部Drないし第2

端子部Tpに近い位置の走査線12に接続されている保護TFT30が静電破壊され、静

電気は、第1のコンタクトホール19'、補助容量線13を経てコモン電位に流れて放電

される。

静電気が進入してきても、最も静電気が進入してきた側に近い保護TFTが静電破壊され

ることにより、他の保護TFT30及び表示領域DAのTFTは保護される。このような

保護動作は、表示領域DAに最も近い保護TFT30が静電破壊されるまで継続できるの

で、1走査線当たりないし1信号線当たりに接続されている保護TFT30の数を増加さ

せることにより、より多くの静電気進入に耐えることができるようになる。

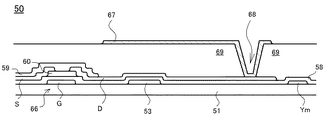

上記実施形態の液晶表示装置10では、非表示領域NDの1画素分の領域内の走査線1

2の長さを長くするために走査線12を屈曲させた例を示したが、信号線16の長さを長

くするために信号線16を屈曲させることもできる。このような非表示領域NDの1画素

分の領域内の信号線16を屈曲させた変形例を図7を用いて説明する。

にジグザグに折り曲げられている。そして、走査線12からは枝状に分岐された分岐走査

線12'が「コ」字状にジグザグに折り曲げられた信号線16を横切るように配置されて

いる。そして、分岐走査線12'上にこの分岐走査線12'をゲート電極Gとする保護TF

T30が複数個、ここでは8個形成されている。また、非表示領域NDの1画素分の領域

内の補助容量線は、図示省略したが、それぞれのドレイン電極Dの下部に配置されており

、分岐走査線12'を跨ぐ部分は別途絶縁膜を介して表示領域DAの補助容量線13と電

気的に接続されている。なお、この変形例の非表示領域NDの1画素分の領域内において

は、走査線12から分岐した分岐走査線12'の幅は、インピーダンスを下げて、全ての

保護TFT30が有効に作動するようになすため、可能な限り太くするとよい。

せないようにするためには補助容量線をベタ状に配置することができないので、上述のよ

うに、適宜ゲート配線及びソース配線を利用してそれぞれの保護TFT30のドレイン電

極Dを電気的に補助容量線に接続すればよい。更には、表示領域DAの画素電極20の場

合と同様に、非表示領域NDの1画素分の領域内に層間膜18及びダミー画素電極を形成

し、このダミー画素電極を表示領域外でコモン配線COMに接続すると共に、ダミー画素

電極を層間膜18及びパッシベーション膜17に形成したコンタクトホールを経て保護T

FT30のドレイン電極Dと電気的に接続してもよい。このような構成とすると特に非表

示領域NDの1画素分の領域内に補助容量線を形成しなくてもすむ。

表示領域NDの1画素分の領域の形状も縦長である場合について説明した。しかしながら

、表示領域DAの画素の形状が横長の矩形状である場合、非表示領域NDの1画素分の領

域では、走査線を屈曲させるようにする場合は「コ」字状にジグザグに屈曲しているよう

にすれば良く、信号線を屈曲させるようにする場合は凸状ないし凹状に屈曲しているよう

にすればよい。また、上記実施形態においては、全ての1画素分の領域内の静電気保護手

段の構成を同一とした例について説明したが、表示領域DAの左右の非表示領域NDと上

下の表示領域NDとでそれぞれ異なる構成となしてもよい。

とり説明したが、本発明はこれに限らず、他のモードの縦電界方式の液晶表示装置に対し

ても、或いは、横電界方式の液晶表示装置に対しても、更には反射部を有する詠唱表示装

置に対しても等しく適用可能である。特に、層間膜上に下電極及びスリットを有する上電

極を備える構成のFFSモードの液晶表示装置においては、上電極又は下電極はコモン電

位に接続されているので、上記変形例の構成を採用しても特に製造工数を増加させること

なく簡単に保護TFT30ドレイン電極Dをコモン電位に接続することができるようにな

る。

容量線 14…ゲート絶縁膜 15…半導体層 16…信号線 16'…分岐信号線 1

7…パッシベーション膜 18…層間膜 19、19'…コンタクトホール 20…画素

電極 21…第2基板 22…カラーフィルタ層 23…遮光層 24…トップコート層

25…共通電極 30…保護TFT AR…アレイ基板 CF…カラーフィルタ基板

DA…表示領域 ND…非表示領域 COM…共通配線 GL…走査線引き回し配線 S

L…信号線引き回し配線

Claims (6)

- 液晶層を挟持して対向配置された第1基板及び第2基板を有し、前記第1基板の液晶層

側には、マトリクス状に配置された複数の走査線及び信号線と、表示領域の前記各走査線

及び信号線の交差部近傍に配置されたスイッチング素子と、前記表示領域の前記各走査線

及び信号線で囲まれた画素領域毎にそれぞれ配置されているとともに前記スイッチング素

子に電気的に接続された画素電極と、前記表示領域の周囲に非表示領域が形成された液晶

表示装置において、

前記非表示領域には、前記走査線又は信号線に屈曲部が形成され、前記屈曲部に沿って

複数のスイッチング素子が形成され、前記複数のスイッチング素子は互いに並列に接続さ

れて前記スイッチング素子の電極の一つはコモン電位に接続されていることを特徴とする

液晶表示装置。 - 前記非表示領域に形成されたスイッチング素子は、前記画素領域に形成されたスイッチ

ング素子と略同一の大きさであることを特徴とする請求項1に記載の液晶表示装置。 - 前記非表示領域には、前記走査線に屈曲部が形成され、前記信号線は前記走査線の屈曲

部の外周囲に沿って延びる分岐信号線が形成されていることを特徴とする請求項1に記載

の液晶表示装置。 - 前記非表示領域には、前記信号線に屈曲部が形成され、前記走査線は前記信号線の屈曲

部に交差するように延びる分岐走査線が形成されていることを特徴とする請求項1に記載

の液晶表示装置。 - 前記スイッチング素子は薄膜トランジスタであり、前記非表示領域に形成されている薄

膜トランジスタは、それぞれソース電極が前記信号線に接続され、ゲート電極が前記走査

線に接続され、ドレイン電極が前記コモン電位に接続されていることを特徴とする請求項

1〜4のいずれかに記載の液晶表示装置。 - 前記非表示領域に形成されている薄膜トランジスタは、前記表示領域に形成されている

薄膜トランジスタのチャネル幅及びチャネル長よりも小さくなっていることを特徴とする

請求項5に記載の液晶表示装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269671A JP5472895B2 (ja) | 2008-10-20 | 2008-10-20 | 液晶表示装置 |

| US12/547,738 US8493543B2 (en) | 2008-10-17 | 2009-08-26 | Liquid crystal display device |

| KR1020090098197A KR101064389B1 (ko) | 2008-10-17 | 2009-10-15 | 액정 표시 장치 |

| TW098135065A TWI476496B (zh) | 2008-10-17 | 2009-10-16 | 液晶顯示裝置 |

| CN2009101740093A CN101726895B (zh) | 2008-10-17 | 2009-10-16 | 液晶显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269671A JP5472895B2 (ja) | 2008-10-20 | 2008-10-20 | 液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010097114A true JP2010097114A (ja) | 2010-04-30 |

| JP5472895B2 JP5472895B2 (ja) | 2014-04-16 |

Family

ID=42258821

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008269671A Active JP5472895B2 (ja) | 2008-10-17 | 2008-10-20 | 液晶表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5472895B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108122926A (zh) * | 2016-11-29 | 2018-06-05 | 合肥鑫晟光电科技有限公司 | 阵列基板及其制作方法、显示面板和显示装置 |

| JP2023133618A (ja) * | 2012-11-16 | 2023-09-22 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07333654A (ja) * | 1994-06-10 | 1995-12-22 | Sony Corp | アクティブマトリクス型液晶表示装置 |

| JPH0997909A (ja) * | 1995-09-28 | 1997-04-08 | Sharp Corp | 液晶表示装置 |

| JPH1062808A (ja) * | 1996-08-23 | 1998-03-06 | Toshiba Corp | 液晶表示装置 |

| JP2000323664A (ja) * | 1999-05-13 | 2000-11-24 | Nec Corp | 半導体装置 |

| JP2000338514A (ja) * | 1999-05-31 | 2000-12-08 | Hitachi Ltd | 液晶表示装置 |

| JP2001142096A (ja) * | 1999-08-31 | 2001-05-25 | Fujitsu Ltd | 液晶表示装置 |

| JP2002110995A (ja) * | 2000-09-29 | 2002-04-12 | Casio Comput Co Ltd | アクティブマトリックス基板 |

| JP2006276590A (ja) * | 2005-03-30 | 2006-10-12 | Sanyo Epson Imaging Devices Corp | アクティブマトリクス型液晶表示装置 |

| JP2007188076A (ja) * | 2006-01-10 | 2007-07-26 | Toppoly Optoelectronics Corp | 表示画素と非表示画素を含む画像を表示するディスプレイ装置 |

-

2008

- 2008-10-20 JP JP2008269671A patent/JP5472895B2/ja active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07333654A (ja) * | 1994-06-10 | 1995-12-22 | Sony Corp | アクティブマトリクス型液晶表示装置 |

| JPH0997909A (ja) * | 1995-09-28 | 1997-04-08 | Sharp Corp | 液晶表示装置 |

| JPH1062808A (ja) * | 1996-08-23 | 1998-03-06 | Toshiba Corp | 液晶表示装置 |

| JP2000323664A (ja) * | 1999-05-13 | 2000-11-24 | Nec Corp | 半導体装置 |

| JP2000338514A (ja) * | 1999-05-31 | 2000-12-08 | Hitachi Ltd | 液晶表示装置 |

| JP2001142096A (ja) * | 1999-08-31 | 2001-05-25 | Fujitsu Ltd | 液晶表示装置 |

| JP2002110995A (ja) * | 2000-09-29 | 2002-04-12 | Casio Comput Co Ltd | アクティブマトリックス基板 |

| JP2006276590A (ja) * | 2005-03-30 | 2006-10-12 | Sanyo Epson Imaging Devices Corp | アクティブマトリクス型液晶表示装置 |

| JP2007188076A (ja) * | 2006-01-10 | 2007-07-26 | Toppoly Optoelectronics Corp | 表示画素と非表示画素を含む画像を表示するディスプレイ装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2023133618A (ja) * | 2012-11-16 | 2023-09-22 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP7550934B2 (ja) | 2012-11-16 | 2024-09-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN108122926A (zh) * | 2016-11-29 | 2018-06-05 | 合肥鑫晟光电科技有限公司 | 阵列基板及其制作方法、显示面板和显示装置 |

| CN108122926B (zh) * | 2016-11-29 | 2023-09-22 | 合肥鑫晟光电科技有限公司 | 阵列基板及其制作方法、显示面板和显示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5472895B2 (ja) | 2014-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101064389B1 (ko) | 액정 표시 장치 | |

| US11774809B2 (en) | Liquid crystal display panel | |

| JP5548488B2 (ja) | 液晶表示パネル | |

| US8405808B2 (en) | Active matrix substrate and display unit provided with it | |

| JP4762297B2 (ja) | 液晶表示装置 | |

| CN101419366B (zh) | 液晶装置以及具备它的电子设备 | |

| JP4858820B2 (ja) | アクティブマトリクス基板及び液晶表示装置並びにその製造方法 | |

| JP3792670B2 (ja) | 横電界方式のアクティブマトリクス型液晶表示装置及びその製造方法 | |

| JP2003167270A (ja) | 反射型液晶表示装置及びその製造方法 | |

| CN101359139A (zh) | 液晶显示面板及其制造方法 | |

| JP5429776B2 (ja) | 液晶表示パネル | |

| KR20080068949A (ko) | 어레이 기판 및 이를 갖는 표시패널 | |

| KR20090033809A (ko) | 액정 표시 장치 및 전자 기기 | |

| JP5681269B2 (ja) | 液晶表示パネル | |

| JP3464945B2 (ja) | 液晶表示装置 | |

| JP5271661B2 (ja) | 液晶表示装置 | |

| JP5472895B2 (ja) | 液晶表示装置 | |

| KR100698049B1 (ko) | 액정표시장치 및 그의 제조방법 | |

| JP5131525B2 (ja) | アクティブマトリクス型液晶表示装置 | |

| JP2001092378A (ja) | アクティブマトリクス基板 | |

| JP5429775B2 (ja) | 液晶パネル | |

| JP5455011B2 (ja) | 液晶表示パネル | |

| JP4404835B2 (ja) | 横電界方式のアクティブマトリクス型液晶表示装置及びその製造方法 | |

| KR101423909B1 (ko) | 표시 기판 및 이를 구비하는 액정 표시 장치 | |

| KR20120015555A (ko) | 액정표시장치용 어레이기판 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20100702 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100702 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110824 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20120330 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130228 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20130328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130430 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130621 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140114 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20140129 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140129 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5472895 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |