JP2010074088A - 有機半導体装置、有機半導体装置の製造方法、電子デバイス、電子機器および絶縁層形成組成物 - Google Patents

有機半導体装置、有機半導体装置の製造方法、電子デバイス、電子機器および絶縁層形成組成物 Download PDFInfo

- Publication number

- JP2010074088A JP2010074088A JP2008242937A JP2008242937A JP2010074088A JP 2010074088 A JP2010074088 A JP 2010074088A JP 2008242937 A JP2008242937 A JP 2008242937A JP 2008242937 A JP2008242937 A JP 2008242937A JP 2010074088 A JP2010074088 A JP 2010074088A

- Authority

- JP

- Japan

- Prior art keywords

- organic semiconductor

- insulating layer

- electrode

- gate

- polymer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 120

- 238000000034 method Methods 0.000 title claims description 65

- 238000004519 manufacturing process Methods 0.000 title claims description 23

- 238000009413 insulation Methods 0.000 title abstract description 8

- 239000000203 mixture Substances 0.000 title description 4

- 229920000642 polymer Polymers 0.000 claims abstract description 135

- 239000000463 material Substances 0.000 claims abstract description 38

- 239000010410 layer Substances 0.000 claims description 212

- 239000002904 solvent Substances 0.000 claims description 46

- 239000000758 substrate Substances 0.000 claims description 41

- 230000008569 process Effects 0.000 claims description 26

- 239000007791 liquid phase Substances 0.000 claims description 24

- 125000003118 aryl group Chemical group 0.000 claims description 15

- 125000004430 oxygen atom Chemical group O* 0.000 claims description 14

- 125000005647 linker group Chemical group 0.000 claims description 8

- 229910052717 sulfur Inorganic materials 0.000 claims description 8

- 125000004434 sulfur atom Chemical group 0.000 claims description 8

- JBTWLSYIZRCDFO-UHFFFAOYSA-N ethyl methyl carbonate Chemical compound CCOC(=O)OC JBTWLSYIZRCDFO-UHFFFAOYSA-N 0.000 claims description 6

- 239000011254 layer-forming composition Substances 0.000 claims description 6

- 229920001940 conductive polymer Polymers 0.000 claims description 5

- 239000000126 substance Substances 0.000 claims description 5

- 239000002612 dispersion medium Substances 0.000 claims description 4

- 239000002923 metal particle Substances 0.000 claims description 4

- 125000000468 ketone group Chemical group 0.000 claims 1

- 239000010409 thin film Substances 0.000 description 97

- 239000000243 solution Substances 0.000 description 37

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 30

- 239000010408 film Substances 0.000 description 24

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 22

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 18

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 18

- 230000000052 comparative effect Effects 0.000 description 18

- BWHMMNNQKKPAPP-UHFFFAOYSA-L potassium carbonate Chemical compound [K+].[K+].[O-]C([O-])=O BWHMMNNQKKPAPP-UHFFFAOYSA-L 0.000 description 18

- 239000011159 matrix material Substances 0.000 description 17

- 239000008367 deionised water Substances 0.000 description 15

- 229910021641 deionized water Inorganic materials 0.000 description 15

- 239000010931 gold Substances 0.000 description 14

- 239000002245 particle Substances 0.000 description 14

- 239000006185 dispersion Substances 0.000 description 13

- 238000001226 reprecipitation Methods 0.000 description 13

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 12

- 239000011521 glass Substances 0.000 description 12

- 229910052737 gold Inorganic materials 0.000 description 12

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 12

- -1 polyethylene terephthalate Polymers 0.000 description 12

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 10

- 229910052731 fluorine Inorganic materials 0.000 description 10

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 10

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 10

- 239000004926 polymethyl methacrylate Substances 0.000 description 10

- OKKJLVBELUTLKV-UHFFFAOYSA-N Methanol Chemical compound OC OKKJLVBELUTLKV-UHFFFAOYSA-N 0.000 description 9

- 125000002915 carbonyl group Chemical group [*:2]C([*:1])=O 0.000 description 9

- 238000007865 diluting Methods 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 229910000027 potassium carbonate Inorganic materials 0.000 description 9

- 239000011241 protective layer Substances 0.000 description 9

- 239000007787 solid Substances 0.000 description 9

- 238000004528 spin coating Methods 0.000 description 9

- 238000012360 testing method Methods 0.000 description 9

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 8

- FXHOOIRPVKKKFG-UHFFFAOYSA-N N,N-Dimethylacetamide Chemical compound CN(C)C(C)=O FXHOOIRPVKKKFG-UHFFFAOYSA-N 0.000 description 7

- DQEPMTIXHXSFOR-UHFFFAOYSA-N benzo[a]pyrene diol epoxide I Chemical compound C1=C2C(C3OC3C(C3O)O)=C3C=C(C=C3)C2=C2C3=CC=CC2=C1 DQEPMTIXHXSFOR-UHFFFAOYSA-N 0.000 description 7

- 239000000470 constituent Substances 0.000 description 7

- 125000004185 ester group Chemical group 0.000 description 7

- 239000007788 liquid Substances 0.000 description 7

- 239000002808 molecular sieve Substances 0.000 description 7

- URGAHOPLAPQHLN-UHFFFAOYSA-N sodium aluminosilicate Chemical compound [Na+].[Al+3].[O-][Si]([O-])=O.[O-][Si]([O-])=O URGAHOPLAPQHLN-UHFFFAOYSA-N 0.000 description 7

- 239000004372 Polyvinyl alcohol Substances 0.000 description 6

- WYURNTSHIVDZCO-UHFFFAOYSA-N Tetrahydrofuran Chemical compound C1CCOC1 WYURNTSHIVDZCO-UHFFFAOYSA-N 0.000 description 6

- 238000010521 absorption reaction Methods 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 6

- 239000002798 polar solvent Substances 0.000 description 6

- 229920002451 polyvinyl alcohol Polymers 0.000 description 6

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 5

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 230000015556 catabolic process Effects 0.000 description 5

- 238000000576 coating method Methods 0.000 description 5

- 229920001577 copolymer Polymers 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 239000011737 fluorine Substances 0.000 description 5

- 125000001153 fluoro group Chemical group F* 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 150000002576 ketones Chemical group 0.000 description 5

- UHOVQNZJYSORNB-UHFFFAOYSA-N monobenzene Natural products C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 5

- YLQBMQCUIZJEEH-UHFFFAOYSA-N tetrahydrofuran Natural products C=1C=COC=1 YLQBMQCUIZJEEH-UHFFFAOYSA-N 0.000 description 5

- 238000007740 vapor deposition Methods 0.000 description 5

- SYBYTAAJFKOIEJ-UHFFFAOYSA-N 3-Methylbutan-2-one Chemical compound CC(C)C(C)=O SYBYTAAJFKOIEJ-UHFFFAOYSA-N 0.000 description 4

- IAZDPXIOMUYVGZ-UHFFFAOYSA-N Dimethylsulphoxide Chemical compound CS(C)=O IAZDPXIOMUYVGZ-UHFFFAOYSA-N 0.000 description 4

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 4

- 239000011248 coating agent Substances 0.000 description 4

- USIUVYZYUHIAEV-UHFFFAOYSA-N diphenyl ether Chemical compound C=1C=CC=CC=1OC1=CC=CC=C1 USIUVYZYUHIAEV-UHFFFAOYSA-N 0.000 description 4

- 238000001035 drying Methods 0.000 description 4

- 238000001914 filtration Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 239000002861 polymer material Substances 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- WEVYAHXRMPXWCK-UHFFFAOYSA-N Acetonitrile Chemical compound CC#N WEVYAHXRMPXWCK-UHFFFAOYSA-N 0.000 description 3

- 229920002799 BoPET Polymers 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 3

- YMWUJEATGCHHMB-UHFFFAOYSA-N Dichloromethane Chemical compound ClCCl YMWUJEATGCHHMB-UHFFFAOYSA-N 0.000 description 3

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 3

- XTHFKEDIFFGKHM-UHFFFAOYSA-N Dimethoxyethane Chemical compound COCCOC XTHFKEDIFFGKHM-UHFFFAOYSA-N 0.000 description 3

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- MWPLVEDNUUSJAV-UHFFFAOYSA-N anthracene Chemical compound C1=CC=CC2=CC3=CC=CC=C3C=C21 MWPLVEDNUUSJAV-UHFFFAOYSA-N 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 239000003094 microcapsule Substances 0.000 description 3

- VLKZOEOYAKHREP-UHFFFAOYSA-N n-Hexane Chemical compound CCCCCC VLKZOEOYAKHREP-UHFFFAOYSA-N 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 238000005406 washing Methods 0.000 description 3

- FYGHSUNMUKGBRK-UHFFFAOYSA-N 1,2,3-trimethylbenzene Chemical compound CC1=CC=CC(C)=C1C FYGHSUNMUKGBRK-UHFFFAOYSA-N 0.000 description 2

- 125000003363 1,3,5-triazinyl group Chemical group N1=C(N=CN=C1)* 0.000 description 2

- MLDVGCCQHBDHDR-UHFFFAOYSA-N 2-(3-hexylthiophen-2-yl)-5-[5-(3-hexylthiophen-2-yl)thiophen-2-yl]thiophene Chemical compound C1=CSC(C=2SC(=CC=2)C=2SC(=CC=2)C2=C(C=CS2)CCCCCC)=C1CCCCCC MLDVGCCQHBDHDR-UHFFFAOYSA-N 0.000 description 2

- ZNQVEEAIQZEUHB-UHFFFAOYSA-N 2-ethoxyethanol Chemical compound CCOCCO ZNQVEEAIQZEUHB-UHFFFAOYSA-N 0.000 description 2

- POXVKKNWVAADKL-UHFFFAOYSA-N 3,4-dihexyl-2-[3-[3-[3-(3-thiophen-2-ylthiophen-2-yl)thiophen-2-yl]thiophen-2-yl]thiophen-2-yl]thiophene Chemical compound C(CCCCC)C=1C(=C(SC1)C=1SC=CC1C=1SC=CC1C=1SC=CC1C=1SC=CC1C=1SC=CC1)CCCCCC POXVKKNWVAADKL-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- XMWRBQBLMFGWIX-UHFFFAOYSA-N C60 fullerene Chemical compound C12=C3C(C4=C56)=C7C8=C5C5=C9C%10=C6C6=C4C1=C1C4=C6C6=C%10C%10=C9C9=C%11C5=C8C5=C8C7=C3C3=C7C2=C1C1=C2C4=C6C4=C%10C6=C9C9=C%11C5=C5C8=C3C3=C7C1=C1C2=C4C6=C2C9=C5C3=C12 XMWRBQBLMFGWIX-UHFFFAOYSA-N 0.000 description 2

- HEDRZPFGACZZDS-UHFFFAOYSA-N Chloroform Chemical compound ClC(Cl)Cl HEDRZPFGACZZDS-UHFFFAOYSA-N 0.000 description 2

- PEDCQBHIVMGVHV-UHFFFAOYSA-N Glycerine Chemical compound OCC(O)CO PEDCQBHIVMGVHV-UHFFFAOYSA-N 0.000 description 2

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 2

- NTIZESTWPVYFNL-UHFFFAOYSA-N Methyl isobutyl ketone Chemical compound CC(C)CC(C)=O NTIZESTWPVYFNL-UHFFFAOYSA-N 0.000 description 2

- UIHCLUNTQKBZGK-UHFFFAOYSA-N Methyl isobutyl ketone Natural products CCC(C)C(C)=O UIHCLUNTQKBZGK-UHFFFAOYSA-N 0.000 description 2

- IMNFDUFMRHMDMM-UHFFFAOYSA-N N-Heptane Chemical compound CCCCCCC IMNFDUFMRHMDMM-UHFFFAOYSA-N 0.000 description 2

- OFBQJSOFQDEBGM-UHFFFAOYSA-N Pentane Chemical compound CCCCC OFBQJSOFQDEBGM-UHFFFAOYSA-N 0.000 description 2

- 229920000291 Poly(9,9-dioctylfluorene) Polymers 0.000 description 2

- XBDQKXXYIPTUBI-UHFFFAOYSA-M Propionate Chemical compound CCC([O-])=O XBDQKXXYIPTUBI-UHFFFAOYSA-M 0.000 description 2

- KYQCOXFCLRTKLS-UHFFFAOYSA-N Pyrazine Chemical compound C1=CN=CC=N1 KYQCOXFCLRTKLS-UHFFFAOYSA-N 0.000 description 2

- JUJWROOIHBZHMG-UHFFFAOYSA-N Pyridine Chemical compound C1=CC=NC=C1 JUJWROOIHBZHMG-UHFFFAOYSA-N 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- DHXVGJBLRPWPCS-UHFFFAOYSA-N Tetrahydropyran Chemical compound C1CCOCC1 DHXVGJBLRPWPCS-UHFFFAOYSA-N 0.000 description 2

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 2

- DTQVDTLACAAQTR-UHFFFAOYSA-N Trifluoroacetic acid Chemical compound OC(=O)C(F)(F)F DTQVDTLACAAQTR-UHFFFAOYSA-N 0.000 description 2

- 229920000109 alkoxy-substituted poly(p-phenylene vinylene) Polymers 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- RDOXTESZEPMUJZ-UHFFFAOYSA-N anisole Chemical compound COC1=CC=CC=C1 RDOXTESZEPMUJZ-UHFFFAOYSA-N 0.000 description 2

- 239000011230 binding agent Substances 0.000 description 2

- IISBACLAFKSPIT-UHFFFAOYSA-N bisphenol A Chemical compound C=1C=C(O)C=CC=1C(C)(C)C1=CC=C(O)C=C1 IISBACLAFKSPIT-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000000084 colloidal system Substances 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- SBZXBUIDTXKZTM-UHFFFAOYSA-N diglyme Chemical compound COCCOCCOC SBZXBUIDTXKZTM-UHFFFAOYSA-N 0.000 description 2

- 238000004090 dissolution Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 150000002148 esters Chemical class 0.000 description 2

- 238000011156 evaluation Methods 0.000 description 2

- 229910003472 fullerene Inorganic materials 0.000 description 2

- 238000007756 gravure coating Methods 0.000 description 2

- 238000007654 immersion Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 239000011344 liquid material Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- BDAGIHXWWSANSR-UHFFFAOYSA-N methanoic acid Natural products OC=O BDAGIHXWWSANSR-UHFFFAOYSA-N 0.000 description 2

- FDPIMTJIUBPUKL-UHFFFAOYSA-N pentan-3-one Chemical compound CCC(=O)CC FDPIMTJIUBPUKL-UHFFFAOYSA-N 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- KJFMBFZCATUALV-UHFFFAOYSA-N phenolphthalein Chemical compound C1=CC(O)=CC=C1C1(C=2C=CC(O)=CC=2)C2=CC=CC=C2C(=O)O1 KJFMBFZCATUALV-UHFFFAOYSA-N 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920000301 poly(3-hexylthiophene-2,5-diyl) polymer Polymers 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 230000008961 swelling Effects 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- WSLDOOZREJYCGB-UHFFFAOYSA-N 1,2-Dichloroethane Chemical compound ClCCCl WSLDOOZREJYCGB-UHFFFAOYSA-N 0.000 description 1

- RYHBNJHYFVUHQT-UHFFFAOYSA-N 1,4-Dioxane Chemical compound C1COCCO1 RYHBNJHYFVUHQT-UHFFFAOYSA-N 0.000 description 1

- QMEFNLUMYJUTGK-UHFFFAOYSA-N 1-N-(4-methoxyphenyl)-4-N,4-N-diphenylbenzene-1,4-diamine Chemical compound COC1=CC=C(C=C1)NC1=CC=C(C=C1)N(C1=CC=CC=C1)C1=CC=CC=C1 QMEFNLUMYJUTGK-UHFFFAOYSA-N 0.000 description 1

- XNWFRZJHXBZDAG-UHFFFAOYSA-N 2-METHOXYETHANOL Chemical compound COCCO XNWFRZJHXBZDAG-UHFFFAOYSA-N 0.000 description 1

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 1

- QCDWFXQBSFUVSP-UHFFFAOYSA-N 2-phenoxyethanol Chemical compound OCCOC1=CC=CC=C1 QCDWFXQBSFUVSP-UHFFFAOYSA-N 0.000 description 1

- KUJYDIFFRDAYDH-UHFFFAOYSA-N 2-thiophen-2-yl-5-[5-[5-(5-thiophen-2-ylthiophen-2-yl)thiophen-2-yl]thiophen-2-yl]thiophene Chemical compound C1=CSC(C=2SC(=CC=2)C=2SC(=CC=2)C=2SC(=CC=2)C=2SC(=CC=2)C=2SC=CC=2)=C1 KUJYDIFFRDAYDH-UHFFFAOYSA-N 0.000 description 1

- OSWFIVFLDKOXQC-UHFFFAOYSA-N 4-(3-methoxyphenyl)aniline Chemical compound COC1=CC=CC(C=2C=CC(N)=CC=2)=C1 OSWFIVFLDKOXQC-UHFFFAOYSA-N 0.000 description 1

- PVFQHGDIOXNKIC-UHFFFAOYSA-N 4-[2-[3-[2-(4-hydroxyphenyl)propan-2-yl]phenyl]propan-2-yl]phenol Chemical compound C=1C=CC(C(C)(C)C=2C=CC(O)=CC=2)=CC=1C(C)(C)C1=CC=C(O)C=C1 PVFQHGDIOXNKIC-UHFFFAOYSA-N 0.000 description 1

- OORILJYVKWFYKT-UHFFFAOYSA-N 6-(1,1,1,3,3,3-hexafluoropropan-2-yl)cyclohexa-2,4-diene-1,1-diol Chemical compound OC1(C(C=CC=C1)C(C(F)(F)F)C(F)(F)F)O OORILJYVKWFYKT-UHFFFAOYSA-N 0.000 description 1

- IXDGHAZCSMVIFX-UHFFFAOYSA-N 6-(dibutylamino)-1h-1,3,5-triazine-2,4-dithione Chemical compound CCCCN(CCCC)C1=NC(=S)NC(=S)N1 IXDGHAZCSMVIFX-UHFFFAOYSA-N 0.000 description 1

- 229920003026 Acene Polymers 0.000 description 1

- 239000005964 Acibenzolar-S-methyl Substances 0.000 description 1

- NLHHRLWOUZZQLW-UHFFFAOYSA-N Acrylonitrile Chemical compound C=CC#N NLHHRLWOUZZQLW-UHFFFAOYSA-N 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- GGBJHURWWWLEQH-UHFFFAOYSA-N Butyl-cyclohexane Natural products CCCCC1CCCCC1 GGBJHURWWWLEQH-UHFFFAOYSA-N 0.000 description 1

- UJOBWOGCFQCDNV-UHFFFAOYSA-N Carbazole Natural products C1=CC=C2C3=CC=CC=C3NC2=C1 UJOBWOGCFQCDNV-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- ZAFNJMIOTHYJRJ-UHFFFAOYSA-N Diisopropyl ether Chemical compound CC(C)OC(C)C ZAFNJMIOTHYJRJ-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 239000002879 Lewis base Substances 0.000 description 1

- 229920000106 Liquid crystal polymer Polymers 0.000 description 1

- 239000004977 Liquid-crystal polymers (LCPs) Substances 0.000 description 1

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- PCNDJXKNXGMECE-UHFFFAOYSA-N Phenazine Natural products C1=CC=CC2=NC3=CC=CC=C3N=C21 PCNDJXKNXGMECE-UHFFFAOYSA-N 0.000 description 1

- 229920000280 Poly(3-octylthiophene) Polymers 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 229920001665 Poly-4-vinylphenol Polymers 0.000 description 1

- 239000004962 Polyamide-imide Substances 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 229920002367 Polyisobutene Polymers 0.000 description 1

- 229920000265 Polyparaphenylene Polymers 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- XBDYBAVJXHJMNQ-UHFFFAOYSA-N Tetrahydroanthracene Natural products C1=CC=C2C=C(CCCC3)C3=CC2=C1 XBDYBAVJXHJMNQ-UHFFFAOYSA-N 0.000 description 1

- VEBSPLIVZXWXFB-UHFFFAOYSA-N [2-[2-[2-(2,3,4,5,6-pentafluorobenzoyl)oxyphenyl]propan-2-yl]phenyl] 2,3,4,5,6-pentafluorobenzoate Chemical compound C=1C=CC=C(OC(=O)C=2C(=C(F)C(F)=C(F)C=2F)F)C=1C(C)(C)C1=CC=CC=C1OC(=O)C1=C(F)C(F)=C(F)C(F)=C1F VEBSPLIVZXWXFB-UHFFFAOYSA-N 0.000 description 1

- KXKVLQRXCPHEJC-UHFFFAOYSA-N acetic acid trimethyl ester Natural products COC(C)=O KXKVLQRXCPHEJC-UHFFFAOYSA-N 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 239000005456 alcohol based solvent Substances 0.000 description 1

- 150000001338 aliphatic hydrocarbons Chemical class 0.000 description 1

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 125000005577 anthracene group Chemical group 0.000 description 1

- 125000006615 aromatic heterocyclic group Chemical group 0.000 description 1

- 238000007664 blowing Methods 0.000 description 1

- 239000002775 capsule Substances 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 239000003575 carbonaceous material Substances 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- 230000021615 conjugation Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- MTHSVFCYNBDYFN-UHFFFAOYSA-N diethylene glycol Chemical compound OCCOCCO MTHSVFCYNBDYFN-UHFFFAOYSA-N 0.000 description 1

- XXJWXESWEXIICW-UHFFFAOYSA-N diethylene glycol monoethyl ether Chemical compound CCOCCOCCO XXJWXESWEXIICW-UHFFFAOYSA-N 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000003618 dip coating Methods 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 239000003480 eluent Substances 0.000 description 1

- 238000010828 elution Methods 0.000 description 1

- 239000003759 ester based solvent Substances 0.000 description 1

- 239000004210 ether based solvent Substances 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 235000019253 formic acid Nutrition 0.000 description 1

- WBJINCZRORDGAQ-UHFFFAOYSA-N formic acid ethyl ester Natural products CCOC=O WBJINCZRORDGAQ-UHFFFAOYSA-N 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 235000011187 glycerol Nutrition 0.000 description 1

- 150000002366 halogen compounds Chemical class 0.000 description 1

- QSQIGGCOCHABAP-UHFFFAOYSA-N hexacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC6=CC=CC=C6C=C5C=C4C=C3C=C21 QSQIGGCOCHABAP-UHFFFAOYSA-N 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 239000005453 ketone based solvent Substances 0.000 description 1

- 238000001182 laser chemical vapour deposition Methods 0.000 description 1

- 150000007527 lewis bases Chemical class 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- UZKWTJUDCOPSNM-UHFFFAOYSA-N methoxybenzene Substances CCCCOC=C UZKWTJUDCOPSNM-UHFFFAOYSA-N 0.000 description 1

- 238000000813 microcontact printing Methods 0.000 description 1

- 239000012046 mixed solvent Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 125000001624 naphthyl group Chemical group 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000002825 nitriles Chemical class 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- YNPNZTXNASCQKK-UHFFFAOYSA-N phenanthrene Chemical group C1=CC=C2C3=CC=CC=C3C=CC2=C1 YNPNZTXNASCQKK-UHFFFAOYSA-N 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 1

- 229920000548 poly(silane) polymer Polymers 0.000 description 1

- 229920001197 polyacetylene Polymers 0.000 description 1

- 229920002312 polyamide-imide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920001083 polybutene Polymers 0.000 description 1

- 229920001088 polycarbazole Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920002098 polyfluorene Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- FVSKHRXBFJPNKK-UHFFFAOYSA-N propionitrile Chemical compound CCC#N FVSKHRXBFJPNKK-UHFFFAOYSA-N 0.000 description 1

- UMJSCPRVCHMLSP-UHFFFAOYSA-N pyridine Natural products COC1=CC=CN=C1 UMJSCPRVCHMLSP-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- HXJUTPCZVOIRIF-UHFFFAOYSA-N sulfolane Chemical compound O=S1(=O)CCCC1 HXJUTPCZVOIRIF-UHFFFAOYSA-N 0.000 description 1

- 125000000472 sulfonyl group Chemical group *S(*)(=O)=O 0.000 description 1

- 150000003464 sulfur compounds Chemical class 0.000 description 1

- IFLREYGFSNHWGE-UHFFFAOYSA-N tetracene Chemical compound C1=CC=CC2=CC3=CC4=CC=CC=C4C=C3C=C21 IFLREYGFSNHWGE-UHFFFAOYSA-N 0.000 description 1

- UOHMMEJUHBCKEE-UHFFFAOYSA-N tetramethylbenzene Natural products CC1=CC=C(C)C(C)=C1C UOHMMEJUHBCKEE-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 238000007751 thermal spraying Methods 0.000 description 1

- 229930192474 thiophene Natural products 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- YNJBWRMUSHSURL-UHFFFAOYSA-N trichloroacetic acid Chemical compound OC(=O)C(Cl)(Cl)Cl YNJBWRMUSHSURL-UHFFFAOYSA-N 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 238000001291 vacuum drying Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

Images

Landscapes

- Thin Film Transistor (AREA)

- Formation Of Insulating Films (AREA)

Abstract

Description

この薄膜トランジスタは、薄型軽量化に適すること、可撓性を有すること、材料コストが安価であること等の長所を有しており、フレキシブルディスプレイ等のスイッチング素子として期待されている。

しかしながら、ゲート絶縁層の形成に気相成膜法を用いるため、ゲート絶縁層の形成に手間と時間とを要するという問題や、ゲート絶縁層の形成時に有機半導体層に変質、劣化を生じさせてしまうおそれがある。

ところが、これらの樹脂は、極性を有しているため、吸湿性が高い。かかる薄膜トランジスタを大気中で使用した場合、ゲート絶縁層が吸湿し、ゲート絶縁体層中の水分が上昇すると、イオン電流が流れるようになり、しきい電圧(Vth)のシフト、ゲートリーク電流の上昇、絶縁破壊等が生じ易くなるという問題がある。

本発明の有機半導体装置は、ソース電極と、ドレイン電極と、ゲート電極と、該ゲート電極に対して前記ソース電極および前記ドレイン電極を絶縁するゲート絶縁層と、該ゲート絶縁層に接触して設けられた有機半導体層と、該有機半導体層の前記ゲート絶縁層と反対側に接触して設けられた第2の絶縁層とを有し、前記ゲート絶縁層および前記第2の絶縁層の少なくとも一方に、下記一般式(1)、または(2)で表される繰り返し単位を含む絶縁性高分子を含むことを特徴とする。

特に、ゲート絶縁層の誘電率が上記範囲内である場合には、十分な絶縁性を発揮しつつ、有機半導体装置の動作電圧を低くすることができる。

本発明の有機半導体装置では、前記絶縁性高分子において、R1およびR2は、同一または異なって下記化2で表される一般式(3−1)〜(3−13)であることが好ましい。

これにより、絶縁性高分子は、さらに高い絶縁性を示すようになる。

本発明の有機半導体装置では、前記有機半導体装置は、基板を有し、前記ソース電極および前記ドレイン電極が前記ゲート電極より前記基板側に位置するトップゲート型構造であり、少なくとも前記ゲート絶縁層に前記絶縁性高分子を主材料として構成したことが好ましい。

前記絶縁性高分子を主材料としてゲート絶縁層を構成することにより、トップゲート型構造の有機半導体装置において、ゲート絶縁層を液相プロセスにより形成する場合であっても、有機半導体層が変質、劣化するのを好適に防止することができる。

前記第2の絶縁層を形成する第1の工程と、

前記第2の絶縁層上に、前記ソース電極および前記ドレイン電極を互いに離間して形成する第2の工程と、

前記ソース電極および前記ドレイン電極とに接触するように、前記有機半導体層を形成する第3の工程と、

前記ソース電極、前記ドレイン電極および前記有機半導体層を覆うように、前記ゲート絶縁層を形成する第4の工程と、

前記ゲート絶縁層上に、前記ソース電極と前記ドレイン電極との間の領域に対応するように前記ゲート電極を形成する第5の工程とを有し、

前記第1の工程および前記第4の工程の少なくとも一方は、下記一般式(1)、または(2)で表される繰り返し単位を含む絶縁性高分子を溶媒に溶解した溶液を用いた液相プロセスにより行われるものであることを特徴とする。

液相プロセスによれば、低温での層形成が可能なため、高温の熱履歴を経ることによる有機半導体装置の特性の低下を防止することができる。その結果、吸湿性が低く、特性が経時的に劣化し難い有機半導体装置が得られる。

前記絶縁性高分子は、ケトン系溶媒やエステル系溶媒のように比較的極性の高い溶媒に良好に溶解させることができる。また、これらの溶媒は、有機半導体層を溶解または膨潤し難い溶媒であるため、特にトップゲート型構造の有機半導体装置において、ゲート絶縁層を液相プロセスにより形成する場合であっても、有機半導体層が変質、劣化するのを好適に防止することができる。

かかる液相プロセスにおいて、例えば、電極形成用材料をインクジェト法により供給することにより、寸法精度の高いゲート電極を簡便に形成することができる。

本発明の電子デバイスは、本発明の有機半導体装置を備えることを特徴とする。

これにより、信頼性の高い電子デバイスが得られる。

これにより、信頼性の高い電子機器が得られる。

本発明の絶縁層形成組成物は、下記一般式(1)、または(2)で表される繰り返し単位を含む絶縁性高分子を含むことを特徴とする。

これにより、吸湿性が低く特性が劣化し難い有機半導体装置を得られるだけでなく、前記絶縁性高分子を含む溶液に対する溶媒の選択範囲を大幅に拡げることができる。例えば、液相プロセスに最適な溶液を作製することが可能になり、容易にかつ均一性の高い十分な膜強度を有するゲート絶縁層および/または第2の絶縁層を形成することができる。

なお、以下では、本発明の有機半導体装置をアクティブマトリクス装置に適用した場合を一例に説明する。

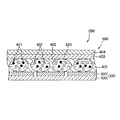

図1は、本発明の有機半導体装置を適用したアクティブマトリクス装置の構成を示すブロック図、図2は、図1に示すアクティブマトリクス装置が備える有機薄膜トランジスタの構成を示す図(縦断面図および平面図)、図3および図4は、それぞれ、図2に示す有機薄膜トランジスタの製造方法を説明するための図(縦断面図)である。なお、以下の説明では、図2〜図4中上側を「上」、下側を「下」として説明する。

そして、薄膜トランジスタ1が有するゲート電極50は走査線302に、ソース電極20aはデータ線301に、ドレイン電極20bは後述する画素電極(個別電極)303に、それぞれ接続されている。

具体的には、図2(a)に示すように、この薄膜トランジスタ1は、基板500上に設けられたバッファ層(第2の絶縁層)60と、バッファ層60上に、互いに分離して設けられたソース電極20aおよびドレイン電極20bと、ソース電極20aおよびドレイン電極20bに接触して設けられた有機半導体層30と、有機半導体層30とゲート電極50との間に位置するゲート絶縁層40と、これらの各層を覆うように設けられた保護層70とを有している。

以下、各部の構成について、順次説明する。

基板500は、薄膜トランジスタ1(アクティブマトリクス装置300)を構成する各層(各部)を支持するものである。

薄膜トランジスタ1に可撓性を付与する場合には、基板500には、プラスチック基板、あるいは、薄い(比較的膜厚の小さい)金属基板が選択される。

このバッファ層60は、後述する有機半導体層30に水分が浸入するのを防止する機能や、基板500がガラス材料等で構成される場合、基板500から有機半導体層30にイオン等が拡散するのを防止する機能を有する。

このような有機半導体層30に接触するバッファ層60、および、後述するゲート絶縁層40の少なくとも一方(好ましくは双方)が、後述する一般式(1)、または(2)で表される絶縁性高分子を主材料として構成されている。この絶縁性高分子については、後に詳述する。

バッファ層60上には、所定の間隔離間して、ソース電極20aおよびドレイン電極20bが設けられている。

ソース電極20aおよびドレイン電極20bの構成材料としては、例えば、Au、Ag、Cu、Pt、Ni、Cr、Ti、Ta、Alまたはこれらを含む合金のような金属材料等が挙げられ、これらのうちの1種または2種以上を組み合わせて用いることができる。

ソース電極20aとドレイン電極20bとの距離、すなわち、図2(b)に示すチャネル長Lは、2〜30μm程度であるのが好ましく、2〜20μm程度であるのがより好ましい。このような範囲にチャネル長Lの値を設定することにより、薄膜トランジスタ1の特性の向上(特に、ON電流値の上昇)を図ることができる。

ソース電極20aおよびドレイン電極20bに接触するように、有機半導体層30が設けられている。

ここで、液相プロセスとは、成膜したい材料を溶解もしくは分散させることで液状体とし、この液状体を用いてスピンコート法、ディップ法、あるいは液滴吐出法(インクジェット法)等により薄膜を作製する方法である。

この有機半導体層30の平均厚さは、特に限定されないが、0.1〜1000nm程度であるのが好ましく、1〜500nm程度であるのがより好ましく、1〜100nm程度であるのがさらに好ましい。

有機半導体層30と接触し、かつ、有機半導体層30、ソース電極20aおよびドレイン電極20bを覆うように、ゲート絶縁層40が設けられている。

このゲート絶縁層40は、ソース電極20aおよびドレイン電極20bに対して、後述するゲート電極50を絶縁するものである。

ゲート絶縁層40の厚さを前記範囲とすることにより、ソース電極20aおよびドレイン電極20bとゲート電極50とを確実に絶縁しつつ、薄膜トランジスタ1の動作電圧を低くすることができる。後述するように、ゲート絶縁層を構成する絶縁性高分子(後述する一般式(1)、または(2)で表わされる高分子(絶縁層形成組成物))は、液相プロセスに適した高分子であるため、液相プロセスを用いて、比較的容易かつ高精度に、上記範囲内に属するような比較的薄い層を形成することができる。

ゲート絶縁層40上の所定の位置、すなわち、ソース電極20aとドレイン電極20bとの間の領域に対応する位置には、有機半導体層30に電界をかけるゲート電極50が設けられている。

また、以上のような各層を覆うようにして、保護層70が設けられている。

この保護層70は、有機半導体層30に水分が浸入するのを防止する機能や、ゲート電極50に異物が接触して、隣接する薄膜トランジスタ1同士がショートするのを防止する機能を有する。

なお、保護層70は、必要に応じて設けるようにすればよく、省略することもできる。

−薄膜トランジスタ1の作動−

このような薄膜トランジスタ1では、ソース電極20aおよびドレイン電極20bの間に電圧を印加した状態で、ゲート電極50にゲート電圧を印加すると、有機半導体層30のゲート絶縁層40との界面付近にチャネルが形成され、チャネル領域をキャリア(正孔)が移動することで、ソース電極20aおよびドレイン電極20bの間に電流が流れる。

一方、ゲート電極50に電圧が印加されているON状態では、有機半導体層30のゲート絶縁層40に面した部分に電荷が誘起され、チャネル(キャリアの流路)が形成される。この状態でソース電極20aおよびドレイン電極20bの間に電圧を印加すると、チャネル領域を通って電流が流れる。

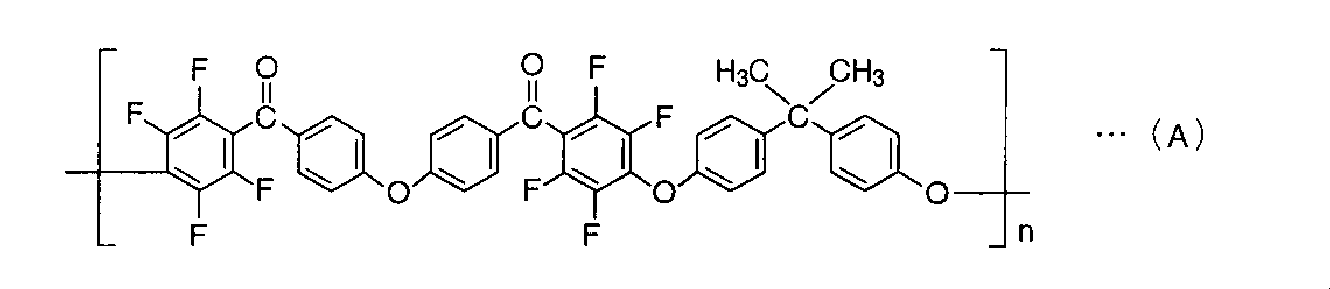

次に、下記一般式(1)、または(2)で表される絶縁性高分子について説明する。

したがって、かかる絶縁性高分子を主材料として、ゲート絶縁膜40やバッファ層60を構成することにより、吸湿による薄膜トランジスタ1の特性の劣化、特に、イオン電流の発生に伴うしきい電圧(Vth)のシフト(変動)、ゲートリーク電流の上昇、絶縁破壊の発生等を防止することができる。

これに対して、前記絶縁性高分子では、フッ素原子がベンゼン(共役系の構造)に結合しているため、絶縁性高分子の分子構造内において、電子がフッ素原子側に偏在しており、そのため、隣接する分子から電子を引き抜く力、すなわち、有機半導体層30からの電子吸引力が弱い。

また、この絶縁性高分子は、フッ素化された芳香族環を含むことにより、絶縁性高分子同士の凝集が防止され、各種溶媒に対して高い溶解性を示す。このため、液相プロセスを用いて、ゲート絶縁膜40やバッファ層60を形成することが可能となり、薄膜トランジスタ1の製造コストの削減を図ることができる。また、液相プロセスによれば、低温での層形成が可能なため、高温の熱履歴を経ることによる薄膜トランジスタ1の特性の低下を防止することができる。このようなゲート絶縁膜40やバッファ層60を形成する方法については、後に詳述する。

次いで、式(1)、または(2)に示す絶縁性高分子について説明する。

カルボニル基(またはエステル基)を含む前記絶縁性高分子においては、カルボニル基(またはエステル基)中の酸素原子が非共有電子対の存在により弱いルイス塩基としての性質を示すため、仮に有機半導体層30中に正孔が生起した場合でも、この正孔を捕捉することができる。

また、カルボニル基、またはエステル基を含むことにより、前記絶縁性高分子材料を、ケトン系溶媒やエステル系溶媒のように比較的極性の高い溶媒に溶解させることができる。これらの溶媒は、有機半導体層30を溶解または膨潤し難い溶媒であるため、本実施形態のように、トップゲート型構造の薄膜トランジスタ1において、ゲート絶縁層40を液相プロセスにより形成する場合であっても、有機半導体層30が変質、劣化するのを好適に防止することができる。

このような絶縁性高分子の重量平均分子量としては、特に限定されないが、5千〜50万程度であるのが好ましく、2万〜19万程度であることがより好ましい。重量平均分子量が小さ過ぎると、二価の連結基R1、R2の種類によっては、成膜後において、十分な膜強度等が得られないおそれがあり、一方、重量平均分子量が大き過ぎると、溶媒へ溶解した際の溶液の粘度が高くなり過ぎ、液相プロセスによる成膜が困難となるおそれがある。すなわち、絶縁性高分子の重量平均分子量を上記範囲とすることにより、液相プロセスを用いて、比較的容易に、十分な膜強度を有するゲート絶縁層40およびバッファ層60を形成することができる。

まず、式(1)、または(2)中のYについて説明する。

Yは、前述したように、酸素原子または硫黄原子であるが、酸素原子であるのがより好ましい。これにより、絶縁性高分子をより極性の高い溶媒に溶解することが可能となるとともに、絶縁性高分子をゲート絶縁層40に用いる場合には、酸素原子が有機半導体層40中に生起した正孔を捕捉して、有機半導体層40の導電化をより確実に防止することができるようになる。

R1およびR2としては、それぞれ、特に限定されないが、芳香族環を少なくとも1つ含むものが好ましい。芳香族環は、π電子を有するため、他の分子を引き付け易い性質を有する。そのため、前記絶縁性高分子に含まれる芳香族環により、この部分のポリマー凝集力が増す為、膜にした場合の機械的強度が増す。

このようなR1およびR2としては、それぞれ、下記化6に示されるものが好適である。なお、R1およびR2は、互いに同じ基であってもよいし、異なる基であってもよい。

さらに、R1およびR2としては、それぞれ、極性基を有していないものであることが好ましい。例えば(3−1)、(3−2)、(3−4)、(3−10)である。これにより、前記絶縁性高分子の極性を比較的低くすることができ、特に、ゲート絶縁層40の構成材料として適したものとなる。極性基としては、例えば、カルボニル基(>C=O)、スルホニル基(>S(=O)2)、−CF3、−N(Bu)2等が挙げられる。

次に、アクティブマトリクス装置300の製造方法について説明する。

なお、以下では、薄膜トランジスタ1の製造方法(本願発明の製造方法)を中心に説明する。

[1] バッファ層形成工程(図3(a)参照)

まず、基板500を用意し、基板500上にバッファ層60を形成する。

バッファ層60は、例えば、前述した絶縁性高分子を溶媒に溶解した溶液を、基板500上に供給した後、脱溶媒する方法(液相プロセス)により形成することができる。

脱溶媒の方法としては、例えば、自然乾燥、真空乾燥、加熱による乾燥、ガス(例えば不活性ガス等)を吹付けることによる乾燥等の方法を用いることができる。

次に、バッファ層60上に、ソース電極20aおよびドレイン電極20bを所定距離離間して形成する。

まず、バッファ層60上に金属膜(金属層)を形成する。これは、例えば、プラズマCVD、熱CVD、レーザーCVDのような化学蒸着法(CVD)、真空蒸着、スパッタリング(低温スパッタリング)、イオンプレーティング等の乾式メッキ法、電解メッキ、浸漬メッキ、無電解メッキ等の湿式メッキ法、溶射法、ゾル・ゲル法、MOD法、金属箔の接合等により形成することができる。

なお、ソース電極20aおよびドレイン電極20bは、例えば、導電性粒子を含む導電性材料をバッファ層60上に供給して液状被膜を形成した後、必要に応じて、この液状被膜に対して後処理(例えば加熱、赤外線の照射、超音波の付与等)を施すことにより形成することもできる。

なお、この導電性材料を供給する方法には、前記工程[1]で挙げた方法を用いることができる。

また、このとき、データ線301および画素電極303も形成する。

次に、ソース電極20aおよびドレイン電極20bとに接触するように、有機半導体層30を形成する。

有機半導体層30は、例えば、有機半導体材料またはその前駆体を含む溶液を、バッファ層60上の、ソース電極20aとドレイン電極20bとの間の領域を含む所定の領域に供給して液状被膜を形成した後、必要に応じて、この液状被膜に対して後処理(例えば加熱、赤外線の照射、超音波の付与等)を施すことにより形成することができる。

なお、この溶液を供給する方法には、前記工程[1]で挙げた方法を用いることができる。

次に、ソース電極20a、ドレイン電極20bおよび有機半導体層30を覆うように、ゲート絶縁層40を形成する。

ゲート絶縁層40は、前記バッファ層60と同様にして、液相プロセスにより形成することができる。

液相プロセスを用いることにより、有機半導体層30に不要な熱が加わるのを防止して、有機半導体層30の特性、ひいては、薄膜トランジスタ1の特性の低下を好適に防止することができる。

なお、前記一般式(I)で表される絶縁性高分子は、フッ素化されたベンゼン環およびカルボニル基を有することから、ケトン系溶媒やエステル系溶媒のような比較的極性の高い溶にも十分に溶解する。

次に、ゲート絶縁層40上に、ソース電極20aとドレイン電極20bとの間の領域に対応するように、ゲート電極50を形成する。

ゲート電極50は、前記ソース電極20aおよびドレイン電極20bと同様にして形成することができる。

かかる液相プロセスにおいて、例えば、電極形成用材料を、ゲート絶縁層40上にインクジェト法により供給することにより、寸法精度の高いゲート電極50を簡便に形成することができる。

ここで、これらの電極形成用材料は、水系分散媒を用いて調製されるが、水系分散媒中には、不純物としてまたは金属粒子から溶出する等して各種イオンが溶存することが多い。

また、このとき、走査線302を形成する。

なお、本実施形態では、走査線302は、ゲート電極50とは別途形成されるが、隣接する薄膜トランジスタ1のゲート電極50を連続して形成することにより走査線302としてもよい。

次に、ゲート絶縁層40上に、ゲート電極50を覆うように保護層70を形成する。

保護層70は、前記有機半導体層30と同様にして形成することができる。

<電子デバイス>

次に、本発明の電子デバイスとして、前述したようなアクティブマトリクス装置が組み込まれた電気泳動表示装置を一例に説明する。

図5は、電気泳動表示装置の実施形態を示す縦断面図である。なお、以下の説明では、図5中上側を「上」、下側を「下」として説明する。

この電気泳動表示部400は、透明電極(共通電極)403を備える透明基板404と、バインダ材405により透明電極403に固定されたマイクロカプセル402とで構成されている。

各カプセル402内には、それぞれ、特性の異なる複数種の電気泳動粒子、本実施形態では、電荷および色(色相)の異なる2種の電気泳動粒子421、422を含む電気泳動分散液420が封入されている。

これにより、かかる薄膜トランジスタ1に接続されているデータ線301と画素電極303とは、実質的に導通する。このとき、データ線301に所望のデータ(電圧)を供給した状態であれば、このデータ(電圧)は画素電極303に供給される。

一方、この状態から、走査線302への選択信号(選択電圧)の供給を停止すると、薄膜トランジスタ1はOFFとなり、かかる薄膜トランジスタ1に接続されているデータ線301と画素電極303とは非導通状態となる。

特に、本実施形態の電気泳動表示装置200では、電気泳動粒子421、422の色を異ならせていることにより、多階調の画像を表示することが可能となっている。

また、本実施形態の電気泳動表示装置200は、アクティブマトリクス装置300を有することにより、特定の走査線302に接続された薄膜トランジスタ1を選択的にON/OFFすることができるので、クロストークの問題が生じにくく、また、回路動作の高速化が可能であることから、高い品質の画像(情報)を得ることができる。

なお、前述したような薄膜トランジスタ1を備えるアクティブマトリクス装置が組み込まれた表示装置は、このような電気泳動表示装置200への適用に限定されるものではなく、例えば、液晶表示装置等に適用することもできる。

このような電気泳動表示装置200は、各種電子機器に組み込むことができる。以下、電気泳動表示装置200を備える本発明の電子機器について説明する。

<<電子ペーパー>>

まず、本発明の電子機器を電子ペーパーに適用した場合の実施形態について説明する。

図6は、本発明の電子機器を電子ペーパーに適用した場合の実施形態を示す斜視図である。

この図に示す電子ペーパー600は、紙と同様の質感および柔軟性を有するリライタブルシートで構成される本体601と、表示ユニット602とを備えている。

このような電子ペーパー600では、表示ユニット602が、前述したような電気泳動表示装置200で構成されている。

次に、本発明の電子機器をディスプレイに適用した場合の実施形態について説明する。

図7は、本発明の電子機器をディスプレイに適用した場合の実施形態を示す図であり、(a)は断面図、(b)は平面図である。

この図に示すディスプレイ800は、本体部801と、この本体部801に対して着脱自在に設けられた電子ペーパー600とを備えている。なお、この電子ペーパー600は、前述したような構成、すなわち、図6に示す構成と同様のものである。

また、電子ペーパー600の挿入方向先端部(図中、左側)には、端子部806が設けられており、本体部801の内部には、電子ペーパー600を本体部801に設置した状態で端子部806が接続されるソケット807が設けられている。このソケット807には、コントローラー808と操作部809とが電気的に接続されている。

また、このようなディスプレイ800では、電子ペーパー600が、前述したような電気泳動表示装置200で構成されている。

なお、本発明の電子機器は、以上のようなものへの適用に限定されず、例えば、テレビ、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、電子新聞、ワードプロセッサ、パーソナルコンピュータ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等を挙げることができ、これらの各種電子機器の表示部に、電気泳動表示装置200を適用することが可能である。

前記実施形態では、薄膜トランジスタ1がトップゲート型構造である場合を代表に説明したが、薄膜トランジスタ1は、ゲート電極50がソース電極20aおよびドレイン電極20bより基板500側に位置するボトムゲート型構造であってもよい。

前記高分子(A)は、次のようにして得た。

まず、ビス(2、3、4、5、6−ペンタフルオロベンゾイル)ジフェニルエーテル(以下BPDEと略する)15.45g(27.7mmol)、ビスフェノールA(以下BisAと略する)6.16g(27mmol)、炭酸カリウム 11.17g(80.8mmol)、モレキュラーシーブ6.8g、メチルエチルケトン81gを加えて、79℃で7時間反応した。その後、酢酸ブチルで希釈した後に濾過を行ない、そのポリマー溶液を脱イオン水で分液洗浄し、洗浄したポリマー溶液を濃縮することで高分子(A)を得た。

まず、BPDE16.75g、ビスフェノールフルオレン10.50g、炭酸カリウム4.55g、モレキュラーシーブ5.4g、ジメチルアセトアミド90gを加えて、60℃で8時間反応した。その後、アセトンで希釈化したのちに濾過を行い、それによって得られたポリマー溶液を脱イオン水に混合して再沈殿した。再沈殿により得られた固体を濾過乾燥し、再度アセトンに溶解して脱イオン水で再沈殿工程を2回繰り返すことにより高分子(B)を得た。

まず、2、2−ビス(2、3、4、5、6−ペンタフルオロベンゾイルオキシフェニル)プロパン(以下エステルBisAと略する)15.0g、BisA5.56g、炭酸カリウム10.09g、モレキュラーシーブ7g、MEK110gを加えて79℃で6.5時間反応した。その後、酢酸ブチルで希釈した後に濾過を行い、それにより得られたポリマー溶液を脱イオン水で分液洗浄した。洗浄して得られたポリマー溶液を濃縮し、メタノールに混合して再沈殿を行った。再沈殿により得られた固体を濾過乾燥し高分子(C)を得た。

まず、2、2−ビス(2、3、4、5、6−ペンタフルオロベンゾイルオキシ)ジフェニルエーテル(以下エステルDEと略す)12.1g、BisA4.56g、炭酸カリウム5.53g、モレキュラーシーブ7g、メチルエチルケトン90gを加えて、79℃で7.5時間反応した。その後、酢酸ブチルで希釈した後に濾過を行ない、そのポリマー溶液を脱イオン水で分液洗浄し、洗浄したポリマー溶液を濃縮することで高分子(D)を得た。

まず、BPDE11.17g、フェノールフタレイン6.37g、炭酸カリウム8.29g、モレキュラーシーブ5.0g、MEK85gを加えて79℃で6.5時間反応した。その後、酢酸ブチルで希釈化した後に濾過を行い、それにより得られたポリマー溶液を脱イオン水で分液洗浄した。洗浄して得られたポリマー溶液を濃縮し、メタノールに混合して再沈殿を行った。再沈殿により得られた固体を濾過し乾燥することにより高分子(E)を得た。

まず、BPDE16.75g、2、2−ジヒドロキシフェニルヘキサフルオロプロパン(以下、BisAFと略する)10.08g、炭酸カリウム4.55g、モレキュラーシーブ5.4g、ジメチルアセトアミド90gを加えて、60℃で6時間反応した。その後、アセトンで希釈した後に濾過を行い、これにより得られたポリマー溶液を脱イオン水に混合して再沈殿を行った。再沈殿により得られた固体を濾過し乾燥し、再度アセトン溶解して脱イオン水で再沈殿工程を2回繰り返し行った。これにより得られた固体を濾過し乾燥することにとり高分子(F)を得た。

まず、BPDE16.75g、2−ジブチルアミノ−4、6−ジメルカプト−s−トリアジン(三協化成株式会社製ジスネットDB)8.17g、炭酸カリウム4.35、モレキュラーシーブ5.4g、ジメチルアセトアミド60gを加えて、60℃で2時間反応した。その後、アセトンで希釈した後に濾過を行い、それにより得られたポリマー溶液を脱イオン水に混合して再沈殿を行った。得られた固体を濾過、乾燥し、再度アセトンに溶解して脱イオン水で再沈殿工程を行った。これにより得られた固体を濾過して乾燥することにより、高分子(G)を得た。

BPDE16.75g、BisZ8.05g、炭酸カリウム4.56g、ジメチルアセトアミド75gを加えて、80℃で6時間反応した。その後、アセトンで希釈した後に濾過を行い、それにより得られたポリマー溶液を脱イオン水に混合して再沈殿を行った。酢酸ブチルに溶解して、ポリマー溶液を脱イオン水で分液洗浄し、洗浄したポリマー溶液を濃縮することで高分子(H)を得た。

BPDE15.07g、1,3−ビス[2−(4−ヒドロキシフェニル)−2−プロピル]ベンゼン9.35g、炭酸カリウム4.10g、ジメチルアセトアミド65gを加えて、65℃で5.5時間反応した。その後、アセトンで希釈した後に濾過を行い、それにより得られたポリマー溶液を脱イオン水に混合して再沈殿を行った。得られた固体を濾過、乾燥し、再度アセトンに溶解して脱イオン水で再度沈殿を行った。これにより得られた固体を濾過、乾燥し、高分子(I)を得た。

以下に示すようにして、実施例1〜13および比較例1〜10の薄膜トランジスタを、それぞれ、200個ずつ製造した。

(実施例1)

まず、ガラス基板(NECコーニング社製、「OA10」)を用意し、水を用いて洗浄した後、乾燥した。

次に、ソース電極およびドレイン電極を形成したガラス基板上に、1wt%となるように調製したフルオレン−ビチオフェン共重合体の誘導体であるF8T2(ADS社製)溶液のトルエン溶液を、スピンコート法により塗布した後、60℃×10分間で乾燥した。これにより、平均厚さ50nmの有機半導体層を得た。

次に、ゲート絶縁層上の、ソース電極とドレイン電極との間の領域に対応する領域に、Ag粒子の水分散液を、インクジェット法により塗布した後、80℃×10分間で乾燥した。これにより、平均厚さ100nm、平均幅30μmのゲート電極を得た。なお、以下の表1中、ゲート電極の形成に、Ag粒子の水分散液を用いた場合を「Ag−IJ」と略して示す。なお、窒素中でのVthと大気中でのVthとの差(ΔVth=Vth(air)−Vth(N2))が−2[V]であった。

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(B)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、ΔVth=−5[V]であった。

(実施例3)

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(C)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、ΔVth=−3[V]であった。

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(D)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、ΔVth=−3[V]であった。

(実施例5)

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(E)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(F)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

(実施例7)

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(G)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(H)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

(実施例9)

ゲート絶縁層を形成する際に、高分子(A)に代えて、高分子(I)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

ゲート電極を、金を蒸着することにより形成した以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、以下の表1中、ゲート電極の形成に、金の蒸着を用いた場合を「Au」と略して示す。

(実施例11)

ゲート電極を形成する際に、Ag粒子の水分散液に代えて、ポリ(3,4−エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)(PEDOT/PSS)の水分散液を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、以下の表1中、ゲート電極の形成に、ポリ(3,4−エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)の水分散液を用いた場合を「PEDOT/PSS」と略して示す。

有機半導体層を形成する際に、F8T2に代えて、MEH−PPVを用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

(実施例13)

まず、ガラス基板(NECコーニング社製、「OA10」)を用意し、水を用いて洗浄した後、乾燥した。

次に、0.7wt%となるように調製した高分子(A)の酢酸ブチル溶液を、スピンコート法により塗布した後、60℃×10分間で乾燥した。これにより、平均厚さ50nmのバッファ層を得た。

次に、前記バッファ層上にソース電極およびドレイン電極の形状に対応するように、マスク蒸着法を用いて金の薄膜を形成した。これにより、平均厚さ100nm、チャネル長50μm/チャネル幅1mmの金のソース電極およびドレイン電極を得た。

次に、ソース電極およびドレイン電極を形成した前記基板上に、1wt%となるように調製したフルオレン−ビチオフェン共重合体の誘導体であるF8T2(ADS社製)溶液のトルエン溶液をスピンコート法により塗布した後、60℃×10分間で乾燥した。これにより平均厚さ50nmの有機半導体層を得た。

次に、有機半導体層、ソース電極およびドレイン電極を覆うように、5wt%となるように調製した高分子(A)の酢酸ブチル溶液を、スピンコート法により塗布した後、60℃×10分間で乾燥した。これにより、平均厚さ500nmのゲート絶縁層を得た。

次に、ゲート絶縁層上の、ソース電極とドレイン電極との間に対応する領域に、Ag粒子の水分散液を、インクジェット法により塗布した後、80℃×10分間で乾燥した。これにより、平均厚さ100nm、平均幅70μmのゲート電極を得た。なお、以下の表1中、ゲート電極の形成に、Ag粒子の水分散液を用いた場合を「Ag−IJ」と略して示す。

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリメチルメタクリレート(PMMA)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、ΔVth=−15[V]であった。

(比較例2)

ゲート絶縁層を形成する際に、高分子(A)に代えて、フッ素系ポリマー(旭硝子製、「サイトップ」)を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。なお、溶媒には、フッ素系溶媒を用いた。

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリビニルアルコール(PVA)脂を用いた以外は、前記実施例1と同様にして薄膜トランジスタを製造した。

(比較例4)

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリメチルメタクリレート(PMMA)を用いた以外は、前記実施例10と同様にして薄膜トランジスタを製造した。

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリメチルメタクリレート(PMMA)を用いた以外は、前記実施例11と同様にして薄膜トランジスタを製造した。

(比較例6)

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリメチルメタクリレート(PMMA)を用いた以外は、前記実施例12と同様にして薄膜トランジスタを製造した。

(比較例7)

ゲート絶縁層を形成する際に、高分子(A)に代えて、フッ素系ポリマー(旭硝子製、「サイトップ」)を用いた以外は、前記実施例12と同様にして薄膜トランジスタを製造した。なお、溶媒には、フッ素系溶媒を用いた。

ゲート絶縁層を形成する際に、高分子(A)に代えて、ポリビニルアルコール(PVA)脂を用いた以外は、前記実施例12と同様にして薄膜トランジスタを製造した。

(比較例9)

まず、ガラス基板(NECコーニング社製、「OA10」)を用意し、水を用いて洗浄した後、乾燥した。

次に、ガラス基板上にソース電極およびドレイン電極の形状に対応するように、マスク蒸着法を用いて金の薄膜を形成した。これにより、平均厚さ100nm、チャネル長50μm/チャネル幅1mmの金のソース電極およびドレイン電極を得た。

次に、ソース電極およびドレイン電極を形成したガラス基板上に、1wt%となるように調製したフルオレン−ビチオフェン共重合体の誘導体であるF8T2(ADS社製)溶液のトルエン溶液をスピンコート法により塗布した後、60℃×10分間で乾燥した。これにより平均厚さ50nmの有機半導体層を得た。

次に、有機半導体層、ソース電極およびドレイン電極を覆うように、5wt%となるように調製した高分子(A)の酢酸ブチル溶液を、スピンコート法により塗布した後、60℃×10分間で乾燥した。これにより、平均厚さ500nmのゲート絶縁層を得た。

次に、ゲート絶縁層上の、ソース電極とドレイン電極との間の領域に対応する領域に、Ag粒子の水分散液を、インクジェット法により塗布した後、80℃×10分間で乾燥した。これにより、平均厚さ100nm、平均幅70μmのゲート電極を得た。なお、以下の表1中、ゲート電極の形成に、Ag粒子の水分散液を用いた場合を「Ag−IJ」と略して示す。

(比較例10)

バッファ層を形成する際に、高分子(A)に変えてポリビニルアルコール(PVA)を用いた以外は、前記比較例9と同様にして薄膜トランジスタを形成した。

各実施例1〜13および各比較例1〜10で用いられる高分子(絶縁性高分子)について、それぞれ、誘電率、吸水率および分子量(Mw)を以下のようにして測定した。

≪誘電率≫

まず、銅板上に絶縁性高分子をスピンコーターを用いて塗布した後、80℃×10分の後、さらに150℃×30分乾燥し、厚さ10μmの薄膜(絶縁層)を得た。さらに、薄膜の表面(前記銅板と反対側の面)に金(Au)を蒸着して電極を形成し、これにより、絶縁層の両面に電極が形成された評価用サンプルを得た。このサンプルの誘電率をインピーダンスアナライザ(ヒューレットパッカード社製、HP−4292A)を用いて測定した。

絶縁性高分子を適当な溶媒(酢酸ブチル、シクロヘキサン、トルエンから好適に選択される溶媒)に溶解してなる溶液を、アプリケータを用いてPETフィルム(20cm×20cm、膜厚40μm)上に塗工し、80℃で120分間乾燥した(これにより、PETフィルム上に、絶縁性高分子を含む薄膜(フィルム)が形成されることとなる)。そして、PETフィルムを剥離した後、アフターヒートを行って、前記薄膜から溶媒を除去した。

このようにして得られた溶媒除去後の薄膜の重量を測定し、その後、当該薄膜を脱イオン水に浸漬して浸漬後の薄膜の重量を測定し、これら重量差(比)から吸水率を求めた。

高速GPC装置(東ソー(株)製、HLC−8220)を用いて、以下の条件で測定を行った。

展開溶媒:THF

カラム:TSK−gel GMHXL×2本

溶離液流量:1ml/min

カラム温度:40℃

実施例1〜13および比較例1〜10に用いられる絶縁性高分子について、以下のような試験を行った。

(4−1)薄膜形成性試験

絶縁性高分子を基板上にスピンコーターを用いて塗布し、乾燥させて厚さ約1μmの薄膜(フィルム)の形成を試みた。このような薄膜形成性試験を各絶縁性高分子について、それぞれ100回行った。薄膜形成性は、次のようにして評価した。

◎‥‥‥95〜100回、薄膜が形成された

○‥‥‥70〜94回、薄膜が形成された

△‥‥‥10〜69回、薄膜が形成された

×‥‥‥0〜9回、薄膜が形成された

絶縁性高分子1gに、各溶剤(酢酸ブチル、シクロヘキサン、トルエン)を9g添加して溶解性を確認した。なお、この試験は、25℃の各溶剤を用いて行った。溶解性は、次のようにして評価した。

◎‥‥‥溶解

○‥‥‥一部溶解

△‥‥‥膨潤

×‥‥‥不溶

また、実施例1〜13および比較例1〜10により得られた有機半導体素子について、以下のような試験を行った。なお、各試験は、200個の有機半導体を用いて行った。

窒素(N2)中または大気(air)中(25℃、60%RH)において伝達特性を測定した。そして、得られた結果から、それぞれの雰囲気での移動度、オン電流とオフ電流との比率であるオン/オフ比(on−off比)、しきい電圧(Vth)を算出した。

なお、表1には、移動度およびon−off比を示した。さらに、表1中には、大気中(25℃、60%RH)において絶縁破壊試験を5回以上行い、その最低値をVbdとして示した。また、表1中の各数値は、いずれも、200個の薄膜トランジスタで得られたデータの平均値である。

以上の各試験(4−1)〜(4−3)の結果を、表1に示す。

しかしながら、各実施例の薄膜トランジスタは、いずれも、その移動度の低下が、対応する比較例の薄膜トランジスタの移動度の低下に比較して小さいことが明らかとなった。

また、各実施例の薄膜トランジスタは、いずれも、そのΔVthが、対応する比較例の薄膜トランジスタのΔVthに比較して小さいことも明らかとなった。

さらに、大気中での絶縁破壊電圧は、各実施例の薄膜トランジスタの方が、全体的に各比較例の薄膜トランジスタより高くなる傾向を示し、この傾向は、ゲート電極をAg粒子やPEDOT/PSSで作製した場合に顕著であった。

Claims (11)

- 前記ゲート絶縁層および前記第2の絶縁層の少なくとも一方が、100KHzにおける誘電率が2.9以上である請求項1に記載の有機半導体装置。

- 前記絶縁性高分子において、R1およびR2は、同一または異なって一般式(3−1)、(3−4)、(3−10)である請求項1ないし3のいずれかに記載の有機半導体装置。

- 前記有機半導体装置は、基板を有し、前記ソース電極および前記ドレイン電極が前記ゲート電極より前記基板側に位置するトップゲート型構造であり、少なくとも前記ゲート絶縁層に前記絶縁性高分子を主材料として構成した請求項1ないし4のいずれかに記載の有機半導体装置。

- ソース電極と、ドレイン電極と、ゲート電極と、該ゲート電極に対して前記ソース電極および前記ドレイン電極を絶縁するゲート絶縁層と、該ゲート絶縁層に接触して設けられた有機半導体層と、該有機半導体層の前記ゲート絶縁層と反対側に接触して設けられた第2の絶縁層とを有する有機半導体装置の製造方法であって、

前記第2の絶縁層を形成する第1の工程と、

前記第2の絶縁層上に、前記ソース電極および前記ドレイン電極を互いに離間して形成する第2の工程と、

前記ソース電極および前記ドレイン電極とに接触するように、前記有機半導体層を形成する第3の工程と、

前記ソース電極、前記ドレイン電極および前記有機半導体層を覆うように、前記ゲート絶縁層を形成する第4の工程と、

前記ゲート絶縁層上に、前記ソース電極と前記ドレイン電極との間の領域に対応するように前記ゲート電極を形成する第5の工程とを有し、

前記第1の工程および前記第4の工程の少なくとも一方は、下記一般式(1)、または(2)で表される繰り返し単位を含む絶縁性高分子を溶媒に溶解した溶液を用いた液相プロセスにより行われるものであることを特徴とする有機半導体装置の製造方法。

- 前記溶媒がケトン系溶媒またはエステル系溶媒である請求項6に記載の有機半導体装置の製造方法。

- 前記ゲート電極を、導電性高分子または金属粒子を水系分散媒に分散してなる電極形成材料を用いて液相プロセスにより形成する請求項6または7に記載の有機半導体装置の製造方法。

- 請求項1ないし4のいずれかに記載の有機半導体装置を備えることを特徴とする電子デバイス。

- 請求項9に記載の電子デバイスを備えることを特徴とする電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008242937A JP5470788B2 (ja) | 2008-09-22 | 2008-09-22 | 有機半導体装置、有機半導体装置の製造方法、電子デバイスおよび電子機器 |

| PCT/JP2009/066400 WO2010032834A1 (ja) | 2008-09-22 | 2009-09-18 | 有機半導体装置、有機半導体装置の製造方法、電子デバイス、電子機器および絶縁層形成組成物 |

| US13/119,979 US8698142B2 (en) | 2008-09-22 | 2009-09-18 | Organic semiconductor element, method of manufacturing organic semiconductor element, electronic device, electronic equipment and insulating layer forming composition |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008242937A JP5470788B2 (ja) | 2008-09-22 | 2008-09-22 | 有機半導体装置、有機半導体装置の製造方法、電子デバイスおよび電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010074088A true JP2010074088A (ja) | 2010-04-02 |

| JP5470788B2 JP5470788B2 (ja) | 2014-04-16 |

Family

ID=42205575

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008242937A Active JP5470788B2 (ja) | 2008-09-22 | 2008-09-22 | 有機半導体装置、有機半導体装置の製造方法、電子デバイスおよび電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5470788B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012074616A (ja) * | 2010-09-29 | 2012-04-12 | Kaneka Corp | 有機半導体素子の製造方法および該製造方法によって得られる有機半導体素子 |

| JP2012244181A (ja) * | 2011-05-19 | 2012-12-10 | Samsung Electronics Co Ltd | 有機保護膜組成物およびこれから製造される有機保護膜を含む薄膜トランジスタ、並びに電子素子 |

| WO2022075382A1 (ja) * | 2020-10-07 | 2022-04-14 | 味の素株式会社 | エステル化合物及び樹脂組成物 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000068523A (ja) * | 1998-08-20 | 2000-03-03 | Lucent Technol Inc | 薄膜トランジスタ |

| JP2001049110A (ja) * | 1999-08-10 | 2001-02-20 | Nippon Shokubai Co Ltd | 低誘電性樹脂組成物 |

| JP2001177109A (ja) * | 1999-11-17 | 2001-06-29 | Lucent Technol Inc | 薄膜トランジスタ |

| JP2002060683A (ja) * | 2000-08-15 | 2002-02-26 | Nippon Shokubai Co Ltd | プリント基板用の表面コーティング剤 |

| JP2002064253A (ja) * | 2000-08-21 | 2002-02-28 | Nippon Shokubai Co Ltd | 多層配線基板 |

| JP2003183495A (ja) * | 2001-12-18 | 2003-07-03 | Nippon Shokubai Co Ltd | フッ素化合物含有樹脂組成物 |

| WO2005033209A1 (ja) * | 2003-09-30 | 2005-04-14 | Nippon Shokubai Co., Ltd. | 複合誘電体用樹脂組成物および複合誘電体、該誘電体を使用した電気回路基板 |

-

2008

- 2008-09-22 JP JP2008242937A patent/JP5470788B2/ja active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000068523A (ja) * | 1998-08-20 | 2000-03-03 | Lucent Technol Inc | 薄膜トランジスタ |

| JP2001049110A (ja) * | 1999-08-10 | 2001-02-20 | Nippon Shokubai Co Ltd | 低誘電性樹脂組成物 |

| JP2001177109A (ja) * | 1999-11-17 | 2001-06-29 | Lucent Technol Inc | 薄膜トランジスタ |

| JP2002060683A (ja) * | 2000-08-15 | 2002-02-26 | Nippon Shokubai Co Ltd | プリント基板用の表面コーティング剤 |

| JP2002064253A (ja) * | 2000-08-21 | 2002-02-28 | Nippon Shokubai Co Ltd | 多層配線基板 |

| JP2003183495A (ja) * | 2001-12-18 | 2003-07-03 | Nippon Shokubai Co Ltd | フッ素化合物含有樹脂組成物 |

| WO2005033209A1 (ja) * | 2003-09-30 | 2005-04-14 | Nippon Shokubai Co., Ltd. | 複合誘電体用樹脂組成物および複合誘電体、該誘電体を使用した電気回路基板 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012074616A (ja) * | 2010-09-29 | 2012-04-12 | Kaneka Corp | 有機半導体素子の製造方法および該製造方法によって得られる有機半導体素子 |

| JP2012244181A (ja) * | 2011-05-19 | 2012-12-10 | Samsung Electronics Co Ltd | 有機保護膜組成物およびこれから製造される有機保護膜を含む薄膜トランジスタ、並びに電子素子 |

| WO2022075382A1 (ja) * | 2020-10-07 | 2022-04-14 | 味の素株式会社 | エステル化合物及び樹脂組成物 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5470788B2 (ja) | 2014-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5630036B2 (ja) | 有機トランジスター、有機トランジスターの製造方法、電気光学装置および電子機器 | |

| KR100707775B1 (ko) | 박막 트랜지스터, 배선 기판, 표시 장치, 전자 기기 및 박막 트랜지스터의 제조 방법 | |

| US8188465B2 (en) | Method of manufacturing semiconductor device, semiconductor device, display device, and electronic instrument | |

| US7781760B2 (en) | Thin film transistor, electro-optical device, and electronic apparatus | |

| KR100766513B1 (ko) | 유기 반도체 장치의 제조 방법, 유기 반도체 장치, 전자장치 및 전자 기기 | |

| US8105870B2 (en) | Method for manufacturing semiconductor device, semiconductor device, semiconductor circuit, electro-optical device, and electronic apparatus | |

| JP4888043B2 (ja) | 有機半導体用組成物、トランジスタの製造方法、アクティブマトリクス装置の製造方法、電気光学装置の製造方法および電子機器の製造方法 | |

| JP5470788B2 (ja) | 有機半導体装置、有機半導体装置の製造方法、電子デバイスおよび電子機器 | |

| US8022396B2 (en) | Semiconductor device including an insulating layer resistant to a photolithography process, electronic device, and electronic equipment | |

| WO2010032834A1 (ja) | 有機半導体装置、有機半導体装置の製造方法、電子デバイス、電子機器および絶縁層形成組成物 | |

| JP5470787B2 (ja) | 有機半導体装置、有機半導体装置の製造方法、電子デバイスおよび電子機器 | |

| JP4729855B2 (ja) | 薄膜トランジスタ、薄膜トランジスタ回路、電子デバイスおよび電子機器 | |

| JP2007238724A (ja) | 液状材料、膜付き基板の製造方法、電気光学装置の製造方法および電子機器の製造方法 | |

| JP2005251809A (ja) | 薄膜トランジスタの製造方法、薄膜トランジスタ、薄膜トランジスタ回路、電子デバイスおよび電子機器 | |

| JP5103735B2 (ja) | 有機半導体層用組成物、薄膜トランジスタの製造方法、アクティブマトリクス装置の製造方法、電気光学装置の製造方法および電子機器の製造方法 | |

| JP2004281477A (ja) | 有機薄膜トランジスタおよびその製造方法 | |

| JP2007180231A (ja) | 有機半導体装置、電子デバイスおよび電子機器 | |

| JP2005146400A (ja) | 電極形成方法、薄膜トランジスタ、薄膜トランジスタ回路、電子デバイスおよび電子機器 | |

| JP2016039307A (ja) | 有機薄膜トランジスタの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110921 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130723 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130920 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20131105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20131105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140120 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5470788 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |