JP2010066743A - 液晶表示装置及びその駆動方法 - Google Patents

液晶表示装置及びその駆動方法 Download PDFInfo

- Publication number

- JP2010066743A JP2010066743A JP2008316324A JP2008316324A JP2010066743A JP 2010066743 A JP2010066743 A JP 2010066743A JP 2008316324 A JP2008316324 A JP 2008316324A JP 2008316324 A JP2008316324 A JP 2008316324A JP 2010066743 A JP2010066743 A JP 2010066743A

- Authority

- JP

- Japan

- Prior art keywords

- dimming

- liquid crystal

- divided

- display device

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims abstract description 83

- 238000000034 method Methods 0.000 title claims description 19

- 239000011159 matrix material Substances 0.000 claims abstract description 8

- 238000004458 analytical method Methods 0.000 claims description 32

- 235000019557 luminance Nutrition 0.000 description 50

- 238000010586 diagram Methods 0.000 description 15

- 230000008569 process Effects 0.000 description 10

- 239000000758 substrate Substances 0.000 description 8

- 239000010409 thin film Substances 0.000 description 4

- 230000004044 response Effects 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000010191 image analysis Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3406—Control of illumination source

- G09G3/342—Control of illumination source using several illumination sources separately controlled corresponding to different display panel areas, e.g. along one dimension such as lines

- G09G3/3426—Control of illumination source using several illumination sources separately controlled corresponding to different display panel areas, e.g. along one dimension such as lines the different display panel areas being distributed in two dimensions, e.g. matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0238—Improving the black level

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0626—Adjustment of display parameters for control of overall brightness

- G09G2320/064—Adjustment of display parameters for control of overall brightness by time modulation of the brightness of the illumination source

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0626—Adjustment of display parameters for control of overall brightness

- G09G2320/0646—Modulation of illumination source brightness and image signal correlated to each other

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/16—Calculation or use of calculated indices related to luminance levels in display data

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

Abstract

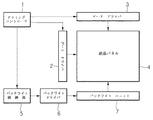

【解決手段】本発明の液晶表示装置は、多数の画素がマトリックス形態に配列された液晶パネルと、液晶パネルに表示する一フレームの映像から分割された少なくとも一つ以上の分割領域に相異した輝度の光を発光させるための少なくとも一つ以上のPWM信号を生成するバックライト制御部と、少なくとも一つ以上の分割領域に対応するように区画された少なくとも一つ以上のブロックを含むバックライトユニットと、少なくとも一つ以上のPWM信号に相応する少なくとも一つ以上の駆動信号をバックライトユニットの少なくとも一つ以上のブロックに供給するバックライトドライバとを含む。

【選択図】図2

Description

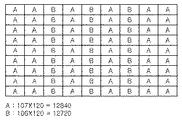

本発明の第2実施例では、説明の便宜のため一つのフレームが第1及び第2領域等(A,B)に分割されているが。領域等の個数が顧慮される際、第1及び第2領域等の以外に第3領域等が更に追加されることができる。

12:タイミングコントローラ

14:ゲートドライバ

16:データドライバ

18:液晶パネル

20,50,70:バックライト制御部

22,52,72:映像分析部

24,54,74:ディミング制御部

26,56,58,82,84,86,88:貯蔵部

30:バックライトドライバ

32:バックライトユニット

34:映像分割部

36:平均計算部

Claims (16)

- 多数の画素がマトリックス形態に配列された液晶パネルと、

前記液晶パネルに表示する一フレームの映像から分割された少なくとも一つ以上の分割領域に互いに相異する輝度の光を発光させるための少なくとも一つ以上のPWM信号を生成するバックライト制御部と、

前記分割領域に対応するように区画された少なくとも一つ以上のブロックを含むバックライトユニットと、

前記PWM信号などに相応する少なくとも一つ以上の駆動信号を前記バックライトユニットの前記ブロックに供給するバックライトドライバと

を含むことを特徴とする液晶表示装置。 - 前記バックライト制御部は、

前記一フレームの映像を前記バックライトユニットに区画されたブロックの個数に対応する分割領域に分割して前記各分割領域の平均輝度値によるディミングアドレスを生成する映像分析部、

前記映像分析部で生成されたディミングアドレスに対応するディミング信号を生成して前記ディミング信号に相応するPWM信号を生成するディミング制御部、

及び、前記少なくとも一つ以上の分割領域の各々に対してディミングアドレスとこれに対応するディミング信号に構成された少なくとも一つ以上のディミングカーブを貯蔵する少なくとも一つ以上の貯蔵部

を含むことを特徴とする請求項1記載の液晶表示装置。 - 前記ディミングアドレスの個数は前記少なくとも一つ以上の分割領域に対して互いに相異することを特徴とする請求項2記載の液晶表示装置。

- 前記分割領域に含まれた画素の総数が多ければ多いほど前記ディミングアドレスの個数は増加することを特徴とする請求項3記載の液晶表示装置。

- 前記ディミング信号は0乃至255階調の中の一つを表す輝度信号であることを特徴とする請求項2記載の液晶表示装置。

- 前記ディミングカーブの個数は前記分割領域の個数に応じて設定されることを特徴とする請求項2記載の液晶表示装置。

- 前記分割領域は前記液晶パネルの横方向に互いに相異した画素数を有することにより分割された少なくとも二つ以上の領域を含むことを特徴とする請求項1記載の液晶表示装置。

- 前記分割領域は前記液晶パネルの縦方向に互いに相異した画素数を有することにより分割された少なくとも二つ以上の領域を含むことを特徴とする請求項1記載の液晶表示装置。

- 前記分割領域は前記液晶パネルの横方向と縦方向に互いに相異した画素数を有することにより分割された少なくとも四つ以上の領域を含むことを特徴とする請求項1記載の液晶表示装置。

- 前記各ブロックは多数の発光ダイオードとを含むことを特徴とする請求項1記載の液晶表示装置。

- 前記各ブロックは導光板と導光板の側面に配置された多数の発光ダイオードとを含むことを特徴とする請求項1記載の液晶表示装置。

- 前記分割領域の個数は前記バックライトユニットに区画されたブロックの個数により決定されることを特徴とする請求項1記載の液晶表示装置。

- 多数の画素がマトリックス形態に配列された液晶パネルと少なくとも一つ以上のブロックを含むバックライトユニットを含む液晶表示装置において、

前記液晶パネルに表示する一フレームの映像を前記ブロックに対応する少なくとも一つ以上の分割領域に分割する段階、

前記各分割領域の平均輝度値によるディミングアドレスを生成する段階、

前記分割領域別に設定されたディミングカーブを基に前記各分割領域に対して生成されたディミングアドレスに対応するディミング信号を生成する段階、

及び、前記各分割領域に対して生成されたディミング信号に相応するPWM信号を生成して前記バックライトユニットのブロックに供給する段階、

を含むことを特徴とする液晶表示装置の駆動方法。 - 前記分割領域は前記バックライトユニットに区画されたブロックに対応するように分割されることを特徴とする請求項13記載の液晶表示装置の駆動方法。

- 前記各ディミングカーブはディミングアドレスを入力値としてディミング信号を出力値として構成されることを特徴とする請求項13記載の液晶表示装置の駆動方法。

- 前記各分割領域に対応する前記バックライトのブロックから互いに相異した輝度の光が発光されることを特徴とする請求項13記載の液晶表示装置の駆動方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2008-0089278 | 2008-09-10 | ||

| KR1020080089278A KR101337142B1 (ko) | 2008-09-10 | 2008-09-10 | 액정표시장치 및 그 구동 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010066743A true JP2010066743A (ja) | 2010-03-25 |

| JP4980336B2 JP4980336B2 (ja) | 2012-07-18 |

Family

ID=41798820

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008316324A Active JP4980336B2 (ja) | 2008-09-10 | 2008-12-12 | 液晶表示装置及びその駆動方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8223116B2 (ja) |

| JP (1) | JP4980336B2 (ja) |

| KR (1) | KR101337142B1 (ja) |

| CN (1) | CN101673518B (ja) |

| TW (1) | TWI415097B (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013070774A1 (en) * | 2011-11-11 | 2013-05-16 | Dolby Laboratories Licensing Corporation | Systems and method for display systems having improved power profiles |

| JP2014032523A (ja) * | 2012-08-02 | 2014-02-20 | Sharp Corp | 机型表示装置 |

| JP2014073069A (ja) * | 2012-09-28 | 2014-04-21 | Lg Display Co Ltd | Dc−dc変換器制御回路と、それを用いた映像表示装置及びその駆動方法 |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010147293A1 (ko) * | 2009-06-15 | 2010-12-23 | 엘지전자 주식회사 | 디스플레이 장치 |

| JP2011013458A (ja) * | 2009-07-02 | 2011-01-20 | Panasonic Corp | 液晶表示装置 |

| TW201128618A (en) * | 2010-02-03 | 2011-08-16 | Novatek Microelectronics Corp | Apparatus of back-light control and control method thereof |

| US10002571B1 (en) * | 2010-02-26 | 2018-06-19 | Zulch Laboratories, Inc. | Liquid crystal display incorporating color-changing backlight |

| US8766904B2 (en) * | 2010-03-18 | 2014-07-01 | Stmicroelectronics, Inc. | Method of modeling the light field created by a local-dimming LED backlight for an LCD display |

| US9336728B2 (en) | 2010-05-14 | 2016-05-10 | Stmicroelectronics, Inc. | System and method for controlling a display backlight |

| WO2012114682A1 (ja) * | 2011-02-23 | 2012-08-30 | パナソニック株式会社 | 表示装置及び表示方法 |

| KR101781502B1 (ko) | 2011-03-28 | 2017-09-26 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 구동 방법 |

| US20140132493A1 (en) * | 2012-11-15 | 2014-05-15 | Shenzhen China Star Optoelectronics Technology Co., Ltd | Clock Driver of Liquid Crystal Display |

| TWI573125B (zh) * | 2015-07-24 | 2017-03-01 | 明基電通股份有限公司 | 顯示方法及顯示裝置 |

| CN105825821B (zh) * | 2016-05-18 | 2018-09-14 | 青岛海信电器股份有限公司 | 背光源的控制方法、背光源的控制装置和液晶显示屏 |

| KR102637702B1 (ko) * | 2016-08-30 | 2024-02-15 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 액정 표시 장치의 로컬 디밍 방법 |

| TWI672686B (zh) * | 2018-02-13 | 2019-09-21 | 佳世達科技股份有限公司 | 顯示裝置及背光控制方法 |

| CN109979389B (zh) | 2019-04-08 | 2020-07-31 | 成都京东方光电科技有限公司 | 伽马校正方法及装置、显示装置、计算机存储介质 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002099250A (ja) * | 2000-09-21 | 2002-04-05 | Toshiba Corp | 表示装置 |

| JP2005338857A (ja) * | 2004-05-28 | 2005-12-08 | Lg Philips Lcd Co Ltd | 液晶表示装置の駆動装置及びその方法 |

| JP2007183608A (ja) * | 2005-12-29 | 2007-07-19 | Lg Philips Lcd Co Ltd | 液晶表示装置の駆動装置及び駆動方法 |

| JP2007212782A (ja) * | 2006-02-09 | 2007-08-23 | Sony Corp | カラー液晶表示装置組立体の駆動方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4628770B2 (ja) | 2004-02-09 | 2011-02-09 | 株式会社日立製作所 | 照明装置を備えた画像表示装置及び画像表示方法 |

| KR101097584B1 (ko) * | 2004-11-25 | 2011-12-22 | 엘지디스플레이 주식회사 | 액정표시장치의 휘도제어 장치 및 방법 |

| KR101136185B1 (ko) * | 2004-12-30 | 2012-04-17 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 구동방법 |

| US8373640B2 (en) * | 2005-07-07 | 2013-02-12 | Sharp Kabushiki Kaisha | Display device |

| EP2439728A3 (en) * | 2006-06-02 | 2013-09-04 | Samsung Display Co., Ltd. | High dynamic contrast display system having multiple segmented backlight |

| TWI381362B (zh) * | 2006-09-13 | 2013-01-01 | Mstar Semiconductor Inc | 顯示裝置及其亮度控制方法 |

| JP4264558B2 (ja) * | 2006-11-10 | 2009-05-20 | ソニー株式会社 | バックライト装置、バックライト駆動方法及びカラー画像表示装置 |

| CN100583214C (zh) * | 2006-12-31 | 2010-01-20 | 深圳Tcl工业研究院有限公司 | 液晶电视背光控制系统及方法 |

| TWI455085B (zh) * | 2007-01-26 | 2014-10-01 | Au Optronics Corp | 液晶顯示器之背光控制方法 |

| JP2008299145A (ja) * | 2007-05-31 | 2008-12-11 | Toshiba Corp | 表示装置および表示方法 |

-

2008

- 2008-09-10 KR KR1020080089278A patent/KR101337142B1/ko active IP Right Grant

- 2008-12-03 US US12/327,169 patent/US8223116B2/en active Active

- 2008-12-12 JP JP2008316324A patent/JP4980336B2/ja active Active

- 2008-12-25 CN CN2008101865855A patent/CN101673518B/zh active Active

-

2009

- 2009-07-30 TW TW098125709A patent/TWI415097B/zh active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002099250A (ja) * | 2000-09-21 | 2002-04-05 | Toshiba Corp | 表示装置 |

| JP2005338857A (ja) * | 2004-05-28 | 2005-12-08 | Lg Philips Lcd Co Ltd | 液晶表示装置の駆動装置及びその方法 |

| JP2007183608A (ja) * | 2005-12-29 | 2007-07-19 | Lg Philips Lcd Co Ltd | 液晶表示装置の駆動装置及び駆動方法 |

| JP2007212782A (ja) * | 2006-02-09 | 2007-08-23 | Sony Corp | カラー液晶表示装置組立体の駆動方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013070774A1 (en) * | 2011-11-11 | 2013-05-16 | Dolby Laboratories Licensing Corporation | Systems and method for display systems having improved power profiles |

| JP2014032523A (ja) * | 2012-08-02 | 2014-02-20 | Sharp Corp | 机型表示装置 |

| JP2014073069A (ja) * | 2012-09-28 | 2014-04-21 | Lg Display Co Ltd | Dc−dc変換器制御回路と、それを用いた映像表示装置及びその駆動方法 |

| US9448573B2 (en) | 2012-09-28 | 2016-09-20 | Lg Display Co., Ltd. | DC-DC converter control circuit, image display device using the same and driving method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201011726A (en) | 2010-03-16 |

| CN101673518B (zh) | 2013-04-03 |

| KR101337142B1 (ko) | 2013-12-05 |

| TWI415097B (zh) | 2013-11-11 |

| KR20100030361A (ko) | 2010-03-18 |

| US8223116B2 (en) | 2012-07-17 |

| CN101673518A (zh) | 2010-03-17 |

| JP4980336B2 (ja) | 2012-07-18 |

| US20100060555A1 (en) | 2010-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4980336B2 (ja) | 液晶表示装置及びその駆動方法 | |

| US8243010B2 (en) | Liquid crystal display device and driving method thereof for improving a contrast ratio | |

| JP4956520B2 (ja) | バックライト装置及びこれを用いた液晶表示装置 | |

| JP5368465B2 (ja) | 画像表示用発光装置の電力制御方法、画像表示用発光装置、表示装置、及びテレビ受信装置 | |

| JP4882657B2 (ja) | バックライト制御装置、バックライト制御方法、および液晶表示装置 | |

| EP2128687A1 (en) | Light source device and liquid crystal display device | |

| JP2008249780A (ja) | 液晶ディスプレイ装置 | |

| JP2004191490A (ja) | 液晶表示装置 | |

| US10347194B2 (en) | Display device and method for driving same | |

| WO2012111471A1 (ja) | 表示装置 | |

| US20120293571A1 (en) | Image display device | |

| US8976204B2 (en) | Display device | |

| US20110234478A1 (en) | Liquid crystal display device | |

| JP2010122657A (ja) | 表示装置 | |

| KR101603242B1 (ko) | 로컬 디밍을 위한 표시 영역의 분할 방법과 그를 이용한 액정 표시 장치 및 그 구동 방법 | |

| US10529287B2 (en) | Display device and control method for the same | |

| US20060017687A1 (en) | Liquid crystal display device | |

| KR102059501B1 (ko) | 표시 장치 및 그 구동 방법 | |

| US20090174730A1 (en) | Data driving apparatus and method thereof | |

| US20160049122A1 (en) | Display apparatus and method of driving the same | |

| JP4732070B2 (ja) | フィードフォワード回路部が具備される液晶表示装置 | |

| JP2011128251A (ja) | 液晶表示装置 | |

| KR102488471B1 (ko) | 액정표시장치 | |

| KR100712292B1 (ko) | 액정표시장치 | |

| JP2007114480A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111026 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120321 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120418 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150427 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4980336 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |