JP2010056278A - 半導体装置の検査方法 - Google Patents

半導体装置の検査方法 Download PDFInfo

- Publication number

- JP2010056278A JP2010056278A JP2008219412A JP2008219412A JP2010056278A JP 2010056278 A JP2010056278 A JP 2010056278A JP 2008219412 A JP2008219412 A JP 2008219412A JP 2008219412 A JP2008219412 A JP 2008219412A JP 2010056278 A JP2010056278 A JP 2010056278A

- Authority

- JP

- Japan

- Prior art keywords

- chip

- light

- inspected

- inspection

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000007689 inspection Methods 0.000 title claims abstract description 52

- 238000000034 method Methods 0.000 title claims abstract description 34

- 239000004065 semiconductor Substances 0.000 title claims abstract description 17

- 238000012360 testing method Methods 0.000 claims abstract description 28

- 230000001678 irradiating effect Effects 0.000 claims abstract description 15

- 238000011990 functional testing Methods 0.000 claims abstract description 9

- 230000007547 defect Effects 0.000 claims abstract description 8

- 230000007257 malfunction Effects 0.000 claims abstract description 7

- 230000035945 sensitivity Effects 0.000 abstract description 8

- 238000001514 detection method Methods 0.000 abstract description 7

- 230000002950 deficient Effects 0.000 abstract description 5

- 239000000523 sample Substances 0.000 description 19

- 230000006870 function Effects 0.000 description 13

- 230000003071 parasitic effect Effects 0.000 description 9

- 235000012431 wafers Nutrition 0.000 description 7

- 239000000758 substrate Substances 0.000 description 5

- 238000012790 confirmation Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

Images

Landscapes

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

Abstract

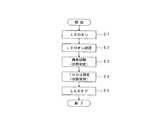

【解決手段】ICチップ内の配線について断線不良を検出する配線検査工程、を含み、この配線検査工程は、被検査部を含む回路について機能試験を開始して、被検査部を電荷が供給される状態に設定する工程と、電荷が供給された被検査部に光を照射する工程と、被検査部に光を一定時間照射した後で、機能試験の結果を出力させる工程と、を有する(ステップ(S)3〜7)。このような方法によれば、被検査部に光を照射しない場合と比べて、断線に起因した動作不良を起こし易くすることができ、断線不良の検出感度を高めることができる。

【選択図】図2

Description

一方で、メモリ、サーマルドライバ等を備えたICチップの電気的特性は、外部からの光の照射によって変化するものがあり、この種の電気的特性の検査に関しては、ICチップに光を照射した状態で行う場合がある。その場合は、特許文献1、2に開示されているように、光源内臓プローブカードや、光源ガイド付きプローブカード等を使用することができる。

そこで、本発明はこのような事情に鑑みてなされたものであって、ICチップの良、不良をより高精度に判定することができるようにした半導体装置の検査方法の提供を目的とする。

発明3の半導体装置の検査方法は、発明1又は発明2の半導体装置の検査方法において、前記ICチップが誤作動しないように前記光の照度を調整することを特徴とするものである。

発明4の半導体装置の検査方法は、発明1から発明3の何れか一の半導体装置の検査方法において、前記ICチップ内の回路について電気的試験を行う回路検査工程、をさらに含み、前記回路検査工程では、前記ICチップに光を照射しないことを特徴とするものである。ここで、「電気的試験」とは、例えば、機能試験、回路の直流(DC)特性を調べるDC試験、又は、回路の交流(AC)特性を調べるAC試験等である。

また、特に、発明4の半導体装置の製造方法によれば、ICチップを遮光することにより、ICチップの電気的な状態を安定化させることができる。従って、回路検査工程において、各試験の精度を高めることができる。

このような検査方法によれば、トランジスタに光を照射しない場合と比べて、リーク電流値を大きくすることができ、リーク電流不良の検出感度を高めることができる。これにより、ICチップの良、不良をより高精度に判定することができる。

(1)第1実施形態

図1は、本発明の実施形態に係る検査装置10の構成例を示す概念図である。ここでは、まず始めに、検査装置10の概要について説明し、次に、この検査装置10を用いてICチップを検査する方法について説明する。

図1に示すように、この検査装置10は、ウエーハW上に形成されたICチップのパッド電極に探針(以下、プローブ針ともいう。)を接触させて、ICチップの電気的特性や機能等を試験するための装置である。この検査装置10は、例えば、ステージ1と、プローブカード3と、パフォーマンスボード5と、ヘッド7と、テスタ9と、を含んで構成されている。これらの中で、ステージ1は、ウエーハWを支持すると共に、支持したウエーハWを水平方向(即ち、X軸方向、Y軸方向)と、垂直方向(即ち、Z軸方向)に移動させるものである。

まず始めに、図2のステップ(S)1では、検査装置10のステージ1上にウエーハWを固定した状態で、発光ダイオード(LED)が発光していないことを確認する。

次に、図2のステップ(S)2では、例えば、ICチップに含まれる順序論理回路(sequencial logic)等の機能を調べる機能試験や、ICチップに含まれるアナログ回路等のDC特性を調べるDC試験、AC特性を調べるAC試験を行う。ここでは、ICチップを遮光することにより、ICチップの電気的な状態を安定化させることができるので、ICチップ内の回路について、各試験の精度を高めることができる。

次に、図2のステップ(S)4では、発光ダイオード(LED)が発光していることを確認する。そして、図2のステップ(S)5では、機能試験1(状態設定)を行う。ここで、機能試験1(状態設定)の一例について、具体的に説明する。

次に、図2のステップ(S)7では、例えばICチップ20の入力端子25、27に信号を入力して、機能試験2(状態確認)を行う。これにより、機能試験の結果がICチップ20の出力端子29に伝えられる。その後、図2のステップ(S)8で発光ダイオードによる発光を止め、検査工程を終了する。

図4に示すように、機能試験1(状態設定)は、例えば試験を開始してから「入力1がH(High)、入力2がH」となるまでの間に行われる。また、待機(状態保持)は、例えば「入力1がH、入力2がH」となってから「入力1がL(Low)、入力2がH」となるまでの間、連続して行われる。そして、この後で、機能試験2(状態確認)が行われ、出力1が出力される。この出力1は、例えば図3の出力端子29を介してプローブ針に伝えられ、この出力1の値に基づいて断線不良の有無を判定する。この判定は、例えば図1に示したテスタ9が行う。

このように、本発明の第1実施形態によれば、被検査部21に断線不良が存在し、寄生容量が生じている場合であっても、被検査部21に光を照射することにより、寄生容量から電荷を効率良くディスチャージすることができる。従って、断線不良の検出感度が高い。

これに対して、本発明の第1実施形態によれば、電荷のディスチャージを例えば10msec程度で完了させることができる。つまり、光を照射しない場合と比べて、待機(状態保持)の所要時間が1/10である。従って、断線に起因した動作不良を起こし易くすることができ、断線不良の検出感度を高めることができる。これにより、ICチップ20の良、不良をより高精度に判定することができる。

上記の第1実施形態では、ICチップ20に光を照射しながら機能試験をすることで、断線不良を検出する場合について説明した。しかしながら、本発明はこれに限られることは無い。例えば、図1に示した検査装置10を用いて、ICチップに光を照射しながら、IDDQ試験(即ち、静止状態の電源電流を測定する試験)を行っても良い。これにより、例えば、図5に示すようなCMOS回路30において、nMOSトランジスタ31のリーク不良を感度良く検出することができる。

このように、本発明の第2実施形態によれば、光を照射しない場合と比べて、リーク電流値を大きくすることができ、リーク電流不良の検出感度を高めることができる。これにより、ICチップの良、不良をより高精度に判定することができる

Claims (5)

- ICチップ内の配線について断線不良を検出する配線検査工程、を含み、

前記配線検査工程は、

前記配線のうちの被検査部を含む回路について機能試験を開始して、前記被検査部を電荷が供給される状態に設定する工程と、

電荷が供給された前記被検査部に光を照射する工程と、

前記被検査部に光を一定時間照射した後で、前記機能試験の結果を出力させる工程と、を有することを特徴とする半導体装置の検査方法。 - 前記機能試験の結果を出力させる工程は、前記被検査部に光を照射しながら行うことを特徴とする請求項1に記載の半導体装置の検査方法。

- 前記ICチップが誤作動しないように前記光の照度を調整することを特徴とする請求項1又は請求項2に記載の半導体装置の検査方法。

- 前記ICチップ内の回路について電気的試験を行う回路検査工程、をさらに含み、

前記回路検査工程では、前記ICチップに光を照射しないことを特徴とする請求項1から請求項3の何れか一項に記載の半導体装置の検査方法。 - ICチップ内のトランジスタを含む回路についてリーク電流不良を検出する検査工程、を含み、

前記検査工程では、前記トランジスタに光を照射しながらリーク電流値を測定することを特徴とする半導体装置の検査方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008219412A JP5343454B2 (ja) | 2008-08-28 | 2008-08-28 | 半導体装置の検査方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008219412A JP5343454B2 (ja) | 2008-08-28 | 2008-08-28 | 半導体装置の検査方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056278A true JP2010056278A (ja) | 2010-03-11 |

| JP5343454B2 JP5343454B2 (ja) | 2013-11-13 |

Family

ID=42071886

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008219412A Expired - Fee Related JP5343454B2 (ja) | 2008-08-28 | 2008-08-28 | 半導体装置の検査方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5343454B2 (ja) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62283499A (ja) * | 1986-05-31 | 1987-12-09 | Mitsubishi Electric Corp | 半導体集積回路の検査方法 |

| JPS63102331A (ja) * | 1986-10-20 | 1988-05-07 | Matsushita Electronics Corp | 半導体集積回路の検査方法 |

| JPH047851A (ja) * | 1990-04-25 | 1992-01-13 | Mitsubishi Electric Corp | 半導体装置 |

| JP2004328758A (ja) * | 2003-04-29 | 2004-11-18 | Aisin Seiki Co Ltd | 信号受信用ゴーストキャンセルシステム |

| JP2004327858A (ja) * | 2003-04-25 | 2004-11-18 | Toshiba Corp | 半導体装置の検査方法および検査装置 |

-

2008

- 2008-08-28 JP JP2008219412A patent/JP5343454B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62283499A (ja) * | 1986-05-31 | 1987-12-09 | Mitsubishi Electric Corp | 半導体集積回路の検査方法 |

| JPS63102331A (ja) * | 1986-10-20 | 1988-05-07 | Matsushita Electronics Corp | 半導体集積回路の検査方法 |

| JPH047851A (ja) * | 1990-04-25 | 1992-01-13 | Mitsubishi Electric Corp | 半導体装置 |

| JP2004327858A (ja) * | 2003-04-25 | 2004-11-18 | Toshiba Corp | 半導体装置の検査方法および検査装置 |

| JP2004328758A (ja) * | 2003-04-29 | 2004-11-18 | Aisin Seiki Co Ltd | 信号受信用ゴーストキャンセルシステム |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5343454B2 (ja) | 2013-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8237462B2 (en) | Method for wafer-level testing of integrated circuits | |

| JP2004006857A (ja) | 集積回路チップ及びそれの製造方法 | |

| JP2004150840A (ja) | 半導体集積回路の不良解析装置、システムおよび検出方法 | |

| JPH0645418A (ja) | 半導体テストシステム、半導体テスト方法、半導体集積回路の配線パターン作成方法および半導体集積回路 | |

| US9575114B2 (en) | Test system and device | |

| JP3624717B2 (ja) | マルチチップモジュール及びその試験方法 | |

| JP5343454B2 (ja) | 半導体装置の検査方法 | |

| US7617427B2 (en) | Method and apparatus for detecting defects in integrated circuit die from stimulation of statistical outlier signatures | |

| JP2007139603A (ja) | 半導体集積回路の検査方法およびデザインルール検証方法 | |

| JP2010223647A (ja) | 電気的接続状態の検査装置および検査方法 | |

| TWI735915B (zh) | 與面向受測裝置側之光源整合的晶圓探針卡及製造方法 | |

| JP2004045132A (ja) | 半導体集積回路の故障解析装置及び故障解析方法 | |

| CN100533163C (zh) | 可实施老化与电性测试的晶圆及其实施方法 | |

| TWI449933B (zh) | 晶片之測試系統 | |

| JP2023039003A (ja) | 試験装置、試験方法およびプログラム | |

| TW202300933A (zh) | 積體電路裝置之檢測系統、訊號源及電源供應裝置 | |

| JP2003057308A (ja) | 電子装置及び電子装置の良否の検査方法 | |

| JP4744884B2 (ja) | ウエハ検査装置及びウエハ検査方法 | |

| KR20090122615A (ko) | 릴레이 테스트 모듈 및 프로브 스테이션의 릴레이 테스트방법 | |

| KR101144638B1 (ko) | 유기 전계 발광 소자 테스트 방법 | |

| KR100613169B1 (ko) | 무접촉 반도체 소자 테스트 장치 및 테스트 방법 | |

| JP2011029512A (ja) | 半導体集積回路の試験方法及び試験装置 | |

| US20030210068A1 (en) | Apparatus of testing semiconductor | |

| JP2006261391A (ja) | 半導体装置およびその検査方法 | |

| JP2002334966A (ja) | マルチチップモジュールおよびその検査方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110630 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110810 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130423 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130621 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130716 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130729 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5343454 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |