JP2010055653A - 半導体集積記憶回路及びラッチ回路のトリミング方法 - Google Patents

半導体集積記憶回路及びラッチ回路のトリミング方法 Download PDFInfo

- Publication number

- JP2010055653A JP2010055653A JP2008216198A JP2008216198A JP2010055653A JP 2010055653 A JP2010055653 A JP 2010055653A JP 2008216198 A JP2008216198 A JP 2008216198A JP 2008216198 A JP2008216198 A JP 2008216198A JP 2010055653 A JP2010055653 A JP 2010055653A

- Authority

- JP

- Japan

- Prior art keywords

- node

- circuit

- bit line

- main electrode

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1045—Read-write mode select circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/412—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger using field-effect transistors only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

- G11C7/065—Differential amplifiers of latching type

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Static Random-Access Memory (AREA)

Abstract

【解決手段】この半導体集積記憶回路は、第1、第2のインバータを第1及び第2のノードにおいてクロスカップル接続させて形成されるラッチ回路と、その第1のノードと第2のノードにホットキャリアを発生させる為のホットキャリア発生電圧を与える電圧印加回路とを含む。また、ラッチ回路から出力された増幅信号を反転させた反転信号を生成するために形成される反転回路を備える。

【選択図】図1B

Description

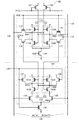

まず本発明の第1の実施の形態を、図1A、図1Bを参照して説明する。

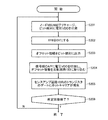

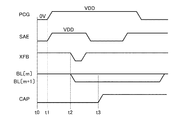

次に、第1の実施の形態に係るSRAMの動作を図2を参照して説明する。ここでは、センスアンプ回路10のトリミングを実行する場合の動作を図2を用いて説明する。

次に、本発明の第2の実施の形態を、図4等を参照して説明する。

次に、第2の実施の形態に係るSRAMの動作を図6を参照して説明する。ここでは、センスアンプ回路110のトリミングを実行する場合の動作を図6を用いて説明する。

次に、本発明の第3の実施の形態を、図7等を参照して説明する。図7は、本発明の第3の実施の形態に係るSRAMの構成を示す回路図である。本実施の形態では、メモリセル1を構成するラッチ回路のオフセットをトリミングするものであり、この点、上述の実施の形態がセンスアンプ回路のトリミングを行うものであるのと異なっている。電圧印加回路を構成するpMOSトランジスタ15、及び反転回路50の構成は第1の実施の形態と同様である。すなわち、この実施の形態では、反転回路50は、メモリセル1を構成するラッチ回路のトランジスタに対し反転データを提供するように構成されているものである。その他、上記の実施の形態と共通する部分については、同一の符号を付し、以下ではその詳細な説明は省略する。

Claims (5)

- 第1のビット線と第2のビット線からなるビット線対と、

第1のインバータと第2のインバータを第1ノード及び第2ノードにおいてクロスカップル接続させて形成されるラッチ回路と、

前記第1のインバータ又は前記第2のインバータを構成するトランジスタにホットキャリアを発生させる為のホットキャリア発生電圧を印加する電圧印加回路と、

前記ラッチ回路から前記ビット線対に出力された増幅信号を反転させた反転信号を生成して前記第1ノード及び前記第2ノードに供給する反転回路と

を備えることを特徴とする半導体集積記憶回路。 - 第1のインバータと第2のインバータを第1ノード及び第2ノードにおいてクロスカップル接続させて形成されるラッチ回路のトリミング方法において、

前記ラッチ回路からビット線対に供給された増幅信号を反転させて反転信号を生成するステップと、

前記反転信号を前記第1ノード及び前記第2ノードに供給するステップと、

前記ラッチ回路を構成するトランジスタにホットキャリアを発生させる為のホットキャリア発生電圧を印加するステップと、

を備えたことを特徴とする半導体集積記憶回路のラッチ回路のトリミング方法。 - 前記電圧印加回路は、

前記第1ノードに第1主電極が接続され前記第1のビット線に第2主電極が接続される第3のトランジスタと、

前記第2ノードに第1主電極が接続され前記第2のビット線に第2主電極が接続される第4のトランジスタと、

前記第1ノードに第1主電極が接続され前記ホットキャリア発生電圧を供給する電源に第2主電極が接続され、ゲートに前記反転回路が接続される第5のトランジスタと、

前記第2ノードに第1主電極が接続され前記ホットキャリア発生電圧を供給する電源に第2主電極が接続され、ゲートに前記反転回路が接続される第6のトランジスタと

を備えることを特徴とする請求項1記載の半導体集積記憶回路。 - 前記反転回路は、

第3のインバータと第4のインバータを第3のノード及び第4のノードにおいてクロスカップル接続させて形成されるラッチ回路と、

前記第3のノードに第2主電極が接続され前記第1のビット線に第1主電極が接続される第7のトランジスタと前記第4のノードに第2主電極が接続され前記第2のビット線に第1主電極が接続される第8のトランジスタとにより構成され、前記第3のノード及び前記第4のノードと前記ビット線対とを適宜接続して前記ラッチ回路に前記増幅信号を取り込むキャプチャ回路と、

前記第4のノードに第2主電極が接続され前記第1のビット線に第1主電極が接続される第9のトランジスタと、前記第3のノードに第2主電極が接続され前記第2のビット線に第1主電極が接続される第10のトランジスタとにより構成され、前記第3のノード及び前記第4のノードと前記ビット線対とを適宜接続して前記ビット線対に前記反転信号を転送するリバース回路と

を備えることを特徴とする請求項1記載の半導体集積記憶回路。 - 前記反転回路は、

第5のインバータと第6のインバータを第5のノード及び第6のノードにおいてクロスカップル接続させて形成されるラッチ回路と、

前記第5のインバータの一端及び前記第6のインバータの一端と前記ビット線対とを適宜接続して前記ラッチ回路に前記反転信号を生成する反転信号生成回路と

を備え、

前記第5のインバータは、

第11のトランジスタと第12のトランジスタとを電流経路を直列に接続させて形成され、

前記第6のインバータは、

第13のトランジスタと第14のトランジスタとを電流経路を直列に接続させて形成され、

前記反転信号生成回路は、

前記第1のビット線にゲートが接続され前記第12のトランジスタの第2主電極に第1主電極が接続される第15のトランジスタと、

前記第2のビット線にゲートが接続され前記第14のトランジスタの第2主電極に第1主電極が接続される第16のトランジスタと、

前記第5のノードに第1主電極が接続され正電圧を供給する電源に第2主電極が接続される第17のトランジスタと、

前記第6のノードに第1主電極が接続され前記正電圧を供給する電源に第2主電極が接続される第18のトランジスタと

により形成されることを特徴とする請求項1記載の半導体集積記憶回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216198A JP4908472B2 (ja) | 2008-08-26 | 2008-08-26 | 半導体集積記憶回路及びラッチ回路のトリミング方法 |

| US12/540,022 US8077499B2 (en) | 2008-08-26 | 2009-08-12 | Semiconductor integrated memory circuit and trimming method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216198A JP4908472B2 (ja) | 2008-08-26 | 2008-08-26 | 半導体集積記憶回路及びラッチ回路のトリミング方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010055653A true JP2010055653A (ja) | 2010-03-11 |

| JP4908472B2 JP4908472B2 (ja) | 2012-04-04 |

Family

ID=41725246

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008216198A Expired - Fee Related JP4908472B2 (ja) | 2008-08-26 | 2008-08-26 | 半導体集積記憶回路及びラッチ回路のトリミング方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8077499B2 (ja) |

| JP (1) | JP4908472B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9368228B2 (en) | 2013-11-19 | 2016-06-14 | Kabushiki Kaisha Toshiba | Semiconductor memory |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012064292A (ja) * | 2010-09-17 | 2012-03-29 | Toshiba Corp | 半導体集積回路 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0676582A (ja) * | 1992-08-27 | 1994-03-18 | Hitachi Ltd | 半導体装置 |

| JP2000311491A (ja) * | 1999-04-28 | 2000-11-07 | Hitachi Ltd | 半導体メモリ |

| JP2003045190A (ja) * | 2001-07-27 | 2003-02-14 | Toshiba Corp | 半導体集積回路 |

| JP2004127499A (ja) * | 2002-09-30 | 2004-04-22 | Agere Systems Inc | スタティック・ランダム・アクセス・メモリの初期状態を決定する方法 |

| JP2005276315A (ja) * | 2004-03-24 | 2005-10-06 | Kawasaki Microelectronics Kk | 半導体集積回路の使用方法および半導体集積回路 |

| JP2005353106A (ja) * | 2002-12-19 | 2005-12-22 | Kazuyuki Nakamura | Cmis型半導体不揮発記憶回路 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10162585A (ja) | 1996-12-03 | 1998-06-19 | Sony Corp | トリミング機能付きセンスアンプを備えた半導体メモリ素子 |

| US6584026B2 (en) | 2000-06-28 | 2003-06-24 | Kabushiki Kaisha Toshiba | Semiconductor integrated circuit capable of adjusting input offset voltage |

| JP4965883B2 (ja) | 2006-04-07 | 2012-07-04 | 株式会社東芝 | 半導体集積回路装置および半導体集積回路装置のトリミング方法 |

-

2008

- 2008-08-26 JP JP2008216198A patent/JP4908472B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-12 US US12/540,022 patent/US8077499B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0676582A (ja) * | 1992-08-27 | 1994-03-18 | Hitachi Ltd | 半導体装置 |

| JP2000311491A (ja) * | 1999-04-28 | 2000-11-07 | Hitachi Ltd | 半導体メモリ |

| JP2003045190A (ja) * | 2001-07-27 | 2003-02-14 | Toshiba Corp | 半導体集積回路 |

| JP2004127499A (ja) * | 2002-09-30 | 2004-04-22 | Agere Systems Inc | スタティック・ランダム・アクセス・メモリの初期状態を決定する方法 |

| JP2005353106A (ja) * | 2002-12-19 | 2005-12-22 | Kazuyuki Nakamura | Cmis型半導体不揮発記憶回路 |

| JP2005276315A (ja) * | 2004-03-24 | 2005-10-06 | Kawasaki Microelectronics Kk | 半導体集積回路の使用方法および半導体集積回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9368228B2 (en) | 2013-11-19 | 2016-06-14 | Kabushiki Kaisha Toshiba | Semiconductor memory |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100054025A1 (en) | 2010-03-04 |

| US8077499B2 (en) | 2011-12-13 |

| JP4908472B2 (ja) | 2012-04-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7936624B2 (en) | Reduced power bitline precharge scheme for low power applications in memory devices | |

| US7590003B2 (en) | Self-reference sense amplifier circuit and sensing method | |

| US9589630B2 (en) | Low voltage current reference generator for a sensing amplifier | |

| US20040017717A1 (en) | Differential amplifier circuit with high amplification factor and semiconductor memory device using the differential amplifier circuit | |

| US9257995B2 (en) | Apparatuses and methods for mitigating uneven circuit degradation of delay circuits | |

| Gavaskar et al. | Design and comparative analysis of SRAM array using low leakage controlled transistor technique with improved delay | |

| JP4908472B2 (ja) | 半導体集積記憶回路及びラッチ回路のトリミング方法 | |

| US8743628B2 (en) | Line driver circuits, methods, and apparatuses | |

| US20170243634A1 (en) | Semiconductor memory device including sram cells | |

| JP2006221769A (ja) | メモリ回路 | |

| CN103312311B (zh) | 一种用于电平转换的集成电路及其方法 | |

| CN106898382B (zh) | 存储器的读取电路及其读取方法 | |

| US7539064B2 (en) | Precharge circuit of semiconductor memory apparatus | |

| JP2013246775A5 (ja) | ||

| JP6069544B1 (ja) | ラッチ回路及び半導体記憶装置 | |

| US10832765B2 (en) | Variation tolerant read assist circuit for SRAM | |

| US7872927B2 (en) | Semiconductor memory device and method of controlling power source | |

| CN102201806A (zh) | 具有电流控制机制的电路及电流控制方法 | |

| JP5772058B2 (ja) | 半導体記憶装置 | |

| US6396740B1 (en) | Reference cell circuit for split gate flash memory | |

| CN206505723U (zh) | 一种基于stt‑mtj的mram单元控制电路 | |

| US20090190424A1 (en) | Semiconductor circuit | |

| KR100729350B1 (ko) | 시리얼 센싱 동작을 수행하는 노어 플래시 메모리 장치 | |

| WO2023106105A1 (ja) | 半導体記憶装置及び制御方法 | |

| TW202524475A (zh) | 半導體記憶裝置及其控制方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100729 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101025 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101102 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101227 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111102 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20111110 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20111125 |

|

| TRDD | Decision of grant or rejection written | ||

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20111205 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111213 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |