JP2010044403A - 液晶表示装置及びこれの製造方法 - Google Patents

液晶表示装置及びこれの製造方法 Download PDFInfo

- Publication number

- JP2010044403A JP2010044403A JP2009219345A JP2009219345A JP2010044403A JP 2010044403 A JP2010044403 A JP 2010044403A JP 2009219345 A JP2009219345 A JP 2009219345A JP 2009219345 A JP2009219345 A JP 2009219345A JP 2010044403 A JP2010044403 A JP 2010044403A

- Authority

- JP

- Japan

- Prior art keywords

- transparent substrate

- data line

- pixel

- gate

- liquid crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

【解決手段】複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が画素領域に印加される画素アレイが、第1透明基板の第1表面と第2透明基板の第1表面とに形成されており、データ線は、行及び列方向の一方の方向に配列されており、ゲート線は、行及び列方向の他方の方向に配列されており、そして第1透明基板の画素領域のそれぞれは、第2透明基板の画素領域のそれぞれに対して、ゲート線に沿った方向において、該ゲート線に沿った画素領域の幅の半分の距離だけシフトされている。

【選択図】図6

Description

第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

第1透明基板及び第2透明基板は、第1透明基板の第1表面が第2透明基板の第1表面に対面するように配列されており、そして液晶材料が、第1透明基板の第1表面と第2透明基板の第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が画素領域に印加される画素アレイが、第1透明基板の第1表面と第2透明基板の第1表面とに形成されており、

データ線は、行及び列方向の一方の方向に配列されており、そしてゲート線は、行及び列方向の他方の方向に配列されており、そして

第1透明基板の画素領域のそれぞれは、第2透明基板の画素領域のそれぞれに対して、ゲート線に沿った方向において、該ゲート線に沿った画素領域の幅の半分の距離だけシフトされていることを特徴とする。

第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

第1透明基板及び第2透明基板は、第1透明基板の第1表面が第2透明基板の第1表面に対面するように配列されており、そして液晶材料が、第1透明基板の第1表面と第2透明基板の第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が画素領域に印加される画素アレイが、第1透明基板の第1表面と第2透明基板の第1表面とに形成されており、

データ線は、行及び列方向の一方の方向に配列されており、そしてゲート線は、行及び列方向の他方の方向に配列されており、そして第1透明基板の画素領域のそれぞれは、第2透明基板の画素領域のそれぞれに対して、データ線に沿った方向において、該データ線に沿った画素領域の高さの半分の距離だけシフトされていることを特徴とする。

第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

第1透明基板及び第2透明基板は、第1透明基板の第1表面が第2透明基板の第1表面に対面するように配列されており、そして垂直配向液晶材料が、第1透明基板の第1表面と第2透明基板の第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が画素領域に印加される画素アレイが、第1透明基板の第1表面と第2透明基板の第1表面とに形成されており、

データ線は、行及び列方向の一方の方向に配列されており、そしてゲート線は、行及び列方向の他方の方向に配列されており、そして

第1透明基板の画素領域のそれぞれは、第2透明基板の画素領域のそれぞれに対して、ゲート線に沿った方向において、該ゲート線に沿った画素領域の幅の半分の距離だけシフトされており、そして

第2透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが第1透明基板に形成され、そして第1透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが第2透明基板に形成されており、ブラック・マトリクスのそれぞれは台形状の断面を有することを特徴とする。

第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

第1透明基板及び第2透明基板は、第1透明基板の第1表面が第2透明基板の第1表面に対面するように配列されており、そして垂直配向液晶材料が、第1透明基板の第1表面と第2透明基板の第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が画素領域に印加される画素アレイが、第1透明基板の第1表面と第2透明基板の第1表面とに形成されており、

データ線は、行及び列方向の一方の方向に配列されており、そしてゲート線は、行及び列方向の他方の方向に配列されており、そして

第1透明基板の画素領域のそれぞれは、第2透明基板の画素領域のそれぞれに対して、データ線に沿った方向において、該データ線に沿った画素領域の高さの半分の距離だけシフトされており、そして

第2透明基板に形成された1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが第1透明基板に形成され、そして第1透明基板に形成された1つのゲートにそれぞれ対面する複数個のブラック・マトリクスが第2透明基板に形成されており、ブラック・マトリクスのそれぞれは台形状の断面を有することを特徴とする。

(a)複数個の画素領域が行及び列の方向に配列されそしてデータ線を介してデータ信号が画素領域に印加される画素アレイを、1つの透明基板の第1部分及び第2部分に形成するステップと、

(b)透明基板を第1部分と第2部分とに切断するステップと、

(c)第1部分の画素アレイと第2部分の画素アレイとを対面させるように第1部分及び第2部分を配列するステップと、

(d)第1及び第2部分の画素アレイを囲むように、第1部分と第2部分とを封止領域で接着するステップと、

(e)封止領域により囲まれた空間内に液晶材料を充填するステップとを含み、

画素アレイにおいて、データ線は行及び列方向の一方の方向に配列され、ゲート線は行及び列方向の他方の方向に配列され、そして画素領域のそれぞれは、ゲート線とデータ線との交点に隣接する領域に形成されており、そして画素領域のそれぞれは、表示電極と、ゲート線及びデータ線と表示電極との間に接続された薄膜トランジスタとを有し、

ステップ(c)において、第1部分の画素領域のそれぞれは、第2部分の画素領域のそれぞれに対して、ゲート線に沿った方向で、ゲート線に沿った画素領域の幅の半分の距離だけシフトされることを特徴とする。

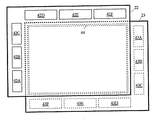

ステップ(a)において、第1部分のデータ線に接続されているデータ線パッドが、第1部分の上側エッジ及び下側エッジの一方に隣接する第1領域に形成され、第1部分のゲート線に接続されているゲート線パッドが、第1部分の左側エッジ及び右側エッジの一方に隣接する第2領域に形成され、第2部分のデータ線に接続されているデータ線パッドが、第2部分の上側エッジ及び下側エッジの他方に隣接する第3領域に形成され、そして第2部分のゲート線に接続されているゲート線パッドが、第2部分の左側エッジ及び右側エッジの他方に隣接する第4領域に形成されることを特徴とする。

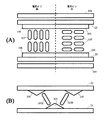

ステップ(a)において、逆スタガ型の薄膜トランジスタのゲート電極と複数個のブラック・マトリクスとが第1及び第2部分に同時に形成されることを特徴とする。

ステップ(a)において、スタガ型の薄膜トランジスタの光遮断層と複数個のブラック・マトリクスとが第1及び第2部分に同時に形成されることを特徴とする。

ステップ(a)において、スタガ型の薄膜トランジスタの光遮断層と複数個のブラック・マトリクスとが第1及び第2部分に同時に形成されることを特徴とする。

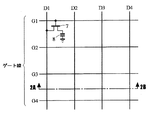

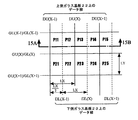

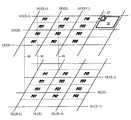

図6は、上側及び下側ガラス基板22及び23上のデータ線D1乃至DNとゲート線G1乃至GMの配列を示す。図7は、上側及び下側の両ガラス基板22及び23上のゲート線に印加されるゲート・パルスを示す。図8は、LCDパネルを制御するための回路のブロック図を示す。図9は、上側及び下側ガラス基板22及び23のデータ線に印加されるデータ・パルスを示す。図10は、図6の線6A−6A及び6B−6Bに沿った上側及び下側ガラス基板22及び23の断面を示す。

図6の上側ガラス基板22上のTFTの破損に基づいて画素P11に点欠陥が生じ、そして上側ガラス基板22のデータ線D1の部分50とゲート線G1の部分51とで線欠陥が生じているとする。図4に示す部分A及びBにおいて修理されていない従来のLCD装置では、欠陥による画素に黒いイメージ又はドットを表示できない。その理由は、液晶分子を図3(B)に示すように整列させる電圧を液晶材料に印加できないからである。

本発明に従うこの方式においては、点欠陥の画素及び線欠陥に含まれる画素の黒イメージは完全に回復されることができる。この完全回復を説明する前に、図8に示されている回路の動作を説明する。制御装置53は、制御線58を介して第1及び第2データ線ドライバ45及び46と第1及び第2ゲート線ドライバ47及び48の動作を制御する。例えばパーソナル・コンピュータのようなホスト・プロセッサ54は、ゲート線に沿った画素ラインのデータ信号をデータ・バスを介してデータ・バッファ55に送る。データ・バッファ55は、白レベル、種々なグレイ・レベル及び黒レベルを表すデータ信号に対応した種々な電圧源を含み、そして第1データ線ドライバ45に対する第1のサブ・バッファA及び第2データ線ドライバ46に対応する第2サブ・バッファBを有する。説明を簡単にするために本明細書においては白レベル及び黒レベルを使用する例が示されていることに注目されたい。サブ・バッファA及びBのそれぞれは、ゲート線に沿った1画素ラインの画素の数に等しい複数のバッファ・ステージを有する。データ・バッファ55はホスト・プロセッサ54から送られた1つのデータ信号に対応する電圧レベルを選択して、これをサブ・バッファA又はBの1つのバッファ・ステージに記憶する。例えば、黒イメージが画素P11に表示される場合には、奇数フレームの間データ・バッファ55は、サブ・バッファAの第1番目のバッファ・ステージに+2.5Vを記憶し、そしてサブ・バッファBの第1番目のバッファ・ステージに−2.5Vを記憶する。このような記憶動作が、サブ・バッファA及びBのすべてのバッファ・ステージについて行われる。上記のデータ・バッファの動作はこの分野で周知であるので、詳細な動作は説明しない。

(B)データ線(D1)上の欠陥(50)の位置(この場合には、ゲート線G2とゲート線G3の間の位置)を表すデータと、この欠陥データ線(D1)が形成されている、上側及び下側ガラス基板の一方を示す識別データ(ビット”1”)とを含むデータ線欠陥情報;及び

(C)ゲート線(G1)上の欠陥(51)の位置(この場合には、データ線D4とデータ線D5との間の位置)を表すデータと、この欠陥ゲート線(G1)が形成されている、上側及び下側ガラス基板の一方を示す識別データ(ビット”1”)とを含むゲート線欠陥情報。

画素P15 :黒

画素P16 :黒

画素P17−P1N: 白

黒イメージを表示する画素は、図3に示すように、上側及び下側ガラス基板22及び23のデータ線相互間への電圧の印加を必要とする。

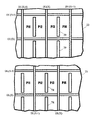

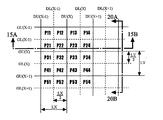

図12及び図13は、本発明の第2実施例の第1即ち上側ガラス基板22上の画素アレイ及び第2即ち下側ガラス基板23上の画素アレイの配列を示す。この第2実施例のLCD装置の構造は、下側ガラス基板23の画素アレイに対する上側ガラス基板22の画素アレイの位置づけを除いて、第1実施例とほぼ同じであることに注目されたい。

画素P12は、ゲート線GU(X−1)及びデータ線DU(X−1)の交点にある上側画素領域の右側半分と、ゲート線GL(X−1)及びデータ線DL(X−1)の交点にある下側画素領域の左側半分とにより構成される。白イメージを表示するには、図3(A)に示すように電圧0Vが液晶材料に印加されねばならない。電圧−2.5Vがデータ線DU(X−1)に印加されているものとする。データ線DL(X−1)に印加される電圧は、データ線DU(X−1)上の電圧の値に基づいて選択されることに注目されたい。従って、図14に示すように、ゲート線GU(X−1)及びGL(X−1)へのゲート・パルスの印加の間、電圧−2.5Vがデータ線DU(X−1)に印加され、そして電圧−2.5Vがデータ線DL(X−1)に印加される。

画素P13は、ゲート線GU(X−1)及びデータ線DU(X)の交点にある上側画素領域の左側半分と、ゲート線GL(X−1)及びデータ線DL(X−1)の交点にある下側画素領域の右側半分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加されねばならない。電圧−2.5Vがデータ線DL(X−1)に印加されているので、データ線DU(X)に印加される電圧は、データ線DL(X−1)上の電圧の値に基づいて選択される。従って、図14に示すように、ゲート線GU(X−1)及びGL(X−1)へのゲート・パルスの印加の間、電圧+2.5Vがデータ線DU(X)に印加され、そして電圧−2.5Vがデータ線DL(X−1)に印加される。

画素P14は、ゲート線GU(X−1)及びデータ線DU(X)の交点にある上側画素領域の右側半分と、ゲート線GL(X−1)及びデータ線DL(X)の交点にある下側画素領域の左側半分とにより構成される。白イメージを表示するには、図3(A)に示すように電圧0Vが液晶材料に印加されねばならない。電圧+2.5Vがデータ線DU(X)に印加されているので、データ線DL(X)に印加される電圧は、データ線DU(X)上の電圧の値に基づいて選択される。従って、図14に示すように、ゲート線GU(X−1)及びGL(X−1)へのゲート・パルスの印加の間、電圧+2.5Vがデータ線DU(X)に印加され、そして電圧+2.5Vがデータ線DL(X)に印加される。

画素P15は、ゲート線GU(X−1)及びデータ線DU(X+1)の交点にある上側画素領域の左側半分と、ゲート線GL(X−1)及びデータ線DL(X)の交点にある下側画素領域の右側半分とにより構成される。白イメージを表示するには、図3(A)に示すように電圧0Vが液晶材料に印加されねばならない。電圧+2.5Vがデータ線DL(X)に印加されているので、データ線DU(X+1)に印加される電圧は、データ線DL(X)上の電圧の値に基づいて選択される。従って、図14に示すように、ゲート線GU(X−1)及びGL(X−1)へのゲート・パルスの印加の間、電圧+2.5Vがデータ線DU(X+1)に印加され、そして電圧+2.5Vがデータ線DL(X)に印加される。

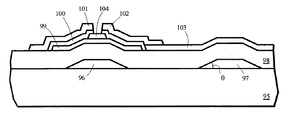

図26に示すような逆スタガ型のTFTが画素領域のスイッチング素子として使用される場合には、MoWにより形成されるゲート線とブラック・マトリクス78(79)が下側又は上側ガラス基板23又は22に同時に形成される。図27に示すようなスタガ型のTFTが画素領域のスイッチング素子として使用される場合には、Mo又はCuにより形成される光遮断層121とブラック・マトリクス122が下側又は上側ガラス基板23又は22上に同時に形成される。更に、複数個のブラック・マトリクスが上側ガラス基板22に形成され、そして各カラー・フィルタは上側データ線とブラック・マトリクスとの間の位置に形成される。

上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の幅(即ちゲート線に沿った長さ)の半分に等しい距離だけ水平方向(ゲート線に沿った方向)にシフトされる。上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し垂直方向(即ち、データ線に沿った方向)にはシフトされない。上側ガラス基板22のデータ線は、下側ガラス基板23のブラック・マトリクス78にそれぞれ対面され、そして下側ガラス基板23のデータ線は上側ガラス基板22のブラック・マトリクス79にそれぞれ対面される。

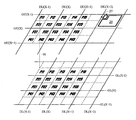

図17及び図18は、本発明の第3実施例の第1即ち上側ガラス基板22上の画素アレイと第2即ち下側ガラス基板23上の画素アレイの配列を示す。この第3実施例のLCD装置の構造は、下側ガラス基板23の画素アレイに対する上側ガラス基板22の画素アレイの位置づけを除いて、第1実施例とほぼ同じであることに注目されたい。

画素P21は、ゲート線GU(X−1)とデータ線DU(X−1)との交点の上側画素領域の下側半分と、ゲート線GL(X−1)とデータ線DL(X−1)との交点の下側画素領域の上側半分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加される。図19に示すように、ゲート・パルスGU(X−1)の後半部分と、ゲート・パルスGL(X−1)の前半部分とにより規定される期間T1の間、電圧+2.5Vがデータ線DU(X−1)に印加されそして電圧−2.5Vがデータ線DL(X−1)に印加される。

画素P31は、ゲート線GU(X)とデータ線DU(X−1)との交点の上側画素領域の上側半分と、ゲート線GL(X−1)とデータ線DL(X−1)との交点の下側画素領域の下側半分とにより構成される。白イメージを表示するには、図3(A)に示すように電圧0Vが液晶材料に印加される。図19に示すように、ゲート・パルスGU(X)の前半部分と、ゲート・パルスGL(X−1)の後半部分とにより規定される期間T2の間、電圧+2.5Vがデータ線DU(X−1)に印加されそして電圧+2.5Vがデータ線DL(X−1)に印加される。

画素P41は、ゲート線GU(X)とデータ線DU(X−1)との交点の上側画素領域の下側半分と、ゲート線GL(X)とデータ線DL(X−1)との交点の下側画素領域の上側半分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加される。図19に示すように、ゲート・パルスGU(X)の後半部分と、ゲート・パルスGL(X)の前半部分とにより規定される期間T3の間、電圧+2.5Vがデータ線DU(X−1)に印加されそして電圧−2.5Vがデータ線DL(X−1)に印加される。

図26に示すような逆スタガ型のTFTが画素領域のスイッチング素子として使用される場合には、MoWにより形成されるゲート線とブラック・マトリクス88(89)が下側又は上側ガラス基板23又は22に同時に形成される。図27に示すようなスタガ型のTFTが画素領域のスイッチング素子として使用される場合には、Mo又はCuにより形成される光遮断層121とブラック・マトリクス122が下側又は上側ガラス基板23又は22上に同時に形成される。更に、複数個のカラー・フィルタが上側ガラス基板22に形成され、そして各カラー・フィルタは上側ゲート線とブラック・マトリクスとの間の位置に形成される。

上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の高さ(即ちデータ線に沿った長さ)の半分に等しい距離だけ垂直方向(データ線に沿った方向)にシフトされる。上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し水平方向(即ち、ゲート線に沿った方向)にはシフトされない。上側ガラス基板22のゲート線は、下側ガラス基板23のブラック・マトリクス88にそれぞれ対面され、そして下側ガラス基板23のゲート線は上側ガラス基板22のブラック・マトリクス89にそれぞれ対面される。

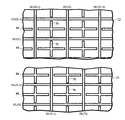

図22及び図23は、本発明の第4実施例の第1即ち上側ガラス基板22上の画素アレイと第2即ち下側ガラス基板23上の画素アレイの配列を示す。この第4実施例のLCD装置の構造は、下側ガラス基板23の画素アレイに対する上側ガラス基板22の画素アレイの位置づけを除いて、第1実施例とほぼ同じであることに注目されたい。

画素P22は、ゲート線GU(X−1)及びデータ線DU(X−1)の交点の上側画素領域の右下の部分と、ゲート線GL(X−1)及びデータ線DL(X−1)の交点の下側画素領域の左上の部分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加される。電圧+2.5Vがデータ線DU(X−1)に印加されているものとする。データ線DL(X−1)に印加される電圧は、データ線DU(X−1)に印加されている電圧に基づいて選択される。従って、図24に示すように、期間T1の間、電圧+2.5Vがデータ線DU(X−1)に印加され、そして電圧−2.5Vがデータ線DL(X−1)に印加される。

画素P23は、ゲート線GU(X−1)及びデータ線DU(X)の交点の上側画素領域の左下の部分と、ゲート線GL(X−1)及びデータ線DL(X−1)の交点の下側画素領域の右上の部分とにより構成される。白イメージを表示するには、図3(A)に示すように電圧0Vが液晶材料に印加される。電圧−2.5Vがデータ線DL(X−1)に印加されているので、期間T1の間、電圧−2.5Vがデータ線DU(X)に印加される。

画素P24は、ゲート線GU(X−1)及びデータ線DU(X)の交点の上側画素領域の右下の部分と、ゲート線GL(X−1)及びデータ線DL(X)の交点の下側画素領域の左上の部分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加される。電圧−2.5Vがデータ線DU(X)に印加されているので、期間T1の間、電圧+2.5Vがデータ線DL(X)に印加される。

画素P25は、ゲート線GU(X−1)及びデータ線DU(X+1)の交点の上側画素領域の左下の部分と、ゲート線GL(X−1)及びデータ線DL(X)の交点の下側画素領域の右上の部分とにより構成される。黒イメージを表示するには、図3(B)に示すように電圧5Vが液晶材料に印加される。電圧+2.5Vがデータ線DL(X)に印加されているので、期間T1の間、電圧−2.5Vがデータ線DU(X+1)に印加される。

図26に示すような逆スタガ型のTFTが画素領域のスイッチング素子として使用される場合には、MoWにより形成されるゲート線とブラック・マトリクス88(89、78,79)が下側又は上側ガラス基板23又は22に同時に形成される。図27に示すようなスタガ型のTFTが画素領域のスイッチング素子として使用される場合には、Mo又はCuにより形成される光遮断層121とブラック・マトリクス122(ブラック・マトリクス88,89,78,79に対応する)が下側又は上側ガラス基板23又は22上に同時に形成される。更に、複数個のカラー・フィルタが上側ガラス基板22に形成される。

上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の幅(即ちゲート線に沿った長さ)の半分に等しい距離だけ水平方向(ゲート線に沿った方向)にシフトされており、そして画素領域の高さ(即ちデータ線に沿った長さ)の半分に等しい距離だけ垂直方向(データ線に沿った方向)にシフトされる。

図29は、上側及び下側ガラス基板22及び23上に形成された構造の断面を示す。この第5実施例においては、VA液晶材料が使用され、ラビング層は使用されず、そして上側及び下側ガラス基板22及び23の位置づけ即ち位置的なシフトは第2実施例と同じである。即ち、上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の幅(即ちゲート線に沿った長さ)の半分に等しい距離だけ水平方向(ゲート線に沿った方向)にシフトされている。上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し垂直方向(即ち、データ線に沿った方向)にはシフトされていない。即ち、上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し垂直方向において整列されている。この整列は、上側ガラス基板22のゲート線を下側ガラス基板23のゲート線に整列させることにより行われる。即ち、上側ガラス基板22のゲート線は下側ガラス基板23のゲート線にそれぞれ整列され、そして上側ガラス基板22の各データ線は、下側ガラス基板23のデータ線相互間の中間位置に整列されている。中間位置は、データ線の中心からLX/2だけ離れている。即ち、上側ガラス基板22のデータ線は、下側ガラス基板23のデータ線に対して、ゲート線に沿った水平方向においてLX/2だけシフトされている。

第6実施例を実現するために、第3実施例の上側及び下側ガラス基板22及び23の配列即ち位置的シフトを使用するように第5実施例が変更されている。即ち、上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の高さ(即ちデータ線に沿った長さ)の半分に等しい距離だけ垂直方向(データ線に沿った方向)にシフトされている。上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し水平方向(即ち、ゲート線に沿った方向)にはシフトされていない。即ち、上側ガラス基板22の各画素領域は下側ガラス基板23の各画素領域に対し水平方向において整列されている。この整列は、上側ガラス基板22のデータ線を下側ガラス基板23のデータ線に整列させることにより行われる。更に具体的にいうと、上側ガラス基板22のデータ線は下側ガラス基板23のデータ線にそれぞれ整列され、そして上側ガラス基板22の各ゲート線は、下側ガラス基板23のゲート線相互間の中間位置に整列されている。この中間位置は、ゲート線の中心からLY/2だけ離れている。即ち、上側ガラス基板22のゲート線は、下側ガラス基板23のゲート線に対して、データ線に沿った垂直方向においてLY/2だけシフトされている。

第7実施例を実現するために、第4実施例の上側及び下側ガラス基板22及び23の配列即ち位置的シフトを使用するように第5実施例が変更されている。即ち、上側ガラス基板22の各画素領域は、下側ガラス基板23の各画素領域に対して、画素領域の幅(即ちゲート線に沿った長さ)の半分に等しい距離だけ水平方向(ゲート線に沿った方向)にシフトされており、そして画素領域の高さ(即ちデータ線に沿った長さ)の半分に等しい距離だけ垂直方向(データ線に沿った方向)にシフトされている。更に具体的にいうと、上側ガラス基板22の各ゲート線は、下側ガラス基板23のゲート線相互間の中間位置に整列され、そして上側ガラス基板22の各データ線は、下側ガラス基板23のデータ線相互間の中間位置に整列されている。ゲート線相互間の中間位置は、ゲート線の中心からLY/2だけ離れており、そしてデータ線相互間の中間位置は、データ線の中心からLX/2だけ離れている。即ち、上側ガラス基板22のゲート線は、下側ガラス基板23のゲート線に対して、データ線に沿った垂直方向においてLY/2だけシフトされており、そして上側ガラス基板22のデータ線は、下側ガラス基板23のデータ線に対して、ゲート線に沿った水平方向においてLX/2だけシフトされている。

22,23・・・ガラス基板

24,25・・・偏光板

26・・・バック・ライト装置

27・・・TFT

29,33・・・ITO層

30,34・・・パッシベーション層

31,36・・・ラビング層

32・・・ブラック・マトリクス

35・・・カラー・フィルタ

38,39,40,41・・・接続パッド

42,43・・・ICモジュール

44・・・封止領域

Claims (31)

- 第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

上記第1透明基板及び上記第2透明基板は、上記第1透明基板の上記第1表面が上記第2透明基板の上記第1表面に対面するように配列されており、そして液晶材料が、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が上記画素領域に印加される画素アレイが、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面とに形成されており、

上記データ線は、上記行及び列方向の一方の方向に配列されており、そして上記ゲート線は、上記行及び列方向の他方の方向に配列されており、そして

上記第1透明基板の上記画素領域のそれぞれは、上記第2透明基板の上記画素領域のそれぞれに対して、上記ゲート線に沿った方向において、該ゲート線に沿った上記画素領域の幅の半分の距離だけシフトされていることを特徴とする液晶表示装置。 - 上記第1透明基板の上記ゲート線は、上記第2透明基板の上記ゲート線にそれぞれ整列されており、そして上記第1透明基板の上記データ線のそれぞれは、上記第2透明基板の上記データ線相互間の中間位置にそれぞれ整列されていることを特徴とする請求項1に記載の液晶表示装置。

- 上記中間位置は、上記データ線の中心からLX/2だけ離れており、ここでLXは、1つのデータ線の中心と次のデータ線の中心との間の距離であることを特徴とする請求項2に記載の液晶表示装置。

- 上記画素アレイの上記画素領域は、上記ゲート線と上記データ線との交点のそれぞれに隣接して形成され、そして上記画素領域は、表示電極と、上記ゲート及びデータ線と上記表示電極との間の接続されたスイッチング素子とを含むことを特徴とする請求項3に記載の液晶表示装置。

- 上記第2透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第1透明基板に形成され、そして上記第1透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第2透明基板に形成されていることを特徴とする請求項1に記載の液晶表示装置。

- 複数個のカラー・フィルタが上記第1透明基板に形成され、そして該カラー・フィルタのそれぞれは、上記データ線と上記ブラック・マトリクスとの間の位置で上記第1透明基板に形成されていることを特徴とする請求項5に記載の液晶表示装置。

- 第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

上記第1透明基板及び上記第2透明基板は、上記第1透明基板の上記第1表面が上記第2透明基板の上記第1表面に対面するように配列されており、そして液晶材料が、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が上記画素領域に印加される画素アレイが、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面とに形成されており、

上記データ線は、上記行及び列方向の一方の方向に配列されており、そして上記ゲート線は、上記行及び列方向の他方の方向に配列されており、そして

上記第1透明基板の上記画素領域のそれぞれは、上記第2透明基板の上記画素領域のそれぞれに対して、上記データ線に沿った方向において、該データ線に沿った上記画素領域の高さの半分の距離だけシフトされていることを特徴とする液晶表示装置。 - 上記第1透明基板の上記データ線は、上記第2透明基板の上記データ線にそれぞれ整列されており、そして上記第1透明基板の上記ゲート線のそれぞれは、上記第2透明基板の上記ゲート線相互間の中間位置にそれぞれ整列されていることを特徴とする請求項7に記載の液晶表示装置。

- 上記中間位置は、上記ゲート線の中心からLY/2だけ離れており、ここでLYは、1つのゲート線の中心と次のゲート線の中心との間の距離であることを特徴とする請求項8に記載の液晶表示装置。

- 上記画素アレイの上記画素領域は、上記ゲート線と上記データ線との交点のそれぞれに隣接して形成され、そして上記画素領域は、表示電極と、上記ゲート及びデータ線と上記表示電極との間の接続されたスイッチング素子とを含むことを特徴とする請求項9に記載の液晶表示装置。

- 上記第2透明基板に形成された1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが上記第1透明基板に形成され、そして上記第1透明基板に形成された1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが上記第2透明基板に形成されていることを特徴とする請求項7に記載の液晶表示装置。

- 複数個のカラー・フィルタが上記第1透明基板に形成され、そして該カラー・フィルタのそれぞれは、上記ゲート線と上記ブラック・マトリクスとの間の位置で上記第1透明基板に形成されていることを特徴とする請求項11に記載の液晶表示装置。

- 第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

上記第1透明基板及び上記第2透明基板は、上記第1透明基板の上記第1表面が上記第2透明基板の上記第1表面に対面するように配列されており、そして垂直配向液晶材料が、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が上記画素領域に印加される画素アレイが、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面とに形成されており、

上記データ線は、上記行及び列方向の一方の方向に配列されており、そして上記ゲート線は、上記行及び列方向の他方の方向に配列されており、そして

上記第1透明基板の上記画素領域のそれぞれは、上記第2透明基板の上記画素領域のそれぞれに対して、上記ゲート線に沿った方向において、該ゲート線に沿った上記画素領域の幅の半分の距離だけシフトされており、そして

上記第2透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第1透明基板に形成され、そして上記第1透明基板に形成された1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第2透明基板に形成されており、上記ブラック・マトリクスのそれぞれは台形状の断面を有することを特徴とする液晶表示装置。 - 上記画素アレイの上記画素領域は、上記ゲート線と上記データ線との交点のそれぞれに隣接して形成され、そして上記画素領域は、表示電極と、上記ゲート及びデータ線と上記表示電極との間の接続されたスイッチング素子とを含むことを特徴とする請求項13に記載の液晶表示装置。

- カラー・フィルタが形成されている別個のガラス基板が、上記第1透明基板の上記第2表面、または上記第2透明基板の上記第2表面に位置づけられていることを特徴とする請求項13に記載の液晶表示装置。

- 第1表面及び第2表面を有する第1透明基板と、

第1表面及び第2表面を有する第2透明基板と、

上記第1透明基板及び上記第2透明基板は、上記第1透明基板の上記第1表面が上記第2透明基板の上記第1表面に対面するように配列されており、そして垂直配向液晶材料が、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面の間に封入されており、

複数個の画素領域が行及び列方向に配列され、そしてデータ線を介してデータ信号が上記画素領域に印加される画素アレイが、上記第1透明基板の上記第1表面と上記第2透明基板の上記第1表面とに形成されており、

上記データ線は、上記行及び列方向の一方の方向に配列されており、そして上記ゲート線は、上記行及び列方向の他方の方向に配列されており、そして

上記第1透明基板の上記画素領域のそれぞれは、上記第2透明基板の上記画素領域のそれぞれに対して、上記データ線に沿った方向において、該データ線に沿った上記画素領域の高さの半分の距離だけシフトされており、そして

上記第2透明基板に形成された1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが上記第1透明基板に形成され、そして上記第1透明基板に形成された1つのゲートにそれぞれ対面する複数個のブラック・マトリクスが上記第2透明基板に形成されており、上記ブラック・マトリクスのそれぞれは台形状の断面を有することを特徴とする液晶表示装置。 - 上記画素アレイの上記画素領域は、上記ゲート線と上記データ線との交点のそれぞれに隣接して形成され、そして上記画素領域は、表示電極と、上記ゲート及びデータ線と上記表示電極との間の接続されたスイッチング素子とを含むことを特徴とする請求項16に記載の液晶表示装置。

- カラー・フィルタが形成されている別個のガラス基板が、上記第1透明基板の上記第2表面、または上記第2透明基板の上記第2表面に位置づけられていることを特徴とする請求項16に記載の液晶表示装置。

- (a)複数個の画素領域が行及び列の方向に配列されそしてデータ線を介してデータ信号が上記画素領域に印加される画素アレイを、1つの透明基板の第1部分及び第2部分に形成するステップと、

(b)上記透明基板を上記第1部分と上記第2部分とに切断するステップと、

(c)上記第1部分の画素アレイと上記第2部分の画素アレイとを対面させるように上記第1部分及び上記第2部分を配列するステップと、

(d)上記第1及び第2部分の上記画素アレイを囲むように、上記第1部分と上記第2部分とを封止領域で接着するステップと、

(e)上記封止領域により囲まれた空間内に液晶材料を充填するステップとを含み、

上記画素アレイにおいて、データ線は上記行及び列方向の一方の方向に配列され、ゲート線は上記行及び列方向の他方の方向に配列され、そして上記画素領域のそれぞれは、上記ゲート線と上記データ線との交点に隣接する領域に形成されており、そして上記画素領域のそれぞれは、表示電極と、上記ゲート線及びデータ線と上記表示電極との間に接続された薄膜トランジスタとを有し、

上記ステップ(c)において、上記第1部分の上記画素領域のそれぞれは、上記第2部分の画素領域のそれぞれに対して、上記ゲート線に沿った方向で、上記ゲート線に沿った上記画素領域の幅の半分の距離だけシフトされることを特徴とする液晶表示装置の製造方法。 - 上記第1部分及び上記第2部分のそれぞれは、上側エッジ、下側エッジ、左側エッジ及び右側エッジを有し、そして

上記ステップ(a)において、上記第1部分のデータ線に接続されているデータ線パッドが、上記第1部分の上側エッジ及び下側エッジの一方に隣接する第1領域に形成され、上記第1部分のゲート線に接続されているゲート線パッドが、上記第1部分の左側エッジ及び右側エッジの一方に隣接する第2領域に形成され、上記第2部分のデータ線に接続されているデータ線パッドが、上記第2部分の上側エッジ及び下側エッジの他方に隣接する第3領域に形成され、そして上記第2部分のゲート線に接続されているゲート線パッドが、上記第2部分の左側エッジ及び右側エッジの他方に隣接する第4領域に形成されることを特徴とする請求項19に記載の液晶表示装置の製造方法。 - 第1データ線ドライバを上記第1領域のデータ線パッドに接続し、第1ゲート線ドライバを上記第2領域のゲート線パッドに接続し、第2データ線ドライバを上記第3領域のデータ線パッドに接続し、そして第2ゲート線ドライバを上記第4領域のゲート線パッドに接続することを特徴とする請求項20に記載の液晶表示装置の製造方法。

- 上記ステップ(c)において、上記第1部分のゲート線を上記第2部分のゲート線に整列させ、上記第1部分のデータ線を上記第2部分のデータ線に整列させるように、上記第1部分及び上記第2部分が配列されることを特徴とする請求項19に記載の液晶表示装置の製造方法。

- 上記ステップ(a)において、上記第2部分の1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第1部分に形成され、そして上記第1部分の1つのデータ線にそれぞれ対面する複数個のブラック・マトリクスが上記第2部分に形成されることを特徴とする請求項19に記載の液晶表示装置の製造方法。

- 上記薄膜トランジスタは逆スタガ型の薄膜トランジスタであり、そして

上記ステップ(a)において、上記逆スタガ型の薄膜トランジスタのゲート電極と上記複数個のブラック・マトリクスとが上記第1及び第2部分に同時に形成されることを特徴とする請求項23に記載の液晶表示装置の製造方法。 - 上記薄膜トランジスタは、ゲート電極の下側に光遮断層を有するスタガ型の薄膜トランジスタであり、そして

上記ステップ(a)において、上記スタガ型の薄膜トランジスタの光遮断層と上記複数個のブラック・マトリクスとが上記第1及び第2部分に同時に形成されることを特徴とする請求項23に記載の液晶表示装置の製造方法。 - 上記ステップ(a)において、複数個のカラー・フィルタが上記第1部分に形成され、そして上記カラー・フィルタのそれぞれは上記データ線と上記ブラック・マトリクスとの間の位置に形成されることを特徴とする請求項19に記載の液晶表示装置の製造方法。

- 上記ステップ(c)において、上記第1部分の上記画素領域のそれぞれは、上記第2部分の画素領域のそれぞれに対して、上記データ線に沿った方向で、上記データ線に沿った上記画素領域の高さの半分の距離だけシフトされることを特徴とする請求項19に記載の液晶表示装置の製造方法。

- 上記ステップ(a)において、上記第2部分の1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが上記第1部分に形成され、そして上記第1部分の1つのゲート線にそれぞれ対面する複数個のブラック・マトリクスが上記第2部分に形成されることを特徴とする請求項19に記載の液晶表示装置の製造方法。

- 上記薄膜トランジスタは逆スタガ型の薄膜トランジスタであり、そして上記ステップ(a)において、上記逆スタガ型の薄膜トランジスタのゲート電極と上記複数個のブラック・マトリクスとが上記第1及び第2部分に同時に形成されることを特徴とする請求項28に記載の液晶表示装置の製造方法。

- 上記薄膜トランジスタは、ゲート電極の下側に光遮断層を有するスタガ型の薄膜トランジスタであり、そして

上記ステップ(a)において、上記スタガ型の薄膜トランジスタの光遮断層と上記複数個のブラック・マトリクスとが上記第1及び第2部分に同時に形成されることを特徴とする請求項28に記載の液晶表示装置の製造方法。 - 上記ステップ(a)において、上記複数個のカラー・フィルタが上記第1部分に形成され、そして上記カラー・フィルタのそれぞれは上記ゲート線と上記ブラック・マトリクスとの間の位置に形成されることを特徴とする請求項19に記載の液晶表示装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009219345A JP4612100B2 (ja) | 2009-09-24 | 2009-09-24 | 液晶表示装置及びこれの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009219345A JP4612100B2 (ja) | 2009-09-24 | 2009-09-24 | 液晶表示装置及びこれの製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP11133355A Division JP2000321600A (ja) | 1999-05-13 | 1999-05-13 | 液晶表示装置及びこれの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010044403A true JP2010044403A (ja) | 2010-02-25 |

| JP4612100B2 JP4612100B2 (ja) | 2011-01-12 |

Family

ID=42015773

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009219345A Expired - Lifetime JP4612100B2 (ja) | 2009-09-24 | 2009-09-24 | 液晶表示装置及びこれの製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4612100B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN115202093A (zh) * | 2021-04-13 | 2022-10-18 | 合肥京东方显示技术有限公司 | 显示面板及其制作方法、显示装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5384597A (en) * | 1976-12-29 | 1978-07-26 | Seiko Epson Corp | Manufacture for display unit |

| JPH01179993A (ja) * | 1988-01-11 | 1989-07-18 | Toshiba Corp | 液晶を用いた表示装置 |

| JPH02242228A (ja) * | 1989-03-16 | 1990-09-26 | Fujitsu Ltd | 液晶表示装置 |

| JPH0338617A (ja) * | 1989-07-05 | 1991-02-19 | Toshiba Corp | 液晶表示装置 |

| JPH0339722U (ja) * | 1989-08-30 | 1991-04-17 | ||

| JPH0850309A (ja) * | 1994-05-31 | 1996-02-20 | Semiconductor Energy Lab Co Ltd | 電気光学装置 |

-

2009

- 2009-09-24 JP JP2009219345A patent/JP4612100B2/ja not_active Expired - Lifetime

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5384597A (en) * | 1976-12-29 | 1978-07-26 | Seiko Epson Corp | Manufacture for display unit |

| JPH01179993A (ja) * | 1988-01-11 | 1989-07-18 | Toshiba Corp | 液晶を用いた表示装置 |

| JPH02242228A (ja) * | 1989-03-16 | 1990-09-26 | Fujitsu Ltd | 液晶表示装置 |

| JPH0338617A (ja) * | 1989-07-05 | 1991-02-19 | Toshiba Corp | 液晶表示装置 |

| JPH0339722U (ja) * | 1989-08-30 | 1991-04-17 | ||

| JPH0850309A (ja) * | 1994-05-31 | 1996-02-20 | Semiconductor Energy Lab Co Ltd | 電気光学装置 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN115202093A (zh) * | 2021-04-13 | 2022-10-18 | 合肥京东方显示技术有限公司 | 显示面板及其制作方法、显示装置 |

| CN115202093B (zh) * | 2021-04-13 | 2024-03-22 | 合肥京东方显示技术有限公司 | 显示面板及其制作方法、显示装置 |

| US12204196B2 (en) | 2021-04-13 | 2025-01-21 | Hefei Boe Display Technology Co., Ltd. | Display panel and method for manufacturing the same, and display device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4612100B2 (ja) | 2011-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7936323B2 (en) | Liquid crystal display device | |

| KR100788392B1 (ko) | 횡전계 방식 액정 표시 장치의 구동방법 | |

| JP4989607B2 (ja) | 静電気防止回路とその製造方法及びこれを具備した液晶表示装置 | |

| JP3730161B2 (ja) | 液晶表示装置 | |

| US6654075B1 (en) | Liquid crystal display device and method for fabricating the same | |

| US8259047B2 (en) | Horizontal stripe liquid crystal display device | |

| TWI386882B (zh) | 液晶顯示面板及其驅動方法以及使用該面板及方法之液晶顯示裝置 | |

| KR101623593B1 (ko) | 액정표시장치 | |

| KR100741894B1 (ko) | 횡전계 방식 액정 표시 장치의 구동방법 | |

| CN101563646A (zh) | 液晶面板、液晶显示装置和电视装置 | |

| GB2464803A (en) | Liquid Crystal Display | |

| CN101685230A (zh) | 液晶面板及装有该液晶面板的液晶显示器 | |

| US20070035687A1 (en) | Display device | |

| US20080284708A1 (en) | Liquid Crystal Display Device | |

| US20120007843A1 (en) | Tft substrate and liquid crystal display apparatus using the same | |

| KR20250020567A (ko) | 이형 액정 표시 패널 | |

| CN106814505B (zh) | 液晶显示装置 | |

| CN101625494B (zh) | 显示装置以及显示装置的驱动方法 | |

| KR101074381B1 (ko) | 횡전계방식 액정표시장치 | |

| JP2011128265A (ja) | 表示装置 | |

| US20190287473A1 (en) | Liquid crystal display device and drive method for same | |

| JP3724163B2 (ja) | 液晶表示素子及び液晶表示装置 | |

| JP4612100B2 (ja) | 液晶表示装置及びこれの製造方法 | |

| KR100640995B1 (ko) | 횡전계형 액정 표시 장치 | |

| WO2022193440A1 (zh) | 显示面板及显示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100316 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100616 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101005 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101014 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |