JP2010039969A - クロストークノイズの判定方法およびプログラム - Google Patents

クロストークノイズの判定方法およびプログラム Download PDFInfo

- Publication number

- JP2010039969A JP2010039969A JP2008205029A JP2008205029A JP2010039969A JP 2010039969 A JP2010039969 A JP 2010039969A JP 2008205029 A JP2008205029 A JP 2008205029A JP 2008205029 A JP2008205029 A JP 2008205029A JP 2010039969 A JP2010039969 A JP 2010039969A

- Authority

- JP

- Japan

- Prior art keywords

- aggressor

- noise

- error

- crosstalk

- error threshold

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

【解決手段】データベースからレイアウトデータを読み込み、各配線の対接地容量と配線間カップリング容量と計算する。また、レイアウトデータのネットからクロストーク解析対象となるビクティム配線を抽出し、抽出した各ビクティム配線に対してアグレッサ配線の本数を求める。その後、クロストークノイズ値を計算した後、アグレッサ本数別エラーしきい値テーブルを読み込み、該アグレッサ本数に応じたエラーしきい値を抽出し、該エラーしきい値と算出したクロストークノイズ値との比較を行い、エラー判定を行う。このように、アグレッサ本数に応じたエラーしきい値を設定することにより、真のエラーを摘出することが可能となる。

【選択図】図2

Description

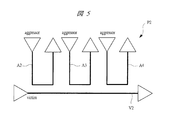

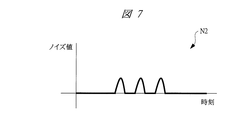

図1は、本発明の実施の形態1による電子システムの一例を示すブロック図、図2は、図1の電子システムによるクロストーク解析処理の一例を示すフローチャート、図3は、クロストークノイズ判定に用いられるアグレッサ本数別エラーしきい値テーブルの一例を示す説明図、図4は、ビクティム配線とアグレッサとの配線パターンの一例を示す説明図、図5は、ビクティム配線とアグレッサとの配線パターンの他の例を示す説明図、図6は、図4、および図5の配線パターンにおけるノイズ波形の一例を示す説明図、図7は、図5の配線パターンにおけるノイズ波形の一例を示す説明図、図8は、図5の配線パターンにおけるノイズ波形の他の例を示す説明図、図9は、アグレッサ本数と実効ノイズ最大値との関係を示す説明図である。

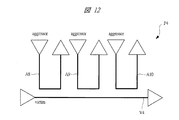

図10は、本発明の実施の形態2によるクロストーク解析処理の一例を示すフローチャート、図11は、ビクティム配線とアグレッサとの配線パターンの一例を示す説明図、図12は、ビクティム配線とアグレッサとの配線パターンの他の例を示す説明図、図13は、図11の配線パターンにおけるノイズ波形の一例を示す説明図、図14は、図12の配線パターンにおけるノイズ波形の一例を示す説明図である。

2 入力部

3 中央制御装置

4 出力部

5 データベース

P1〜P4 レイアウトパターン

N1〜N8 ノイズ波形

V1〜V4 ビクティム配線

A1〜A10 アグレッサ配線

Claims (8)

- レイアウトデータから、クロストーク解析の対象となるノイズを受ける側の配線であるビクティム配線を選択するステップと、

レイアウトデータから、選択した前記ビクティム配線に対してノイズを与える側の配線であるアグレッサ配線の本数を算出するステップと、

前記アグレッサ配線の本数毎に任意に設定された複数のエラーしきい値を有するアグレッサ本数別エラーしきい値テーブルを準備するステップと、

レイアウトデータから、クロストークノイズを算出するステップと、

算出した前記アグレッサ配線の本数に応じたエラーしきい値を前記アグレッサ本数別エラーしきい値テーブルから選択するステップと、

選択した前記エラーしきい値と算出した前記クロストークノイズの値とを比較し、前記エラーしきい値よりも前記クロストークノイズの値が大きい際にエラーと判定し、前記クロストークノイズの値が前記エラーしきい値よりも小さい場合にノーエラーとするクロストークエラー判定を行うステップとを有することを特徴とするクロストークノイズの判定方法。 - 請求項1記載のクロストークノイズの判定方法において、

前記アグレッサ本数別エラーしきい値テーブルにおける前記アグレッサ配線の本数毎のエラーしきい値の設定は、モンテカルロシミュレーションにより算出することを特徴とするクロストークノイズの判定方法。 - レイアウトデータから、クロストーク解析の対象となるノイズを受ける側の配線であるビクティム配線を選択するステップと、

レイアウトデータから、選択した前記ビクティム配線に対してノイズを与える側の配線であるアグレッサ配線の本数を算出するステップと、

前記アグレッサ配線の本数毎に任意に設定された複数のエラーしきい値を有するアグレッサ本数別エラーしきい値テーブルを準備するステップと、

レイアウトデータから、クロストークノイズを算出するステップと、

算出したアグレッサ配線の本数、および各々の前記アグレッサ配線が、前記ビクティム配線に与えるノイズの大きさから、前記アグレッサ配線の本数を補正した実効アグレッサ配線の本数を算出するステップと、

算出した前記実効アグレッサ配線の本数に応じたエラーしきい値を前記アグレッサ本数別エラーしきい値テーブルから選択するステップと、

選択した前記エラーしきい値と算出した前記クロストークノイズの値とを比較し、前記エラーしきい値よりも前記クロストークノイズの値が大きい際にエラーと判定し、前記クロストークノイズの値が前記エラーしきい値よりも小さい場合にノーエラーとするクロストークエラー判定を行うステップとを有することを特徴とするクロストークノイズの判定方法。 - 請求項3記載のクロストークノイズの判定方法において、

前記実効アグレッサ本数の算出は、

算出した各々の前記アグレッサ配線のノイズ値の全体ノイズ値に対する比率を算出し、各々の前記アグレッサ配線が全体ノイズ値に対する割合から実効アグレッサ配線の本数を計算することを特徴とするクロストークノイズの判定方法。 - 半導体集積回路装置の配線パターン設計におけるクロストークノイズの判定をコンピュータシステムに実行させるプログラムであって、

レイアウトデータから、クロストーク解析の対象となるノイズを受ける側の配線であるビクティム配線を選択するステップと、

レイアウトデータから、選択した前記ビクティム配線に対してノイズを与える側の配線であるアグレッサ配線の本数を算出するステップと、

前記アグレッサ配線の本数毎に任意に設定された複数のエラーしきい値を有するアグレッサ本数別エラーしきい値テーブルを準備するステップと、

レイアウトデータから、クロストークノイズを算出するステップと、

算出した前記アグレッサ配線の本数に応じたエラーしきい値を前記アグレッサ本数別エラーしきい値テーブルから選択するステップと、

選択した前記エラーしきい値と算出した前記クロストークノイズの値とを比較し、前記エラーしきい値よりも前記クロストークノイズの値が大きい際にエラーと判定し、前記クロストークノイズの値が前記エラーしきい値よりも小さい場合にノーエラーとするクロストークエラー判定を行うステップとを有することを特徴とするプログラム。 - 請求項5記載のプログラムにおいて、

前記アグレッサ本数別エラーしきい値テーブルにおける前記アグレッサ配線の本数毎のエラーしきい値の設定は、モンテカルロシミュレーションにより算出することを特徴とするプログラム。 - 半導体集積回路装置の配線パターン設計におけるクロストークノイズの判定をコンピュータシステムに実行させるプログラムであって、

レイアウトデータから、クロストーク解析の対象となるノイズを受ける側の配線であるビクティム配線を選択するステップと、

レイアウトデータから、選択した前記ビクティム配線に対してノイズを与える側の配線であるアグレッサ配線の本数を算出するステップと、

前記アグレッサ配線の本数毎に任意に設定された複数のエラーしきい値を有するアグレッサ本数別エラーしきい値テーブルを準備するステップと、

レイアウトデータから、クロストークノイズを算出するステップと、

算出した前記アグレッサ配線の本数、および各々の前記アグレッサ配線が、前記ビクティム配線に与えるノイズの大きさから、前記アグレッサ配線の本数を補正した実効アグレッサ配線の本数を算出するステップと、

算出した前記実効アグレッサ配線の本数に応じたエラーしきい値を前記アグレッサ本数別エラーしきい値テーブルから選択するステップと、

選択した前記エラーしきい値と算出した前記クロストークノイズの値とを比較し、前記エラーしきい値よりも前記クロストークノイズの値が大きい際にエラーと判定し、前記クロストークノイズの値が前記エラーしきい値よりも小さい場合にノーエラーとするクロストークエラー判定を行うステップとを有することを特徴とするプログラム。 - 請求項7記載のプログラムにおいて、

前記実効アグレッサ本数の算出は、

算出した各々の前記アグレッサ配線のノイズ値の全体ノイズ値に対する比率を算出し、各々の前記アグレッサ配線が全体ノイズ値に対する割合から実効アグレッサ本数を計算することを特徴とするプログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008205029A JP5103321B2 (ja) | 2008-08-08 | 2008-08-08 | クロストークノイズの判定方法およびプログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008205029A JP5103321B2 (ja) | 2008-08-08 | 2008-08-08 | クロストークノイズの判定方法およびプログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010039969A true JP2010039969A (ja) | 2010-02-18 |

| JP5103321B2 JP5103321B2 (ja) | 2012-12-19 |

Family

ID=42012406

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008205029A Expired - Fee Related JP5103321B2 (ja) | 2008-08-08 | 2008-08-08 | クロストークノイズの判定方法およびプログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5103321B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013120585A (ja) * | 2011-12-09 | 2013-06-17 | Renesas Electronics Corp | 閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム |

| CN103338007A (zh) * | 2013-06-04 | 2013-10-02 | 上海华力创通半导体有限公司 | 一种噪声处理方法及噪声处理后的电路 |

| CN113836071A (zh) * | 2021-11-26 | 2021-12-24 | 苏州浪潮智能科技有限公司 | 自纠正电路以及信号自纠正方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09147009A (ja) * | 1995-11-24 | 1997-06-06 | Hitachi Ltd | クロストークディレイ決定方法及び平行配線長制限方法 |

| JP2002259486A (ja) * | 2001-02-28 | 2002-09-13 | Fujitsu Ltd | クロストークノイズ解析方法およびその方法をコンピュータに実行させるプログラム |

| JP2003288381A (ja) * | 2002-03-28 | 2003-10-10 | Nec Corp | クロストークノイズ量検証方法及び装置 |

| JP2006171818A (ja) * | 2004-12-13 | 2006-06-29 | Matsushita Electric Ind Co Ltd | クロストーク検証装置およびクロストーク検証方法 |

| JP2008020986A (ja) * | 2006-07-11 | 2008-01-31 | Renesas Technology Corp | クロストーク解析方法 |

-

2008

- 2008-08-08 JP JP2008205029A patent/JP5103321B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09147009A (ja) * | 1995-11-24 | 1997-06-06 | Hitachi Ltd | クロストークディレイ決定方法及び平行配線長制限方法 |

| JP2002259486A (ja) * | 2001-02-28 | 2002-09-13 | Fujitsu Ltd | クロストークノイズ解析方法およびその方法をコンピュータに実行させるプログラム |

| JP2003288381A (ja) * | 2002-03-28 | 2003-10-10 | Nec Corp | クロストークノイズ量検証方法及び装置 |

| JP2006171818A (ja) * | 2004-12-13 | 2006-06-29 | Matsushita Electric Ind Co Ltd | クロストーク検証装置およびクロストーク検証方法 |

| JP2008020986A (ja) * | 2006-07-11 | 2008-01-31 | Renesas Technology Corp | クロストーク解析方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013120585A (ja) * | 2011-12-09 | 2013-06-17 | Renesas Electronics Corp | 閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム |

| CN103338007A (zh) * | 2013-06-04 | 2013-10-02 | 上海华力创通半导体有限公司 | 一种噪声处理方法及噪声处理后的电路 |

| CN113836071A (zh) * | 2021-11-26 | 2021-12-24 | 苏州浪潮智能科技有限公司 | 自纠正电路以及信号自纠正方法 |

| CN113836071B (zh) * | 2021-11-26 | 2022-02-22 | 苏州浪潮智能科技有限公司 | 自纠正电路以及信号自纠正方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5103321B2 (ja) | 2012-12-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20080034338A1 (en) | Timing analysis method and device | |

| US20070136705A1 (en) | Timing analysis method and device | |

| US9443041B2 (en) | Simulation system and method for testing a simulation of a device against one or more violation rules | |

| JP2008250630A (ja) | デカップリングセル配置方法及びデカップリングセル配置装置 | |

| JP2005537566A (ja) | 集積回路においてフィルターされたインターコネクションに関する配線寄生を抽出する方法 | |

| US8595677B1 (en) | Method and system for performing voltage-based fast electrical analysis and simulation of an electronic design | |

| JP2005352787A (ja) | タイミング解析方法およびタイミング解析装置 | |

| JP5103321B2 (ja) | クロストークノイズの判定方法およびプログラム | |

| US7836421B2 (en) | Semiconductor layout design apparatus and method for evaluating a floorplan using distances between standard cells and macrocells | |

| US20040054974A1 (en) | Method and system for power node current waveform modeling | |

| US8843873B1 (en) | Capacitive cell load estimation using electromigration analysis | |

| JP4969416B2 (ja) | 動作タイミング検証装置及びプログラム | |

| JP5071081B2 (ja) | 半導体装置に対する同時動作信号ノイズ見積り方法における同時動作信号ノイズ基礎特性取得方法、及びプログラム | |

| US7185298B2 (en) | Method of parasitic extraction from a previously calculated capacitance solution | |

| JP5304088B2 (ja) | 遅延時間分布を解析する解析方法および解析装置 | |

| US7809542B2 (en) | System and method for glitch analysis in circuits | |

| WO2010125752A1 (ja) | 電源設計システム、電源設計方法、及び電源設計用プログラム | |

| JP2005141434A (ja) | 集積回路のタイミング検証システム、タイミング検証プログラム | |

| JP2008287666A (ja) | 回路動作検証装置、半導体集積回路の製造方法、回路動作検証方法、制御プログラムおよび可読記録媒体 | |

| US9703906B2 (en) | Circuit simulation device, circuit simulation method, and circuit simulation program | |

| US20060047492A1 (en) | Circuit simulation methods and systems | |

| KR102109101B1 (ko) | Ntv 영역에서의 정적 타이밍 분석 방법 및 그 장치 | |

| Qi et al. | Fast decap allocation algorithm for robust on-chip power delivery | |

| JP2006195754A (ja) | 回路動作検証方法、回路動作検証装置及びコンピュータプログラム | |

| JP5332972B2 (ja) | デカップリング容量決定方法、デカップリング容量決定装置およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110317 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120607 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120619 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120815 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120904 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121001 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151005 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |