JP2010039463A - ドット反転駆動システムの極性切換構造 - Google Patents

ドット反転駆動システムの極性切換構造 Download PDFInfo

- Publication number

- JP2010039463A JP2010039463A JP2009005826A JP2009005826A JP2010039463A JP 2010039463 A JP2010039463 A JP 2010039463A JP 2009005826 A JP2009005826 A JP 2009005826A JP 2009005826 A JP2009005826 A JP 2009005826A JP 2010039463 A JP2010039463 A JP 2010039463A

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- type well

- doped region

- switching structure

- polarity switching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3696—Generation of voltages supplied to electrode drivers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D48/00—Individual devices not covered by groups H10D1/00 - H10D44/00

- H10D48/30—Devices controlled by electric currents or voltages

- H10D48/32—Devices controlled by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H10D48/36—Unipolar devices

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- H10P95/92—

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

【解決手段】 ドット反転駆動システムの極性切換構造は、第一トランジスタと第二トランジスタがどちらもP型ウェルに設置され、N型ウェルはP型ウェル内に設置して第一トランジスタと第二トランジスタの間に位置する。N型ウェルは第三トランジスタと第四トランジスタを含み、そのうち、第三トランジスタの一端は第一トランジスタの一端を結合して第一入力端を形成する。第四トランジスタの一端は第二トランジスタの一端を結合して第二入力端を形成する。更に第一トランジスタの別一端、第二トランジスタの別一端、第三トランジスタの別一端及び第四トランジスタの別一端は相互に結合して一出力端を形成する。

【選択図】図7

Description

11 第二ガンマ(Gamma)回路

12 第一デジタル-アナログ変換モジュール

13 第二デジタル-アナログ変換モジュール

14 メモリー

16 切換モジュール

160 切換回路

161 P型ウェル

162 第一トランジスタ

1620 第一ゲート酸化層

1622 第一N型ドープ領域

1624 第二N型ドープ領域

163 第二トランジスタ

1630 第二ゲート酸化層

1632 第三N型ドープ領域

1634 第四N型ドープ領域

164 N型ウェル

165 第三トランジスタ

1650 第三ゲート酸化層

1652 第一P型ドープ領域

1654 第二P型ドープ領域

166 第四トランジスタ

1660 第四ゲート酸化層

1662 第三P型ドープ領域

1664 第四P型ドープ領域

167 基底

168 隔離層

Claims (14)

- P型ウェルと、

P型ウェルに設置した第一トランジスタと、

P型ウェルに設置した第二トランジスタと、

P型ウェル内に設置し、該第一トランジスタと該第二トランジスタの間に位置するN型ウェルと、

N型ウェルの一端に設置し、一端は第一トランジスタの一端を結合して第一入力端を形成する第三トランジスタと、

N型ウェルに設置し、一端は第二トランジスタの一端を結合して第二入力端を形成する第四トランジスタを含むドット反転駆動システムの極性切換構造において、そのうち、

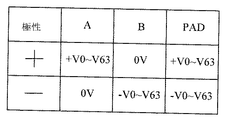

該第一トランジスタの別一端、該第二トランジスタの別一端、該第三トランジスタの別一端と該第四トランジスタの別一端は相互に結合して出力端を形成することを特徴とするドット反転駆動システムの極性切換構造。 - 前記第一入力端は、第一入力信号を受信し、該第二入力端は第二入力信号を受信し、該第一入力信号が第一入力範囲にある時、該第二入力信号は低レベル信号であることを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

- 前記第一入力範囲は、0〜5ボルトであることを特徴とする請求項2記載のドット反転駆動システムの極性切換構造。

- 前記第一入力端は第一入力信号を受信し、該第二入力端が第二入力信号を受信し、該第二入力信号が第二入力範囲にある時、該第一入力信号は低レベル信号となることを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

- 前記第二入力範囲は、0〜5ボルトであることを特徴とする請求項4記載のドット反転駆動システムの極性切換構造。

- 前記第一トランジスタは、

該P型ウェルの上方に位置するゲート酸化層と、

該P型ウェル内に位置し該ゲート酸化層の一側辺に位置する第一N型ドープ領域と、

P型ウェル内に位置し、更に該ゲート酸化層の別一側辺に位置する第二N型ドープ領域を含み、そのうち、

該第一N型ドープ領域は該第三トランジスタを結合し、該第二N型ドープ領域は該第二トランジスタ、該第三トランジスタ及び該第四トランジスタを結合することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。 - 前記第二トランジスタは、

該P型ウェルの上方に位置するゲート酸化層と、

該P型ウェル内に位置し該ゲート酸化層の一側辺に位置する第一N型ドープ領域と、

P型ウェル内に位置し、更に該ゲート酸化層の別一側辺に位置する第二N型ドープ領域を含み、そのうち、

該第一N型ドープ領域は該第四トランジスタを結合し、該第二N型ドープ領域は該第一トランジスタ、該第三トランジスタ及び該第四トランジスタを結合することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。 - 前記第三トランジスタは、

該N型ウェルの上方に位置するゲート酸化層と、

該N型ウェル内に位置し該ゲート酸化層の一側辺に位置する第一P型ドープ領域と、

N型ウェル内に位置し、更に該ゲート酸化層の別一側辺に位置する第二P型ドープ領域を含み、そのうち、

該第一P型ドープ領域は該第一トランジスタを結合し、該第二P型ドープ領域は該第一トランジスタ、該第二トランジスタ及び該第四トランジスタを結合することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。 - 前記第四トランジスタは、

該N型ウェルの上方に位置するゲート酸化層と、

該N型ウェル内に位置し該ゲート酸化層の一側辺に位置する第一P型ドープ領域と、

N型ウェル内に位置し、更に該ゲート酸化層の別一側辺に位置する第二P型ドープ領域を含み、そのうち、

該第一P型ドープ領域は該第二トランジスタを結合し、該第二P型ドープ領域は該第一トランジスタ、該第二トランジスタ及び該第三トランジスタを結合することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。 - 前記極性切換構造は、更に

該P型ウェルの下方に位置する基底と、

該基底と該P型ウェルの間に位置する隔離層を含むことを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。 - 前記出力端は、出力パッド(output pad)を結合することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

- 前記第一トランジスタ、第二トランジスタ、第三トランジスタ及び第四トランジスタは、モス電界効果トランジスタ(MOSFET)とすることを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

- 前記第一トランジスタと第三トランジスタは、相補型MOS(CMOS)を形成することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

- 前記第二トランジスタと第四トランジスタは、相補型MOS(CMOS)を形成することを特徴とする請求項1記載のドット反転駆動システムの極性切換構造。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW097129091 | 2008-07-31 | ||

| TW97129091A TWI474305B (zh) | 2008-07-31 | 2008-07-31 | The polarity switching structure of point conversion system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010039463A true JP2010039463A (ja) | 2010-02-18 |

| JP4839383B2 JP4839383B2 (ja) | 2011-12-21 |

Family

ID=41607684

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009005826A Active JP4839383B2 (ja) | 2008-07-31 | 2009-01-14 | ドット反転駆動システムの極性切換構造 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8710571B2 (ja) |

| JP (1) | JP4839383B2 (ja) |

| KR (1) | KR101044882B1 (ja) |

| TW (1) | TWI474305B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9143148B2 (en) | 2013-03-26 | 2015-09-22 | Seiko Epson Corporation | Amplification circuit, source driver, electrooptical device, and electronic device |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105096859A (zh) * | 2015-07-29 | 2015-11-25 | 深圳市华星光电技术有限公司 | 一种液晶显示器的驱动方法及装置 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000516769A (ja) * | 1996-08-16 | 2000-12-12 | ノースロップ グラマン コーポレーション | 超低電力―遅延積nnn/pppロジック装置 |

| JP2002158293A (ja) * | 2000-11-16 | 2002-05-31 | Sharp Corp | 半導体装置及び携帯電子機器 |

| JP2002209375A (ja) * | 2001-01-10 | 2002-07-26 | Seiko Epson Corp | 電圧変換回路 |

| JP2006292807A (ja) * | 2005-04-06 | 2006-10-26 | Renesas Technology Corp | 液晶表示駆動用半導体集積回路 |

| JP2007003563A (ja) * | 2005-06-21 | 2007-01-11 | Nec Electronics Corp | 液晶表示装置の駆動回路 |

| WO2008076406A2 (en) * | 2006-12-14 | 2008-06-26 | Ion Torrent Systems Incorporated | Methods and apparatus for measuring analytes using large scale fet arrays |

| US20080316076A1 (en) * | 2007-06-19 | 2008-12-25 | Telefonaktiebolaget Lm Ericsson (Publ) | Direct RF D-to-A Conversion |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA1040321A (en) * | 1974-07-23 | 1978-10-10 | Alfred C. Ipri | Polycrystalline silicon resistive device for integrated circuits and method for making same |

| US5028978A (en) * | 1990-09-27 | 1991-07-02 | Hall John H | Complementary bipolar complementary CMOS (CBiCMOS) transmission gate |

| US5994755A (en) * | 1991-10-30 | 1999-11-30 | Intersil Corporation | Analog-to-digital converter and method of fabrication |

| JP3417514B2 (ja) * | 1996-04-09 | 2003-06-16 | 株式会社日立製作所 | 液晶表示装置 |

| US6100557A (en) * | 1996-10-10 | 2000-08-08 | Macronix International Co., Ltd. | Triple well charge pump |

| KR100223671B1 (ko) * | 1996-12-06 | 1999-10-15 | 윤종용 | 다중 전원전압을 가지는 반도체 메모리 장치 |

| JPH11133926A (ja) * | 1997-10-30 | 1999-05-21 | Hitachi Ltd | 半導体集積回路装置および液晶表示装置 |

| KR100304502B1 (ko) * | 1998-03-27 | 2001-11-30 | 김영환 | 액정표시장치 소스구동회로 |

| KR100268904B1 (ko) * | 1998-06-03 | 2000-10-16 | 김영환 | Tft-lcd 구동 회로 |

| WO2000016153A1 (en) * | 1998-09-10 | 2000-03-23 | Seiko Epson Corporation | Substrate for liquid crystal panel, liquid crystal panel, electronic apparatus comprising the panel, and method for manufacturing substrate for liquid crystal panel |

| WO2000045437A1 (en) * | 1999-01-26 | 2000-08-03 | Hitachi, Ltd. | Method of setting back bias of mos circuit, and mos integrated circuit |

| JP2002033451A (ja) * | 2000-07-14 | 2002-01-31 | Fujitsu Ltd | 半導体集積回路 |

| JP3506235B2 (ja) * | 2000-08-18 | 2004-03-15 | シャープ株式会社 | 液晶表示装置の駆動装置および駆動方法 |

| JP4049988B2 (ja) * | 2000-11-24 | 2008-02-20 | 株式会社東芝 | 論理回路 |

| CN1212598C (zh) * | 2001-04-26 | 2005-07-27 | 凌阳科技股份有限公司 | 液晶显示器的源驱动放大器 |

| TW548835B (en) * | 2001-08-30 | 2003-08-21 | Sony Corp | Semiconductor device and production method thereof |

| TW569444B (en) * | 2001-12-28 | 2004-01-01 | Sanyo Electric Co | Charge pump device |

| JP2003197791A (ja) * | 2001-12-28 | 2003-07-11 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP2003197790A (ja) * | 2001-12-28 | 2003-07-11 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP4155396B2 (ja) * | 2002-12-26 | 2008-09-24 | 株式会社 日立ディスプレイズ | 表示装置 |

| US7342566B2 (en) * | 2003-03-04 | 2008-03-11 | Lg.Philips Lcd Co., Ltd. | Liquid crystal display device and driving method thereof |

| US6970033B1 (en) * | 2003-11-26 | 2005-11-29 | National Semiconductor Corporation | Two-by-two multiplexer circuit for column driver |

| US7027316B2 (en) * | 2003-12-29 | 2006-04-11 | Micron Technology, Inc. | Access circuit and method for allowing external test voltage to be applied to isolated wells |

| JP4847702B2 (ja) * | 2004-03-16 | 2011-12-28 | ルネサスエレクトロニクス株式会社 | 表示装置の駆動回路 |

| JP4584131B2 (ja) * | 2005-04-18 | 2010-11-17 | ルネサスエレクトロニクス株式会社 | 液晶表示装置及びその駆動回路 |

| US7330066B2 (en) * | 2005-05-25 | 2008-02-12 | Himax Technologies Limited | Reference voltage generation circuit that generates gamma voltages for liquid crystal displays |

| US7368789B1 (en) * | 2005-06-13 | 2008-05-06 | Actel Corporation | Non-volatile programmable memory cell and array for programmable logic array |

| TWI285362B (en) * | 2005-07-12 | 2007-08-11 | Novatek Microelectronics Corp | Source driver and the internal data transmission method thereof |

| WO2007047429A1 (en) * | 2005-10-12 | 2007-04-26 | Spinnaker Semiconductor, Inc. | A cmos device with zero soft error rate |

| US7298010B1 (en) * | 2006-02-21 | 2007-11-20 | Sandia Corporation | Radiation-hardened transistor and integrated circuit |

| US7443231B2 (en) * | 2006-08-09 | 2008-10-28 | Elite Semiconductor Memory Technology Inc. | Low power reference voltage circuit |

| EP1895545B1 (en) * | 2006-08-31 | 2014-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| JP2008170993A (ja) * | 2007-01-15 | 2008-07-24 | Lg Display Co Ltd | 液晶表示装置とその駆動方法 |

| TW201001911A (en) * | 2008-06-18 | 2010-01-01 | Genesys Logic Inc | Transmission gate with body effect compensation circuit |

-

2008

- 2008-07-31 TW TW97129091A patent/TWI474305B/zh active

-

2009

- 2009-01-14 JP JP2009005826A patent/JP4839383B2/ja active Active

- 2009-06-17 US US12/486,340 patent/US8710571B2/en active Active

- 2009-07-30 KR KR1020090069884A patent/KR101044882B1/ko active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000516769A (ja) * | 1996-08-16 | 2000-12-12 | ノースロップ グラマン コーポレーション | 超低電力―遅延積nnn/pppロジック装置 |

| JP2002158293A (ja) * | 2000-11-16 | 2002-05-31 | Sharp Corp | 半導体装置及び携帯電子機器 |

| JP2002209375A (ja) * | 2001-01-10 | 2002-07-26 | Seiko Epson Corp | 電圧変換回路 |

| JP2006292807A (ja) * | 2005-04-06 | 2006-10-26 | Renesas Technology Corp | 液晶表示駆動用半導体集積回路 |

| JP2007003563A (ja) * | 2005-06-21 | 2007-01-11 | Nec Electronics Corp | 液晶表示装置の駆動回路 |

| WO2008076406A2 (en) * | 2006-12-14 | 2008-06-26 | Ion Torrent Systems Incorporated | Methods and apparatus for measuring analytes using large scale fet arrays |

| US20080316076A1 (en) * | 2007-06-19 | 2008-12-25 | Telefonaktiebolaget Lm Ericsson (Publ) | Direct RF D-to-A Conversion |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9143148B2 (en) | 2013-03-26 | 2015-09-22 | Seiko Epson Corporation | Amplification circuit, source driver, electrooptical device, and electronic device |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI474305B (zh) | 2015-02-21 |

| KR101044882B1 (ko) | 2011-06-28 |

| KR20100014152A (ko) | 2010-02-10 |

| US8710571B2 (en) | 2014-04-29 |

| TW201005720A (en) | 2010-02-01 |

| JP4839383B2 (ja) | 2011-12-21 |

| US20100026356A1 (en) | 2010-02-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI404039B (zh) | 液晶顯示裝置 | |

| KR101323090B1 (ko) | 액정표시장치와 그 구동방법 | |

| KR100272723B1 (ko) | 평면표시장치 | |

| CN101000414B (zh) | 液晶显示器 | |

| KR101330415B1 (ko) | 액정표시장치와 그 구동방법 | |

| US7800705B2 (en) | Liquid crystal display having electrically floating thin film transistor within sub pixel unit | |

| US20110122055A1 (en) | Liquid crystal display with double data lines | |

| CN116250032B (zh) | 显示面板和显示装置 | |

| WO2014000381A1 (zh) | 阵列基板、显示装置和驱动所述阵列基板的方法 | |

| JP2008033312A (ja) | 画像表示システムとその駆動方法 | |

| KR100440360B1 (ko) | 액정표시장치및그구동방법 | |

| TWI412852B (zh) | 具有電荷分享架構之顯示面板之畫素結構及其驅動方法 | |

| CN101004502A (zh) | 液晶显示器结构 | |

| KR101585687B1 (ko) | 액정표시장치 | |

| US7307612B2 (en) | Liquid crystal display device having drive circuit | |

| CN111009224A (zh) | 显示面板的驱动方法、显示装置 | |

| US20050110739A1 (en) | Method of driving gates of liquid crystal display | |

| US7969403B2 (en) | Driving circuit, driving method, and liquid crystal display using same | |

| KR20040021384A (ko) | 액정표시장치용 액정패널의 하부어레이기판 | |

| JP4839383B2 (ja) | ドット反転駆動システムの極性切換構造 | |

| KR20040061205A (ko) | 액정표시장치 및 그 구동방법 | |

| TW591576B (en) | Active matrix display device | |

| KR101604481B1 (ko) | 액정표시장치 | |

| CN101281330A (zh) | 液晶显示器及其显示面板 | |

| TW200820183A (en) | Method for driving LCD monitors |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110817 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110920 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111003 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141007 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4839383 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20161007 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |