JP2010035252A - 電力変換装置 - Google Patents

電力変換装置 Download PDFInfo

- Publication number

- JP2010035252A JP2010035252A JP2008191598A JP2008191598A JP2010035252A JP 2010035252 A JP2010035252 A JP 2010035252A JP 2008191598 A JP2008191598 A JP 2008191598A JP 2008191598 A JP2008191598 A JP 2008191598A JP 2010035252 A JP2010035252 A JP 2010035252A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- phase inverter

- phase

- drive signal

- power converter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

- H02M7/487—Neutral point clamped inverters

Landscapes

- Inverter Devices (AREA)

Abstract

【解決手段】3相インバータ1の上アームのスイッチング素子12aがオフする場合は、相電圧切り換えのタイミングがT2m遅れるので、それを見越して、スイッチング素子オフの信号をT2m早めて出力する。一方、単相インバータ2の相電圧切り換えのタイミングは、(Tds+T1s)遅れるので、(Tds+T1s)早めてスイッチング素子18a、18dオフの信号を出力する。これにより、3相インバータ1、単相インバータ2の相電圧切り換えのタイミングが揃い、同時に、電圧が切り換わるので、3相インバータ1と単相インバータ2とを合わせた相電圧にサージ電圧が生じず、負荷3の電圧にもサージ電圧が生じない。

【選択図】図14

Description

第1の電力変換器のスイッチング素子を駆動する第1の駆動信号と第2の電力変換器のスイッチング素子を駆動する第2の駆動信号とを作成する駆動信号生成回路を備えた電力変換装置において、

第1の電力変換器の交流出力電圧を上昇または下降させるタイミングで第2の電力変換器の交流出力電圧を下降または上昇させるため、第1および第2の駆動信号として作成された第1および第2の指令駆動信号に対し、第1の電力変換器の交流出力電圧が実際に上昇または下降する電圧変化タイミングと第2の電力変換器の交流出力電圧が実際に下降または上昇する電圧変化タイミングとが同一の同期電圧変化タイミングとなるよう第1および第2の指令駆動信号を補正して第1および第2の補正駆動信号を出力する駆動信号補正手段を備えたものである。

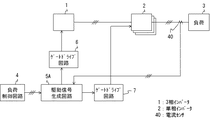

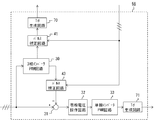

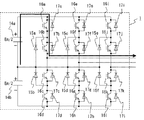

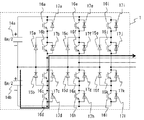

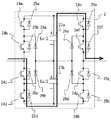

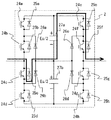

図1は、この発明の実施の形態1における電力変換装置の全体構成を示す図である。図に示すように、電力変換装置の主回路構成としては、第1の電力変換器である3相インバータ1の交流側の各相出力線に、第2の電力変換器である単相インバータ2の交流側が直列に接続される。単相インバータ2の交流側は、その片方を3相インバータ1に、残る片方を負荷3にそれぞれ接続する。図1では省略しているが、3相インバータ1は直流電圧源を備え、そこから電力の供給を受けるものとする。単相インバータ2は、直流側に直流電圧源を備えそこから電力の供給を受ける構成でも、電力は3相インバータ1から供給を受け単相インバータ2の直流電圧を制御することによって維持する構成でもよい。

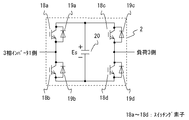

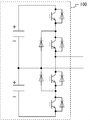

単相インバータ2は、図3に示すようなスイッチング素子18a〜18d、ダイオード19a〜19d、およびコンデンサ20から構成される単相フルブリッジの2レベルインバータである。

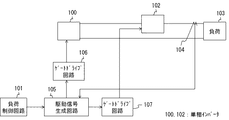

図4の負荷制御回路4は、負荷3を制御するための回路で、電力変換装置が出力する電圧の指令(交流電圧指令)を出力する。これを駆動信号生成回路5に入力する。

減算器31では、負荷制御回路4が出力する交流電圧指令と、3相インバータ1のPWM回路30が出力するPWMされた電圧波形との減算を行い偏差指令を作成する。この結果求められる波形は、図6(c)に示すようになる。この波形は、3相インバータ1の理想的な電圧である交流電圧指令から、実際に出力している電圧を減算しているので、3相インバータ1が出力している電圧のうち、余剰な高調波電圧を正負反転させたものである。よって、この電圧波形を指令として単相インバータ2から電圧を出力すると、3相インバータ1が出力する余剰な高調波電圧を打ち消すように単相インバータ2が動作するので、負荷3の電圧高調波を低減できる。

図6(d)をPWMすると、図6(e)に示すような波形となる。負荷3の相電圧は、3相インバータ1と単相インバータ2との電圧を加算して零相電圧を除いたものであり、図6(f)に示す波形となる。

2レベルインバータの場合、上アームと下アームとのスイッチング素子が交互にオンする。しかし、例えば、上アームのスイッチング素子をオフに切り換える駆動信号と下アームのスイッチング素子をオンに切り換える駆動信号とが同時に制御装置から出力されたとしても、ゲートドライブ回路やスイッチング素子に遅れがあり、遅れの量がオンの場合とオフの場合に異なるので上アームのスイッチング素子と下アームのスイッチング素子とが同時に切り換わらない。このときに両方のスイッチング素子が同時にオン状態になると直流回路が短絡してしまうため、通常オンの信号を数マイクロ秒遅れさせて上アームと下アームとのスイッチング素子が両方ともオフとなる期間を作る。これを短絡防止時間と呼ぶ。

上アームのスイッチング素子がオンの間はスイッチング素子のコレクタ、エミッタ間電圧VCEは0である。制御回路から出力する駆動信号がオフに切り換わるとT2遅れてスイッチング素子がオフになる。また、上アームのスイッチング素子がオフになる駆動信号が出てから下アームのスイッチング素子がオンになる駆動信号が出るまでにTdの遅れがあり、さらに、下アームのスイッチング素子がオンするまでT1の遅れがあるので、上アームのスイッチング素子がオフする駆動信号が出力されてから(Td+T1)遅れてオンする。

以上のように、実際の電圧波形は、Td、T1、T2があるため、駆動信号のオン・オフとはタイミングがずれる上に、さらに電流の方向によって異なる電圧となる。

図8は、3相インバータ1が図2の回路であるとした場合の、1相の電流経路を表している。図2の回路の直流電圧をEmとし、この直流回路の仮想中性点から3相インバータ1が交流側に出力する電圧を見ると、出力電圧は、Em/2または−Em/2のいずれかとなる。

3相インバータ1が出力する電流が負荷に向かって正の方向であるとすると、3相インバータ1の出力電圧がEm/2である場合は、図8(a)の太線で示す経路で矢印の方向に電流が流れる。即ち、上アームのスイッチング素子12aに電流が流れる。一方、図8(a)からスイッチングしてスイッチング素子12aがオフ、12bがオンすると3相インバータ1の出力電圧が−Em/2に切り換わり、図8(b)に太線で示す経路で電流が流れるので、下アームのダイオード13bに電流が流れる。

よって、3相インバータ1でスイッチング素子12aからダイオード13bに電流が転流すると、単相インバータ2ではダイオード19a〜19dのいずれかから反対側のアームにあるスイッチング素子18a〜18dに電流が転流する。

3相インバータ1の短絡防止時間をTdm、駆動信号生成回路5が駆動信号をオンにしてから実際にスイッチング素子がオンするまでの遅延時間をT1m、駆動信号生成回路5が駆動信号をオフにしてから実際に素子がオフするまでの遅延時間をT2mとする。また、単相インバータ2については、その短絡防止時間をTds、駆動信号生成回路5が駆動信号をオンにしてから実際にスイッチング素子がオンするまでの遅延時間をT1s、駆動信号生成回路5が駆動信号をオフにしてから実際に素子がオフするまでの遅延時間をT2sとする。

駆動信号生成回路5は、3相インバータ1のスイッチング素子12aがオフする信号を出力すると同時に単相インバータ2のスイッチング素子18a、18dがオフする信号を出力する。その後、駆動信号生成回路5は、3相インバータ1、単相インバータ2のオフするアームと反対側のアームのスイッチング素子をオンする指令を出すが、3相インバータ1はTdm、単相インバータ2はTds遅れてオンする信号を出す。

また、図10(c)(d)(e)の破線は、電流が負荷3に向かって負の方向に流れている場合の電圧波形である。この場合は、図10(e)の合成相電圧では正の方向にサージ電圧が生じる。

また、単相インバータ2の電圧切り換えが他のパターンでも、同様にダイオードから反対側アームのスイッチング素子への転流なので単相インバータ2の電圧切り換えが(Tds+T1s)遅れる。よって、3相インバータ1と単相インバータ2との電圧切り換えにタイミングのずれが発生し、電圧の変化幅は異なるが電流の方向が同じなら上記のタイミングは図9(a)から(b)に切り換わる場合と同じである。

また、3相インバータ1の電圧が逆に切り換わる場合も、同様に3相インバータ1と単相インバータ2との電圧が切り換わるタイミングのずれが生じる。

図1に戻り、単相インバータ2、負荷3間あるいは3相インバータ1、単相インバータ2間に電流センサ40を設け、計測した電流値を駆動信号生成回路5Aに入力する。

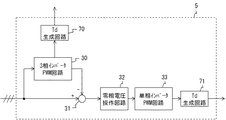

駆動信号生成回路5Aは、図13に示すように、PWMパターン記憶回路46で構成する。

PWMパターン記憶回路46は、電圧切換動作の種別毎に、3相インバータ1や単相インバータ2のスイッチング素子をオンオフするための駆動信号のパターンを記憶しておき、負荷制御回路4からの電圧指令値と電流センサ40で計測した電流に応じて、記憶しているパターンから最適なパターンを出力する。

図14は、負荷3に向かって電流が正の方向に流れている場合の駆動信号生成回路5Aの出力と3相インバータ1の相電圧、単相インバータ2の相電圧および3相インバータ1と単相インバータ2の相電圧を合わせた相電圧波形を示すものである。実線が、本実施の形態1のパルス補正を行った場合の各波形であり、上述した第1および第2の補正駆動信号に相当する。破線は、補正を行わない場合の波形で、上述の第1および第2の指令駆動信号に相当する。補正を行っていない場合は、先の図10の実線と同じである。

負荷3に向かって正の方向に電流が流れていて、3相インバータ1の上アームのスイッチング素子12aがオフする場合は、相電圧切り換えのタイミングがT2m遅れるので、それを見越して、図14(a)に実線で示すように、スイッチング素子オフの信号をT2m早めて出力する。一方、単相インバータ2の相電圧切り換えのタイミングは、(Tds+T1s)遅れるので、図14(b)に実線で示すように、(Tds+T1s)早めてスイッチング素子18a、18dオフの信号を出力する。これにより実際の電圧切り換えのタイミングが、理想的なタイミングになる。よって、3相インバータ1、単相インバータ2の相電圧切り換えのタイミングが揃い、同時に、電圧が切り換わるので、3相インバータ1と単相インバータ2とを合わせた相電圧にサージ電圧が生じず、負荷3の電圧にもサージ電圧が生じない。

駆動信号を早めることにより、電圧切り換えのタイミングを理想のタイミングに合わせることは先の実施の形態1と同じであるが、実施の形態1とは異なる駆動信号補正手段の例を、実施の形態2として以下に説明する。

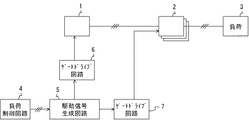

図16は、この発明の実施の形態2における電力変換装置の全体構成を示す図である。図17は、図16の駆動信号生成回路5Bの内部構成を示す図である。

図17は、先の図5の駆動信号生成回路5に、パルス補正回路44とパルス補正回路45とを追加し、パルス補正回路44には3相インバータPWM回路30が出力する駆動信号と電流センサ40で計測する電流値とを入力するようにしたものである。また、パルス補正回路45には、単相インバータPWM回路33が出力する駆動信号と電流センサ40で計測する電流値とを入力する。

パルス補正回路44、パルス補正回路45で遅延させている時間内では、駆動信号を修正して早めることが可能であるので、図14、図15で示したと同様の補正が可能となるわけである。また、パルス補正回路44、45で遅延させる時間は等しいものとする。

負荷制御回路52中の負荷制御回路4Aは、先の図4の負荷制御回路4の交流電圧指令を演算するために用いる出力電圧の角周波数と位相を出力するようにしたものである。進み時間設定値と負荷制御回路4Aが出力した角周波数とを乗算器50で乗算し、進み時間設定値で設定されている時間で回転する位相を求める。これを加算器51で負荷制御回路4Aが出力する位相に加算する。これは、進み時間設定値で設定した時間の分、未来の位相を求めていることになる。加算器51の出力を負荷制御回路4Aに入力する。負荷制御回路4Aでは、負荷制御の演算は先の負荷制御回路4と同じ現在の位相で行うが、出力する電圧指令の位相は、加算器51が出力する進み時間設定値だけ未来の位相での値を演算して出力する。この進み時間設定値は、パルス補正回路44、45で遅延させる時間と同じにする。

従って、3相インバータ1と単相インバータ2との電圧切り換えのタイミングが揃い、3相インバータ1と単相インバータ2とを合わせた相電圧の、各インバータの短絡防止時間、ゲート回路の特性やスイッチング素子の特性に起因するサージ電圧を抑制できる。

また、実施の形態1のように、あらかじめ電圧指令や電流の向きに合わせて駆動信号のパターンを大量に演算、記憶する必要がないので、構成が簡便となる。

本実施の形態3では、まずパルス(駆動信号)を補正する他の方法について説明する。

図19は、電流が負荷3に向かって正の方向に流れていて、3相インバータ1が、先の図8(a)から(b)、単相インバータ2が、先の図9(a)から(b)に切り換わるときの波形を示し、破線は補正を行わない場合で、実線は本実施の形態3の補正を行った場合である。

本実施の形態3では、電流が負荷3に向かって正の方向に流れている場合は、図19(a)のように、後述する駆動信号生成回路5Bが出力する3相インバータ1のスイッチング素子12aをオフさせる駆動信号を(Tds+T1s−T2m)遅れさせて出力する。単相インバータ2のスイッチング素子18a、18dをオフさせる指令はそのままのタイミングで出力する。

本実施の形態4は、3相インバータ1自体に先のものとは異なる構成のものも適用し得ることを示すものである。即ち、3相インバータ1が、図22に示す、3相の3レベルインバータであっても、先の実施の形態1〜3と同様の方法により、3相インバータ1と単相インバータ2との電圧切り換えのずれを補正して電圧サージを抑制できる。

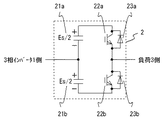

本実施の形態5は、単相インバータ2自体に先のものとは異なる構成のものも適用し得ることを示すものである。即ち、単相インバータ2が、図26に示すような2レベルハーフブリッジの回路のものであっても先の実施の形態1〜3と同様の方法により、3相インバータ1と単相インバータ2との電圧切り換えのずれを補正して電圧サージを抑制できる。

更に、単相インバータ2が、図28に示すような、3レベルフルブリッジのインバータであっても、先の実施の形態1〜3と同様の方法により、3相インバータ1と単相インバータ2との電圧切り換えのタイミングずれを補正して電圧サージを抑制できる。

図35から図31に切り換わる場合は、ダイオード25b、25aからスイッチング素子24c、24dに転流し、ダイオード26c、スイッチング素子24fからダイオード25h、25gに転流する。この時の3相インバータ1および単相インバータ2の駆動信号および3相インバータ1、単相インバータ2の電圧切り換わりのタイミングは図38に示すようになる。3相インバータ1では、スイッチング素子12aがオフする駆動信号がオフになって図38(c)に実線で示すように、T2m後に電圧が切り換わる。

一方、コンデンサ27a、27bより負荷3側では、スイッチング素子24fがオフするとダイオード25h、25gに転流する。直流電圧中性点から負荷3側の出力端子までの電圧を単相インバータ2の負荷3側電圧とすると、図38(e)で実線で示すようにT2s後に電圧が切り換わる。よって、単相インバータ2の電圧は、図38(d)(e)を合わせた電圧となり、図38(f)の実線のようになる。これを図38(c)の3相インバータ1の相電圧と合わせると、図38(g)の実線のようになる。

また、電流の方向が逆の場合は、図38に破線で示すような波形となる。

また、先の実施の形態3のように、駆動信号を遅れさせる補正ならば、3相インバータ1および単相インバータ2における電圧切り換えのタイミングずれのうち一番遅いものに合わせるよう補正すればよい。よって、実施の形態3の制御回路におけるパルス補正のアルゴリズムを変更することで実現可能である。

以上の実施の形態4〜6では、3相インバータ1か単相インバータ2のいずれかが、実施の形態1〜3の説明で用いた回路と異なる場合について説明したが、更に、3相インバータ1が図22の3レベルインバータ、単相インバータ2が図28の3レベルインバータなど、どの組み合わせでも可能であり、同様の手法で負荷3のサージ電圧を抑制することができる。

先の実施の形態1〜6では、単相インバータ2は各相1台の例について説明しているが、単相インバータ2は、図41に示すように、複数の単相インバータの交流側を直列に接続したものでもよい。このような構成であっても、実施の形態1〜6と同様の方法を用いて負荷3のサージ電圧を抑制できる。

図41、図42は、先の実施の形態2と同じ手法を用いることを想定した図であるが、駆動信号生成回路82は、図42のようにして、単相インバータPWM回路90により単相インバータ80、81の駆動信号を生成する。パルス補正回路91、92は、先の実施の形態2のパルス補正回路45と同じ手法の動作でよい。単相インバータ80、81は同じ回路でも、例えば、単相インバータ80が2レベルインバータ、単相インバータ81が3レベルインバータといった異なる回路の組み合わせや、単相インバータ80、81の直流電圧が異なる組み合わせでも構わない。

また、3相インバータ1を単相インバータとして単相の負荷に用いる構成でも、先の実施の形態1〜6で説明した補正方法が適用できる。図43は、負荷103が単相負荷である場合であるが、ここで、3相インバータ1を単相インバータ100に変更し、単相インバータ102を1台用いた構成としている。単相インバータ100は、図44の2レベルフルブリッジインバータ、図45の2レベルハーフブリッジインバータ、図46の3レベルフルブリッジインバータ、図47の3レベルハーフブリッジインバータ等、どれでもよい。単相インバータ102に関しても先の実施の形態1〜6で説明したどの回路でもよい。補正の方法も実施の形態1〜6で説明したどの方法でもよい。例えば、実施の形態2と同じ方法なら、図48のような構成となる。図48は、先の図17を単相の電力変換装置に対応させただけの構成であり、単相なので零相電圧操作回路32は省略している。他の実施の形態1、3〜5であっても容易に単相の電力変換装置に対応させた構成とできる。このように単相の電力変換装置であっても実施の形態1〜6と同様の効果が得られる。

また、先の実施の形態1〜6は、直流電力を交流電力に変換して負荷へ供給するインバータとしての用途について説明を行ったが、負荷の代わりに交流電力系統を接続し、交流電力を直流電力に変換するコンバータとして用いることも可能である。

6,7,83,84 ゲートドライブ回路、

11,14a,14b,20,21a,21b,27a,27b コンデンサ、

12a〜12f,16a〜16l,18a〜18d,22a,22b,24a〜24h スイッチング素子、

30 3相インバータPWM回路、

33,90,110,112 単相インバータPWM回路、40,104 電流センサ、41,43〜45,91,92,113,114 パルス補正回路、

46 PWMパターン記憶回路、

70,71,93,94,115,116 Td生成回路。

Claims (11)

- スイッチング素子をオンオフ制御することにより直流/交流間で電力の変換を行う第1および第2の電力変換器の各交流側を直列に接続してなる電力変換装置であって、

上記第1の電力変換器のスイッチング素子を駆動する第1の駆動信号と上記第2の電力変換器のスイッチング素子を駆動する第2の駆動信号とを作成する駆動信号生成回路を備えた電力変換装置において、

上記第1の電力変換器の交流出力電圧を上昇または下降させるタイミングで上記第2の電力変換器の交流出力電圧を下降または上昇させるため、上記第1および第2の駆動信号として作成された第1および第2の指令駆動信号に対し、上記第1の電力変換器の交流出力電圧が実際に上昇または下降する電圧変化タイミングと上記第2の電力変換器の交流出力電圧が実際に下降または上昇する電圧変化タイミングとが同一の同期電圧変化タイミングとなるよう上記第1および第2の指令駆動信号を補正して第1および第2の補正駆動信号を出力する駆動信号補正手段を備えたことを特徴とする電力変換装置。 - 上記駆動信号補正手段は、上記第1および第2の電力変換器に設定された短絡防止時間と、上記第1および第2の電力変換器のスイッチング素子におけるオンオフ駆動信号入力時からオンオフ動作出力時までのオンオフ遅延時間と、上記第1および第2の電力変換器の交流側電流の向きとに基づき上記補正に係る補正時間量を設定することを特徴とする請求項1記載の電力変換装置。

- 上記駆動信号生成回路は、交流電圧指令に基づきPWM(パルス幅変調)制御で上記第1の駆動信号を作成し、上記交流電圧指令と上記第1の電力変換器の交流出力電圧との偏差である偏差指令に基づきPWM制御で上記第2の駆動信号を作成することを特徴とする請求項2記載の電力変換装置。

- 上記駆動信号補正手段は、上記第1および第2の指令駆動信号に基づく電圧変化タイミングが上記同期電圧変化タイミングと一致するよう、上記第1および第2の補正駆動信号を、上記第1および第2の指令駆動信号を所定の補正時間量だけ早めたものとすることを特徴とする請求項3記載の電力変換装置。

- 上記第1および第2の電力変換器の電圧切換動作の種別毎に上記第1および第2の指令駆動信号に対応する上記第1および第2の補正駆動信号を予め記憶しておき、上記駆動信号補正手段は、上記電圧切換動作の種別毎に上記予め記憶された上記第1および第2の指令駆動信号に対応する上記第1および第2の補正駆動信号を読み出すようにしたことを特徴とする請求項4記載の電力変換装置。

- 上記交流電圧指令を所定時間進める進み時間設定回路を設け、上記駆動信号補正手段は、上記第1および第2の指令駆動信号に基づく電圧変化タイミングが上記同期電圧変化タイミングと一致するよう、上記第1および第2の補正駆動信号を、上記第1および第2の指令駆動信号を所定の補正時間量だけ遅らせたものとすることを特徴とする請求項3記載の電力変換装置。

- 上記駆動信号補正手段は、上記第1または第2の電力変換器のいずれか、その駆動信号の変化タイミングに対して交流出力電圧の電圧変化タイミングがより遅くなる方の電圧変化タイミングが上記同期電圧変化タイミングと一致するよう、上記第1および第2の指令駆動信号を補正して上記第1および第2の補正駆動信号を出力することを特徴とする請求項3記載の電力変換装置。

- 上記第1の電力変換器は、第1の直流電圧源の直流電圧を3相の交流電圧に変換する3相インバータであり、上記第2の電力変換器は、第2の直流電圧源の直流電圧を単相の交流電圧に変換する単相インバータであり、上記3相インバータの各相交流側と上記単相インバータの交流側とを直列にして3相交流負荷に接続されたことを特徴とする請求項3ないし7のいずれか1項に記載の電力変換装置。

- 上記単相インバータを、その交流側が互いに直列に接続された複数の単相インバータで構成したことを特徴とする請求項8記載の電力変換装置。

- 上記第1の電力変換器は、第1の直流電圧源の直流電圧を単相の交流電圧に変換する第1の単相インバータであり、上記第2の電力変換器は、第2の直流電圧源の直流電圧を単相の交流電圧に変換する第2の単相インバータであり、上記第1の単相インバータの交流側と上記第2の単相インバータの交流側とを直列にして単相交流負荷に接続されたことを特徴とする請求項3ないし7のいずれか1項に記載の電力変換装置。

- 上記第1および第2の電力変換器は、それらの交流側に接続された交流電源の交流電圧を直流電圧に変換する第1および第2のコンバータとしたことを特徴とする請求項3ないし7のいずれか1項に記載の電力変換装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008191598A JP5247282B2 (ja) | 2008-07-25 | 2008-07-25 | 電力変換装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008191598A JP5247282B2 (ja) | 2008-07-25 | 2008-07-25 | 電力変換装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010035252A true JP2010035252A (ja) | 2010-02-12 |

| JP5247282B2 JP5247282B2 (ja) | 2013-07-24 |

Family

ID=41739096

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008191598A Expired - Fee Related JP5247282B2 (ja) | 2008-07-25 | 2008-07-25 | 電力変換装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5247282B2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012035807A1 (ja) * | 2010-09-13 | 2012-03-22 | オムロン株式会社 | パワーコンディショナ |

| JP2013198182A (ja) * | 2012-03-16 | 2013-09-30 | Meidensha Corp | 多重インバータ |

| JP2013230001A (ja) * | 2012-04-25 | 2013-11-07 | Denso Corp | 電源安定化装置 |

| US8902620B2 (en) | 2010-09-13 | 2014-12-02 | Omron Corporation | Power conditioner |

| CN110176869A (zh) * | 2019-07-07 | 2019-08-27 | 达微智能科技(厦门)有限公司 | 一种混合箝位型三电平h桥逆变器的驱动信号时序方法 |

| WO2023032150A1 (ja) * | 2021-09-03 | 2023-03-09 | 三菱電機株式会社 | 電力変換装置及び電力変換装置を搭載した航空機 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03277177A (ja) * | 1990-03-27 | 1991-12-09 | Matsushita Electric Works Ltd | インバータ装置 |

| JPH08266063A (ja) * | 1995-03-20 | 1996-10-11 | Meidensha Corp | 多重インバータのpwm波形制御方式 |

| JP2004120979A (ja) * | 2002-09-30 | 2004-04-15 | Mitsubishi Electric Corp | 電力変換装置 |

| JP2006081362A (ja) * | 2004-09-13 | 2006-03-23 | Mitsubishi Electric Corp | 電力変換装置 |

| JP2006166499A (ja) * | 2004-12-02 | 2006-06-22 | Toshiba Corp | 電力変換装置 |

| WO2007111018A1 (ja) * | 2006-03-27 | 2007-10-04 | Mitsubishi Electric Corporation | 電力変換装置 |

-

2008

- 2008-07-25 JP JP2008191598A patent/JP5247282B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03277177A (ja) * | 1990-03-27 | 1991-12-09 | Matsushita Electric Works Ltd | インバータ装置 |

| JPH08266063A (ja) * | 1995-03-20 | 1996-10-11 | Meidensha Corp | 多重インバータのpwm波形制御方式 |

| JP2004120979A (ja) * | 2002-09-30 | 2004-04-15 | Mitsubishi Electric Corp | 電力変換装置 |

| JP2006081362A (ja) * | 2004-09-13 | 2006-03-23 | Mitsubishi Electric Corp | 電力変換装置 |

| JP2006166499A (ja) * | 2004-12-02 | 2006-06-22 | Toshiba Corp | 電力変換装置 |

| WO2007111018A1 (ja) * | 2006-03-27 | 2007-10-04 | Mitsubishi Electric Corporation | 電力変換装置 |

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8902620B2 (en) | 2010-09-13 | 2014-12-02 | Omron Corporation | Power conditioner |

| JP2012060856A (ja) * | 2010-09-13 | 2012-03-22 | Omron Corp | パワーコンディショナ |

| CN103004078A (zh) * | 2010-09-13 | 2013-03-27 | 欧姆龙株式会社 | 功率调节器 |

| WO2012035807A1 (ja) * | 2010-09-13 | 2012-03-22 | オムロン株式会社 | パワーコンディショナ |

| US8570781B2 (en) | 2010-09-13 | 2013-10-29 | Omron Corporation | Power conditioner |

| EP2618475A4 (en) * | 2010-09-13 | 2016-06-29 | Omron Tateisi Electronics Co | POWER UNIT |

| JP2013198182A (ja) * | 2012-03-16 | 2013-09-30 | Meidensha Corp | 多重インバータ |

| JP2013230001A (ja) * | 2012-04-25 | 2013-11-07 | Denso Corp | 電源安定化装置 |

| CN110176869A (zh) * | 2019-07-07 | 2019-08-27 | 达微智能科技(厦门)有限公司 | 一种混合箝位型三电平h桥逆变器的驱动信号时序方法 |

| WO2023032150A1 (ja) * | 2021-09-03 | 2023-03-09 | 三菱電機株式会社 | 電力変換装置及び電力変換装置を搭載した航空機 |

| JP7313566B1 (ja) * | 2021-09-03 | 2023-07-24 | 三菱電機株式会社 | 電力変換装置及び電力変換装置を搭載した航空機 |

| EP4398475A4 (en) * | 2021-09-03 | 2024-10-30 | Mitsubishi Electric Corporation | POWER CONVERSION DEVICE AND AIRCRAFT WITH THE POWER CONVERSION DEVICE |

| US12525899B2 (en) | 2021-09-03 | 2026-01-13 | Mitsubishi Electric Corporation | Power conversion device and aircraft equipped with power conversion device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5247282B2 (ja) | 2013-07-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8817499B2 (en) | Control method and system for reducing the common-mode current in a power converter | |

| KR102409013B1 (ko) | 전력 변환 장치 | |

| JP5247282B2 (ja) | 電力変換装置 | |

| JP5374336B2 (ja) | 電力変換装置 | |

| JP5364303B2 (ja) | 電流制御型電力変換器及び電流制御型電力変換器の出力電流波形改善方法 | |

| JP5104083B2 (ja) | 電力変換装置および電力変換方法 | |

| JP5787053B2 (ja) | 3相v結線コンバータの制御装置 | |

| CN115398789B (zh) | 用分离dc链路控制多电平逆变器的方法 | |

| JP2017153277A (ja) | 自励式無効電力補償装置 | |

| JP2007097389A (ja) | 電力変換装置 | |

| JP5849632B2 (ja) | 電力変換装置 | |

| JP7051600B2 (ja) | 多段変換器の制御装置 | |

| JP4448294B2 (ja) | 電力変換装置 | |

| CN117882287A (zh) | 电力变换器的控制部以及电力变换装置 | |

| US20250317072A1 (en) | Carrier based model predictive control for converter with filter cells | |

| JP5894031B2 (ja) | 電力変換装置 | |

| US20260019007A1 (en) | Model predictive control for converter with filter cells based on offline-computed pulse patterns and online cell balancing | |

| JP4503937B2 (ja) | 電力変換装置の制御装置 | |

| JP7328352B2 (ja) | Pwmインバータ制御装置および制御方法 | |

| WO2025002624A1 (en) | Method, computer program, and controller for controlling an electrical converter, and computer-readable medium | |

| JP4611009B2 (ja) | インバータの制御方法 | |

| WO2024042942A1 (ja) | 回転電機の駆動制御装置および駆動制御方法 | |

| JP2022084042A (ja) | 電力変換装置および電力変換装置の制御方法 | |

| KR20220010536A (ko) | 전력 변환 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101004 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120829 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120904 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121029 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130409 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5247282 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160419 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |