JP2010029474A - 遊技機の不正対策装置 - Google Patents

遊技機の不正対策装置 Download PDFInfo

- Publication number

- JP2010029474A JP2010029474A JP2008195269A JP2008195269A JP2010029474A JP 2010029474 A JP2010029474 A JP 2010029474A JP 2008195269 A JP2008195269 A JP 2008195269A JP 2008195269 A JP2008195269 A JP 2008195269A JP 2010029474 A JP2010029474 A JP 2010029474A

- Authority

- JP

- Japan

- Prior art keywords

- power

- main board

- flag

- random number

- jackpot

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000001514 detection method Methods 0.000 abstract description 10

- 230000004913 activation Effects 0.000 abstract 5

- 238000000034 method Methods 0.000 description 49

- 239000000758 substrate Substances 0.000 description 7

- 230000000694 effects Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 238000009434 installation Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000004886 process control Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Landscapes

- Pinball Game Machines (AREA)

Abstract

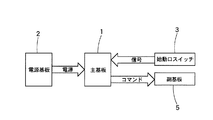

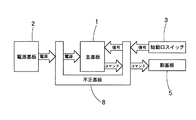

【解決手段】遊技機への最初の電源投入時に立てられる電源投入フラグであって、その後は、主基板1への電源供給が強制的に遮断されるまでオン状態に保持される電源投入フラグを主基板1に設ける。主基板1は、電源投入時に、電源投入フラグがオン状態か否かを判定し、電源投入フラグがオフ状態であると判断すると、不正を検出した旨の信号を出力する。

【選択図】図2

Description

当該パチンコ遊技機の出荷時などにおいて、当該パチンコ遊技機に対し最初の電源投入が行われると、主基板1のCPU11は、図2に示すように、まず初期設定を行い(ステップS1)、次にRAM13へのアクセスを許可する(ステップS2)。

当該パチンコ遊技機に対して電源が投入されるたびに、主基板1のCPU11は、図2に示すように、まず初期設定を行い(ステップS1)、次にRAM13へのアクセスを許可する(ステップS2)。

乱数更新処理は、大当たり判定用乱数、初期値乱数、大当たり図柄判定用乱数など所定の乱数を更新することを内容とする。大当たり判定用乱数の更新について説明すると、大当たり判定用乱数が例えば「0」〜「316」の数値である場合、電源投入時にRAMクリア(図2図示ステップS7)が行われた場合、「0」を初期値乱数として、4msec周期で「0」、「1」、…、「315」、「316」と順に更新してゆき、「0」〜「316」の1サイクル分の更新が終了すると、この更新終了時点の初期値乱数を先頭にして次の1サイクル分の更新を開始する。ここで、上記更新終了時点の初期値乱数が例えば「5」であるとすると、「5」を先頭として、「6」、「7」、…、「315」、「316」、「0」、「1」、「2」、「3」、「4」と順に更新してゆく。一方、電源投入時にRAM復帰(図2図示ステップS13)が行われた場合、復帰したRAMデータ中の初期値乱数を先頭にして大当たり判定用乱数の更新が開始される。

始動口SW処理の内容を図5に示す。

特別図柄処理の内容を図6に示す。

大当たり判定処理の内容を図7に示す。

大入賞口処理は、大当たり中に、大入賞口ソレノイド4への通電を制御して、大入賞口を所定ラウンド数だけ間欠的に開放し、大入賞口への多数の遊技球の入賞を可能にするための処理を行う。

賞球処理は、始動口、大入賞口、普通入賞口に遊技球が入賞した場合に、賞球払出装置を動作させ、所定個数の遊技球の払い出しを行うための処理を行う。

出力処理は、副基板5への各種コマンド送信、大入賞口ソレノイド4への駆動制御信号出力、特別図柄表示器への変動表示制御信号出力などを行う。

初期値乱数更新処理は、初期値乱数を繰り返し更新する処理を行う。

不正行為により、電源基板2から主基板1への電源供給が遮断されると、CPU11は、上記のようなバックアップ処理を行うことができず、記憶内容は消去されることになる。このため、上述したように当該パチンコ遊技機の出荷時などの最初の電源投入時に立てられ、その後、オン状態に保持され続けた電源投入フラグは、オフされることになる。

Claims (2)

- 遊技機への最初の電源投入時に立てられる電源投入フラグであって、その後は、主基板への電源供給が強制的に遮断されるまでオン状態に保持される電源投入フラグを主基板に設け、

前記主基板は、電源投入時に、前記電源投入フラグがオン状態か否かを判定し、前記電源投入フラグがオフ状態であると判断すると、不正を検出した旨の信号を出力することを特徴とする遊技機の不正対策装置。 - 前記主基板は、電源投入時に、前記電源投入フラグがオフ状態であると判断すると、前記電源投入フラグを立てることを特徴とする請求項1に記載の遊技機の不正対策装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008195269A JP5285346B2 (ja) | 2008-07-29 | 2008-07-29 | 遊技機の不正対策装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008195269A JP5285346B2 (ja) | 2008-07-29 | 2008-07-29 | 遊技機の不正対策装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010029474A true JP2010029474A (ja) | 2010-02-12 |

| JP5285346B2 JP5285346B2 (ja) | 2013-09-11 |

Family

ID=41734675

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008195269A Expired - Fee Related JP5285346B2 (ja) | 2008-07-29 | 2008-07-29 | 遊技機の不正対策装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5285346B2 (ja) |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007167149A (ja) * | 2005-12-19 | 2007-07-05 | Olympia:Kk | 遊技機及び遊技機における不正行為の検知方法並びにプログラム |

| JP2007325816A (ja) * | 2006-06-09 | 2007-12-20 | Sanyo Product Co Ltd | 遊技機 |

-

2008

- 2008-07-29 JP JP2008195269A patent/JP5285346B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007167149A (ja) * | 2005-12-19 | 2007-07-05 | Olympia:Kk | 遊技機及び遊技機における不正行為の検知方法並びにプログラム |

| JP2007325816A (ja) * | 2006-06-09 | 2007-12-20 | Sanyo Product Co Ltd | 遊技機 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5285346B2 (ja) | 2013-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7473982B2 (ja) | 遊技機 | |

| JP6884407B2 (ja) | 遊技機 | |

| JP7473981B2 (ja) | 遊技機 | |

| JP2001259209A (ja) | 遊技機 | |

| JP2001327726A (ja) | 遊技機 | |

| JP6603952B2 (ja) | 遊技機 | |

| JP5378086B2 (ja) | 遊技機 | |

| JP5100542B2 (ja) | 遊技機の不正対策装置 | |

| JP2012070859A (ja) | 遊技機 | |

| JP4076979B2 (ja) | 遊技機 | |

| JP6893642B2 (ja) | 遊技機 | |

| JP5285346B2 (ja) | 遊技機の不正対策装置 | |

| JP5124750B2 (ja) | 遊技機 | |

| JP6893641B2 (ja) | 遊技機 | |

| JP2009005971A (ja) | 遊技機 | |

| JP2011250916A (ja) | 遊技機 | |

| JP4667906B2 (ja) | 遊技機 | |

| JP2010017301A (ja) | 遊技機の不正対策装置 | |

| JP2012081334A (ja) | 遊技機 | |

| JP6893640B2 (ja) | 遊技機 | |

| JP2010099282A (ja) | 遊技機 | |

| JP6884409B2 (ja) | 遊技機 | |

| JP2018175774A (ja) | 遊技機 | |

| JP5261659B2 (ja) | 遊技機 | |

| JP2009005983A (ja) | 遊技機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121025 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121214 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130531 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5285346 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |