JP2010004642A - 昇圧回路 - Google Patents

昇圧回路 Download PDFInfo

- Publication number

- JP2010004642A JP2010004642A JP2008160421A JP2008160421A JP2010004642A JP 2010004642 A JP2010004642 A JP 2010004642A JP 2008160421 A JP2008160421 A JP 2008160421A JP 2008160421 A JP2008160421 A JP 2008160421A JP 2010004642 A JP2010004642 A JP 2010004642A

- Authority

- JP

- Japan

- Prior art keywords

- level

- voltage

- output

- output voltage

- switching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000003990 capacitor Substances 0.000 claims description 14

- 238000001514 detection method Methods 0.000 description 16

- 239000000872 buffer Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 230000008901 benefit Effects 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Landscapes

- Logic Circuits (AREA)

- Dc-Dc Converters (AREA)

Abstract

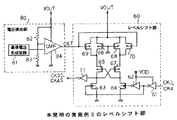

【解決手段】電源電圧VDDレベルのクロック信号CK3,CK4を出力電圧VOUTレベルにシフトするレベルシフト部20A,20Bに、出力電圧VOUTが低くても正常に動作するレベルシフタ30と、出力電圧VOUTが高い時に低消費電流で動作するレベルシフタ40を設け、動作開始から出力電圧VOUTが所定の電圧に上昇すると想定されるまでレベルシフタ30を選択し、その後、レベルシフタ40に切り替えて昇圧動作を継続する。

【選択図】図1

Description

この昇圧回路は、例えばLCD(液晶表示装置)のドライバICで使用されるもので、図2(a)に示したものは、電源電圧VDDのロジック回路で生成されるクロック信号CK1〜CK4に従ってトランジスタをオンオフ制御し、キャパシタに順次電荷を蓄積することによって入力電圧VINを4倍に昇圧して出力電圧VOUTを生成するチャージポンプ型のものである。

この昇圧回路は、入力電圧VIN(例えば、1.4〜3.0V)を4倍に昇圧して出力電圧VOUT(例えば、5.6〜12.0V)を生成するもので、電源電圧VDD(例えば、3.0V)のロジック回路で生成されるクロック信号CK1〜CK4に従ってトランジスタをオンオフ制御してキャパシタに順次電荷を蓄積して昇圧動作を行うチャージポンプ型のものである。

このレベルシフト部60は、図1中のレベルシフト部20A,20Bに代えて設けられるもので、レベルシフト部20A,20Bと同様に、電源電圧VDDレベルのクロック信号CK3(または、CK4)を、出力電圧VOUTレベルのクロック信号CK3S(または、CK4S)にレベルシフトするものである。

電圧検出部80の基準電圧生成回路81に電源電圧VDD(=3.0V)が安定して供給されていると、この電圧検出部80から出力される基準電圧は約1.2Vの安定した電圧となる。一方、抵抗82,83による分圧回路からは、出力電圧VOUTを分圧した電圧が出力される。抵抗82,83の抵抗値は、レベルシフト部60が高い周波数でも問題なく動作するような値、例えば、出力電圧VOUTが3.0V以上になると1.2V以上の電圧が出力されるような抵抗比に設定されている。

(a) 4倍の昇圧回路に対するレベルシフト部の適用例を説明したが、昇圧回路の段数は4段に限定されるものではない。また、チャージポンプの構成は、例示したものに限定されない。

(b) 実施例1のカウンタ55に代えて実施例2と同様の電圧検出部80を使用し、この電圧検出部80から出力される検出信号によってレベルシフト部20A,20Bのスイッチ51を切り替えるように構成しても良い。

(c) 実施例2の電圧検出部80に代えて実施例1と同様のカウンタ55を使用し、このカウンタ55から出力される制御信号によってレベルシフト部60のPMOS69,70をオンオフ制御するように構成しても良い。

(d) 実施例1では、リセット解除後、一定の時間の経過を監視するためにカウンタを使用しているが、例えば抵抗とキャパシタからなる積分回路等を使用することも可能である。

2a〜2c,10a〜10c,33,34,43,44,63,64 NMOS

3a,3c,4a,4c,12a〜12c バッファ

5b,6b,11a〜11d,31,32,41,42,61,62,72 インバータ

7a〜7c キャパシタ

8 ダイオード

20A,20B,60 レベルシフト部

30,40 レベルシフタ

51 スイッチ

52,53,82,83 抵抗

54 NOR

55 カウンタ

80 電圧検出部

81 基準電圧生成回路

84 比較器

Claims (6)

- 入力電圧を電源電圧よりも高いレベルに昇圧し、該昇圧した電圧を出力電圧として出力する昇圧回路であって、

第1の制御信号に従ってオンオフ制御して、前記入力電圧を複数の第1の内部ノードに出力する入力側スイッチ群と、

前記第1の内部ノードとこれに対応する第2の内部ノードとの間に接続された電荷蓄積用のキャパシタと、

第2の制御信号を前記出力電圧に応じたレベルの第3の制御信号にレベルシフトするレベルシフト部と、

前記第3の制御信号に従って前記第2の内部ノード間をオンオフ制御して該第2の内部ノードの電圧を出力ノードへ伝達し、該出力ノードから前記出力電圧を出力する出力側スイッチ群とを備え、

前記レベルシフト部は、前記出力電圧が所定の電圧に達するまでは低電圧動作を行い、該出力電圧が該所定の電圧に達した後は低消費電流動作となるように構成したことを特徴とする昇圧回路。 - 前記レベルシフト部は、

前記出力電圧が前記所定の電圧以下でも前記第2の制御信号を前記第3の制御信号にレベルシフトすることができる第1のレベルシフタと、

前記出力電圧が前記所定の電圧以上のときに前記第1のレベルシフタよりも少ない消費電流で前記第2の制御信号を前記第3の制御信号にレベルシフトする第2のレベルシフタと、

切替制御部からの切替信号に従って前記第1または第2のレベルシフタのいずれか一方を選択するスイッチとを、

有することを特徴とする請求項1記載の昇圧回路。 - 前記レベルシフト部は、

前記第2の制御信号を前記第3の制御信号にレベルシフトして出力する駆動回路に直列に挿入された電流制限用の第1のトランジスタと、

前記第1のトランジスタに並列に接続され、切替制御部からの切替信号に従ってオンオフ制御される第2のトランジスタとを、

有することを特徴とする請求項1記載の昇圧回路。 - 前記切替制御部は、動作開始時から予め定められた時間が経過した時に、前記レベルシフト部が低消費電流となるように切り替える前記切替信号を出力するように構成したことを特徴とする請求項2または3記載の昇圧回路。

- 前記切替制御部は、動作開始時からクロック信号のカウントを行い、そのカウント値が予め定められた値に達した時に、前記レベルシフト部が低消費電流となるように切り替える前記切替信号を出力するように構成したことを特徴とする請求項2または3記載の昇圧回路。

- 前記切替制御部は、前記出力電圧が予め定められた電圧に達した時に、前記レベルシフト部が低消費電流となるように切り替える前記切替信号を出力するように構成したことを特徴とする請求項2または3記載の昇圧回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008160421A JP5198163B2 (ja) | 2008-06-19 | 2008-06-19 | 昇圧回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008160421A JP5198163B2 (ja) | 2008-06-19 | 2008-06-19 | 昇圧回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004642A true JP2010004642A (ja) | 2010-01-07 |

| JP5198163B2 JP5198163B2 (ja) | 2013-05-15 |

Family

ID=41585875

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008160421A Expired - Fee Related JP5198163B2 (ja) | 2008-06-19 | 2008-06-19 | 昇圧回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5198163B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110768659A (zh) * | 2019-10-29 | 2020-02-07 | 湖南国科微电子股份有限公司 | 高压驱动电路 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07159754A (ja) * | 1993-12-08 | 1995-06-23 | Toshiba Corp | 半導体集積回路 |

| JP2001028533A (ja) * | 1999-07-13 | 2001-01-30 | Nec Ic Microcomput Syst Ltd | 電源昇圧回路 |

| JP2002190730A (ja) * | 2000-12-22 | 2002-07-05 | Oki Electric Ind Co Ltd | レベルシフタ制御回路 |

| JP2002233133A (ja) * | 2001-01-31 | 2002-08-16 | Nec Corp | 電源昇圧回路 |

| JP2002305871A (ja) * | 2001-02-01 | 2002-10-18 | Sanyo Electric Co Ltd | チャージポンプ回路 |

| JP2008131778A (ja) * | 2006-11-22 | 2008-06-05 | Oki Electric Ind Co Ltd | チャージポンプ型dc/dcコンバータ |

-

2008

- 2008-06-19 JP JP2008160421A patent/JP5198163B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07159754A (ja) * | 1993-12-08 | 1995-06-23 | Toshiba Corp | 半導体集積回路 |

| JP2001028533A (ja) * | 1999-07-13 | 2001-01-30 | Nec Ic Microcomput Syst Ltd | 電源昇圧回路 |

| JP2002190730A (ja) * | 2000-12-22 | 2002-07-05 | Oki Electric Ind Co Ltd | レベルシフタ制御回路 |

| JP2002233133A (ja) * | 2001-01-31 | 2002-08-16 | Nec Corp | 電源昇圧回路 |

| JP2002305871A (ja) * | 2001-02-01 | 2002-10-18 | Sanyo Electric Co Ltd | チャージポンプ回路 |

| JP2008131778A (ja) * | 2006-11-22 | 2008-06-05 | Oki Electric Ind Co Ltd | チャージポンプ型dc/dcコンバータ |

Non-Patent Citations (1)

| Title |

|---|

| JPN6012067525; 名野隆夫: '「携帯型機器にチャージ・ポンプ型 高効率で低雑音の電源回路を開発」' 日経エレクトロニクス 第857号, 20030929, p. 129-140 * |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110768659A (zh) * | 2019-10-29 | 2020-02-07 | 湖南国科微电子股份有限公司 | 高压驱动电路 |

| CN110768659B (zh) * | 2019-10-29 | 2023-10-31 | 湖南国科微电子股份有限公司 | 高压驱动电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5198163B2 (ja) | 2013-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100448144C (zh) | 电源电路 | |

| US8610509B2 (en) | Flexible low current oscillator for multiphase operations | |

| CN101087104B (zh) | 电源电路 | |

| JP5013603B2 (ja) | チャージポンプ駆動回路、及びそれを用いた半導体装置 | |

| US7005912B2 (en) | Simple step-up apparatus including level shift circuits capable of low breakdown voltage | |

| CN106655757B (zh) | 电容式电荷泵 | |

| US7948300B2 (en) | Negative supply voltage generating circuit and semiconductor integrated circuit having the same | |

| JP2005278378A (ja) | チャージポンプ回路 | |

| US9653990B1 (en) | Negative charge pump with soft start | |

| JP2010178051A (ja) | パワーオンリセット回路 | |

| CN107231143B (zh) | 电平移位电路 | |

| JP2015065735A (ja) | ソフトスタート回路及びそれを含む半導体装置 | |

| US8072257B2 (en) | Charge pump-type voltage booster circuit and semiconductor integrated circuit device | |

| US10727827B2 (en) | Self-biased gate controlled switching circuit | |

| JP5198163B2 (ja) | 昇圧回路 | |

| US9735682B1 (en) | Step-down circuit | |

| US11165415B2 (en) | Relaxation oscillator and method | |

| CN107306082B (zh) | 电荷泵电路 | |

| CN108932956A (zh) | 具有倍压器的装置 | |

| JP2002233134A (ja) | チャージポンプ回路 | |

| KR100762679B1 (ko) | 레벨 쉬프터 | |

| JP2005204366A (ja) | Dc−dcコンバータ | |

| JP2005117830A (ja) | チャージポンプ回路 | |

| US8779850B2 (en) | Bootstrap circuit | |

| JP4877334B2 (ja) | チャージポンプ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110530 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20111220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130108 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5198163 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |