JP2010004079A - 半導体チップ - Google Patents

半導体チップ Download PDFInfo

- Publication number

- JP2010004079A JP2010004079A JP2009231085A JP2009231085A JP2010004079A JP 2010004079 A JP2010004079 A JP 2010004079A JP 2009231085 A JP2009231085 A JP 2009231085A JP 2009231085 A JP2009231085 A JP 2009231085A JP 2010004079 A JP2010004079 A JP 2010004079A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- thermal expansion

- expansion coefficient

- layer

- insulating layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W72/012—

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【解決手段】 第2絶縁層236は、熱膨張率の相対的に低い絶縁膜236Aと、熱膨張率の相対的に高い絶縁膜236Bとの2層構造からなる。半導体チップ30と基板90との熱膨張率は異なり、半導体チップ30の動作時に発生する熱によって半導体チップ30と基板90との間に応力が発生するが、熱膨張率の異なる絶縁膜236A、236Bによりそれぞれ応力を吸収できる。

【選択図】 図1

Description

前記絶縁層が、2以上の絶縁膜からなり、半導体チップ側の絶縁膜が熱膨張率が相対的に低く、外部基板側の絶縁膜の熱膨張率が相対的に高いことを技術的特徴とする。

前記外部基板側の絶縁膜の熱膨張率を、該中間値よりも外部基板の熱膨張率に近い値にしたことを技術的特徴とする。

前記絶縁層の熱膨張率が、半導体チップ側は相対的に低く、外部基板側は相対的に高いことを技術的特徴とする。

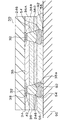

図1は本発明の第1実施形態に係る半導体チップを示している。

半導体チップ30の下面には、パッシベーション膜34の開口にジンケート処理されたアルミニウム電極パッド32が形成されている。本実施形態では、パッシベーション膜34の下面に第1絶縁層136が配設され、該第1絶縁層136には、該アルミニウム電極パッド32に至るテーパ状に広がった非貫通孔136aが形成されている。そして、該非貫通孔136aの底部のアルミニウム電極パッド32には、ニッケルめっき層38,ニッケルと銅との複合めっき層40を介在させて、銅めっきを充填してなるビア42が形成されている。

ここでは、図2の工程(A)に示すパッシベーション膜34の開口にアルミニウム電極パッド32が形成された半導体チップ30に対して、以下の工程で銅めっきポストおよびバンプを形成する。先ず、図2の工程(B)に示すように半導体チップ30を常温で10〜30秒間、金属塩である酸化亜鉛と還元剤として水酸化ナトリウムを混合した液中に浸漬することで、アルミニウム電極パッド32にジンケート処理を施す。これにより、ニッケルめっき層或いは複合めっき層の析出を容易ならしめる。

この絶縁樹脂としては、本実施形態では、レーザー加工により非貫通孔を形成するため、熱硬化性のエポキシ樹脂やポリイミド樹脂を用いる。化学的な処理により非貫通孔を形成する場合には、感光性のエポキシ樹脂やポリイミド樹脂を使用することができる。次に、図3の工程(F)に示すように乾燥処理を行った後、レーザにより第1非貫通孔136aを形成する。そしてさらに、加熱処理してアルミニウム電極パッド32に至る非貫通孔136aを有する第1絶縁層136を形成する。

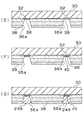

図6は本発明の第2実施形態に係る半導体チップを示している。上述した第1実施形態では、第2絶縁層236を2層構造とし、半導体チップ側の絶縁膜と基板側の絶縁膜とで熱膨張率を異ならしめた。これに対して、第2実施形態では、第2絶縁層236は一層であるが、当該第2絶縁層236の熱膨張率が、半導体チップ側を相対的に低く、外部基板側を相対的に高くなるように傾斜を付けてある。これにより、半導体チップと外部基板との熱膨張差により発生する応力を吸収させる。また、第1実施形態では、第2絶縁層236に形成されるビア(銅めっきポスト)46は、銅を充填してなるが、第2実施形態のビア146は、内部に弾性を有する樹脂147を充填してなる。

先ず、半導体チップ30に第1絶縁層136、ビア42及び再配線層44を形成する工程については、第1実施形態と同様であるため説明を省略する。この半導体チップの第1絶縁層136の上に、工程(A)に示すようにシリカフィラを添加した熱硬化性のエポキシ樹脂又はポリイミド樹脂を塗布してから、24時間放置し、シリカフィラを沈降させる。これにより、上述したように第2絶縁層236の熱膨張率が、半導体チップ側は相対的に低く、外部基板側は相対的に高くなるように傾斜を付ける。

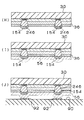

図8は本発明の第3実施形態に係る半導体チップを示している。上述した第1実施形態、第2実施形態では、第1絶縁層36と第2絶縁層136との2層からなったが、この第3実施形態では、1層の絶縁層36のみからなる。但し、該絶縁層36は、熱膨張率の異なる3層の絶縁膜36A、36B、36Cから成る。また、第1、第2実施形態では、再配線層44により配線を取り回したが、第3実施形態では、電極パッド32に直接銅めっきポスト246を形成してある。

図9に示す工程(A)のように、半導体チップにシリカフィラを添加した熱硬化性のエポキシ樹脂又はポリイミド樹脂を塗布してから、乾燥処理を行い絶縁膜36Aを形成する。ここで、シリカフィラの量を多くするとで、上述したように絶縁膜36Aの熱膨張率を相対的に低くしている。

32 アルミニウム電極パッド

34 パッシベーション膜

36 絶縁層

36a 非貫通孔

36A、36B、36C 絶縁膜

38 ニッケルめっき層

40 複合めっき層

42 ビア

44 再配線層

90 基板

92 パッド

236 絶縁層

236A、236B 絶縁膜

Claims (3)

- 電極パッド側の表面に形成された絶縁層と、該絶縁層に形成され該電極パッドを外部基板へ接続するためのビアと、が形成された半導体チップであって、

前記絶縁層が、2以上の絶縁膜からなり、半導体チップ側の絶縁膜が熱膨張率が相対的に低く、外部基板側の絶縁膜の熱膨張率が相対的に高いことを特徴とする半導体チップ。 - 前記半導体チップ側の絶縁膜の熱膨張率を、半導体チップの熱膨張率と外部基板の熱膨張率との中間値よりも半導体チップの熱膨張率に近い値にし、

前記外部基板側の絶縁膜の熱膨張率を、前記中間値よりも外部基板の熱膨張率に近い値にしたことを特徴とする請求項1に記載の半導体チップ。 - 電極パッド側の表面に形成された絶縁層と、該絶縁層に形成され該電極パッドを外部基板へ接続するためのビアと、が形成された半導体チップであって、

前記絶縁層の熱膨張率が、半導体チップ側は相対的に低く、外部基板側は相対的に高いことを特徴とする半導体チップ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009231085A JP5003741B2 (ja) | 2009-10-05 | 2009-10-05 | 半導体チップ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009231085A JP5003741B2 (ja) | 2009-10-05 | 2009-10-05 | 半導体チップ |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000249576A Division JP2002064162A (ja) | 2000-08-21 | 2000-08-21 | 半導体チップ |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010051318A Division JP2010124005A (ja) | 2010-03-09 | 2010-03-09 | 半導体チップモジュール及び半導体チップモジュールの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004079A true JP2010004079A (ja) | 2010-01-07 |

| JP5003741B2 JP5003741B2 (ja) | 2012-08-15 |

Family

ID=41585470

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009231085A Expired - Fee Related JP5003741B2 (ja) | 2009-10-05 | 2009-10-05 | 半導体チップ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5003741B2 (ja) |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000022052A (ja) * | 1998-06-30 | 2000-01-21 | Casio Comput Co Ltd | 半導体装置及びその製造方法 |

| JP2000174051A (ja) * | 1998-09-30 | 2000-06-23 | Ibiden Co Ltd | 半導体チップ及び半導体装置の製造方法 |

-

2009

- 2009-10-05 JP JP2009231085A patent/JP5003741B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000022052A (ja) * | 1998-06-30 | 2000-01-21 | Casio Comput Co Ltd | 半導体装置及びその製造方法 |

| JP2000174051A (ja) * | 1998-09-30 | 2000-06-23 | Ibiden Co Ltd | 半導体チップ及び半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5003741B2 (ja) | 2012-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4093186B2 (ja) | 半導体装置の製造方法 | |

| EP2654388B1 (en) | Semiconductor package, semiconductor apparatus and method for manufacturing semiconductor package | |

| TWI460844B (zh) | 具有內嵌式晶片及矽導通孔晶粒之堆疊封裝結構及其製造方法 | |

| JP6584939B2 (ja) | 配線基板、半導体パッケージ、半導体装置、配線基板の製造方法及び半導体パッケージの製造方法 | |

| US9627308B2 (en) | Wiring substrate | |

| US9338886B2 (en) | Substrate for mounting semiconductor, semiconductor device and method for manufacturing semiconductor device | |

| KR20140107129A (ko) | 반도체 장치 및 반도체 장치의 제조 방법 | |

| JP2009212146A (ja) | 基板およびその製造方法 | |

| JP4416874B2 (ja) | 半導体チップの製造方法 | |

| US20130277828A1 (en) | Methods and Apparatus for bump-on-trace Chip Packaging | |

| JP4416876B2 (ja) | 半導体チップ及び半導体チップの製造方法 | |

| JP5440650B2 (ja) | 基板の製造方法 | |

| US8062927B2 (en) | Wiring board and method of manufacturing the same, and electronic component device using the wiring board and method of manufacturing the same | |

| JP2002064162A (ja) | 半導体チップ | |

| JP4416875B2 (ja) | 半導体チップ及び半導体装置の製造方法 | |

| TW201913944A (zh) | 中介基板及其製法 | |

| JP2002064161A (ja) | 半導体チップ及びその製造方法 | |

| JP5003741B2 (ja) | 半導体チップ | |

| JP4594777B2 (ja) | 積層型電子部品の製造方法 | |

| JP2010124005A (ja) | 半導体チップモジュール及び半導体チップモジュールの製造方法 | |

| CN113506778B (zh) | 半导体封装装置及其制造方法 | |

| JP6009844B2 (ja) | 中継基板及びその製造方法 | |

| JP4818417B2 (ja) | 半導体チップ及びその製造方法 | |

| KR20130027870A (ko) | 패키지 기판 및 패키지의 제조 방법 | |

| JP2008060548A (ja) | 素子搭載用基板、素子搭載用基板の製造方法、および半導体モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091005 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100928 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110830 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111005 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120403 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120403 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120424 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120507 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150601 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5003741 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |