JP2010003858A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010003858A JP2010003858A JP2008161144A JP2008161144A JP2010003858A JP 2010003858 A JP2010003858 A JP 2010003858A JP 2008161144 A JP2008161144 A JP 2008161144A JP 2008161144 A JP2008161144 A JP 2008161144A JP 2010003858 A JP2010003858 A JP 2010003858A

- Authority

- JP

- Japan

- Prior art keywords

- lead

- insulating substrate

- semiconductor device

- patterned insulating

- semiconductor chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W72/60—

-

- H10W72/07336—

-

- H10W72/07337—

-

- H10W72/5524—

-

- H10W72/652—

-

- H10W74/00—

Landscapes

- Lead Frames For Integrated Circuits (AREA)

Abstract

【解決手段】パターン付絶縁基板10及び半導体チップ20とリード40との接合に超音波接合を用いることで、加熱や局所的発熱を発生させることがなく、信頼性を劣化させることがない半導体装置1とすることができる。またリード40を放熱板30に接触させないことで、放熱板30に電位を生じさせず、放熱性の良い半導体装置1とすることができる。更に突出部10aに対してリード40の一部を挟みつけることで、パターン付絶縁基板10及び半導体チップ20とリード40との接合を容易化でき、製造効率を向上させることができる半導体装置1とすることができる。

【選択図】 図1

Description

電力用半導体デバイスは、大電力を消費することから、半導体装置の製造時及び使用時に発生する熱応力や放熱性に対する対策が重要な課題となる。

従来、樹脂封止型の半導体装置として、半導体の電極とリードフレームとの接合にアルミワイヤーを用いず、リードフレームを直接固着させるものがあった。そのようなものとして、下記特許文献1がある。

下記特許文献1は、電力用半導体装置に関する発明で、半導体の電極にリードフレームを直接固着させ、リードフレームと、半導体素子を載置する基板としての金属ブロックと、半導体素子とをモールド樹脂で一体成形する技術が開示されている。

しかし、半導体の電極とリードフレームとの接合にハンダ若しくは溶接を用いる構成としてある。よってハンダを用いる場合には、加熱工程を繰り返すことにより半導体チップの熱履歴が多くなり、半導体チップに悪影響を与え、半導体装置の信頼性を劣化させるという問題があった。また溶接を用いる場合には、固着箇所に局所的な高温を加えることにより半導体チップに熱応力が発生し、半導体チップに悪影響を与え、半導体装置の信頼性を劣化させるという問題があった。

また金属ブロックを筐体から露出させる場合には、ヒートシンクに電位が生じないようにヒートシンク裏面に絶縁性樹脂シートを敷くため、熱伝導率が悪く、放熱性が悪いという問題があった。

また回路パターンを設けることなく且つ放熱板より突出させてなる突出部に対してリードの一部を挟みつけることで、リードが放熱板に接触することがない。よって放熱板に電位を生じさせることがない。従って放熱板裏面に絶縁性樹脂シートを敷く必要がなく、放熱性の良い半導体装置とすることができると共に、コスト面に配慮した半導体装置とすることができる。

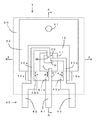

この半導体装置1は、図1に示すように、パターン付絶縁基板10と、半導体チップ20と、放熱板30と、リード40と、樹脂50とで構成される。

また図1、図2(a)に示すように、パターン付絶縁基板10の一部を、回路パターンを設けることなく且つ放熱板30より突出させてなる突出部10aとしてある。

なおパターン付絶縁基板10の寸法は、厚みが0.3mm〜1.0mm程度、横が5.0mm〜10.0mm程度、縦が4.0mm〜8.0mm程度である。

なお上面回路パターン11及び下面回路パターン12の寸法は、厚みが0.2mm〜0.4mm程度、横が4.0mm〜9.0mm程度、縦が2.0mm〜7.0mm程度である。

半導体チップ20は、金属ハンダ若しくは導電性樹脂を用いて上面回路パターン11に接合されることでパターン付絶縁基板10に搭載される。

導電性樹脂としては、エポキシ系、ウレタン系、水性エポキシ系、水性アクリル系等、導電性樹脂として通常用いられるものであれば如何なるものであってもよい。

なお半導体チップ20の寸法は、厚みが0.1mm〜0.5mm程度、横が3.0mm〜5.0mm程度、縦が3.0mm〜5.0mm程度である。

放熱板30は、金属ハンダ若しくは導電性樹脂を用いて下面回路パターン12に接合されることでパターン付絶縁基板10に取り付けられる。

導電性樹脂としては、エポキシ系、ウレタン系、水性エポキシ系、水性アクリル系等、導電性樹脂として通常用いられるものであれば如何なるものであってもよい。

なお放熱板30の寸法は、厚みが1.0mm〜2.0mm程度、横が7.0mm〜12.0mm程度、縦が12.0mm〜16.0mm程度である。

このリード40は、図1に示すように、第1リード41と、第2リード42と、第3リード43の3本のリードで構成され、順にドレイン端子、ゲート端子、ソース端子の3極を構成している。このように3極を有する構成とすることで、半導体装置1をサイリスタ等の大電力パワーデバイスとして有用なものとすることができる。

ここで「上面リード」とは、リード40におけるパターン付絶縁基板10と接する部分のうちパターン付絶縁基板10よりも上面に位置するリードを指し、「下面リード」とは、パターン付絶縁基板10よりも下面に位置するリードを指すものとする。

具体的には、図1に示すように、第1リード41は、第1上面リード41aと第1下面リード41bとを有し、第2リード42は、第2上面リード42aと第2下面リード42bとを有し、第3リード43は、第3上面リード43aと第3下面リード43bとを有している。

この第1リード41は、図1、図2(a)に示すように、第1上面リード41aと、第1下面リード41bとを有している。また図2(a)に示すように、第1上面リード41aの先端は、その下面を上面回路パターン11の上面と面接合させてある。これにより、第1上面リード41aを通じて上面回路パターン11へ電源供給を行うことができる。

ここで「薄肉」とは、薄肉部Lの厚みが該薄肉部Lを除く第1上面リード41aの厚みよりも薄いものであることを示す。

このような構成とすることで、端面11aに第1上面リード41aが接触することがない。よって上面回路パターン11において、第1上面リード41aが接合部分以外に電位を生じさせることがない。従って放熱性の良い半導体装置1とすることができる。

この第2リード42は、図1に示すように、第2上面リード42aと、第2下面リード42bとを有している。また図2(a)に示すように、第2上面リード42aの先端は、その下面を半導体チップ20の上面にある図示していない電極と面接合させてある。これにより第2上面リード42aを通じて半導体チップ20へ電源供給を行うことができる。

ここで「薄肉」とは、薄肉部Mの厚みが該薄肉部Mを除く第2上面リード42aの厚みよりも薄いものであることを示す。

このような構成とすることで、端面20aに第2上面リード42aが接触することがない。よって半導体チップ20において、第2上面リード42aが接合部分以外に電位を生じさせることがない。よって放熱性の良い半導体装置1とすることができる。

この第3リード43は、図1に示すように、第3上面リード43aと、第3下面リード43bとを有している。また図2(b)に示すように、第3上面リード43aの先端は、その下面を半導体チップ20の上面にある図示していない電極と面接合させてある。これにより第3上面リード43aを通じて半導体チップ20へ電源供給を行うことができる。

ここで「薄肉」とは、薄肉部Nの厚みが該薄肉部Nを除く第3上面リード43aの厚みよりも薄いものであることを示す。

このような構成とすることで、端面20bに第3上面リード43aが接触することがない。よって半導体チップ20において、第3上面リード43aが接合部分以外に電位を生じさせることがない。よって放熱性の良い半導体装置1とすることができる。

なおここで及び下記の説明において、図2(a)は、図1のA−A線の拡大断面図であり、且つ全ての下面リードは同一厚、同一長であることから、第1上面リード41aと第1下面リード41bとでリードを突出部10aに挟みつけてある状態のみが示されている。しかし本実施例において、第2リード42及び第3リード43をパターン付絶縁基板10に挟みつけてある状態をA−A線拡大断面図と同方向の断面の拡大図で表す場合、第1リード41と同様の形状で示される。よって図2(a)において、突出部10aに挟みつけてある第1上面リード41a、第1下面リード41bに括弧を付して第2、第3上面リード42a、43aと第2、第3下面リード42b、43bとを示すものとする。

なお隙間Pの長さは、1.0mm〜1.5mm程度とすることが望ましい。

また第1上面リード41a〜第3上面リード43a及び第1下面リード41b〜第3下面リード43bの寸法は、幅が0.5mm〜2.0mm程度、厚みが0.1mm〜0.5mm程度である。

また第1下面リード41b〜第3下面リード43bの長さは、1.0mm〜1.5mm程度である。

また薄肉部L、M、Nの寸法は、幅が0.5mm〜2.0mm程度、厚みが、0.1mm未満、長さが1mm以上である。

またリード40の本数、形状も必ずしも本実施例のものに限る必要はなく、適宜変更可能である。

例えば薄肉部L、M、Nの形状を該薄肉部の下面が、薄肉部L、M、Nを除く上面リード41a〜43aの下面と面一となるような構成とすることができる。このような構成とすることで、薄肉部の長さに関係なく、上面リード41a〜43aが上面回路パターン11及び半導体チップ20の電極との接合部分以外に電位を生じさせることがないものとすることができる。

樹脂50としては、エポキシ樹脂等の熱硬化性樹脂や、ポリエチレン等の熱可塑性樹脂を用い、トランスファー成形によりモールドを行う。このようにトランスファー成形によりモールドを行うことで、モールド作業を簡潔化でき、製造効率を向上させることができる。

なお本実施例においては、図1、図2に示すように、パターン付絶縁基板10と、半導体チップ20と、放熱板30と、端子部分を除くリード40との全てを樹脂50でモールドする構成としてあるが、必ずしもこのような構成に限る必要はなく、適宜変更可能である。

例えば、放熱板30の下面を含む下部を樹脂50でモールドすることなく露出させるものとすることができる。このような構成とすることで、放熱板30の下面に更に外部放熱器を取り付ける場合に外部放熱器を確実に放熱板30に接触させることができる。

まずパターン付絶縁基板10の上面回路パターン11に半導体チップ20を金属ハンダ若しくは導電性樹脂で接合する。そしてパターン付絶縁基板10の下面回路パターン12に放熱板30を金属ハンダ若しくは導電性樹脂で接合する。この際、突出部10aが生じるように放熱板30を取り付ける。これによりパターン付絶縁基板10と、半導体チップ20と、放熱板30とが一体化される。そしてリードフレーム60の第1リード41〜第3リード43を突出部10aに挟みつける。

なおリードフレーム60の厚みは、0.3mm〜0.6mm程度である。

その後、トランスファーモールドにより図示しないモールド金型のダイキャビティにモールド樹脂50を流し込んで、パターン付絶縁基板10と、半導体チップ20と、放熱板30と、リード40とをモールドする。

トランスファーモールド成形後、図3に一点鎖線で示す切断線Qで第1リード41〜第3リード43が切断される。これにより図1に示す半導体装置1が得られる。

つまり図3に示すように、第1リード41〜第3リード43はリードフレーム60において横ダムバー63で連結されている。よって突出部10aに対して少なくとも1本の上面リードと下面リードとを挟みつけることで、第1リード41〜第3リード43の全てをパターン付絶縁基板10に対して保持させて固定することができる。従って少なくとも1本の上面リードと下面リードとを挟みつけるような構成とするものであれば、適宜変更可能である。

半導体装置2は、上述した半導体装置1に比べてパターン付絶縁基板10に複数個の半導体チップ20を搭載するものである。またリード40の形状及び半導体チップ20とリード40との接合位置を変形したものである。その他の構成については、半導体装置1と同様である。同一部材、同一機能を果たすものには同一番号を付し以下説明を省略する。

半導体チップ20としては、同種又は異種のものからなる複数個とすることができる。

このようにパターン付絶縁基板10に複数個の半導体チップ20を搭載することで、複数個の半導体チップ20を1つのモジュールとする、いわゆるマルチチップモジュールを構成することができる。よって半導体装置2の高性能化を図ることができる。

2 半導体装置

10 パターン付絶縁基板

10a 突出部

11 上面回路パターン

11a 端面

12 下面回路パターン

12a 端面

20 半導体チップ

20a 端面

20b 端面

30 放熱板

30a 端面

31 開口部

40 リード

41 第1リード

41a 第1上面リード

41b 第1下面リード

42 第2リード

42a 第2上面リード

42b 第2下面リード

43 第3リード

43a 第3上面リード

43b 第3下面リード

50 樹脂

60 リードフレーム

61 横フレーム

62 縦フレーム

63 横ダムバー

64 縦ダムバー

L 薄肉部

M 薄肉部

N 薄肉部

P 隙間

Q 切断線

Claims (7)

- 回路パターンを備えたパターン付絶縁基板と、該パターン付絶縁基板に搭載される半導体チップと、前記パターン付絶縁基板の下面に取り付けられる放熱板と、前記パターン付絶縁基板及び前記半導体チップに接合されるリードとを備えた半導体装置であって、前記パターン付絶縁基板の一部を回路パターンを設けることなく且つ前記放熱板より突出させてなる突出部とすると共に、該突出部に対して前記リードの一部を挟みつけることで該リードを保持してあることを特徴とする半導体装置。

- リードは複数本からなり、該複数本のリードのうちの少なくとも1本について、そのリードの一部をパターン付絶縁基板の突出部に挟みつけてあることを特徴とする請求項1に記載の半導体装置。

- リードは3本からなり、第1のリードはパターン付絶縁基板の回路パターンに接合され、第2及び第3のリードは半導体チップの電極面に接合されており、且つパターン付絶縁基板の突出部に対してそれぞれのリードの一部を挟みつけてあることを特徴とする請求項1又は2に記載の半導体装置。

- パターン付絶縁基板及び半導体チップに対するリードの接合部分は、通常の0.3mm〜0.6mmリードフレーム厚に対して薄肉に形成してあることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

- パターン付絶縁基板及び半導体チップとリードとの接合は、超音波接合によりなされていることを特徴とする請求項1〜4の何れか1項に記載の半導体装置。

- 同種又は異種のものからなる複数個の半導体チップが1つのパターン付絶縁基板上に搭載されていることを特徴とする請求項1〜5の何れか1項に記載の半導体装置。

- パターン付絶縁基板と、半導体チップと、放熱板と、リードとが樹脂によりモールドされていることを特徴とする請求項1〜6の何れか1項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008161144A JP4614107B2 (ja) | 2008-06-20 | 2008-06-20 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008161144A JP4614107B2 (ja) | 2008-06-20 | 2008-06-20 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010003858A true JP2010003858A (ja) | 2010-01-07 |

| JP4614107B2 JP4614107B2 (ja) | 2011-01-19 |

Family

ID=41585338

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008161144A Expired - Fee Related JP4614107B2 (ja) | 2008-06-20 | 2008-06-20 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4614107B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014132897A1 (ja) * | 2013-03-01 | 2014-09-04 | 住友電気工業株式会社 | 半導体装置 |

| KR20190037722A (ko) * | 2017-09-29 | 2019-04-08 | 현대자동차주식회사 | 차량용 전력모듈 |

| KR20200145091A (ko) * | 2019-06-20 | 2020-12-30 | 제엠제코(주) | 반도체 패키지 |

| CN112992818A (zh) * | 2021-04-26 | 2021-06-18 | 佛山市国星光电股份有限公司 | 一种功率器件及其制作方法 |

| US20210238408A1 (en) * | 2018-10-29 | 2021-08-05 | Henkel Ag & Co. Kgaa | Thermal conductive potting composition |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5273372A (en) * | 1975-12-17 | 1977-06-20 | Hitachi Ltd | Terminal for hyb ic substrate |

| JPS5895656U (ja) * | 1981-12-23 | 1983-06-29 | 日本電気株式会社 | 混成集積回路装置 |

| JPS58111949U (ja) * | 1982-01-25 | 1983-07-30 | 日本電気株式会社 | 混成集積回路装置 |

| JPS59124789A (ja) * | 1983-01-05 | 1984-07-18 | 日本電気株式会社 | 混成集積回路装置 |

| JPS62195159A (ja) * | 1986-02-21 | 1987-08-27 | Hitachi Tobu Semiconductor Ltd | 混成集積回路装置およびその製造に用いられるリ−ドフレ−ム |

| JPH06224359A (ja) * | 1993-01-22 | 1994-08-12 | Toppan Printing Co Ltd | 半導体装置 |

| JP2007251218A (ja) * | 2007-07-06 | 2007-09-27 | Renesas Technology Corp | パワーmosfetの製造方法およびパワーmosfet |

| JP2008098678A (ja) * | 2008-01-04 | 2008-04-24 | Toshiba Corp | 半導体装置及びその製造方法 |

-

2008

- 2008-06-20 JP JP2008161144A patent/JP4614107B2/ja not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5273372A (en) * | 1975-12-17 | 1977-06-20 | Hitachi Ltd | Terminal for hyb ic substrate |

| JPS5895656U (ja) * | 1981-12-23 | 1983-06-29 | 日本電気株式会社 | 混成集積回路装置 |

| JPS58111949U (ja) * | 1982-01-25 | 1983-07-30 | 日本電気株式会社 | 混成集積回路装置 |

| JPS59124789A (ja) * | 1983-01-05 | 1984-07-18 | 日本電気株式会社 | 混成集積回路装置 |

| JPS62195159A (ja) * | 1986-02-21 | 1987-08-27 | Hitachi Tobu Semiconductor Ltd | 混成集積回路装置およびその製造に用いられるリ−ドフレ−ム |

| JPH06224359A (ja) * | 1993-01-22 | 1994-08-12 | Toppan Printing Co Ltd | 半導体装置 |

| JP2007251218A (ja) * | 2007-07-06 | 2007-09-27 | Renesas Technology Corp | パワーmosfetの製造方法およびパワーmosfet |

| JP2008098678A (ja) * | 2008-01-04 | 2008-04-24 | Toshiba Corp | 半導体装置及びその製造方法 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014132897A1 (ja) * | 2013-03-01 | 2014-09-04 | 住友電気工業株式会社 | 半導体装置 |

| JP2014170800A (ja) * | 2013-03-01 | 2014-09-18 | Sumitomo Electric Ind Ltd | 半導体装置 |

| KR20190037722A (ko) * | 2017-09-29 | 2019-04-08 | 현대자동차주식회사 | 차량용 전력모듈 |

| KR102445515B1 (ko) | 2017-09-29 | 2022-09-21 | 현대자동차주식회사 | 차량용 전력모듈 |

| US20210238408A1 (en) * | 2018-10-29 | 2021-08-05 | Henkel Ag & Co. Kgaa | Thermal conductive potting composition |

| US12503586B2 (en) * | 2018-10-29 | 2025-12-23 | Henkel Ag & Co. Kgaa | Thermal conductive potting composition |

| KR20200145091A (ko) * | 2019-06-20 | 2020-12-30 | 제엠제코(주) | 반도체 패키지 |

| KR102199360B1 (ko) * | 2019-06-20 | 2021-01-06 | 제엠제코(주) | 반도체 패키지 |

| CN112992818A (zh) * | 2021-04-26 | 2021-06-18 | 佛山市国星光电股份有限公司 | 一种功率器件及其制作方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4614107B2 (ja) | 2011-01-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101626001B (zh) | 半导体装置及其制造方法 | |

| JP6065973B2 (ja) | 半導体モジュール | |

| US9171773B2 (en) | Semiconductor device | |

| KR101173927B1 (ko) | 반도체장치 모듈 | |

| JP6150866B2 (ja) | 電力半導体装置 | |

| CN105529319A (zh) | 半导体装置 | |

| CN107534025B (zh) | 半导体装置及其制造方法、引线框 | |

| JP2020038914A (ja) | 半導体装置 | |

| JP4614107B2 (ja) | 半導体装置 | |

| JP2008153432A (ja) | 半導体装置およびその製造方法 | |

| JP4985809B2 (ja) | 半導体装置 | |

| JP6010942B2 (ja) | 半導体装置およびその製造方法 | |

| JP2015090965A (ja) | 半導体装置 | |

| KR101644913B1 (ko) | 초음파 용접을 이용한 반도체 패키지 및 제조 방법 | |

| KR20150129269A (ko) | 반도체 패키지를 위한 클립 구조체 및 이를 이용한 반도체 패키지, 제조 방법 | |

| JP4030956B2 (ja) | 電力用半導体装置 | |

| JP5682511B2 (ja) | 半導体モジュール | |

| CN205564736U (zh) | 半导体装置 | |

| CN205406513U (zh) | 半导体装置 | |

| JP4797492B2 (ja) | 半導体装置 | |

| JP2009164511A (ja) | 半導体装置およびその製造方法 | |

| JP7278077B2 (ja) | 半導体装置およびその製造方法 | |

| JP5062189B2 (ja) | 半導体装置の実装構造 | |

| JP5124329B2 (ja) | 半導体装置 | |

| JP2017028131A (ja) | パッケージ実装体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100915 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100922 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101005 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131029 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |