JP2009534895A - Crcエラー検出装置およびcrcエラー検出コード計算方法 - Google Patents

Crcエラー検出装置およびcrcエラー検出コード計算方法 Download PDFInfo

- Publication number

- JP2009534895A JP2009534895A JP2009505948A JP2009505948A JP2009534895A JP 2009534895 A JP2009534895 A JP 2009534895A JP 2009505948 A JP2009505948 A JP 2009505948A JP 2009505948 A JP2009505948 A JP 2009505948A JP 2009534895 A JP2009534895 A JP 2009534895A

- Authority

- JP

- Japan

- Prior art keywords

- error detection

- crc error

- data

- crc

- detection code

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000001514 detection method Methods 0.000 title claims abstract description 226

- 238000004364 calculation method Methods 0.000 title claims abstract description 116

- 238000000034 method Methods 0.000 claims abstract description 56

- 239000011159 matrix material Substances 0.000 claims description 22

- 125000004122 cyclic group Chemical group 0.000 claims 1

- 230000006870 function Effects 0.000 description 14

- 230000005540 biological transmission Effects 0.000 description 7

- 238000004891 communication Methods 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 2

- 238000004886 process control Methods 0.000 description 2

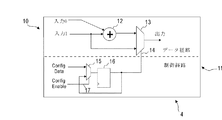

- 238000010586 diagram Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/09—Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit

- H03M13/091—Parallel or block-wise CRC computation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/09—Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6508—Flexibility, adaptability, parametrability and configurability of the implementation

- H03M13/6516—Support of multiple code parameters, e.g. generalized Reed-Solomon decoder for a variety of generator polynomials or Galois fields

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6575—Implementations based on combinatorial logic, e.g. Boolean circuits

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0041—Arrangements at the transmitter end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0061—Error detection codes

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

- Detection And Correction Of Errors (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GBGB0607976.8A GB0607976D0 (en) | 2006-04-22 | 2006-04-22 | Apparatus and method for computing an error detection code |

| PCT/GB2007/001371 WO2007122384A1 (en) | 2006-04-22 | 2007-04-13 | Configurable parallel computation of cyclic redundancy check (crc) codes |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009534895A true JP2009534895A (ja) | 2009-09-24 |

| JP2009534895A5 JP2009534895A5 (enExample) | 2010-06-03 |

Family

ID=36581070

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009505948A Abandoned JP2009534895A (ja) | 2006-04-22 | 2007-04-13 | Crcエラー検出装置およびcrcエラー検出コード計算方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US8321751B2 (enExample) |

| EP (1) | EP2013975B1 (enExample) |

| JP (1) | JP2009534895A (enExample) |

| KR (1) | KR20090008263A (enExample) |

| CN (1) | CN101461140A (enExample) |

| AT (1) | ATE531129T1 (enExample) |

| GB (1) | GB0607976D0 (enExample) |

| IL (1) | IL194807A0 (enExample) |

| RU (1) | RU2008145087A (enExample) |

| WO (1) | WO2007122384A1 (enExample) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8161365B1 (en) * | 2009-01-30 | 2012-04-17 | Xilinx, Inc. | Cyclic redundancy check generator |

| CN101702639B (zh) * | 2009-11-23 | 2012-12-19 | 成都市华为赛门铁克科技有限公司 | 循环冗余校验的校验值计算方法及装置 |

| CN101795175B (zh) * | 2010-02-23 | 2014-03-19 | 中兴通讯股份有限公司 | 数据的校验处理方法及装置 |

| CN101847999B (zh) * | 2010-05-28 | 2012-10-10 | 清华大学 | 一种用循环冗余校验码进行并行校验的方法 |

| CN102546089B (zh) * | 2011-01-04 | 2014-07-16 | 中兴通讯股份有限公司 | 循环冗余校验crc码的实现方法及装置 |

| CN102891685B (zh) * | 2012-09-18 | 2018-06-22 | 国核自仪系统工程有限公司 | 基于fpga的并行循环冗余校验运算电路 |

| CN105099466B (zh) * | 2015-08-17 | 2018-04-17 | 中国航天科技集团公司第九研究院第七七一研究所 | 一种用于128位并行数据的crc校验矩阵生成方法 |

| US10838799B2 (en) * | 2018-08-20 | 2020-11-17 | Micron Technology, Inc. | Parallel error calculation |

| JP6807113B2 (ja) * | 2019-06-07 | 2021-01-06 | ソナス株式会社 | 通信システム、通信方法及び通信装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4712215A (en) * | 1985-12-02 | 1987-12-08 | Advanced Micro Devices, Inc. | CRC calculation machine for separate calculation of checkbits for the header packet and data packet |

| JPH0795096A (ja) * | 1993-09-20 | 1995-04-07 | Fujitsu Ltd | プログラマブル並列crc生成装置 |

| JP3256517B2 (ja) * | 1999-04-06 | 2002-02-12 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 符号化回路、回路、パリティ生成方法及び記憶媒体 |

| US6631488B1 (en) * | 2000-06-30 | 2003-10-07 | Agilent Technologies, Inc. | Configurable error detection and correction engine that has a specialized instruction set tailored for error detection and correction tasks |

| US7171604B2 (en) * | 2003-12-30 | 2007-01-30 | Intel Corporation | Method and apparatus for calculating cyclic redundancy check (CRC) on data using a programmable CRC engine |

-

2006

- 2006-04-22 GB GBGB0607976.8A patent/GB0607976D0/en not_active Ceased

-

2007

- 2007-04-13 RU RU2008145087/09A patent/RU2008145087A/ru not_active Application Discontinuation

- 2007-04-13 EP EP07732413A patent/EP2013975B1/en active Active

- 2007-04-13 KR KR1020087025838A patent/KR20090008263A/ko not_active Withdrawn

- 2007-04-13 JP JP2009505948A patent/JP2009534895A/ja not_active Abandoned

- 2007-04-13 WO PCT/GB2007/001371 patent/WO2007122384A1/en not_active Ceased

- 2007-04-13 AT AT07732413T patent/ATE531129T1/de not_active IP Right Cessation

- 2007-04-13 US US12/298,017 patent/US8321751B2/en active Active

- 2007-04-13 CN CNA2007800208084A patent/CN101461140A/zh active Pending

-

2008

- 2008-10-22 IL IL194807A patent/IL194807A0/en unknown

Also Published As

| Publication number | Publication date |

|---|---|

| WO2007122384A1 (en) | 2007-11-01 |

| US20100058154A1 (en) | 2010-03-04 |

| CN101461140A (zh) | 2009-06-17 |

| GB0607976D0 (en) | 2006-05-31 |

| US8321751B2 (en) | 2012-11-27 |

| EP2013975A1 (en) | 2009-01-14 |

| ATE531129T1 (de) | 2011-11-15 |

| KR20090008263A (ko) | 2009-01-21 |

| IL194807A0 (en) | 2009-09-22 |

| EP2013975B1 (en) | 2011-10-26 |

| RU2008145087A (ru) | 2010-05-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2009534895A (ja) | Crcエラー検出装置およびcrcエラー検出コード計算方法 | |

| US8543888B2 (en) | Programmable cyclic redundancy check CRC unit | |

| US7809050B2 (en) | Method and system for reconfigurable channel coding | |

| US20050010630A1 (en) | Method and apparatus for determining a remainder in a polynomial ring | |

| EP4274127A1 (en) | Data transmission method and apparatus, and device, system and computer-readable storage medium | |

| CN111897674B (zh) | 一种循环冗余校验电路ip核实现系统及方法 | |

| US7904787B2 (en) | Pipelined cyclic redundancy check for high bandwidth interfaces | |

| KR20150130494A (ko) | 모듈식 및 스케일러블 순환 중복 검사 계산 회로 | |

| CN112702065B (zh) | Fpga码流数据校验方法及装置 | |

| US6848072B1 (en) | Network processor having cyclic redundancy check implemented in hardware | |

| US7693928B2 (en) | Galois field linear transformer trellis system | |

| WO2002082664A2 (en) | Variable width parallel cyclical redundancy check | |

| KR20080040706A (ko) | 데이터 스트림에 주기적 덧붙임 검사(crc)를 수행하기위한 crc 생성 회로를 구성하는 방법 및 장치 | |

| CN104484615A (zh) | 适用于可重构阵列架构的基于空间随机化抗故障攻击方法 | |

| CN108574490A (zh) | 计算循环冗余校验crc编码的方法及装置 | |

| US5367479A (en) | Divider device to divide a first polynomial by a second one | |

| US20030041300A1 (en) | Universal device for processing Reed-Solomon forward error-correction encoded messages | |

| US20140317478A1 (en) | Configurable and low power encoder for cyclic error correction codes | |

| US10790852B2 (en) | Cyclic redundancy check (CRC) system for detecting error in data communication | |

| CN114942861B (zh) | Crc计算方法、装置、计算机设备及存储介质 | |

| US7225391B1 (en) | Method and apparatus for parallel computation of linear block codes | |

| CN113657062B (zh) | 基于奇偶校验提高fpga运行可靠性的方法 | |

| El-Medany | Reconfigurable CRC IP core design on xilinx spartan 3AN FPGA | |

| US8015476B2 (en) | CRC syndrome generation for multiple data input widths | |

| JP2000232377A (ja) | リードソロモン復号装置とその制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100331 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100331 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20100331 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100331 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20100423 |