JP2009251802A - マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 - Google Patents

マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 Download PDFInfo

- Publication number

- JP2009251802A JP2009251802A JP2008097226A JP2008097226A JP2009251802A JP 2009251802 A JP2009251802 A JP 2009251802A JP 2008097226 A JP2008097226 A JP 2008097226A JP 2008097226 A JP2008097226 A JP 2008097226A JP 2009251802 A JP2009251802 A JP 2009251802A

- Authority

- JP

- Japan

- Prior art keywords

- interrupt

- processor

- priority

- processors

- multiprocessor system

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

- G06F13/26—Handling requests for interconnection or transfer for access to input/output bus using interrupt with priority control

Abstract

【課題】割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上するマルチプロセッサシステムを提供する。

【解決手段】レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの割込み制御方法であって、対応するプロセッサが割込みを許容する許容度を示す割込み許容度を前記レジスタに設定する設定ステップと、各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知ステップと、前記割込み優先度に比べて低い割込み許容度が記憶されるレジスタを有するプロセッサのいずれかに、前記割込み要求を受理させる割込み受理ステップとを含むことを特徴とする。

【選択図】図1

【解決手段】レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの割込み制御方法であって、対応するプロセッサが割込みを許容する許容度を示す割込み許容度を前記レジスタに設定する設定ステップと、各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知ステップと、前記割込み優先度に比べて低い割込み許容度が記憶されるレジスタを有するプロセッサのいずれかに、前記割込み要求を受理させる割込み受理ステップとを含むことを特徴とする。

【選択図】図1

Description

本発明は、マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法に関し、特にマルチプロセッサにおいて割込みを制御するマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法に関する。

マルチプロセッサシステムは、典型的に、割込み処理可能な複数のプロセッサと、共有バスと、プロセッサから共有バスを介してアクセス可能な共有メモリと、データの入力や出力を行う装置であるI/O(Input/Output)デバイスの信号を割込み信号としてプロセッサに通知する割込み生成器とを有する。

ここで、割込みとは、ある連続した処理の最中に、別の処理を行わせることである。

典型的なマルチプロセッサシステムにおいて、割込みは、I/Oデバイスからの信号によって発生し、マルチプロセッサシステムを構成する複数のプロセッサの中から一つのプロセッサに、割込み処理の責任が割当てられる。責任が割当てられたプロセッサは、それまで行っていた処理を中断し、割込みされた処理を実行する。

ここで、割込み制御を行うマルチプロセッサシステムとして、例えば、すべてのプロセッサに対して、割込みを通知し、最も早くその通知を受け取ったプロセッサに、割込み処理の責任を割当てるマルチプロセッサシステムがある。

このマルチプロセッサシステムの割込み制御方法では、割込み発生からプロセッサが処理を開始するまでの応答性は一般に良い。しかし、割込み処理が割当てられたプロセッサ以外のプロセッサでは割込み通知に対する処理をキャンセルするという処理が発生するため、システム全体の処理効率が低下する。

そこで、割込み制御を行うマルチプロセッサシステムとして、例えば、割込みを処理する責任を特定のプロセッサに予め割当てておき、割込みが発生した場合に、責任が割当てられた特定のプロセッサにのみ割込みを通知するマルチプロセッサシステムがある。

図31は、従来の割込み制御を行うマルチプロセッサシステムの構成を示すブロック図である。図31に示すマルチプロセッサシステムは、割込み処理可能なプロセッサ3101、3102、3103および3104と、共有バス3110と、共有バス3110を介してアクセス可能な共有メモリ3120と、割込み生成器3130と、I/Oデバイス141、142および143と、I/Oインタフェース170とを備える。

割込み生成器130は、I/Oインタフェース170を介して入力されるI/Oデバイス141〜143の信号を割込み信号としてプロセッサに通知する。

また、割込み生成器3130は、割込み信号を通知するプロセッサ(3101、3102、3103または3104)を指定するのに用いる指定レジスタ3100を備える。

指定レジスタ3100は、タスク優先度の最も低いタスクを実行するプロセッサが設定されている。このように、指定レジスタ3100において、割込みを処理する責任が特定のプロセッサに予め設定されている。

図31に示すマルチプロセッサシステムは、指定レジスタ3100を用いて設定されるプロセッサに割込み処理の責任を割当てることで、システム全体の処理効率を向上している。

特開2006−216042号公報

しかしながら、従来の割込み制御方法では、特定のプロセッサに割込み処理の責任が割当てられる。責任が割当てられたプロセッサが、一時的な共有資源の獲得待ちなど、何らかの要因によって応答性が低下してしまった場合には、割込み発生からそのプロセッサが処理を開始するまでの割込み応答性もまた低下してしまう。

そこで、本発明は、上述の事情を鑑みてなされたもので、割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上するマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法を提供することを目的とする。

上記目的を達成するために、本発明に係るマルチプロセッサシステムの割込み制御方法は、レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの割込み制御方法であって、対応するプロセッサが割込みを許容する許容度を示すマスクレベル値を前記レジスタに設定する設定ステップと、各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知ステップと、前記割込み優先度の値に比べて低いマスクレベル値に設定されたレジスタを有するプロセッサのいずれかが、前記割込み要求を受理する割込み受理ステップとを含むことを特徴とする。

また、好ましくは、前記マルチプロセッサシステムの割込み制御方法は、さらに、前記複数のI/Oデバイスの割込み優先度毎に、割込み要求を受理可能なプロセッサの数である第1プロセッサ数と、割込み要求を受理可能にすべきプロセッサの数である第2プロセッサ数とを示すテーブルをメモリに保持させるステップと、前記第2プロセッサ数を変更する変更ステップと、前記第2プロセッサ数が変更された場合、変更された前記第2プロセッサ数に第1プロセッサ数を一致させるように、前記複数のマスクレベル値の少なくとも1つを変更するマスクレベル変更ステップとを含む。

また、上記目的を達成するために、本発明に係るマルチプロセッサシステムは、レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムであって、対応するプロセッサが割込みを許容する許容度を示すマスクレベル値を前記レジスタに設定する設定手段と、各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知手段と、前記割込み優先度の値に比べて低いマスクレベル値に設定されるレジスタを有するプロセッサのいずれかが、前記割込み要求を受理する割込み受理手段とを備えることを特徴とする。

また、好ましくは、前記マルチプロセッサシステムは、さらに、前記複数のI/Oデバイスの割込優先度毎に、割込み要求を受理可能なプロセッサの数である第1プロセッサ数と、割込み要求を受理可能にすべきプロセッサの数である第2プロセッサ数とを保持する保持手段と、前記第2プロセッサ数を変更する変更手段と、前記第2プロセッサ数が変更された場合、変更された前記第2プロセッサ数に第1プロセッサ数を一致させるように、前記複数のマスクレベル値の少なくとも1つを変更するマスクレベル変更手段とを備える。

また、さらに、前記各プロセッサで実行されるタスクのタスク優先度を保持するタスク優先度保持手段と、前記各プロセッサで実行されるタスクに従って、前記タスク優先度を変更するタスク優先度変更手段とを備え、前記変更手段は、手段前記タスク優先度が変更される場合、前記タスク優先度に従って、前記第2プロセッサ数を変更してもよい。

また、さらに、前記各プロセッサの割込み発生頻度を保持するタスク優先度保持手段と、前記各プロセッサで実行される割込み回数に従って、前記割込み発生頻度を変更する割込み発生頻度変更手段とを備え、前記変更手段は、前記割込み発生頻度が変更される場合、前記割込み発生頻度に従って、前記第2プロセッサ数を変更してもよい。

なお、本発明は、装置として実現するだけでなく、このような装置が備える処理手段を備える集積回路として実現したり、その装置を構成する処理手段をステップとする方法として実現したり、それらステップをコンピュータに実行させるプログラムとして実現したり、そのプログラムを記録したコンピュータ読み取り可能なCD−ROMなどの記録媒体として実現したり、そのプログラムを示す情報、データまたは信号として実現したりすることもできる。そして、それらプログラム、情報、データおよび信号は、インターネット等の通信ネットワークを介して配信してもよい。

本発明によれば、割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上できるマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法を実現することができる。

以下に、本発明の実施の形態について、図面を参照しながら説明する。

(実施の形態1)

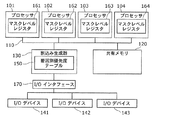

図1は、本発明の実施の形態1におけるマルチプロセッサシステムの構成を示すブロック図である。

図1は、本発明の実施の形態1におけるマルチプロセッサシステムの構成を示すブロック図である。

図1に示すマルチプロセッサシステムは、プロセッサ101、102、103および104と、共有バス110と、共有メモリ120と、割込み生成器130と、I/Oデバイス141、142および143と、I/Oインタフェース170とを備える。

プロセッサ101、102、103および104は、共有バス110を介して相互に通信可能である。また、プロセッサ101、102、103および104は共有バス110を介して共有メモリ120にアクセス可能である。また、プロセッサ101、102、103および104はそれぞれ、マスクレベルレジスタ161、162、163および164を備える。

割込み生成器130は、要因別優先度テーブル150を備える。要因別優先度テーブル150は、I/Oデバイス141、142および143それぞれに予め定義された割込み優先度を有している。

また、割込み生成器130は、I/Oインタフェース170を介して、I/Oデバイス141、142または143の割込みの要求が通知される。割込み生成器130は、すべてのプロセッサ(101、102、103および104)に対し、割込みの要求を発生したI/Oデバイス(141、142または143)の識別番号と、要因別優先度テーブル150に定義されているI/Oデバイス(141、142または143)の割込み優先度とを共有バス110を介して通知する。

プロセッサ101、102、103および104はそれぞれマスクレベルレジスタ161、162、163および164を備える。ここで、マスクレベルレジスタ161、162、163および164には、プロセッサ101、102、103および104それぞれが割込みを許可する割込みの中で最も低い割込み優先度が格納される。

例えばプロセッサ101は、割込み生成器130からの割込み要求の通知に対して、マスクレベルレジスタ161に格納された割込み優先度と、割込み生成器130から通知された割込み優先度とを比較する。プロセッサ101は、割込み生成器130から通知された割込み優先度が、マスクレベルレジスタ161に格納された割込み優先度未満である場合には、割込み生成器130からの割込み要求の通知を無視する。プロセッサ101は、割込み生成器130から通知された割込み優先度が、マスクレベルレジスタ161に格納された割込み優先度以上である場合には、それまで行っていた処理を中断し、割込み処理を開始する。なお、プロセッサ102、103および104もプロセッサ101と同様のため、説明を省略する。

以上のように図1に示すマルチプロセッサシステムは構成される。

図2は、本発明の実施の形態1における要因別優先度テーブル150の状態を示す図である。図2では、I/Oデバイス141、142および143の割り込み優先度を示している。図2において、I/Oデバイス142の割込み要求はI/Oデバイス141より優先的に処理されるべき割込みであるとし、I/Oデバイス143の割込み要求はI/Oデバイス142より優先的に処理されるべき割込みであるとしている。すなわち、要因別優先度テーブル150では、図2に示すように割込み優先度の値が大きい程優先度が高いと定義し、I/Oデバイス間の割込みの優先順位を表現している。

図3は、本発明の実施の形態1における割込み優先度と割込み許可プロセッサ数との関係を示す図である。図4は、本発明の実施の形態1におけるマスクレベルレジスタ値を示す図である。

図3では、図2に示す各々のI/Oデバイス(141、142および143)の割込み優先度に対して、割込みを許可するプロセッサの総数を[割込み許可プロセッサ数]として示され、割込みを許可するプロセッサ(102、103または104)が[割込み許可プロセッサ一覧]として示される。

このとき、各々のプロセッサ(102、103および104)のマスクレベルレジスタ値は図4に示す値で定義される。具体的には、プロセッサ101は、図3に示されるように割込み優先度1以上の割込みを許可するため、図4で示されるマスクレベルレジスタ161の値は1となる。プロセッサ102は、図3で示されるように割込み優先度1の割込みを禁止し、割込み優先度2以上の割込みを許可するため、図4で示されるマスクレベルレジスタ162の値は2となる。プロセッサ103および104は、図3で示されるように割込み優先度2以下の割込みを禁止し、割込み優先度3以上の割込みを許可するため、図4で示されるマスクレベルレジスタ163および164の値は3となる。

次に、図1に示す本発明の実施形態1のマルチプロセッサシステムについて、例を用いて動作を説明する。

図5は、本発明の実施の形態1におけるI/Oデバイスの割込み要求の発生からプロセッサ別割込み処理の開始までの処理を示すフローチャートである。図6は、本発明の実施の形態1におけるプロセッサ別割込み処理を示すフローチャートである。

まず、例えばI/Oデバイス142で割込み要求が発生すると(S51)、I/Oインタフェース170を介して割込み生成器130に割込み要求が通知される(S52)。

次に、割込み生成器130は、図2に示す要因別優先度テーブル150を参照し、割込み要求を発生したI/Oデバイス142の割込み優先度を取得する(S53)。割込み生成器130は、I/Oデバイス142より取得したI/Oデバイス142の識別番号と、要因別優先度テーブル150より取得した割込み優先度1とを、共有バス110を介してすべてのプロセッサ(101、102、103および104)に通知する。なお、I/Oデバイス141および143が割込み要求を発生する場合も同様なので、説明は省略する。

次に、プロセッサ101、102、103および104は、割込み生成器130からの通知を受信し(S55)、プロセッサ101、102、103および104は各々プロセッサ別割込み処理を実行する(S56)。

以上のようにして、プロセッサ101、102、103および104は、プロセッサ別割込み処理を開始する。

次に、プロセッサ101、102、103および104は、図6に示すように、割込み生成器130から通知されたI/Oデバイス142の割込み優先度の値と、マスクレベルレジスタ161、162、163および164の値とを比較する(S561)。割込み生成器130から通知されたI/Oデバイス142の割込み優先度が、例えばマスクレベルレジスタ164の値未満であった場合は、マスクレベルレジスタ164を有するプロセッサ104は、割込み生成器130からの割込み通知を無視して実行中の処理を継続する(S562)。

また、割込み生成器130から通知されたI/Oデバイス142の割込み優先度の値が例えばプロセッサ102のマスクレベルレジスタ162の値以上であった場合は、プロセッサ102は、割込み生成器130からの割込み通知を受理し、実行中の処理を中断する(S563)。

次に、割込み生成器130からの割込み通知を受理したプロセッサ102は、プロセッサ101、103および104間で重複して割込みが処理されることを回避するため、排他制御を行う。すなわち、プロセッサ102は、割込み生成器130から通知されたI/Oデバイス142の識別番号について、該当する割込み処理を実行する権限の獲得を試みる(S564)。なお、プロセッサ(101、102、103および104)間の排他制御に関しては、ミューテックスなど多くの従来技術によって実現が可能である。

次に、割込み処理を実行する権限の獲得に失敗したならば(S565のNoの場合)、割込み処理をキャンセルし、割込み生成器130から通知を受ける以前の処理に復帰する(S、S566)。

割込み処理を実行する権限の獲得に成功したならば(S565のYesの場合)、割込み生成器130から通知されたI/Oデバイス142の識別番号に該当する割込み処理を実行する(S567)。

以上のようにして、プロセッサ101、102、103および104は、プロセッサ別割込み処理を行う。

ここで、例えばI/Oデバイス141が、割込み要求を発生した場合には、割込み生成器130からプロセッサ101、102、103および104に通知される割込み優先度は1であるのに対して、マスクレベルレジスタの値が1以下であるプロセッサはプロセッサ101のみであるため、S561の判定によってプロセッサ101のみが割込み生成器130からの通知を受理する。

したがって、I/Oデバイス141の割込み処理が開始されるまでの遅延時間は、プロセッサ101が割込み処理を開始するまでの時間となる。

このとき、プロセッサ102、103および104はS561における判定により割込み生成器130からの通知を無視するため、プロセッサ101、102、103および104のいずれにおいてもS566における割込み処理のキャンセルは発生せず、処理効率の低下を抑止できる。

また、例えば、I/Oデバイス143が割込み要求を発生した場合には、割込み生成器130からプロセッサ101、102、103および104に通知される割込み優先度は3であるのに対して、マスクレベルレジスタの値が3以下であるプロセッサはプロセッサ101、102、103および104のすべてであるため、S561における判定によってプロセッサ101、102、103および104すべてが割込み生成器130からの通知を受理する可能性がある。

したがって、プロセッサ101、102、103および104はいずれもS566における割込み処理のキャンセルが発生する可能性があるが、I/Oデバイス143の割込み処理が開始されるまでの遅延時間は、プロセッサ101、102、103および104が割込み処理を開始するまでの時間の中で最短となり、I/Oデバイス141が割込み要求を発生した場合と比較して、より高い応答性能を得られる。

以上のように、実施の形態1のマルチプロセッサシステムにおける割込み制御方法によれば、割込み優先度の低い割込みに対してはシステムの処理効率の低下を抑止し、割込み優先度の高い割込みに対しては、より高い応答性能を確保することが可能である。それにより、割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上できるマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法を実現することができる。

(実施の形態2)

実施の形態2では、I/Oデバイス141、142および143の各々の割込み優先度に対して、割込みを許可するプロセッサの割当てが適宜変更可能なマルチプロセッサシステムについて説明する。

実施の形態2では、I/Oデバイス141、142および143の各々の割込み優先度に対して、割込みを許可するプロセッサの割当てが適宜変更可能なマルチプロセッサシステムについて説明する。

図7は、本発明の実施の形態2におけるマルチプロセッサシステムの構成を示すブロック図である。図7に示すマルチプロセッサシステムは、実施の形態1の図1に示すマルチプロセッサシステムと比べて、共有メモリ720の構成が異なり、共有メモリ720は、優先度別プロセッサ数テーブル700が追加されている点が異なっている。なお、図1と同様の要素には同一の符号を付しており、詳細な説明は省略する。

図8は、本発明の実施の形態2における割込み優先度と割込み許可プロセッサ数との関係を示す図である。図8では、優先度別プロセッサ数テーブル700に記憶される情報の例を示している。

図8に示す優先度別プロセッサ数テーブル700は、第1の実施形態の図3と比べて、I/Oデバイスの割込み優先度における割込みを許可するプロセッサの総数の示し方が異なっている。すなわち、I/Oデバイスの割込み優先度における割込みを許可するプロセッサの総数を、I/Oデバイスの割込み優先度における現時点で割込みを許可しているプロセッサの総数を示す[割込み許可プロセッサ数(現在数)]と、I/Oデバイスの割込み優先度における割込みを許可すべきプロセッサの総数を示す[割込み許可プロセッサ数(適正数)]とに分割している。

さらに、図8に示す優先度別プロセッサ数テーブル700では、I/Oデバイスの割込み優先度において割込みを禁止されているプロセッサの一覧を示す[割込み禁止プロセッサ一覧]が追加されている。

図9は、本発明の実施の形態2のマルチプロセッサシステムにおける割込み許可プロセッサ数変更の処理を示すフローチャートである。

まず、図8における[割込み許可プロセッサ数(適正数)]の値を変更するよう、例えばプロセッサ104に指示される(S91)。ここで、指示されるプロセッサはプロセッサ101、プロセッサ102または103でもよく、いずれの場合も同様のため説明を省略する。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、図8における[割込み許可プロセッサ数(適正数)]の値を、指示された任意の適正数を示す値に変更する(S92)。言い換えれば、プロセッサ104により、共有メモリ720が有する優先度別プロセッサ数テーブル700の[割込み許可プロセッサ数(適正数)]の値が変更される(S92a、S92b)。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整が必要かどうかを判定する(S93)。ここで、マスクレベルレジスタ再調整が必要でないと判定した場合には(S93のNoの場合)、割込み許可プロセッサ数変更の処理を終了する。

プロセッサ104は、マスクレベルレジスタ再調整が必要であると判定した場合には(S93のYesの場合)、共有メモリ720が有する優先度別プロセッサ数テーブル700において割込み許可プロセッサ再割当て処理を行う(S94)。

次に、プロセッサ104は、S94において割込み許可プロセッサ再割当て処理されたプロセッサ(指定プロセッサ)に対してマスクレベルレジスタ値変更処理を行う(S95)。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整が必要かどうかを判定し(S96)、マスクレベルレジスタ再調整が必要でないと判定した場合には(S96のNoの場合)、割込み許可プロセッサ数変更の処理を終了する。マスクレベルレジスタ再調整が必要であると判定した場合には(S96のNoの場合)、S94からの処理は、マスクレベルレジスタ再調整が必要でないと判定するまで繰り返される。

以上のようにして、実施の形態2におけるマルチプロセッサシステムは、割込み許可プロセッサ数の変更の処理を行う。

図10は、S93またはS97においてマスクレベルレジスタの再調整が必要かを判定する処理を示すフローチャートである。

ここで、図9同様に、例えばプロセッサ104は、マスクレベルレジスタの再調整が必要かを判定し、再調整を実行するとする。なお、プロセッサ101、102および103の場合も同様のため説明は省略する。

まず、プロセッサ104は、共有メモリ720が有する優先度別プロセッサ数テーブル700を参照し、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度が存在するかどうかを確認する。プロセッサ104は、すべての指定割込み優先度における[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致するならば、再調整が必要な指定割込み優先度が存在しないと判定し(S931のNoの場合)、マスクレベルレジスタの再調整が必要でないとして判定処理を終了する。

次に、プロセッサ104は、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度が存在するならば(S931のYesの場合)、一致しない指定割込み優先度における割込み許可プロセッサの再割当て処理を行う(S94)。

以上のようにして、実施の形態2におけるマルチプロセッサシステムは、マスクレベルレジスタの再調整が必要かを判定する。

図11は、S94において割込み許可プロセッサ再割当て処理を示すフローチャートである。

ここで、図9および図10同様に、例えばプロセッサ104が、割込み許可プロセッサ再割当て処理を実行するとする。なお、プロセッサ101、102および103の場合も同様のため説明は省略する。

まず、プロセッサ104は、共有メモリ720が有する優先度別プロセッサ数テーブル700を参照する。プロセッサ104は、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]との値を比較する。そして、プロセッサ104は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

次に、プロセッサ104は、[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より大きいならば、割込みが許可されたプロセッサ数(現在数)が過多であると判断する(S952のYesの場合)。次いで、プロセッサ104は、優先度別プロセッサ数テーブル700における[割込み許可プロセッサ一覧]に含まれるプロセッサから、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]との差分に相当する数のプロセッサを変更対象として選択する(S953)。プロセッサ104は、変更対象として選択した各々のプロセッサに対して、対応するマスクレベルレジスタの割込み優先度の値を、例えば「I/0デバイスの割込み優先度(以下、指定割込み優先度と呼ぶ)+1」に変更するよう、共有バス110を介して通知する(S954)。

また、プロセッサ104は、S952において、[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より小さいならば、割込みが許可されたプロセッサ数(現在数)が不足していると判断する(S952のNoの場合)。次いで、プロセッサ104は、優先度別プロセッサ数テーブル700における[割込み禁止プロセッサ一覧]に含まれるプロセッサから、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]との差分に相当する数のプロセッサを変更対象として選択する(S955)。プロセッサ104は、変更対象として選択した各々のプロセッサそれぞれに対して、対応するマスクレベルレジスタの割込み優先度の値を例えば指定優先度の値に変更するよう、共有バス110を介して通知する(S956)。

以上のようにして、実施の形態2におけるマルチプロセッサシステムは、割込み許可プロセッサ再割当て処理を実行する。

図12は、S954またはS956においてマスクレベルレジスタ値変更処理を示すフローチャートである。なお、プロセッサ101、102および103の場合も同様のため説明は省略する。

ここで、図9および図10同様に、例えばプロセッサ104が、割込み許可プロセッサ再割当てを実行するとする。

S954またはS956において、プロセッサ104により、マスクレベルレジスタの割込み優先度の値の変更を指示されたプロセッサは、対応するマスクレベルレジスタの割込み優先度の値を、指定された値に変更する(S951)。

次に、プロセッサ104は、マスクレベルレジスタの変更後の割込み優先度の値より低い指定割込み優先度(I/0デバイスの割込み優先度)において、そのマスクレベルレジスタに対応するプロセッサが[割込み許可プロセッサ一覧]に含まれているならば、[割込み許可プロセッサ一覧]からプロセッサを削除する。そして、プロセッサ104は、[割込み禁止プロセッサ一覧]に、削除したプロセッサを追加するとともに、[割込み許可プロセッサ数(現在数)]から1を減算することで、優先度別プロセッサ数テーブル700を更新する(S952)。

また、プロセッサ104は、マスクレベルレジスタの変更後の割込み優先度の値以上の指定割込み優先度(I/0デバイスの割込み優先度)において、そのマスクレベルレジスタに対応するプロセッサが[割込み禁止プロセッサ一覧]に含まれているならば、[割込み禁止プロセッサ一覧]からプロセッサを削除する。そして、プロセッサ104は、[割込み許可プロセッサ一覧]に削除したプロセッサを追加するとともに、[割込み許可プロセッサ数(現在数)]に1を加算することで、優先度別プロセッサ数テーブル700を更新する(S952)。

以上のようにして、実施の形態2におけるマルチプロセッサシステムは、マスクレベルレジスタ値変更処理を実行する。

次に、図7に示す本発明の実施の形態2のマルチプロセッサシステムについて、例を用いてその動作を説明する。

ここで、優先度別プロセッサ数テーブル700が、図8に示す状態にあるとする。このとき、プロセッサ104が、I/Oデバイスの割込み優先度(指定割込み優先度)2における割込みを許可すべきプロセッサ数を、2から1に変更する場合の動作を例に挙げて説明する。

図13、図14および図15は、優先度別プロセッサ数テーブル700と各プロセッサのマスクレベルレジスタの状態とを示す図である。

まず、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、指定割込み優先度2に対応する[割込み許可プロセッサ数(適正数)]を2から1に変更する(S92)。ここで、S92の処理実行直後の優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104におけるマスクレベルレジスタ161、162、163および164との状態は、図13に示すとおりである。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整が必要かどうかを判定し(S93)、割込み許可プロセッサの再割当て処理を行う(S94)。

具体的には、S93においてプロセッサ104は、優先度別プロセッサ数テーブル700を参照し、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度が存在するかどうかを確認する。プロセッサ104は、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度2が存在するため(S931のYesの場合)、指定割込み優先度2における割込み許可プロセッサの再割当て処理を行う(S94)。

S94において、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、指定割込み優先度2に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]の値とを比較する。そして、プロセッサ104は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

プロセッサ104は、指定割込み優先度2に対応する[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より1大きいので、割込みが許可されているプロセッサの数が過多であると判断する(S952のYesの場合)。次に、プロセッサ104は、[割込み許可プロセッサ一覧]に含まれるプロセッサから1つのプロセッサを変更対象として選択する(S953)。プロセッサ104は、変更対象として選択した例えばプロセッサ101に対して、マスクレベルレジスタ161の値を1から3(指定割込み優先度2+1)に変更するよう共有バス110を介して通知する(S954)。なお、ここでは、マスクレベルレジスタを変更するプロセッサとしてプロセッサ101が選択されたものとしているがそれに限らない。

次に、プロセッサ104は、S94において、割込み許可プロセッサ再割当て処理されたプロセッサに対してマスクレベルレジスタ値変更処理を行う(S95)。

具体的には、S95において、プロセッサ104により、マスクレベルレジスタ161の割込み優先度の値の変更を指示されたプロセッサ101は、マスクレベルレジスタ161の値を1から3に変更する(S951)。次に、プロセッサ104は、指定割込み優先度1および2における[割込み許可プロセッサ一覧]からプロセッサ101を削除する。そして、プロセッサ104は、[割込み禁止プロセッサ一覧]にプロセッサ101を追加するとともに、[割込み許可プロセッサ数(現在数)]から1を減算することで、優先度別プロセッサ数テーブル700を更新する(S952)。このとき、指定割込み優先度3における[割込み禁止プロセッサ一覧]にはプロセッサ101が含まれていないため、指定割込み優先度3における[割込み許可プロセッサ数(現在数)]の変更は行わない。

ここで、S952の処理実行直後の優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104におけるマスクレベルレジスタ161、162、163および164の状態は、図14に示すとおりである。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整がさらに必要かどうかを判定し(S96)、割込み許可プロセッサの再割当て処理を再度行う(S94)。

具体的には、プロセッサ104は、S96において、優先度別プロセッサ数テーブル700を参照し、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度が存在するかどうかを確認する。プロセッサ104は、指定割込み優先度1における[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しないため(S931のYesの場合)、指定割込み優先度1における割込み許可プロセッサの再割当て処理を行う(S94)。

S94において、プロセッサ104は優先度別プロセッサ数テーブル700を参照し、指定割込み優先度1に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]の値とを比較する。そして、プロセッサ104は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

プロセッサ104は、指定割込み優先度1に対応する[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より1小さいため、割込みが許可されているプロセッサの数が不足していると判断する(S952のNoの場合)。次に、プロセッサ104は、[割込み禁止プロセッサ一覧]に含まれるプロセッサから1つのプロセッサを変更対象として選択する(S955)。プロセッサ104は、変更対象として選択した例えばプロセッサ102に対して、マスクレベルレジスタ162の値を2から1(指定割込み優先度1)に変更するよう共有バス110を介して通知する(S956)。なお、ここでは、マスクレベルレジスタを変更するプロセッサとしてプロセッサ102が選択されたものとしているがそれに限らない。

次に、プロセッサ104は、S94において、割込み許可プロセッサ再割当て処理されたプロセッサに対してマスクレベルレジスタ値変更処理を行う(S95)。

具体的には、S95において、プロセッサ104により、マスクレベルレジスタ162の割込み優先度の値の変更を指示されたプロセッサ102はマスクレベルレジスタ162の値を2から1に変更する(S951)。次に、プロセッサ104は、指定割込み優先度1における[割込み禁止プロセッサ一覧]からプロセッサ102を削除する。そして、プロセッサ104は、[割込み許可プロセッサ一覧]にプロセッサ102を追加するとともに、[割込み許可プロセッサ数(現在数)]に1を加算することで、優先度別プロセッサ数テーブル700を更新する(S952)。このとき、指定割込み優先度2および3における[割込み禁止プロセッサ一覧]にはプロセッサ102が含まれていないため、指定割込み優先度2および3における[割込み許可プロセッサ数(現在数)]の変更は行わない。

ここで、S952の処理実行直後における優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104におけるマスクレベルレジスタ161、162、163および164の状態は、図15に示すとおりである。

次に、プロセッサ104は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整がさらに必要かどうかを判定する(S96)。プロセッサ104は、図15に示すように、すべての指定割込み優先度における[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致するため、マスクレベルレジスタ再調整が必要でないと判定し(S96のNoの場合)、割込み許可プロセッサ数変更の処理を終了する。

以上のように、本実施の形態2のマルチプロセッサシステムは、すべての指定割込み優先度において、割込みを許可されているプロセッサの総数([割込み許可プロセッサ数(現在数)])と割込みを許可すべきプロセッサの総数([割込み許可プロセッサ数(適正数)])とが一致するように各々のプロセッサにおけるマスクレベルレジスタの再調整を実行することにより、割込み許可プロセッサ数の変更の処理を行う。

以上、実施の形態2のマルチプロセッサシステムにおける割込み制御方法によれば、実施の形態1のマルチプロセッサシステムにおける割込み制御方法に加え、割込みを許可するプロセッサの割当てを任意に変更することが可能である。それにより、割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上できるマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法を実現することができる。

(実施の形態3)

実施の形態3では、実施の形態2におけるマルチプロセッサシステムの割込み制御方法において、さらに、全プロセッサの中から割込み許可するプロセッサを選択する際に選択基準を設け、システム全体の最適化を図るマルチプロセッサシステムの割込み制御方法について説明する。

実施の形態3では、実施の形態2におけるマルチプロセッサシステムの割込み制御方法において、さらに、全プロセッサの中から割込み許可するプロセッサを選択する際に選択基準を設け、システム全体の最適化を図るマルチプロセッサシステムの割込み制御方法について説明する。

特に、本実施の形態3では、マルチプロセッサシステム上で複数のタスクを制御するOS(Operating System)において、各々のプロセッサが実行するタスクのタスク優先度を選択基準とし、タスク優先度の高いタスクを効率的に実行するマルチプロセッサシステムの割込み制御方法について説明する。

図16は、本発明の実施の形態3におけるマルチプロセッサシステムの構成を示すブロック図である。図16に示すマルチプロセッサシステムは、実施の形態2における図7に示すマルチプロセッサシステムと比べて、共有メモリ1620の構成が異なり、共有メモリ1620は、プロセッサ別タスク優先度テーブル1600がさらに追加されている点が異なっている。なお、図1および図7と同様の要素には同一の符号を付しており、詳細な説明は省略する。また、実施の形態3におけるマルチプロセッサシステムは、実施の形態2におけるマルチプロセッサシステム同様に、図9に示す割込み許可プロセッサ数の変更の処理を行う。

プロセッサ別タスク優先度テーブル1600では、プロセッサ(101、102、103および104)毎に、プロセッサ(101、102、103および104)が実行中のタスクのタスク優先度が記憶される。

図17は、実施の形態3におけるS94においての割込み許可プロセッサの再割当て処理を示すフローチャートである。なお、実施の形態2における図11と同様の処理には同一の符号を付しており、詳細な説明は省略する。

図17は、実施の形態2における図11と比べて、割込みが許可されているプロセッサの中から、割込みを禁止に変更するプロセッサを選択するステップ(S953)を、実行中のタスク優先度の高いプロセッサを優先的に選択するステップ(S1753)に拡張している点が異なっている。また、実施の形態2における図11と比べて、割込みが禁止されているプロセッサの中から、割込みを許可に変更するプロセッサを選択するステップ(S955)を、実行中のタスク優先度の低いプロセッサを優先的に選択するステップ(S1755)に拡張している点が異なっている。

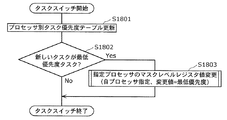

図18は、実施の形態3においてタスクスイッチ時に割込み許可プロセッサを更新する処理を示すフローチャートである。

タスクスイッチを実行するプロセッサ101、102、103または104は、共有メモリ720が有するプロセッサ別タスク優先度テーブル1600を参照し、プロセッサ101、102、103または104に対応するタスク優先度を、プロセッサ101、102、103または104が新しく実行するタスクの優先度に変更する(S1801)。

次に、プロセッサ101、102、103または104(以下、指定プロセッサと呼ぶ)の新しく実行するタスクの優先度が、例えばアイドル等の最低優先度である場合(S1802のYesの場合)、指定プロセッサおよび指定プロセッサのマスクレベルレジスタにおける割込優先度を最低優先度の割込み優先度に変更して、指定プロセッサのマスクレベルレジスタの値変更処理を実行する(S1803)。なお、S1803における指定プロセッサのマスクレベルレジスタの値変更処理は、実施の形態2における図12と同様のため説明を省略する。

以上のようにして、実施の形態3におけるマルチプロセッサシステムは、タスクスイッチ時に割込み許可プロセッサを更新する処理を実行する。それにより、この処理以降は最低優先度のタスクを実行するプロセッサが割込み許可プロセッサとして決定されるとともに、代わって高優先度のタスクを実行するプロセッサが割込み禁止プロセッサとなるため、高優先度のタスクを効率的に実行することが可能となる。

次に、図16に示す本発明の実施の形態3におけるマルチプロセッサシステムについて、例を用いてその動作の詳細を説明する。

図19および図20は、プロセッサ別タスク優先度テーブル1600の状態を示す図である。図21および図22は、優先度別プロセッサ数テーブル700と、各プロセッサのマスクレベルレジスタと、プロセッサ別タスク優先度テーブル1600との状態を示す図である。

ここで、優先度別プロセッサ数テーブル700は、図8に示す状態にあり、プロセッサ別タスク優先度テーブル1600は図19に示す状態にあるとする。このとき、プロセッサ102でタスクスイッチが発生し、プロセッサ102のタスク優先度が最低優先度タスク(優先度1)にスイッチする場合の動作を例に挙げて説明する。

まず、プロセッサ102は、プロセッサ別タスク優先度テーブル1600を参照し、プロセッサ102に対応するタスク優先度を3から最低優先度である1に変更する(S1801)。ここで、S1801の処理実行直後におけるプロセッサ別タスク優先度テーブル1600の状態は、図20に示すとおりである。

次に、プロセッサ102の新しく実行するタスクの優先度が、最低優先度、すなわちプロセッサ102におけるタスクスイッチ先が最低優先度タスクであるため、プロセッサ102に対応するマスクレベルレジスタ162の値を最低優先度である割込み優先度1に変更する。そしてプロセッサ102は、指定プロセッサのマスクレベルレジスタの値変更処理を実行する(S1802)。

S1802において、まず、プロセッサ102は、対応するマスクレベルレジスタ162の値を2から1に変更する(S951)。次に、プロセッサ102は、指定割込み優先度1における[割込み禁止プロセッサ一覧]からプロセッサ102を削除する。そして、プロセッサ102は、[割込み許可プロセッサ一覧]に、プロセッサ102を追加するとともに、[割込み許可プロセッサ数(現在数)]に1を加算する(S952)。ここで、S952の処理実行直後における優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104のマスクレベルレジスタ161、162、163および164と、プロセッサ別タスク優先度テーブル1600との状態は、図21に示すとおりである。

次に、プロセッサ102は、図9に示すように、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整が必要かどうかを判定し(S93)、割込み許可プロセッサの再割当て処理を行う(S94)。

具体的には、S93においてプロセッサ102は、優先度別プロセッサ数テーブル700を参照し、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度1が存在するため(S931のYesの場合)、指定割込み優先度1における割込み許可プロセッサの再割当て処理を行う(S94)。

S94において、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、指定割込み優先度1に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]の値とを比較する。そして、プロセッサ104は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

プロセッサ102は、指定割込み優先度1に対応する[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より1大きいので、割込みが許可されているプロセッサの数が過多であると判断する(S952のYesの場合)。次に、プロセッサ102は、[割込み許可プロセッサ一覧]に含まれるプロセッサから、実行中のタスクのタスク優先度が最も高いプロセッサ101を選択し(S1753)、マスクレベルレジスタ161の値を1から2に変更するよう通知する(S954)。

次に、プロセッサ102は、S94において、割込み許可プロセッサ再割当て処理されたプロセッサに対してマスクレベルレジスタ値変更処理を行う(S95)。

具体的には、S95において、プロセッサ102により、マスクレベルレジスタ161の割込み優先度の値の変更を指示されたプロセッサ101は、マスクレベルレジスタ161の値を1から2に変更する(S951)。次に、プロセッサ102は、指定割込み優先度1における[割込み許可プロセッサ一覧]からプロセッサ101を削除する。そして、プロセッサ102は、[割込み禁止プロセッサ一覧]に、プロセッサ101を追加するとともに、[割込み許可プロセッサ数(現在数)]から1を減算する(S952)。ここで、S952の処理実行直後の優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104におけるマスクレベルレジスタ161、162、163および164の状態は、図22に示すとおりである。

次に、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整がさらに必要かどうかを判定する(S96)。プロセッサ102は、図22に示ように、すべての割込み優先度について[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致するため、マスクレベルレジスタ再調整が必要でないと判定し(S96のNoの場合)、割込み許可プロセッサ数変更の処理を終了する。

このとき、プロセッサ101のマスクレベルレジスタ161の値はプロセッサ102のマスクレベルレジスタ162の値より高く設定されており、タスク優先度の高いタスクを実行中のプロセッサにおける割込み発生が抑止されている。

以上のように、本実施の形態3のマルチプロセッサシステムは、割込み許可プロセッサ数の変更の処理を行う。

以上、説明してきたように、本実施の形態3によれば、タスク優先度の高いタスクを効率的に実行するマルチプロセッサシステムの割込み制御方法が実現できる。

なお、実施の形態3において、割込み許可プロセッサ再割当て処理は、最低優先度のタスクにスイッチする際に実行しているが、他の任意のタイミングで実行するものとしても良い。例えば、任意の優先度のタスクにスイッチする際に実行してもよいし、タイマハンドラを使用するなどして周期的に実行してもよい。

(実施の形態4)

本実施の形態4では、実施の形態3同様に、実施の形態2のマルチプロセッサシステムの割込み制御方法において、さらに、全プロセッサの中から割込み許可プロセッサを選択する際に選択基準を設け、システム全体の最適化を図るマルチプロセッサシステムの割込み制御方法について説明する。

本実施の形態4では、実施の形態3同様に、実施の形態2のマルチプロセッサシステムの割込み制御方法において、さらに、全プロセッサの中から割込み許可プロセッサを選択する際に選択基準を設け、システム全体の最適化を図るマルチプロセッサシステムの割込み制御方法について説明する。

特に、本実施の形態4では、各々のプロセッサにおける割込み発生頻度を選択基準とし、特定のプロセッサで割込みが集中的に発生することを回避し、割込み処理の分散を図るマルチプロセッサシステムの割込み制御方法について説明する。

図23は、本発明の実施の形態4におけるマルチプロセッサシステムの構成を示すブロック図である。図23に示すマルチプロセッサシステムは、実施の形態2における図7に示すマルチプロセッサシステムと比べて、共有メモリ2320の構成が異なり、共有メモリ2320は、プロセッサ別割込み回数テーブル2300がさらに追加されている点が異なっている。なお、図1および図7と同様の要素には同一の符号を付しており、詳細な説明は省略する。また、実施の形態4におけるマルチプロセッサシステムは、実施の形態2におけるマルチプロセッサシステム同様に、図9に示す割込み許可プロセッサ数の変更の処理を行う。

プロセッサ別割込み回数テーブル2300では、プロセッサ(101、102、103および104)毎に、プロセッサ(101、102、103および104)が割込み処理を実行した回数が記憶される。

図24は、本発明の実施の形態4におけるS94においての割込み許可プロセッサの再割当て処理を示すフローチャートである。なお、実施の形態2における図11と同様の処理には同一の符号を付しており、詳細な説明は省略する。

図24は、実施の形態2における図11と比べて、割込みが許可されているプロセッサの中から割込みを禁止に変更するプロセッサを選択するステップ(S953)を、割込み発生回数が多いプロセッサを優先的に選択するステップ(S2453)に拡張している点が異なっている。また、実施の形態2における図11と比べて、割込みが禁止されているプロセッサの中から割込みを許可に変更するプロセッサを選択するステップ(S955)を、割込み発生回数が少ないプロセッサを優先的に選択するステップ(S2455)に拡張している点が異なっている。

図25は、実施の形態4におけるプロセッサ別割込み処理を示すフローチャートである。なお、実施の形態1における図6と同様の処理には同一の符号を付しており、詳細な説明は省略する。

図25は、実施の形態1の図6と比べて、割込み処理の権限獲得直後(S565のYesの場合)に、プロセッサ別割込み回数テーブル2300を参照し、自プロセッサに対応する割込み回数をインクリメントするステップ(S2501)が追加されている。さらに、指定プロセッサおよび指定プロセッサのマスクレベルレジスタにおける割込優先度を例えば最高優先度+1となる割込み優先度に変更して、指定プロセッサのマスクレベルレジスタ値変更処理を実行するステップ(S2502)が追加されている点が異なっている。なお、S2502における指定プロセッサのマスクレベルレジスタの値変更処理は、実施の形態2における図12と同様のため説明を省略する。

以上のようにして、実施の形態4におけるマルチプロセッサシステムは、プロセッサ別割込み処理を実行する。

次に、図23に示す本発明の実施の形態4におけるマルチプロセッサシステムについて、例を用いてその詳細な動作を説明する。

図26および図27は、プロセッサ別割込み回数テーブル2300の状態を示す図である。図28、図29および図30は、優先度別プロセッサ数テーブル700と、各プロセッサのマスクレベルレジスタと、プロセッサ別割込み回数テーブル2300との状態を示す図である。

ここで、優先度別プロセッサ数テーブル700は、図8に示す状態にあり、プロセッサ別割込み回数テーブル2300は、図26に示す状態にあるとする。このとき、I/Oデバイス142が割込み要求を発生し、プロセッサ102が割込み処理を実行した場合の動作を例に挙げて説明する。

プロセッサ102は、割込み処理権限を獲得後(S565のYesの場合)に、プロセッサ別割込み回数テーブル2300を参照し、プロセッサ102に対応する割込み回数をインクリメントする(S2501)。すなわちプロセッサ102は、プロセッサ102に対応する割込み回数を2から3に変更する。ここで、S2501の処理実行直後のプロセッサ別割込み回数テーブル2300の状態は、図27に示すとおりである。

次に、プロセッサ102は、プロセッサ102、および、割込み優先度4を指定し、マスクレベルレジスタ162の値を変更する処理を開始する(S2502)。

S2502において、まず、プロセッサ102は、自プロセッサ102に対応するマスクレベルレジスタ162の値を2から4に変更する(S951)。次に、プロセッサ102は、指定割込み優先度2および3における[割込み許可プロセッサ一覧]からプロセッサ102を削除する。そして、プロセッサ102は、[割込み禁止プロセッサ一覧]にプロセッサ102を追加するとともに、[割込み許可プロセッサ数(現在数)]から1を減算する(S1202)。ここで、S952の処理実行直後における優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104のマスクレベルレジスタ161、162、163および164と、プロセッサ別割込み回数テーブル2300との状態は、図28に示すとおりである。

次に、プロセッサ102は、図9に示すように、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整が必要かどうかを判定し(S93)、割込み許可プロセッサの再割当て処理を行う(S94)。

具体的には、S93においてプロセッサ102は、優先度別プロセッサ数テーブル700を参照し、[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しない指定割込み優先度2が存在するため(S931のYesの場合)、指定割込み優先度2における割込み許可プロセッサの再割当て処理を行う(S94)。

S94において、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、指定割込み優先度2に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]の値とを比較する。そして、プロセッサ102は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

プロセッサ102は、指定割込み優先度2に対応する[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より1小さいため、割込みが許可されているプロセッサの数が不足していると判断する(S952のNoの場合)。次に、プロセッサ104は、[割込み禁止プロセッサ一覧]に含まれるプロセッサから、割込み回数が最も少ないプロセッサ103を選択する(S955)。プロセッサ102は、プロセッサ103に対してマスクレベルレジスタ163の値を3から2に変更するよう通知する(S956)。

次に、プロセッサ102は、S94において、割込み許可プロセッサ再割当て処理されたプロセッサに対してマスクレベルレジスタ値変更処理を行う(S95)。

具体的には、S95において、プロセッサ102により、マスクレベルレジスタ163の割込み優先度の値の変更を指示されたプロセッサ103は、自プロセッサのマスクレベルレジスタ163の値を2に変更する(S951)。次に、プロセッサ102は、指定割込み優先度2における[割込み禁止プロセッサ一覧]からプロセッサ103を削除する。そして、プロセッサ102は、[割込み許可プロセッサ一覧]にプロセッサ103を追加するとともに、[割込み許可プロセッサ数(現在数)]に1を加算する(S952)。ここで、S952の処理実行直後の優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104におけるマスクレベルレジスタ161、162、163および164との状態は、図29に示すとおりである。

次に、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整がさらに必要かどうかを判定し(S96)、割込み許可プロセッサの再割当て処理を再度行う(S94)。

具体的には、プロセッサ102は、S96において、優先度別プロセッサ数テーブル700を参照し、図29に示すように、指定割込み優先度3における[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致しないため(S931のYesの場合)、指定割込み優先度3における割込み許可プロセッサの再割当て処理を行う(S94)。

S94において、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、指定割込み優先度3に対応する[割込み許可プロセッサ数(現在数)]の値と[割込み許可プロセッサ数(適正数)]の値とを比較する。そして、プロセッサ104は、割込みが許可されたプロセッサ数(現在数)が過多であるかどうかを判断する(S952)。

プロセッサ102は、指定割込み優先度3に対応する[割込み許可プロセッサ数(現在数)]が[割込み許可プロセッサ数(適正数)]より1小さいため、割込みが許可されているプロセッサの数が不足していると判断する(S952のNoの場合)。次に、プロセッサ102は、[割込み禁止プロセッサ一覧]に含まれるプロセッサから、割込み回数が最も少ないプロセッサ102を選択し(S2455)、マスクレベルレジスタ162の値を3に変更するよう通知する(S956)。

次に、プロセッサ102は、S94において、割込み許可プロセッサ再割当て処理されたプロセッサに対してマスクレベルレジスタ値変更処理を行う(S95)。

すなわち、S95において、プロセッサ102は、自プロセッサのマスクレベルレジスタ162の値を3に変更する(S951)。次に、プロセッサ102は、指定割込み優先度3における[割込み禁止プロセッサ一覧]からプロセッサ102を削除する。そして、プロセッサ102は、[割込み許可プロセッサ一覧]にプロセッサ102を追加するとともに、[割込み許可プロセッサ数(現在数)]に1を加算する(S952)。ここで、S952の処理実行直後における優先度別プロセッサ数テーブル700と、プロセッサ101、102、103および104のマスクレベルレジスタ161、162、163および164との状態は、図30に示すとおりである。

次に、プロセッサ102は、優先度別プロセッサ数テーブル700を参照し、マスクレベルレジスタ再調整がさらに必要かどうかを判定する(S96)。プロセッサ102は、図30に示すように、すべての指定割込み優先度における[割込み許可プロセッサ数(現在数)]と[割込み許可プロセッサ数(適正数)]とが一致するため、マスクレベルレジスタ再調整が必要でないと判定し(S96のNoの場合)、割込み許可プロセッサ数変更の処理を終了する。

このとき、プロセッサ102のマスクレベルレジスタ162の値はプロセッサ101および103のマスクレベルレジスタ161および163の値より高く設定されており、割込み発生回数の多いプロセッサにおける割込み発生が抑止されている。

以上のように、本実施の形態4のマルチプロセッサシステムは、割込み許可プロセッサ数の変更の処理を行う。

以上、説明してきたように、本実施の形態4によれば、特定のプロセッサで割込みが集中的に発生することを回避し、割込み処理を分散するマルチプロセッサシステムの割込み制御方法が実現できる。

なお、実施の形態4において、割込み許可プロセッサの再割当て処理を、割込み処理の権限を獲得した直後に実行しているが、他の任意のタイミングで実行するものとしても良い。例えば、割込み処理完了後に実行してもよいし、一定回数割込みを処理した際に実行してもよいし、タイマハンドラを使用するなどして周期的に実行してもよい。

以上、本発明のマルチプロセッサシステムにおける割込み制御方法によれば、マルチプロセッサシステムにおける割込み応答性の高度な要求に対応し、かつ、システム全体の処理効率を向上できる。したがって、マルチプロセッサで構成されるマイクロコンピュータの高機能化、および、低消費電力化が実現できる。それにより、割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上できるマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法を実現することができる。

以上、本発明のプログラム実行装置およびプログラム実行装置制御方法について、実施の形態に基づいて説明したが、本発明は、この実施の形態に限定されるものではない。本発明の趣旨を逸脱しない限り、当業者が思いつく各種変形を本実施の形態に施したものや、異なる実施の形態における構成要素を組み合わせて構築される形態も、本発明の範囲内に含まれる。

例えば、本発明の実施形態において、割込み生成器130からプロセッサへの割込みの通知は共有バス110を介して行っているが、専用の信号線を備えるなど、他の手段を用いてもよい。

また、割込み優先度に応じて割込み許可プロセッサを選択できる構成は、本発明の実施の形態において説明したものが特に望ましいが、これに限定されるものではない。

本発明は、マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法に利用でき、特に、マルチプロセッサにおいて割込みを制御するマルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法に利用することができる。

101、102、103、104、3101、3102、3103、3104 プロセッサ

110、3110 共有バス

120、720、1620、2320、3120 共有メモリ

130、3130 割込み生成器

141、142、143 I/Oデバイス

150 要因別優先度テーブル

161、162、163、164 マスクレベルレジスタ

170 I/Oインタフェース

700 優先度別プロセッサ数テーブル

1600 プロセッサ別タスク優先度テーブル

2300 プロセッサ別割込み回数テーブル

3100 指定レジスタ

110、3110 共有バス

120、720、1620、2320、3120 共有メモリ

130、3130 割込み生成器

141、142、143 I/Oデバイス

150 要因別優先度テーブル

161、162、163、164 マスクレベルレジスタ

170 I/Oインタフェース

700 優先度別プロセッサ数テーブル

1600 プロセッサ別タスク優先度テーブル

2300 プロセッサ別割込み回数テーブル

3100 指定レジスタ

Claims (7)

- レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの割込み制御方法であって、

対応するプロセッサが割込みを許容する許容度を示すマスクレベル値を前記レジスタに設定する設定ステップと、

各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知ステップと、

前記割込み優先度の値に比べて低いマスクレベル値に設定されたレジスタを有するプロセッサのいずれかが、前記割込み要求を受理する割込み受理ステップとを含む

ことを特徴とするマルチプロセッサシステムの割込み制御方法。 - 前記マルチプロセッサシステムの割込み制御方法は、さらに、

前記複数のI/Oデバイスの割込み優先度毎に、割込み要求を受理可能なプロセッサの数である第1プロセッサ数と、割込み要求を受理可能にすべきプロセッサの数である第2プロセッサ数とを示すテーブルをメモリに保持させるステップと、

前記第2プロセッサ数を変更する変更ステップと、

前記第2プロセッサ数が変更された場合、変更された前記第2プロセッサ数に第1プロセッサ数を一致させるように、前記複数のマスクレベル値の少なくとも1つを変更するマスクレベル変更ステップとを含む

ことを特徴とする請求項1に記載のマルチプロセッサシステムの割込み制御方法。 - レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムであって、

対応するプロセッサが割込みを許容する許容度を示すマスクレベル値を前記レジスタに設定する設定手段と、

各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知手段と、

前記割込み優先度の値に比べて低いマスクレベル値に設定されるレジスタを有するプロセッサのいずれかが、前記割込み要求を受理する割込み受理手段とを備える

ことを特徴とするマルチプロセッサシステム。 - 前記マルチプロセッサシステムは、さらに、

前記複数のI/Oデバイスの割込優先度毎に、割込み要求を受理可能なプロセッサの数である第1プロセッサ数と、割込み要求を受理可能にすべきプロセッサの数である第2プロセッサ数とを保持する保持手段と、

前記第2プロセッサ数を変更する変更手段と、

前記第2プロセッサ数が変更された場合、変更された前記第2プロセッサ数に第1プロセッサ数を一致させるように、前記複数のマスクレベル値の少なくとも1つを変更するマスクレベル変更手段とを備える

ことを特徴とする請求項3に記載のマルチプロセッサシステム。 - さらに、前記各プロセッサで実行されるタスクのタスク優先度を保持するタスク優先度保持手段と、

前記各プロセッサで実行されるタスクに従って、前記タスク優先度を変更するタスク優先度変更手段とを備え、

前記変更手段は、前記タスク優先度が変更される場合、前記タスク優先度に従って、前記第2プロセッサ数を変更する

ことを特徴とする請求項4に記載のマルチプロセッサシステム。 - さらに、前記各プロセッサの割込み発生頻度を保持するタスク優先度保持手段と、

前記各プロセッサで実行される割込み回数に従って、前記割込み発生頻度を変更する割込み発生頻度変更手段とを備え、

前記変更手段は、前記割込み発生頻度が変更される場合、前記割込み発生頻度に従って、前記第2プロセッサ数を変更する

ことを特徴とする請求項4に記載のマルチプロセッサシステム。 - レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの集積回路であって、

対応するプロセッサが割込みを許容する許容度を示すマスクレベル値を前記レジスタに設定する設定手段と、

各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知手段と、

前記割込み優先度に比べて低いマスクレベル値に設定されたレジスタを有するプロセッサのいずれかが、前記割込み要求を受理する割込み受理手段とを備える

ことを特徴とするマルチプロセッサシステムの集積回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008097226A JP2009251802A (ja) | 2008-04-03 | 2008-04-03 | マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 |

| PCT/JP2009/001285 WO2009122670A1 (ja) | 2008-04-03 | 2009-03-24 | マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 |

| CN2009801115781A CN102099797A (zh) | 2008-04-03 | 2009-03-24 | 多处理器系统以及多处理器系统的中断控制方法 |

| US12/892,136 US20110016247A1 (en) | 2008-04-03 | 2010-09-28 | Multiprocessor system and multiprocessor system interrupt control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008097226A JP2009251802A (ja) | 2008-04-03 | 2008-04-03 | マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2009251802A true JP2009251802A (ja) | 2009-10-29 |

Family

ID=41135079

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008097226A Pending JP2009251802A (ja) | 2008-04-03 | 2008-04-03 | マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20110016247A1 (ja) |

| JP (1) | JP2009251802A (ja) |

| CN (1) | CN102099797A (ja) |

| WO (1) | WO2009122670A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102918516A (zh) * | 2010-06-23 | 2013-02-06 | 国际商业机器公司 | 适配器中断源的类型的标识 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2166457B1 (en) * | 2008-09-12 | 2014-04-23 | TELEFONAKTIEBOLAGET LM ERICSSON (publ) | Interrupt controller and methods of operation |

| US8407710B2 (en) * | 2010-10-14 | 2013-03-26 | International Business Machines Corporation | Systems and methods for dynamically scanning a plurality of active ports for priority schedule of work |

| US9330035B2 (en) | 2013-05-23 | 2016-05-03 | Arm Limited | Method and apparatus for interrupt handling |

| CN104424145A (zh) * | 2013-08-30 | 2015-03-18 | 联想(北京)有限公司 | 一种电子设备及数据传输方法 |

| CN104424122B (zh) * | 2013-09-09 | 2018-10-12 | 联想(北京)有限公司 | 一种电子设备及内存划分方法 |

| US9665508B2 (en) * | 2013-12-26 | 2017-05-30 | Cavium, Inc. | Method and an apparatus for converting interrupts into scheduled events |

| CN108073545A (zh) * | 2016-11-17 | 2018-05-25 | 联芯科技有限公司 | 一种多处理器通信装置及方法 |

| CN110737616B (zh) * | 2018-07-20 | 2021-03-16 | 瑞昱半导体股份有限公司 | 处理中断优先级的电路系统 |

| CN110457243B (zh) * | 2019-07-30 | 2021-04-06 | 西安理工大学 | 一种可扩展多输出中断控制器 |

| JP7380416B2 (ja) | 2020-05-18 | 2023-11-15 | トヨタ自動車株式会社 | エージェント制御装置 |

| JP7380415B2 (ja) * | 2020-05-18 | 2023-11-15 | トヨタ自動車株式会社 | エージェント制御装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0346051A (ja) * | 1989-07-14 | 1991-02-27 | Oki Electric Ind Co Ltd | マルチプロセッサシステムの割込み制御方式 |

| JPH03144847A (ja) * | 1989-10-26 | 1991-06-20 | Internatl Business Mach Corp <Ibm> | マルチプロセッサ・システムおよびそのプロセス同期方法 |

| JPH11237992A (ja) * | 1998-02-20 | 1999-08-31 | Fujitsu Ltd | 割込みレベル制御装置 |

| JP2006216042A (ja) * | 2005-02-04 | 2006-08-17 | Sony Computer Entertainment Inc | 割り込み処理のためのシステムおよび方法 |

| JP2008065713A (ja) * | 2006-09-08 | 2008-03-21 | Canon Inc | マルチプロセッサシステム及び割込み制御方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4001783A (en) * | 1975-03-26 | 1977-01-04 | Honeywell Information Systems, Inc. | Priority interrupt mechanism |

| US5613128A (en) * | 1990-12-21 | 1997-03-18 | Intel Corporation | Programmable multi-processor interrupt controller system with a processor integrated local interrupt controller |

| US5659759A (en) * | 1992-09-21 | 1997-08-19 | Kabushiki Kaisha Toshiba | Data processing device having improved interrupt controller to process interrupts of different priority levels |

| EP0602858A1 (en) * | 1992-12-18 | 1994-06-22 | International Business Machines Corporation | Apparatus and method for servicing interrupts in a multiprocessor system |

| US5721931A (en) * | 1995-03-21 | 1998-02-24 | Advanced Micro Devices | Multiprocessing system employing an adaptive interrupt mapping mechanism and method |

| US6003129A (en) * | 1996-08-19 | 1999-12-14 | Samsung Electronics Company, Ltd. | System and method for handling interrupt and exception events in an asymmetric multiprocessor architecture |

| US6418496B2 (en) * | 1997-12-10 | 2002-07-09 | Intel Corporation | System and apparatus including lowest priority logic to select a processor to receive an interrupt message |

| DE19955776C1 (de) * | 1999-11-19 | 2001-07-19 | Infineon Technologies Ag | Multitasking-Prozessorsystem |

| US20050125582A1 (en) * | 2003-12-08 | 2005-06-09 | Tu Steven J. | Methods and apparatus to dispatch interrupts in multi-processor systems |

| JP2006243865A (ja) * | 2005-03-01 | 2006-09-14 | Seiko Epson Corp | プロセッサおよび情報処理方法 |

| JP4457047B2 (ja) * | 2005-06-22 | 2010-04-28 | 株式会社ルネサステクノロジ | マルチプロセッサシステム |

| JP3976065B2 (ja) * | 2006-01-16 | 2007-09-12 | セイコーエプソン株式会社 | マルチプロセッサシステム及びマルチプロセッサシステムの割込み制御方法をコンピュータに実行させるためのプログラム |

| JP2007328461A (ja) * | 2006-06-06 | 2007-12-20 | Matsushita Electric Ind Co Ltd | 非対称マルチプロセッサ |

| JP5243711B2 (ja) * | 2006-11-10 | 2013-07-24 | セイコーエプソン株式会社 | プロセッサ |

| JP2009175960A (ja) * | 2008-01-23 | 2009-08-06 | Panasonic Corp | 仮想マルチプロセッサシステム |

| JP4996519B2 (ja) * | 2008-03-27 | 2012-08-08 | パナソニック株式会社 | 仮想マルチプロセッサ、システムlsi、携帯電話機器、及び仮想マルチプロセッサの制御方法 |

-

2008

- 2008-04-03 JP JP2008097226A patent/JP2009251802A/ja active Pending

-

2009

- 2009-03-24 CN CN2009801115781A patent/CN102099797A/zh active Pending

- 2009-03-24 WO PCT/JP2009/001285 patent/WO2009122670A1/ja active Application Filing

-

2010

- 2010-09-28 US US12/892,136 patent/US20110016247A1/en not_active Abandoned

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0346051A (ja) * | 1989-07-14 | 1991-02-27 | Oki Electric Ind Co Ltd | マルチプロセッサシステムの割込み制御方式 |

| JPH03144847A (ja) * | 1989-10-26 | 1991-06-20 | Internatl Business Mach Corp <Ibm> | マルチプロセッサ・システムおよびそのプロセス同期方法 |

| JPH11237992A (ja) * | 1998-02-20 | 1999-08-31 | Fujitsu Ltd | 割込みレベル制御装置 |

| JP2006216042A (ja) * | 2005-02-04 | 2006-08-17 | Sony Computer Entertainment Inc | 割り込み処理のためのシステムおよび方法 |

| JP2008065713A (ja) * | 2006-09-08 | 2008-03-21 | Canon Inc | マルチプロセッサシステム及び割込み制御方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102918516A (zh) * | 2010-06-23 | 2013-02-06 | 国际商业机器公司 | 适配器中断源的类型的标识 |

| JP2013536485A (ja) * | 2010-06-23 | 2013-09-19 | インターナショナル・ビジネス・マシーンズ・コーポレーション | アダプタ割り込みのソース・タイプの識別 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110016247A1 (en) | 2011-01-20 |

| WO2009122670A1 (ja) | 2009-10-08 |

| CN102099797A (zh) | 2011-06-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2009122670A1 (ja) | マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法 | |

| CA3047884C (en) | Method and device for sending transaction information and for consensus verification | |

| EP3000036B1 (en) | A method and apparatus for interrupt handling | |

| CN106775977B (zh) | 任务调度方法、装置及系统 | |

| JP2009294712A (ja) | 優先度制御装置及び優先度制御方法 | |

| KR20180069815A (ko) | 충돌들의 존재시 효율적인 작업 스케줄링을 위한 방법 | |

| US9740266B2 (en) | Apparatus and method for controlling multi-core of electronic device | |

| JP2008123157A (ja) | プロセッサ及び割込み制御方法 | |

| JP2010140290A (ja) | マルチプロセッサシステム及びその排他制御の調停方法 | |

| JP2011164971A (ja) | Biosとbmcとの間の通信パス強化方法、その装置及びそのプログラム | |

| JPWO2009060530A1 (ja) | ネットワーク処理制御装置,プログラムおよび方法 | |

| JP2008090507A (ja) | ジョブ実行のスケジューリングプログラム、ジョブ実行のスケジューリング方法、ジョブ実行のスケジューリング装置 | |

| US10649934B2 (en) | Image processing apparatus, notification monitoring program, and notification monitoring method | |

| JP4817834B2 (ja) | 割り込み制御装置及び割り込み制御方法 | |

| JP5579935B2 (ja) | 割り込み処理に起因する異常動作の検知 | |

| CN112214291A (zh) | 一种任务调度方法及装置 | |

| CN113032119A (zh) | 一种任务调度方法、装置、存储介质及电子设备 | |

| US9678752B2 (en) | Scheduling apparatus and method of dynamically setting the size of a rotating register | |

| WO2018211865A1 (ja) | 車両制御装置 | |

| US10269194B2 (en) | Multiprocessor system and vehicle control system | |

| KR101513505B1 (ko) | 프로세서 및 인터럽트 처리 방법 | |

| CN108139932B (zh) | 关闭关键执行路径的任务信令 | |

| JP2018147448A (ja) | 情報処理装置、管理制御装置のプログラム更新制御方法及びプログラム更新制御プログラム | |

| US20190075509A1 (en) | Method and apparatus for scheduling in wireless network | |

| CN111152215B (zh) | 一种应用的控制方法及机器人 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120306 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120626 |