JP2008306037A - 半導体モジュール及びその製造方法 - Google Patents

半導体モジュール及びその製造方法 Download PDFInfo

- Publication number

- JP2008306037A JP2008306037A JP2007152604A JP2007152604A JP2008306037A JP 2008306037 A JP2008306037 A JP 2008306037A JP 2007152604 A JP2007152604 A JP 2007152604A JP 2007152604 A JP2007152604 A JP 2007152604A JP 2008306037 A JP2008306037 A JP 2008306037A

- Authority

- JP

- Japan

- Prior art keywords

- interposer

- semiconductor chip

- terminal

- region

- passive component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

Landscapes

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

Abstract

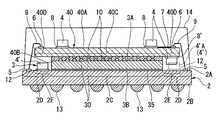

【解決手段】本発明の半導体モジュール1は、第1のインターポーザ2と、能動面3Aと裏面3Bとを有し、裏面3Bが第1のインターポーザ2と対向して配置された半導体チップ3と、半導体チップ3の能動面3Aに対向して半導体チップ3と電気的に接続し、且つ第1のインターポーザと電気的に接続する第2のインターポーザ40と、第2のインターポーザ40の少なくとも上面40Aに実装された受動部品4とを備えている。

【選択図】図1

Description

能動面と裏面とを有し、裏面が第1のインターポーザと対向して配置された半導体チップと、半導体チップの能動面に対向して該半導体チップと電気的に接続し、且つ第1のインターポーザと電気的に接続する第2のインターポーザと、第2のインターポーザの、少なくとも半導体チップと反対側の第1の面に実装された第1の受動部品と、を備えたことを特徴とする。

このような構成によれば、第2のインターポーザの半導体チップと対向する第2の面のうち、半導体チップが接続された第1の領域以外の第2の領域を有効に利用することができる。すなわち、このように第2のインターポーザの、半導体チップから庇状に張り出した領域にも第1の受動部品を備えることで、第2のインターポーザの両面を有効に利用することができる。

このような構成によれば、第1のインターポーザの第1の面のうち、半導体チップが接続される領域以外の領域を有効に利用することができる。

このような構成によれば、第2のインターポーザに各端子間の接続配線を設けることにより、モジュール全体の高集積化が可能になる。

このような構成によれば、半導体チップと第2のインターポーザとの電気的接続を良好にできるとともに、第2のインターポーザと受動部品との電気的接続を良好にすることができる。

このような構成によれば、半導体チップを第1のインターポーザ上にフリップチップ実装することができ、これにより、半導体チップの能動面と第1のインターポーザとを良好に接続することができる。

このような構成によれば、第1のインターポーザと第2のインターポーザとを、ワイヤーを介して電気的に良好に接続することができる。

このような方法によれば、半導体チップの能動面と第2のインターポーザとを良好に接続することができる。

本発明の半導体モジュールの製造方法によれば、半導体チップをその裏面を対向させるようにして第1のインターポーザに実装するとともに、半導体チップの能動面と対向させるようにして第2のインターポーザを配置し、少なくともその上面(半導体チップと反対側の第1の面)に受動部品を接続するようにしたので、半導体モジュールの小型化、特に第1、第2のインターポーザの表面と平行な面内における半導体モジュールの小型化を実現することができる。また、本発明によれば工程の複雑化等を抑制できる。なお、半導体チップを第1のインターポーザ及び第2のインターポーザのどちらに先に実装するかは適宜選択するものとする。

本発明の半導体モジュールの一実施形態について説明する。図1は、本実施形態に係る半導体モジュール1を模式的に示す斜視図、図2は、断面図であって、図1のA−A線断面矢視図に相当する。また、図3は、本実施形態に係る半導体モジュール1の一部を拡大した平面図である。なお、以下の説明に用いる各図面では、各部材を認識可能な大きさとするため、各部材の縮尺を適宜変更している。

なお、電極パッド8’においても、下面40B側に接続される受動部品4に対応するように形成されている。

次に、半導体モジュール1を製造する手順の一例について説明する。なお、本実施形態においては、既存の半導体チップ3を用いて半導体モジュール1を構成してもよいし、以下に説明するように半導体チップ3を始めから形成することとしてもよい。

半導体モジュール1の半導体チップ3を形成する際には、図5に示すように、同一のシリコン基板(ウエハ)100上に半導体チップ3を複数一括して形成し、その後ダイシング(切断)して個片化することによって、半導体チップ3が得られることになるが、以下の図4を用いた説明においては、簡略化のため、1つの半導体チップ3を形成する場合について説明する。

Claims (9)

- 第1のインターポーザと、

能動面と裏面とを有し、前記裏面が前記第1のインターポーザと対向して配置された半導体チップと、

前記半導体チップの前記能動面に対向して該半導体チップと電気的に接続し、且つ前記第1のインターポーザと電気的に接続する第2のインターポーザと、

前記第2のインターポーザの、少なくとも前記半導体チップと反対側の第1の面に実装された第1の受動部品と、を備えたことを特徴とする半導体モジュール。 - 前記第2のインターポーザは、前記半導体チップの前記能動面と平行な平面内における大きさが前記半導体チップよりも大きく、

前記第2のインターポーザの前記半導体チップと対向する第2の面のうち、前記半導体チップが存在する第1の領域以外の第2の領域にも、前記第1の受動部品が実装されていることを特徴とする請求項1に記載の半導体モジュール。 - 前記第2のインターポーザは、前記半導体チップの前記能動面と平行な平面内における大きさが前記半導体チップよりも大きく、

前記第1のインターポーザの前記半導体チップに対向する前記第1の面のうち、前記第2のインターポーザの前記第2の領域に対向する領域に第2の受動部品が実装されていることを特徴とする請求項1または2記載の半導体モジュール。 - 前記第2のインターポーザは、

前記第1の受動部品と電気的に接続するための第1の端子と、

前記半導体チップと電気的に接続するための第2の端子と、

前記第1のインターポーザと電気的に接続するための第3の端子と、を備えた多層配線基板からなることを特徴とする請求項1乃至3のいずれか一項に記載の半導体モジュール。 - 前記第2のインターポーザの前記第1の端子、前記第2の端子、及び前記第3の端子が、金めっきされていることを特徴とする請求項4記載の半導体モジュール。

- 前記半導体チップは、前記第2のインターポーザの前記第2の端子と接続する端子を備え、

当該端子が金バンプまたはハンダパンプからなることを特徴とする請求項4または5記載の半導体モジュール。 - 前記第1のインターポーザは、前記第2のインターポーザの前記第3の端子と電気的に接続する端子を備え、

当該端子と前記第3の端子とがワイヤーボンディングによって接続されていることを特徴とする請求項4または5記載の半導体モジュール。 - 前記半導体チップは、前記第2のインターポーザにフリップチップ実装されていることを特徴とする請求項1乃至7のいずれか一項に記載の半導体モジュール。

- 能動面と裏面とを有する半導体チップを用意し、

第1のインターポーザに、前記半導体チップを、前記裏面が前記第1のインターポーザと対向するようにして実装する工程と、

前記半導体チップの前記能動面側に、前記第2のインターポーザを電気的に接続するようにして実装する工程と、

前記第2のインターポーザの少なくとも前記半導体チップと反対側の第1の面に、受動部品を接続する工程と、

前記第1のインターポーザと前記第2のインターポーザとを電気的に接続する工程と、を含むことを特徴とする半導体モジュールの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007152604A JP2008306037A (ja) | 2007-06-08 | 2007-06-08 | 半導体モジュール及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007152604A JP2008306037A (ja) | 2007-06-08 | 2007-06-08 | 半導体モジュール及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008306037A true JP2008306037A (ja) | 2008-12-18 |

| JP2008306037A5 JP2008306037A5 (ja) | 2010-07-22 |

Family

ID=40234466

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007152604A Withdrawn JP2008306037A (ja) | 2007-06-08 | 2007-06-08 | 半導体モジュール及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2008306037A (ja) |

-

2007

- 2007-06-08 JP JP2007152604A patent/JP2008306037A/ja not_active Withdrawn

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10510659B2 (en) | Substrate-less stackable package with wire-bond interconnect | |

| US8786102B2 (en) | Semiconductor device and method of manufacturing the same | |

| TWI408795B (zh) | Semiconductor device and manufacturing method thereof | |

| US7189593B2 (en) | Elimination of RDL using tape base flip chip on flex for die stacking | |

| KR100868419B1 (ko) | 반도체장치 및 그 제조방법 | |

| JP2007123595A (ja) | 半導体装置及びその実装構造 | |

| JP2008166439A (ja) | 半導体装置およびその製造方法 | |

| KR20010104217A (ko) | 반도체 장치 및 그 제조 방법, 회로 기판 및 전자 기기 | |

| KR20060101385A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP4494249B2 (ja) | 半導体装置 | |

| JP4417974B2 (ja) | 積層型半導体装置の製造方法 | |

| US20100269333A1 (en) | Method for Mounting Flip Chip and Substrate Used Therein | |

| JP2008311347A (ja) | 半導体モジュール及びその製造方法 | |

| JP2007150346A (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 | |

| JP2008306037A (ja) | 半導体モジュール及びその製造方法 | |

| JP2003133509A (ja) | 半導体パッケージ及びその製造方法 | |

| KR101055491B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| JP2008021842A (ja) | 半導体モジュール及び半導体モジュールの製造方法 | |

| JP4465884B2 (ja) | 半導体装置およびその製造方法 | |

| JP2008021710A (ja) | 半導体モジュールならびにその製造方法 | |

| JP2008021712A (ja) | 半導体モジュールならびにその製造方法 | |

| JP5297445B2 (ja) | 半導体装置 | |

| JP5845855B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2008103395A (ja) | 半導体モジュール及びその製造方法 | |

| US20090189272A1 (en) | Wafer Level Chip Scale Packages Including Redistribution Substrates and Methods of Fabricating the Same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100603 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100603 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100604 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20110314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20110315 |