JP2008277751A - Method of manufacturing semiconductor device, and semiconductor device - Google Patents

Method of manufacturing semiconductor device, and semiconductor device Download PDFInfo

- Publication number

- JP2008277751A JP2008277751A JP2008029858A JP2008029858A JP2008277751A JP 2008277751 A JP2008277751 A JP 2008277751A JP 2008029858 A JP2008029858 A JP 2008029858A JP 2008029858 A JP2008029858 A JP 2008029858A JP 2008277751 A JP2008277751 A JP 2008277751A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- bonding

- wire

- ball

- wires

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/4501—Shape

- H01L2224/45012—Cross-sectional shape

- H01L2224/45015—Cross-sectional shape being circular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45147—Copper (Cu) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48095—Kinked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48145—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4845—Details of ball bonds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4846—Connecting portions with multiple bonds on the same bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48471—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area being a ball bond, i.e. wedge-to-ball, reverse stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

- H01L2224/48476—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area

- H01L2224/48477—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding)

- H01L2224/48478—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball

- H01L2224/48479—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/485—Material

- H01L2224/48505—Material at the bonding interface

- H01L2224/48599—Principal constituent of the connecting portion of the wire connector being Gold (Au)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/485—Material

- H01L2224/48505—Material at the bonding interface

- H01L2224/48699—Principal constituent of the connecting portion of the wire connector being Aluminium (Al)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49111—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting two common bonding areas, e.g. Litz or braid wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49113—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting different bonding areas on the semiconductor or solid-state body to a common bonding area outside the body, e.g. converging wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49174—Stacked arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4941—Connecting portions the connecting portions being stacked

- H01L2224/4942—Ball bonds

- H01L2224/49422—Ball bonds outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4941—Connecting portions the connecting portions being stacked

- H01L2224/49425—Wedge bonds

- H01L2224/49427—Wedge bonds outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4945—Wire connectors having connecting portions of different types on the semiconductor or solid-state body, e.g. regular and reverse stitches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

- H01L2224/7825—Means for applying energy, e.g. heating means

- H01L2224/783—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/78301—Capillary

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

- H01L2224/8503—Reshaping, e.g. forming the ball or the wedge of the wire connector

- H01L2224/85035—Reshaping, e.g. forming the ball or the wedge of the wire connector by heating means, e.g. "free-air-ball"

- H01L2224/85045—Reshaping, e.g. forming the ball or the wedge of the wire connector by heating means, e.g. "free-air-ball" using a corona discharge, e.g. electronic flame off [EFO]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

- H01L2224/85051—Forming additional members, e.g. for "wedge-on-ball", "ball-on-wedge", "ball-on-ball" connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85148—Aligning involving movement of a part of the bonding apparatus

- H01L2224/85169—Aligning involving movement of a part of the bonding apparatus being the upper part of the bonding apparatus, i.e. bonding head, e.g. capillary or wedge

- H01L2224/8518—Translational movements

- H01L2224/85181—Translational movements connecting first on the semiconductor or solid-state body, i.e. on-chip, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85148—Aligning involving movement of a part of the bonding apparatus

- H01L2224/85169—Aligning involving movement of a part of the bonding apparatus being the upper part of the bonding apparatus, i.e. bonding head, e.g. capillary or wedge

- H01L2224/8518—Translational movements

- H01L2224/85191—Translational movements connecting first both on and outside the semiconductor or solid-state body, i.e. regular and reverse stitches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/852—Applying energy for connecting

- H01L2224/85201—Compression bonding

- H01L2224/85203—Thermocompression bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/852—Applying energy for connecting

- H01L2224/85201—Compression bonding

- H01L2224/85205—Ultrasonic bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/8593—Reshaping, e.g. for severing the wire, modifying the wedge or ball or the loop shape

- H01L2224/85947—Reshaping, e.g. for severing the wire, modifying the wedge or ball or the loop shape by mechanical means, e.g. "pull-and-cut", pressing, stamping

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/85951—Forming additional members, e.g. for reinforcing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85986—Specific sequence of steps, e.g. repetition of manufacturing steps, time sequence

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20751—Diameter ranges larger or equal to 10 microns less than 20 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20752—Diameter ranges larger or equal to 20 microns less than 30 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20753—Diameter ranges larger or equal to 30 microns less than 40 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20754—Diameter ranges larger or equal to 40 microns less than 50 microns

Abstract

Description

本発明は、半導体装置の製造方法、および半導体装置に関し、特にリードフレーム/配線基板を用いた半導体チップのパッケージ技術に関する。 The present invention relates to a semiconductor device manufacturing method and a semiconductor device, and more particularly to a semiconductor chip packaging technique using a lead frame / wiring substrate.

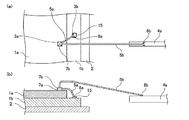

近年、半導体装置の形態として、リードフレームを用いたQFP(クワッド・フラット・パッケージ)などが広く用いられてきている。以下、図面を用いて、従来の一般的なQFP型半導体装置について説明する。 In recent years, QFP (quad flat package) using a lead frame has been widely used as a form of a semiconductor device. Hereinafter, a conventional general QFP type semiconductor device will be described with reference to the drawings.

図17は従来の一般的なQFP型半導体装置の断面図、図18は同半導体装置のワイヤボンディング部分の内部構造図である。このQFP型半導体装置は、図17、図18に示すように、集積回路が形成された半導体チップ1がリードフレームのダイパッド部2に搭載されている。また、ダイパッド部2の周辺には放射状にリードフレームのリード4が配置されており、インナーリード4aの先端がダイパッド部2に対して対向している。また、半導体チップ1の表面に形成された電極3とインナーリード4aとがワイヤ5で接続されている。また、半導体チップ1、ワイヤ5、インナーリード4aが一括して樹脂封止体6により樹脂封止され、インナーリード4aに連続したリードフレームのアウターリード4bが樹脂封止体6の外部でガルウィング型に曲げ成形されている。また、図18に示すダイパッドサポート24は、ダイパッド部2をリードフレームに保持する部材である(例えば、非特許文献1参照。)。

FIG. 17 is a cross-sectional view of a conventional general QFP semiconductor device, and FIG. 18 is an internal structure diagram of a wire bonding portion of the semiconductor device. In this QFP type semiconductor device, as shown in FIGS. 17 and 18, a

続いて、従来の一般的なQFP型半導体装置の製造方法について説明する。

まず、金属板で形成されたリードフレームのダイパッド部2に半導体チップ1を搭載する(ダイボンド工程)。なお、リードフレームは、複数個の半導体装置を同時に、あるいは順次形成するために、各半導体装置に対応する矩形のパターンをフレーム枠で連結して複数個、同一平面上の左右方向ないし上下方向に配列したものである。各パターンは、ダイパッド部2を中央に配置し、複数本のリード4の外端部をフレーム枠に接続し、ダイパッド部2をダイパッドサポート24によりフレーム枠に保持する構造である。

Next, a conventional general QFP type semiconductor device manufacturing method will be described.

First, the

次に、半導体チップ1の表面に形成された電極3と、ダイパッド部2の周囲に配置されたインナーリード4aとをワイヤ5で接続する(ワイヤボンディング工程)。次に、半導体チップ1、ダイパッド部2、ワイヤ5、インナーリード4aを一括して封止樹脂で樹脂封止して、樹脂封止体6を形成する(樹脂封止工程)。

Next, the

最後に、アウターリード4bを所定の長さに合わせてフレーム枠から切断して個片に分離するとともに、アウターリード4bを所定の形状に加工して、半導体装置の完成品を得る。

Finally, the

また、ワイヤボンディング方法としては、(1)キャピラリの先端から突出したワイヤの先端に放電によりボールを形成し、(2)熱と超音波を与えながら、そのボールをキャピラリで一方の接続点に押し付けて接続し(ボールボンディング)、(3)キャピラリからワイヤを引き出しながら他方の接続点に移動し、(4)熱と超音波を与えながらキャピラリの先端部でワイヤを他方の接続点にこすり付けて接続する(ウェッジボンディング)、超音波併用熱圧着ボンディング方式が現在の主流であり、一般的には半導体チップの電極側においてボールボンディングを行う。 The wire bonding method is as follows: (1) a ball is formed by discharge at the tip of the wire protruding from the tip of the capillary, and (2) the ball is pressed against one connection point with the capillary while applying heat and ultrasonic waves. (3) Move to the other connection point while pulling out the wire from the capillary, and (4) Rub the wire to the other connection point at the tip of the capillary while applying heat and ultrasonic waves. The connection method (wedge bonding) and the thermocompression bonding method using ultrasonic waves are the mainstream at present, and ball bonding is generally performed on the electrode side of the semiconductor chip.

以上のように構成されたQFP型半導体装置において、近年、集積回路の高集積化、高密度化に伴い、多ピン化およびリードの狭ピッチ化が進んできた。しかしながら、多ピン化およびリードの狭ピッチ化が進んできたといってもQFP型半導体装置の外形やピン数は業界で標準化されている。そこで、QFP型半導体装置では、限られたピン数の中で高集積化された半導体チップを保持すべく、電源電極や接地電極などの共通化できる電極をまとめて同一のリードに接続している。図19は同一のインナーリード4aに複数の電極3からのワイヤ5を接続した状態を示す模式図である。図19(a)では同一のインナーリード4aに2本のワイヤ5を接続し、図19(b)では同一のインナーリード4aに3本のワイヤ5を接続している。

以上のように、従来から、QFP型半導体装置においては、電源電極や接地電極などの共通化できる電極をまとめて同一のリードに接続していた。一方、半導体チップ1個当たりの回路規模が飛躍的に大きくなったため、電源電極および接地電極への安定した電流供給を確保するための配線が必要となってきた。反面、半導体組立技術の進歩と低コスト化の要求から、半導体装置の配線材料であるAuワイヤに代表される金属ワイヤは細線化が図られてきた。これらの相反する2つの課題に対し、1個の電極と1本のインナーリードとの接続に複数本のワイヤを使用することが行われている。 As described above, conventionally, in the QFP type semiconductor device, common electrodes such as a power supply electrode and a ground electrode are collectively connected to the same lead. On the other hand, since the circuit scale per semiconductor chip has dramatically increased, wiring for securing a stable current supply to the power supply electrode and the ground electrode has become necessary. On the other hand, metal wires typified by Au wires, which are wiring materials for semiconductor devices, have been made thinner because of advances in semiconductor assembly technology and demands for cost reduction. For these two conflicting problems, the use of a plurality of wires for connecting one electrode and one inner lead has been performed.

しかしながら、通常、ワイヤの十分な接合を行うには一定以上の面積が必要になるため、複数本のワイヤを同一の電極に接続する場合、従来は、電極の面積を、複数本のワイヤをボールボンディングできる大きさにする必要があった。このことがチップ面積の縮小化を阻害していた。 However, since an area of a certain size or more is usually required for sufficient bonding of wires, when connecting a plurality of wires to the same electrode, conventionally, the area of the electrode is reduced to a number of wires. It was necessary to make it large enough for bonding. This hindered the reduction of the chip area.

また、リードフレームのリードや、BGA(ボール・グリッド・アレイ)型半導体装置の配線基板の表層配線に、複数本のワイヤをボールボンディングにより接続する場合もあるが、この場合も同様に、リードまたは表層配線の面積を、複数本のワイヤをボールボンディングできる大きさにする必要があった。このことがパッケージ面積の縮小化を阻害していた。 In some cases, a plurality of wires are connected to the lead of the lead frame or the surface layer wiring of the wiring board of the BGA (Ball Grid Array) type semiconductor device by ball bonding. It was necessary to make the surface layer wiring area large enough to allow ball bonding of a plurality of wires. This hindered the reduction of the package area.

本発明は、上記問題点に鑑み、半導体チップ上の同一の電極又はリードフレームの同一のリードあるいは配線基板上の同一の表層配線に、複数本のワイヤを接続する構造において、電極面積またはパッケージ面積を抑制することができる半導体装置の製造方法、および半導体装置を提供することを目的とする。 In view of the above problems, the present invention provides a structure in which a plurality of wires are connected to the same electrode on a semiconductor chip, the same lead of a lead frame, or the same surface layer wiring on a wiring board. An object of the present invention is to provide a method for manufacturing a semiconductor device and a semiconductor device capable of suppressing the above-described problem.

本発明の請求項1記載の半導体装置の製造方法は、ワイヤ供給装置から突出したワイヤの先端にボールを形成して、そのボールを半導体チップ上の電極に圧着するボールボンディングを行い、その後ワイヤ供給装置を移動させ、接続対象部材にウェッジボンディングを行う第1ボンディング工程と、ワイヤ供給装置から突出したワイヤの先端にボールを形成して、そのボールを、前記第1ボンディング工程においてボールボンディングを行った部分に直上から圧着するボールボンディングを行い、その後ワイヤ供給装置を移動させ、前記第1ボンディング工程における接続対象部材又はその接続対象部材とは異なる接続対象部材にウェッジボンディングを行う第2ボンディング工程と、を具備することを特徴とする。 According to a first aspect of the present invention, there is provided a method of manufacturing a semiconductor device in which a ball is formed at a tip of a wire protruding from a wire supply device, and the ball is bonded to an electrode on a semiconductor chip. A first bonding step of moving the device and performing wedge bonding on the connection target member, and forming a ball at the tip of the wire protruding from the wire supply device, and performing the ball bonding of the ball in the first bonding step A second bonding step in which ball bonding is performed to directly press onto the portion, and then the wire supply device is moved, and the bonding target member in the first bonding step or wedge bonding is performed on a connection target member different from the connection target member; It is characterized by comprising.

また、本発明の請求項2記載の半導体装置の製造方法は、請求項1記載の半導体装置の製造方法であって、前記第2ボンディング工程を2回以上繰り返し行い、前記電極に複数本のワイヤを接続させることを特徴とする。

A method for manufacturing a semiconductor device according to

また、本発明の請求項3記載の半導体装置の製造方法は、請求項2記載の半導体装置の製造方法であって、繰り返し行う前記第2ボンディング工程に際し、前記第1ボンディング工程における接続対象部材に少なくとも1本のワイヤをウェッジボンディングにより接続させることを特徴とする。 According to a third aspect of the present invention, there is provided a method for manufacturing a semiconductor device according to the second aspect of the present invention, wherein the connection target member in the first bonding step is used when the second bonding step is repeatedly performed. At least one wire is connected by wedge bonding.

また、本発明の請求項4記載の半導体装置の製造方法は、請求項2記載の半導体装置の製造方法であって、繰り返し行う前記第2ボンディング工程に際し、前記第1ボンディング工程における接続対象部材とは異なる同一の接続対象部材に少なくとも2本のワイヤをウェッジボンディングにより接続させることを特徴とする。 According to a fourth aspect of the present invention, there is provided a method of manufacturing a semiconductor device according to the second aspect of the present invention, wherein, in the second bonding step that is repeatedly performed, the connection target member in the first bonding step and Is characterized in that at least two wires are connected to different same connection target members by wedge bonding.

また、本発明の請求項5記載の半導体装置の製造方法は、請求項1記載の半導体装置の製造方法であって、ワイヤ供給装置から突出したワイヤの先端にボールを形成し、そのボールを、前記第1ボンディング工程ないし前記第2ボンディング工程においてウェッジボンディングを行う部分に圧着してバンプを形成するバンプ形成工程を具備し、前記第1ボンディング工程ないし前記第2ボンディング工程に際し、前記バンプにウェッジボンディングを行うことを特徴とする。

A method for manufacturing a semiconductor device according to

また、本発明の請求項6記載の半導体装置の製造方法は、ワイヤ供給装置から突出したワイヤの先端にボールを形成して、そのボールを半導体チップの周囲に配置されたリードあるいは配線部材に圧着するボールボンディングを行い、その後ワイヤ供給装置を移動させ、接続対象部材にウェッジボンディングを行う第1ボンディング工程と、ワイヤ供給装置から突出したワイヤの先端にボールを形成して、そのボールを、前記第1ボンディング工程においてボールボンディングを行った部分に直上から圧着するボールボンディングを行い、その後ワイヤ供給装置を移動させ、前記第1ボンディング工程における接続対象部材又はその接続対象部材とは異なる接続対象部材にウェッジボンディングを行う第2ボンディング工程と、を具備することを特徴とする。 According to a sixth aspect of the present invention, there is provided a method of manufacturing a semiconductor device, wherein a ball is formed at a tip of a wire protruding from a wire supply device, and the ball is crimped to a lead or a wiring member disposed around the semiconductor chip. Performing a ball bonding, and then moving the wire supply device to perform wedge bonding on the connection target member; forming a ball at the tip of the wire protruding from the wire supply device; Ball bonding is performed by directly pressing onto the portion where ball bonding has been performed in one bonding process, and then the wire supply device is moved so that the connection target member in the first bonding process or a connection target member different from the connection target member is wedged. A second bonding step for performing bonding. The features.

また、本発明の請求項7記載の半導体装置の製造方法は、請求項6記載の半導体装置の製造方法であって、前記第2ボンディング工程を2回以上繰り返し行い、前記リードあるいは前記配線部材に複数本のワイヤを接続させることを特徴とする。 According to a seventh aspect of the present invention, there is provided a method for manufacturing a semiconductor device according to the sixth aspect, wherein the second bonding step is repeated twice or more to form the lead or the wiring member. A plurality of wires are connected.

また、本発明の請求項8記載の半導体装置の製造方法は、請求項7記載の半導体装置の製造方法であって、繰り返し行う前記第2ボンディング工程に際し、前記第1ボンディング工程における接続対象部材に少なくとも1本のワイヤをウェッジボンディングにより接続させることを特徴とする。

Further, the method for manufacturing a semiconductor device according to claim 8 of the present invention is the method for manufacturing a semiconductor device according to

また、本発明の請求項9記載の半導体装置の製造方法は、請求項7記載の半導体装置の製造方法であって、繰り返し行う前記第2ボンディング工程に際し、前記第1ボンディング工程における接続対象部材とは異なる同一の接続対象部材に少なくとも2本のワイヤをウェッジボンディングにより接続させることを特徴とする。

A method for manufacturing a semiconductor device according to

また、本発明の請求項10記載の半導体装置の製造方法は、請求項6記載の半導体装置の製造方法であって、ワイヤ供給装置から突出したワイヤの先端にボールを形成し、そのボールを、前記第1ボンディング工程ないし前記第2ボンディング工程においてウェッジボンディングを行う部分に圧着してバンプを形成するバンプ形成工程を具備し、前記第1ボンディング工程ないし前記第2ボンディング工程に際し、前記バンプにウェッジボンディングを行うことを特徴とする。

A method for manufacturing a semiconductor device according to

また、本発明の請求項11記載の半導体装置は、電極を有する半導体チップと、前記半導体チップが搭載されるチップ搭載部と、前記チップ搭載部の周囲に配置されるリード又は配線部材と、前記半導体チップが有する前記電極と前記リード又は配線部材とを接続するワイヤと、を備え、少なくとも前記半導体チップ、前記チップ搭載部、前記ワイヤおよび前記リード又は配線部材の前記ワイヤとの接続部分が樹脂封止された半導体装置であって、前記半導体チップが有する前記電極のうちの少なくとも1個に、複数本の前記ワイヤの一端の接続部が重ねて接続されており、それらの接続部はボールボンディング法特有の、厚みのあるコイン状に押しつぶされた突起部のほぼ中央からワイヤが導出される形状に形成されていることを特徴とする。 A semiconductor device according to claim 11 of the present invention is a semiconductor chip having electrodes, a chip mounting portion on which the semiconductor chip is mounted, a lead or wiring member disposed around the chip mounting portion, A wire for connecting the electrode of the semiconductor chip and the lead or the wiring member, and at least a connection portion of the semiconductor chip, the chip mounting portion, the wire and the wire of the lead or the wiring member is sealed with resin. A semiconductor device that is stopped, wherein at least one of the electrodes of the semiconductor chip is connected to a connecting portion of one end of the plurality of wires in an overlapping manner, and the connecting portion is connected by a ball bonding method. It is characterized in that the wire is led out from the approximate center of the peculiar, thick coin-shaped protrusion. .

また、本発明の請求項12記載の半導体装置は、請求項11記載の半導体装置であって、前記半導体チップが有する前記電極に一端が重ねて接続された複数本の前記ワイヤのうちの少なくとも一部は、その他端が、同一の前記リード又は配線部材に、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続されていることを特徴とする。 A semiconductor device according to a twelfth aspect of the present invention is the semiconductor device according to the eleventh aspect, wherein at least one of the plurality of wires connected at one end to the electrode of the semiconductor chip. The other end of the part is connected to the same lead or wiring member in the shape of a crescent or ellipse having no thickness peculiar to the wedge bonding method.

また、本発明の請求項13記載の半導体装置は、請求項11記載の半導体装置であって、前記半導体チップを複数個備え、少なくとも1箇の前記半導体チップが有する少なくとも1箇の前記電極に一端が重ねて接続された複数本の前記ワイヤのうちの少なくとも一部は、その他端が、他方の前記半導体チップが有する電極に、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続されていることを特徴とする。 A semiconductor device according to a thirteenth aspect of the present invention is the semiconductor device according to the eleventh aspect, comprising a plurality of the semiconductor chips, and one end of at least one of the electrodes of the at least one semiconductor chip. At least a part of the plurality of wires connected in a stacked manner has a crescent shape or an ellipse shape with no other thickness on the electrode of the other semiconductor chip at the other end. And are connected.

また、本発明の請求項14記載の半導体装置は、請求項11記載の半導体装置であって、前記半導体チップを複数個備え、少なくとも1箇の前記半導体チップが有する少なくとも1箇の前記電極に一端が重ねて接続された複数本の前記ワイヤの一部は、その他端が、他方の前記半導体チップが有する電極に、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続され、他の一部は、その他端が、前記リード又は配線部材に、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続されていることを特徴とする。 A semiconductor device according to a fourteenth aspect of the present invention is the semiconductor device according to the eleventh aspect, comprising a plurality of the semiconductor chips, and one end of at least one electrode of the at least one semiconductor chip. A part of the plurality of wires connected to each other is connected at the other end to the electrode of the other semiconductor chip in a crescent or elliptical shape having no thickness peculiar to the wedge bonding method. The other part is characterized in that the other end is connected to the lead or the wiring member in the shape of a crescent or ellipse having no thickness peculiar to the wedge bonding method.

また、本発明の請求項15記載の半導体装置は、請求項11記載の半導体装置であって、前記チップ搭載部および前記リードは、金属板を加工して製作されるリードフレームの構成部材であることを特徴とする。 A semiconductor device according to a fifteenth aspect of the present invention is the semiconductor device according to the eleventh aspect, wherein the chip mounting portion and the lead are constituent members of a lead frame manufactured by processing a metal plate. It is characterized by that.

また、本発明の請求項16記載の半導体装置は、請求項11記載の半導体装置であって、前記チップ搭載部および前記配線部材は、配線基板の構成部材であることを特徴とする。 According to a sixteenth aspect of the present invention, there is provided the semiconductor device according to the eleventh aspect, wherein the chip mounting portion and the wiring member are constituent members of a wiring board.

また、本発明の請求項17記載の半導体装置は、電極を有する半導体チップと、前記半導体チップが搭載されるチップ搭載部と、前記チップ搭載部の周囲に配置されるリード又は配線部材と、前記半導体チップが有する前記電極と前記リード又は配線部材とを接続するワイヤと、を備え、少なくとも前記半導体チップ、前記チップ搭載部、前記ワイヤおよび前記リード又は配線部材の前記ワイヤとの接続部分が樹脂封止された半導体装置であって、前記リード又は配線部材のうちの少なくとも1個に、複数本の前記ワイヤの一端の接続部が重ねて接続されており、それらの接続部はボールボンディング法特有の、厚みのあるコイン状に押しつぶされた突起部のほぼ中央からワイヤが導出される形状に形成されていることを特徴とする。 A semiconductor device according to claim 17 of the present invention is a semiconductor chip having electrodes, a chip mounting portion on which the semiconductor chip is mounted, a lead or wiring member disposed around the chip mounting portion, A wire for connecting the electrode of the semiconductor chip and the lead or the wiring member, and at least a connection portion of the semiconductor chip, the chip mounting portion, the wire and the wire of the lead or the wiring member is sealed with resin. A semiconductor device that is stopped, wherein at least one of the leads or wiring members is connected to a connecting portion of one end of a plurality of the wires, and these connecting portions are specific to the ball bonding method. The wire is led out from substantially the center of the protruding portion crushed into a thick coin shape.

また、本発明の請求項18記載の半導体装置は、請求項17記載の半導体装置であって、前記リード又は配線部材に一端が重ねて接続された複数本の前記ワイヤの一部は、その他端が他方の前記リード又は配線部材に、ウェッジボンディング法特有の、厚みの無い三日月状または楕円状の形状をなして接続され、他の一部は、その他端が前記半導体チップが有する前記電極に、ウェッジボンディング法特有の、先端が厚みの無い三日月状または楕円状の形状をなして接続されていることを特徴とする。

The semiconductor device according to claim 18 of the present invention is the semiconductor device according to

また、本発明の請求項19記載の半導体装置は、請求項17記載の半導体装置であって、前記半導体チップを複数個備え、前記リード又は配線部材に一端が重ねて接続された複数本の前記ワイヤのうちの少なくとも一部は、その他端が互いに異なる前記半導体チップの各々が有する前記電極に、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続されていることを特徴とする。

The semiconductor device according to claim 19 of the present invention is the semiconductor device according to

また、本発明の請求項20記載の半導体装置は、請求項17記載の半導体装置であって、前記チップ搭載部および前記リードは、金属板を加工して製作されるリードフレームの構成部材であることを特徴とする。 A semiconductor device according to a twentieth aspect of the present invention is the semiconductor device according to the seventeenth aspect, wherein the chip mounting portion and the lead are constituent members of a lead frame manufactured by processing a metal plate. It is characterized by that.

また、本発明の請求項21記載の半導体装置は、請求項17記載の半導体装置であって、前記チップ搭載部および前記配線部材は、配線基板の構成部材であることを特徴とする。 A semiconductor device according to a twenty-first aspect of the present invention is the semiconductor device according to the seventeenth aspect, wherein the chip mounting portion and the wiring member are constituent members of a wiring board.

本発明の好ましい形態によれば、半導体チップ上の同一の電極に対して、電極の面積を拡大することなく2本以上のワイヤを接続することができる。よって、半導体チップ上の同一の電極に複数本のワイヤを接続する構造において、接続するワイヤ数にかかわらず常に電極の面積を最小にすることができ、チップ全体に占める電極の個数および面積を最小にすることが可能となる。通常、半導体チップにおいては、その外周部に電極が一列ないし複数列に配置されており、電極の個数および面積を最小にすることでチップサイズを小さくすることができる。また、複数本のワイヤを同一の電極に接続できるので、より細線化されたワイヤを用いながら、電源電極や接地電極への安定した電流容量を確保すると同時に、半導体チップの小型化を実現できるので、小型、高品質の半導体装置を安価に提供できるようになる。 According to the preferred embodiment of the present invention, two or more wires can be connected to the same electrode on the semiconductor chip without increasing the area of the electrode. Therefore, in the structure in which multiple wires are connected to the same electrode on the semiconductor chip, the area of the electrode can always be minimized regardless of the number of wires to be connected, and the number and area of the electrodes in the entire chip can be minimized. It becomes possible to. Usually, in a semiconductor chip, electrodes are arranged in one or more rows on the outer periphery thereof, and the chip size can be reduced by minimizing the number and area of the electrodes. In addition, since multiple wires can be connected to the same electrode, it is possible to reduce the size of the semiconductor chip while securing a stable current capacity to the power supply electrode and the ground electrode while using a finer wire. Therefore, a small-sized and high-quality semiconductor device can be provided at low cost.

また、近年、機器の小型化の要求から1個の半導体装置(パッケージ)の中に複数個の半導体チップを内蔵することが行われてきており、QFP型の半導体装置では、各半導体チップ上の電極とリード(インナーリード)とをワイヤで接続すると共に、互いに異なる半導体チップ上の電極同士をワイヤで接続することが行われるようになってきた。同様に、配線基板を用いたBGA(ボール・グリッド・アレイ)型の半導体装置においても、1個のパッケージの中に複数個の半導体チップを内蔵して、各半導体チップ上の電極と配線基板上の表層配線(配線部材)とをワイヤで接続すると共に、互いに異なる半導体チップ上の電極同士をワイヤで接続することが行われるようになってきた。 In recent years, a plurality of semiconductor chips have been built in one semiconductor device (package) due to a demand for miniaturization of equipment. In a QFP type semiconductor device, each semiconductor chip has a built-in structure. An electrode and a lead (inner lead) are connected by a wire, and electrodes on different semiconductor chips are connected by a wire. Similarly, in a BGA (ball grid array) type semiconductor device using a wiring board, a plurality of semiconductor chips are built in one package, and electrodes on each semiconductor chip and the wiring board are mounted. In addition to connecting the surface layer wiring (wiring member) with wires, electrodes on different semiconductor chips have been connected with wires.

本発明の好ましい形態によれば、同一の電極からの複数本のワイヤをそれぞれ異なるリード(インナーリード)又は配線部材(配線基板の表層配線)に接続することや、同一の電極からの複数本のワイヤを互いに異なる半導体チップ上の電極同士の接続に用いることも可能となるため、チップサイズを大きくすることなく、複数本のワイヤが接続された電極を、例えば他方の半導体チップ上の電極とリードとの中継電極として使用することができるようになる。また、同一のリード(インナーリード)又は配線部材(配線基板の表層配線)からの複数本のワイヤをそれぞれ異なるリード又は配線部材に接続することや、同一のリード又は配線部材からの複数本のワイヤをそれぞれ異なる半導体チップ上の電極に接続することや、同一のリード又は配線部材からの複数本のワイヤをそれぞれ半導体チップ上の異なる電極に接続することが可能となるため、リードを大きくすることなく、すなわちパッケージを大きくすることなく、複数本のワイヤが接続されたリード又は配線部材を、例えば各半導体チップ上の複数の電極の電源として用いたり、互いに異なる半導体チップ上の電極同士の中継リード又は中継配線として使用することができるようになる。したがって、装置内の配線を簡略化することが可能となり、高集積、高密度、高品質な半導体装置をコンパクトかつ安価に提供できるようになる。 According to a preferred embodiment of the present invention, a plurality of wires from the same electrode are connected to different leads (inner leads) or wiring members (surface layer wiring of a wiring board), or a plurality of wires from the same electrode are connected. Since wires can be used to connect electrodes on different semiconductor chips, an electrode to which a plurality of wires are connected can be connected to, for example, an electrode on the other semiconductor chip without increasing the chip size. And can be used as a relay electrode. Also, a plurality of wires from the same lead (inner lead) or wiring member (surface wiring of the wiring board) are connected to different leads or wiring members, or a plurality of wires from the same lead or wiring member. Can be connected to electrodes on different semiconductor chips, and a plurality of wires from the same lead or wiring member can be connected to different electrodes on the semiconductor chip without increasing the leads. That is, without using a large package, a lead or a wiring member to which a plurality of wires are connected is used as a power source for a plurality of electrodes on each semiconductor chip, for example, or a relay lead between electrodes on different semiconductor chips or It can be used as a relay wiring. Therefore, the wiring in the device can be simplified, and a highly integrated, high-density, high-quality semiconductor device can be provided in a compact and inexpensive manner.

(実施の形態1)

以下、本発明の実施の形態1について、図面を参照しながら説明する。

図1は本発明の実施の形態1に係る半導体装置の断面図、図2(a)は同半導体装置のワイヤボンディング部分の内部構造を説明するための斜視図、図2(b)は同半導体装置のワイヤボンディング部分の内部構造を説明するための上面図、図2(c)は同半導体装置のワイヤボンディング部分の内部構造を説明するための断面図である。なお、以下の説明において同一の部材には同一符号を付して、適宜説明を省略する。

(Embodiment 1)

1 is a cross-sectional view of a semiconductor device according to

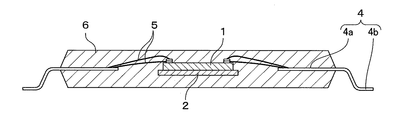

この半導体装置はQFP型の半導体装置であり、図1に示すように、集積回路が形成された半導体チップ1がリードフレームのダイパッド部(チップ搭載部)2に搭載されている。また、ダイパッド部2の周辺には放射状にリードフレームのリード4が配置されており、インナーリード4aの先端がダイパッド部2に対して対向している。また、半導体チップ1の表面に形成されている電極3とインナーリード4aとがワイヤ5で接続されている。また、半導体チップ1、ダイパッド部2、ワイヤ5、インナーリード4a(リード4のワイヤ接続部分)が一括して樹脂封止体6により樹脂封止され、インナーリード4aに連続したリードフレームのアウターリード4bが樹脂封止体6の外部でガルウィング型に曲げ成形されている。

This semiconductor device is a QFP type semiconductor device. As shown in FIG. 1, a

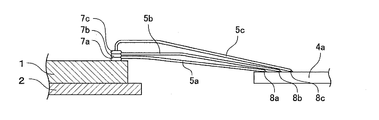

この半導体装置が従来のものと異なるのは、図2に示すように、半導体チップ1上の少なくとも1個の電極3に2本のワイヤ5a、5bの一端の接続部が重ねて接続されており、それらの接続部が、ボールボンディング法特有の、厚みのあるコイン状に押しつぶされた突起部のほぼ中央からワイヤが導出される形状に形成されている点と、それらの2本のワイヤ5a、5bの他端が、同一のインナーリード4aに、ウェッジボンディング法特有の厚みの無い三日月状または楕円状の形状をなして接続されている点である。

As shown in FIG. 2, this semiconductor device is different from the conventional one in that a connection portion at one end of two

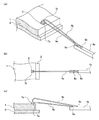

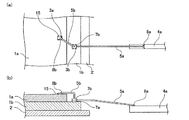

続いて、同一の電極に2本のワイヤを接続する方法について、図3に示す工程断面図に沿って説明する。まず、図3(a)に示すように、ワイヤ供給装置であるキャピラリ9の先端から突出したワイヤ5aの先端とトーチ10との間で放電を行い、スパークによりボール11aを形成する。

Next, a method of connecting two wires to the same electrode will be described along the process cross-sectional view shown in FIG. First, as shown in FIG. 3A, electric discharge is performed between the tip of the

次に図3(b)〜図3(d)に示すように、半導体チップ1上の電極にボール11aを圧着して(ボールボンディング)、ボールボンディング側の接続部7aを形成する。その後、図3(e)〜図3(g)に示すように、ワイヤ5aを水平方向に折り曲げて引き出し、ワイヤ5aが所定の軌跡に沿って配線されるようにキャピラリ9を移動させ、接続対象部材であるインナーリード4aにワイヤ5aをこすり付けて(ウェッジボンディング)、ウェッジボンディング側の接続部8aを形成する。

Next, as shown in FIGS. 3B to 3D, a

以上の第1ボンディング工程を行った後、第2ボンディング工程を行う。すなわち、まず、図3(h)に示すように、キャピラリ9の先端から突出したワイヤ5bの先端とトーチ10との間で放電を行い、スパークによりボール11bを形成する。

After performing the first bonding step, the second bonding step is performed. That is, first, as shown in FIG. 3 (h), discharge is performed between the tip of the

次に図3(i)に示すように、接続部7a(第1ボンディング工程においてボールボンディングを行った部分)に直上からボール11bを圧着して(ボールボンディング)、ボールボンディング側の接続部7bを形成する。その後、図3(j)〜図3(l)に示すように、ワイヤ5bを垂直方向に引き出して折り曲げ、ワイヤ5bが所定の軌跡に沿って配線されるようにキャピラリ9を移動させ、接続対象部材であるインナーリード4aにワイヤ5bをこすり付けて(ウェッジボンディング)、ウェッジボンディング側の接続部8bを形成する。なお、ここでは、第1ボンディング工程と第2ボンディング工程における接続対象部材は同一のインナーリード4aである。

Next, as shown in FIG. 3 (i), the

以上のように第1および第2ボンディング工程を行うことで、同一の電極に2本のワイヤの一端をボールボンディング法により重ねて接続することができる。ワイヤボンディング工程で使用するワイヤには、一般的に、金や銅等の金属を原料とする直径φ15〜40μmのものが使われる。ボールボンディング法においてワイヤの一端に形成されるボールの直径はワイヤの直径の1.5倍〜4倍程度であり、接続点に接合されるときキャピラリの先端部で厚さが5〜60μm程度になるまで押しつぶされるので、ボールボンディング側の接続部は、厚みのあるコイン状に押しつぶされた突起部のほぼ中央からワイヤが導出される形状になる。一方、ワイヤの他端は、キャピラリの先端周辺部で接続点にこすり付けるように潰すので、ウェッジボンディング側の接続部は、厚みの無い三日月状または楕円状の形状になる。 By performing the first and second bonding steps as described above, one end of two wires can be overlapped and connected to the same electrode by the ball bonding method. As a wire used in the wire bonding process, generally, a wire having a diameter of 15 to 40 μm made of a metal such as gold or copper is used. In the ball bonding method, the diameter of the ball formed at one end of the wire is about 1.5 to 4 times the diameter of the wire, and the thickness at the tip of the capillary is about 5 to 60 μm when bonded to the connection point. As a result, the connecting portion on the ball bonding side has a shape in which the wire is led out from substantially the center of the protruding portion crushed into a thick coin shape. On the other hand, the other end of the wire is crushed so as to be rubbed against the connection point around the tip of the capillary, so that the connection part on the wedge bonding side has a crescent or elliptical shape with no thickness.

また、例えば図3(g)に示すように、ボールボンディング側の接続部7aの上部にはワイヤ5aの一部が存在しているため、その上から圧着するボール11bとの接続ズレを防止するために、キャピラリ9によってボール11bを確実に保持しておく必要がある。これに対して、以下で説明する方法を実施すれば、容易に接続ズレを防止することができる。図4は、同一の電極に複数本のワイヤを重ねて接続するに際して接続ズレを防止する方法を説明するための工程断面図である。

Further, for example, as shown in FIG. 3G, since a part of the

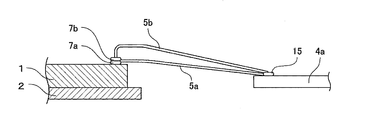

まず、第1ボンディング工程後、図4(a)に示すように、キャピラリ9の先端から突出したワイヤ5bの先端とトーチ10との間で放電を行い、スパークによりボール11bを形成する。次に図4(b)に示すように、平坦部12上にボール11bを押し付けて、ボール11bの下面に平坦面を形成する。次に図4(c)〜図4(d)に示すように、接続部7aに直上からボール11bを圧着してボールボンディング側の接続部7bを形成する。

First, after a 1st bonding process, as shown to Fig.4 (a), it discharges between the front-end | tip of the

このように、第2ボンディング工程に際し、キャピラリ9から突出したワイヤ5bの先端にボール11bを形成した後、平坦部12にボール11bを押し付け、ボール11bの下面に平坦面を形成してボールボンディングを行う。

Thus, in the second bonding step, after forming the

この方法によれば、ボール11bの下面を平坦面としたので、接続部7aの上部に存在するワイヤ5aと接触しても接触ズレを防止することができ、確実な接合を実現できる。なお、平坦部12としては、例えばリードフレームの一部やワイヤボンド設備の一部の平坦面を用いることができる。また、後述するように本発明をBGA型の半導体装置に適用する場合には、配線基板の一部の平坦面を用いることができる。

According to this method, since the lower surface of the

また、以下で説明する方法により接続ズレを防止してもよい。すなわち、図5(a)〜図5(c)に示すように、第1ボンディング工程後、まず、接続部7aに直上から、先端が円錐型の突起形状をしている加圧ツール13を押し当てて接続部7aを押し潰す。次に、図5(d)、図5(e)に示すように、押し潰した接続部7aに直上からボール11bを圧着してボールボンディング側の接続部7bを形成する。加圧ツール13の先端部が押し当てられた接続部7aの上部には円錐型の窪みができるため、ボール11bは確実にその窪みの中央に位置合わせされる。これにより更に確実な接合を実現できる。なお、加圧ツール13の先端部の円錐の開き角度は120〜170°の鈍角に設定するのが望ましい。