JP2008219232A - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP2008219232A JP2008219232A JP2007051170A JP2007051170A JP2008219232A JP 2008219232 A JP2008219232 A JP 2008219232A JP 2007051170 A JP2007051170 A JP 2007051170A JP 2007051170 A JP2007051170 A JP 2007051170A JP 2008219232 A JP2008219232 A JP 2008219232A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- type transistor

- circuit

- delay clock

- inverter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims description 27

- 230000007704 transition Effects 0.000 claims abstract description 5

- 230000003111 delayed effect Effects 0.000 claims description 36

- 239000000758 substrate Substances 0.000 claims description 24

- 230000001934 delay Effects 0.000 claims description 5

- 239000011159 matrix material Substances 0.000 claims description 4

- 230000000630 rising effect Effects 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 24

- 230000004913 activation Effects 0.000 description 18

- 230000004044 response Effects 0.000 description 10

- 238000001514 detection method Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000007257 malfunction Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 238000007562 laser obscuration time method Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356104—Bistable circuits using complementary field-effect transistors

- H03K3/356113—Bistable circuits using complementary field-effect transistors using additional transistors in the input circuit

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/023—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in clock generator or timing circuitry

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/026—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in sense amplifiers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/028—Detection or location of defective auxiliary circuits, e.g. defective refresh counters with adaption or trimming of parameters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

- G11C5/063—Voltage and signal distribution in integrated semi-conductor memory access lines, e.g. word-line, bit-line, cross-over resistance, propagation delay

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

- G11C7/08—Control thereof

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/222—Clock generating, synchronizing or distributing circuits within memory device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

- G11C5/025—Geometric lay-out considerations of storage- and peripheral-blocks in a semiconductor storage device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K2005/00013—Delay, i.e. output pulse is delayed after input pulse and pulse length of output pulse is dependent on pulse length of input pulse

- H03K2005/00019—Variable delay

- H03K2005/00026—Variable delay controlled by an analog electrical signal, e.g. obtained after conversion by a D/A converter

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K2005/00013—Delay, i.e. output pulse is delayed after input pulse and pulse length of output pulse is dependent on pulse length of input pulse

- H03K2005/0015—Layout of the delay element

- H03K2005/00234—Layout of the delay element using circuits having two logic levels

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0018—Special modifications or use of the back gate voltage of a FET

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Static Random-Access Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

- Pulse Circuits (AREA)

Abstract

【課題】回路面積の増大を招くことなく、トランジスタバラツキ耐性を持った遅延クロック回路を提供する。

【解決手段】入力クロック信号を遅延させる遅延クロック回路16では、直列接続された第1および第2のインバータ12,13を有する構成要素が、縦続接続されている。遅延クロック制御回路14は、構成要素の入力の遷移時において、第1および第2のインバータ12,13の接続ノードに貫通電流が流れ、電荷競合が所定時間発生するように、動作する。遅延クロック制御回路14は、電源線VDDと接続ノードとの間に配置されており、ゲートに第2のインバータ13の出力を受ける第1のP型トランジスタ15を備えている。

【選択図】図3

【解決手段】入力クロック信号を遅延させる遅延クロック回路16では、直列接続された第1および第2のインバータ12,13を有する構成要素が、縦続接続されている。遅延クロック制御回路14は、構成要素の入力の遷移時において、第1および第2のインバータ12,13の接続ノードに貫通電流が流れ、電荷競合が所定時間発生するように、動作する。遅延クロック制御回路14は、電源線VDDと接続ノードとの間に配置されており、ゲートに第2のインバータ13の出力を受ける第1のP型トランジスタ15を備えている。

【選択図】図3

Description

本発明は、入力クロック信号を遅延させる遅延クロック回路を備え、遅延クロック信号を、例えばセンスアンプのイネーブル信号等として用いる半導体集積回路に関する。

半導体記憶装置などに用いられるラッチ型センスアンプは、そのイネーブル信号を生成するために、タイミング生成回路を必要とする。タイミング生成回路は、最も簡易な構成としては、縦続接続された複数のインバータによって構成される。インバータのゲート段数を調整することにより、センスアンプのイネーブル信号を最適なタイミングで動作させることができる。

ある従来技術によれば、入力クロック信号の周波数変化に合わせて、遅延クロック信号の遅延時間を調整する。具体的には、入力クロック信号の立下りエッジを基準としたパルス信号をインバータ及びNAND、NOR回路を組み合わせて生成し、遅延クロック信号を生成するインバータチェーンの各インバータの駆動能力を、このパルス信号によって変化させる(特許文献1参照)。

特開2001−344972号公報

上述した従来技術では、入力クロック信号の周波数変化に応じて、最適なタイミングを生成することができる。ところが、インバータの駆動能力を変化させるためのパルス信号を生成するために、規模が大きな回路が必要となる。また、パルス信号の生成回路及び、インバータチェーンに用いられるインバータには、トランジスタのバラツキに対する遅延時間調整の施策がなされていない。

前記の問題に鑑み、本発明は、回路面積の増大を招くことなく、トランジスタバラツキ耐性を持った遅延クロック回路を提供することを目的とする。

本発明は、半導体集積回路として、入力クロック信号を遅延させる遅延クロック回路を備え、前記遅延クロック回路は、直列接続された第1および第2のインバータを有する構成要素が縦続接続されたものであり、前記各構成要素は、入力の遷移時において、前記第1および第2のインバータの接続ノードに貫通電流が流れ、電荷競合が所定時間発生するように動作する遅延クロック制御回路を備えているものである。

本発明によると、遅延クロック回路の各構成要素において、遅延クロック制御回路によって、入力の遷移時において、第1および第2のインバータの接続ノードに、貫通電流による電荷競合を所定時間発生させることができる。これにより、遅延クロック信号を、さらに遅延させることが可能となる。したがって、例えばセンスアンプイネーブル信号の活性化を、従来よりもさらに遅延させることができる。したがって、ビット線対の微小電位差の大きさを増大することができ、誤動作する確率を抑え、半導体集積回路の歩留まりを向上させることができる。

本発明によると、遅延クロック制御回路によって、入力の遷移時において、第1および第2のインバータの接続ノードに、貫通電流による電荷競合を所定時間発生させることができるので、遅延クロック信号をさらに遅延させることが可能となる。

以下、図面を参照しながら、本発明の実施の形態について詳細に説明する。

図1は本発明に係る半導体集積回路の1つとしてのSRAM(Static Random Access Memory)100の構成例を示している。図1のSRAM100は、遅延クロック回路10,16,19,22と、メモリセルアレイ30と、ロウデコーダアレイ40と、書き込み補助回路50と、リード/ライト回路アレイ70とを備えている。リード/ライト回路アレイ70はセンスアンプ20およびデータ入力回路60を含むアレイ構成になっている。

詳細に説明すると、遅延クロック回路10,16,19,22は、入力クロック信号CLKに応じて、センスアンプイネーブル(Sense Amp. Enable)信号SAE、ワード線WLをパルス制御するためのワード線パルス生成信号PLSDLY、および書き込み補助回路50をパルス制御するための書き込みパルス生成信号PWDLYを出力する。これらの信号SAE,PLSDLY,PWDLYが遅延クロック信号に相当する。センスアンプ20は、センスアンプイネーブル信号SAEに応じて動作し、動作時にビット線対BL,NBLの微小電位差を検出し、出力する。メモリセルアレイ30は、行列状に配列された複数のメモリセル8を備えている。複数のワード線WLがメモリセルアレイ30の行に対してそれぞれ設けられており、複数のビット線対BL,NBLがメモリセルアレイ30の列に対してそれぞれ設けられている。

ロウデコーダアレイ40は、メモリセルアレイ40の行に対してそれぞれ設けられた複数のロウデコーダ9を備えている。ロウデコーダ9は、入力クロック信号CLKおよびワード線パルス生成信号PLSDLYに応じて、ワード線WLにパルス信号を出力する。書き込み補助回路50は、メモリセルアレイ40の列に対して設けられており、メモリセル8の電源ソース51と接続されている。そして、書き込みパルス生成信号PWDLYに応じて、電源ソース51にパルス信号を出力する。データ入力回路60は、入力データ信号DIに応じて、ビット線対BL、NBLに電位差を出力する。

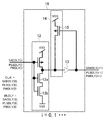

図2は図1のSRAM100における従来技術に係る遅延クロック回路10の概略構成例を示す図である。図2において、12Aは第1のインバータ、13は第2のインバータであり、第1のインバータ12Aの出力と第2のインバータ13の入力とが接続されている。図2に示すように、遅延クロック回路10は、第1のインバータ12Aおよび第2のインバータ13を1構成要素としたアレイ構造である。すなわち、遅延クロック回路10は、直列接続された第1および第2のインバータ12A,13を有する構成要素が、縦続接続されたものである。

図3は図1のSRAM100における本発明の実施形態に係る遅延クロック回路16の概略構成例を示す図である。図3では、図2に示す従来技術の構成に加えて、遅延クロック制御回路14が付された構成になっている。すなわち遅延クロック回路16は、直列接続された第1および第2のインバータ12,13と、遅延クロック制御回路14とを有する構成要素が縦続接続されたものである。遅延クロック制御回路14は、第1および第2のインバータ12,13の接続ノードと、第2のインバータ13の出力ノードとに接続されている。そして、後述するように、構成要素の入力の遷移時において、第1および第2のインバータ12,13の接続ノードに貫通電流が流れ、電荷競合が所定時間発生するように動作する。

そして図3の構成では、遅延クロック制御回路14は、電源線VDDと第1および第2のインバータ12,13の接続ノードとの間に配置されており、ゲートに第2のインバータ13の出力を受ける第1のP型トランジスタ15を備えている。なお、第1のP型トランジスタ15に代えて、多段に直列接続された複数のP型トランジスタを設けてもよい。また、第1のP型トランジスタ15に代えて、インバータを設けてもよい。

また図3の構成では、第1のインバータ12は、接地線VSSと第1および第2のインバータ12,13の接続ノードとの間に配置されており、多段(図では2段)に直列接続された複数のN型トランジスタ12a,12bを備えている。なお、第1および第2のインバータ12,13におけるP型およびN型トランジスタは、1個であってもよいし、多段に直列接続された複数個であってもよい。

図4は図1の構成において、図2の遅延クロック回路10および図3の遅延クロック回路16を採用した場合の動作を説明するためのタイミング図である。ここでは、リード動作の場合を取り上げており、図2の従来技術と図3の本実施形態とを比較して示している。

入力クロック信号CLKがロウデコーダ9に入力され、ロウデコーダ9の出力すなわちワード線WLが活性化する。メモリセル8はワード線WLの活性化に応じて、ビット線対BL,NBLに微小電位差を発生させる。一方で、入力クロック信号CLKは遅延クロック回路10,16に入力される。

図2の従来技術では、入力クロック信号CLKがHigh(以降、“H”)になると、第1のインバータ12はP型トランジスタがオフ、N型トランジスタがオンすることになり、Low(以降、“L”)を出力する。このため、次段の第2のインバータ13の入力に“L”が印加される。そのため、第2のインバータ13はP型トランジスタがオン、N型トランジスタがオフすることになり、“H”を出力する。ゲート段数を変えることにより、センスアンプイネーブル信号SAEの活性化タイミングを調整することができる。センスアンプ20はセンスアンプイネーブル信号SAEの活性化に応じて、ビット線対BL,NBLの微小電位差を検出し、出力する。

一方、図3の本実施形態では、入力クロック信号CLKが“L”のとき、第1のインバータ12はP型トランジスタがオン、N型トランジスタがオフしており、“H”を出力する。このため、次段の第2のインバータ13の入力に“H”が印加される。そのため、第2のインバータ13はP型トランジスタがオフ、N型トランジスタがオンすることになり、“L”を出力する。第2のインバータ13の出力“L”が、遅延クロック制御回路14の第1のP型トランジスタ15のゲートに入力される。この結果、第1のP型トランジスタ15はオンする。

入力クロック信号CLKが“H”になると、第1のインバータ12はP型トランジスタがオフ、N型トランジスタがオンすることになり、“L”を出力する。この時点では、遅延クロック制御回路14の第1のP型トランジスタ15はオンしており、この結果、第1のインバータ12のN型トランジスタによる電荷放電と、第1のP型トランジスタ15による電荷充電との貫通電流による電荷競合が一定時間、発生する。その後、次段の第2のインバータ13の入力に“L”が印加される。そのため、第2のインバータ13はP型トランジスタがオン、N型トランジスタがオフすることになり、“H”を出力する。ゲート段数を変えるだけでなく、遅延クロック制御回路14の第1のP型トランジスタ15を加えることにより、貫通電流による電荷競合を一定時間発生させることができ、センスアンプイネーブル信号SAEの活性化タイミングを調整することができる。センスアンプ20はセンスアンプイネーブル信号SAEの活性化に応じて、ビット線対BL,NBLの微小電位差を検出し、出力する。

以上の通り、本実施形態に係る図3の遅延クロック回路16を採用することによって、遅延クロック制御回路14の第1のP型トランジスタ15と第1のインバータ12のN型トランジスタとによって、貫通電流による電荷競合を一定時間発生させることができる。これにより、センスアンプイネーブル信号SAEの活性化を従来技術よりもさらに遅延させることができる。つまり、トランジスタ素子を1つ追加するだけで、大幅な面積増大を招くことなく、トランジスタバラツキ、特にSRAM100においてP型トランジスタの駆動能力が大きくN型トランジスタの駆動能力が小さい場合において、センスアンプイネーブル信号SAEの活性化を従来技術よりもさらに遅延させることができる。したがって、ビット線対BL,NBLの微小電位差の大きさを増大することができ、誤動作する確率を抑え、SRAMおよびSRAMを搭載する半導体集積回路の歩留まりを向上させることができる。

なお、貫通電流による電荷競合が発生する所定時間は、入力クロック信号CLKの立ち上がりエッジ間隔よりも短いことが望ましい。

また、図3の遅延クロック回路16において、第1のインバータ12が有する多段に直列接続された複数のN型トランジスタのゲート幅の和は、遅延クロック制御回路14の第1のP型トランジスタ15のゲート幅の2倍以上40倍以下であることが望ましい。このゲート幅の比率が2倍未満の場合、第1のインバータ12のN型トランジスタによる電荷を放電する駆動能力が、遅延クロック制御回路14の第1のP型トランジスタ15による電荷を充電する駆動能力に劣ることとなり、遅延クロック回路16が誤動作してしまう。一方、このゲート幅の比率が40倍を超えた場合、貫通電流による電荷競合を発生させて遅延時間を増大させる効果がほとんどなくなる。したがって、上述のゲート幅の制限内で設計を行うことにより、センスアンプイネーブル信号SAEの活性化タイミングを最適とすることができる。

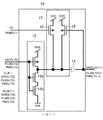

図5は図1のSRAM100における本発明の実施形態に係る遅延クロック回路19の概略構成例を示す図である。図5では、図2に示す従来技術の構成に加えて、遅延クロック制御回路17が付された構成になっている。すなわち遅延クロック回路19は、直列接続された第1および第2のインバータ12,13と、遅延クロック制御回路17とを有する構成要素が縦続接続されたものである。遅延クロック制御回路17は、第1および第2のインバータ12,13の接続ノードと、第2のインバータ13の出力ノードとに接続されている。また遅延クロック制御回路17は、図3の遅延クロック制御回路14と対比すると、第1のP型トランジスタ15に加えて、第2のP型トランジスタ18を備えている。第2のP型トランジスタ18は、電源線VDDと第1および第2のインバータ12,13の接続ノードとの間に、第1のP型トランジスタ15と並列に配置されており、ゲートに第1の外部信号TEを受ける。すなわち第2のP型トランジスタ18は第1の外部信号TEに応じてそのオンオフが制御される。

図6は図1の構成において、図5の遅延クロック回路19を採用した場合の動作を説明するためのタイミング図である。ここでは、リード動作の場合を取り上げている。また第1の外部信号TEは通常動作とテスト動作とを切り替える信号として説明する。また、SRAM100の基本的な動作は図4と同様であるため、説明を省略する。

通常動作では、第1の外部信号TEは“H”になり、第2のP型トランジスタ18をオフにする。このとき、遅延クロック制御回路17において遅延クロック信号をさらに遅延させるトランジスタは第1のP型トランジスタ15のみとなり、図3の構成と同様の効果が得られる。

テスト動作では、第1の外部信号TEは“L”になり、第2のP型トランジスタ18をオンにする。このとき、遅延クロック制御回路17において、第1のP型トランジスタ15に加えて第2のP型トランジスタ18が、遅延クロック信号をさらに遅延させるトランジスタとして動作する。これにより、図3の構成よりもさらに遅延時間が増大する。

以上の通り、本実施形態に係る図5の遅延クロック回路19を採用した場合、テスト動作のとき、遅延クロック制御回路17の第1および第2のP型トランジスタ15,18と第1のインバータ12のN型トランジスタとによって、貫通電流による電荷競合を一定時間発生させることができる。これにより、センスアンプイネーブル信号SAEの活性化をさらに遅延させることができる。つまり、トランジスタ素子をさらに1つ追加するだけで、大幅な面積増大を招くことなく、テスト動作時におけるセンスアンプイネーブル信号SAEの活性化をさらに遅延させることができる。したがって、ビット線対BL,NBLの微小電位差の大きさを増大することができ、誤動作する確率を抑え、SRAMおよびSRAMを搭載する半導体集積回路の故障検出箇所の特定および故障検出率の向上を促進することができるとともに、歩留まりを向上させることができる。

なお、第1の外部信号TEは通常動作とテスト動作とを切り替える信号だけに限定されない。例えば、第1の外部信号TEを定常的に“L”とすることにより、センスアンプイネーブル信号SAEの活性化をさらに遅延させることができる。したがって、ビット線対BL,NBLの微小電位差の大きさを増大することができ、誤動作する確率を抑えることも可能である。

また図5の構成において、第1のP型トランジスタ15を省略しても良い。

また、図5の遅延クロック回路19において、第1のインバータ12が有する多段に直列接続された複数のN型トランジスタのゲート幅の和は、遅延クロック制御回路17の第1および第2のP型トランジスタ15,18のゲート幅の和の2倍以上40倍以下であることが望ましい。このゲート幅の比率が2倍未満の場合、第1のインバータ12のN型トランジスタによる電荷を放電する駆動能力が、遅延クロック制御回路17の第1および第2のP型トランジスタ15,18による電荷を充電する駆動能力に劣ることとなり、遅延クロック回路19が誤動作してしまう。一方、このゲート幅の比率が40倍を超えた場合、貫通電流による電荷競合を発生させて遅延時間を増大させる効果がほとんどなくなる。したがって、上述のゲート幅の制限内で設計を行うことにより、センスアンプイネーブル信号SAEの活性化タイミングを最適とすることができる。

図7は図1のSRAM100における本発明の実施形態に係る遅延クロック回路22の概略構成例を示す図である。図7では、図3の遅延クロック回路16に加えて、P型トランジスタ用基板制御回路23およびN型トランジスタ用基板制御回路24が付された構成になっている。P型トランジスタ用基板制御回路23は第2の外部信号BEに応じて、信号VDDBBによって、遅延クロック制御回路14における第1のP型トランジスタ15の基板電位を制御する。N型トランジスタ用基板制御回路24は同じく第2の外部信号BEに応じて、信号VSSBBによって、第1のインバータ12における複数のN型トランジスタ12a,12bの基板電位を制御する。

図8は図1の構成において、図7の遅延クロック回路22を採用した場合の動作を説明するためのタイミング図である。ここでは、リード動作の場合を取り上げている。また第2の外部信号BEは通常動作とテスト動作とを切り替える信号として説明する。また、SRAM100の基本的な動作は図4と同様であるため、説明を省略する。

通常動作では、第2の外部信号BEに応じて、P型トランジスタ用基板制御回路23は出力信号VDDBBによって第1のP型トランジスタ15の基板にバイアスを印加せず、またN型トランジスタ用基板制御回路24は出力信号VSSBBによって第1のインバータ12のN型トランジスタの基板にバイアスを印加しない。これにより、第1のP型トランジスタ15および第1のインバータ12のN型トランジスタ12a,12bの閾値電圧に変化はなく、図3と同様の効果が得られる。

テスト動作では、第2の外部信号BE25に応じて、P型トランジスタ用基板制御回路23は出力信号VDDBBによって第1のP型トランジスタ15の基板に順バイアスを印加し、N型トランジスタ用基板制御回路24は出力信号VSSBBによって第1のインバータ12のN型トランジスタ12a,12bの基板に逆バイアスを印加する。これにより、第1のP型トランジスタ15は、閾値電圧の絶対値が減少するため電流駆動能力が増大し、第1のインバータ12のN型トランジスタ12a,12bは、閾値電圧の絶対値が増加するため電流駆動能力が減少することから、接続ノードにおいて電荷競合が発生し、図3よりもさらに遅延時間が増大する。

以上の通り、本実施形態に係る図7の遅延クロック回路22を採用した場合、テスト動作のとき、遅延クロック制御回路14における第1のP型トランジスタ15の閾値電圧の絶対値を減少させるとともに、第1のインバータ12におけるN型トランジスタ12a,12bの閾値電圧の絶対値を増加させることができる。このため、第1のP型トランジスタ15の駆動能力が増大するとともに、第1のインバータ12のN型トランジスタ12a,12bの駆動能力が減少するので、貫通電流による電荷競合を一定時間発生させることができる。これにより、テスト動作時のセンスアンプイネーブル信号SAEの活性化をさらに遅延させることができる。したがって、ビット線対BL,NBLの微小電位差の大きさを増大することができ、誤動作する確率を抑え、SRAM及びSRAMを搭載する半導体集積回路の故障検出箇所の特定および故障検出率の向上を促進することができるとともに、歩留まりを向上させることができる。

なお、第2の外部信号BEは通常動作とテスト動作とを切り替える信号だけに限定されない。例えば、第2の外部信号BE25によって、定常的に、第1のP型トランジスタ15の基板に順バイアスを印加し、第1のインバータ12のN型トランジスタ12a,12bの基板に逆バイアスを印加するようにしてもよい。これにより、センスアンプイネーブル信号SAEの活性化をさらに遅延させることができ、ビット線対BL,NBLの微小電位差の大きさを増大することができ、誤動作する確率を抑えることも可能である。また図7において、P型トランジスタ用基板制御回路23またはN型トランジスタ制御回路24のいずれか一方のみを設けるようにしてもかまわない。

図9は図1のSRAM100におけるロウデコーダ9の概略構成例を示す図である。図9において、ロウデコーダ9は、アドレス信号ADによって選択されたとき、ワード線WLにパルス信号を出力する。入力クロック信号CLKはワード線WLに出力するパルス信号の立ち上がり側のパルスエッジを生成する。ワード線パルス生成信号PLSDLYはワード線WLに出力するパルス信号の立ち下がり側のパルスエッジを生成する。そしてロウデコーダ9は、遅延クロック回路16,19,22から出力された遅延クロック信号を、ワード線パルス生成信号PLSDLYとして受ける。

図10は図9のロウデコーダ9を含む図1のSRAM100の動作を説明するためのタイミング図である。ここではリード動作の場合を取り上げている。また図10では、通常動作とセンスアンプイネーブル信号SAEが遅延した場合の動作とを示している。ここでは、通常動作は設計時に設定した動作タイミングであり、これに対してプロセス、電圧、温度、周波数など様々な条件がばらついた場合に、センスアンプイネーブル信号SAEが遅延したものとする。

図10において、入力クロック信号CLKがロウデコーダ9に入力され、ロウデコーダ9の出力すなわちワード線WLが活性化する。メモリセル8はワード線WLの活性化に応じてビット線対BL,NBLに微小電位差を発生させる。一方で、入力クロック信号CLKは遅延クロック回路16,19,22に入力される。センスアンプ20は遅延クロック回路16,19,22の出力であるセンスアンプイネーブル信号SAEの活性化に応じて、ビット線対BL,NBLの微小電位差を検出し、出力する。

ロウデコーダ9の出力すなわちワード線WLは、遅延クロック回路16,19,22の出力であるワード線パルス生成信号PLSDLYに応じて不活性化する。様々な条件がばらついたとしても、センスアンプイネーブル信号SAEとワード線パルス生成信号PLSDLYとは同一の遅延クロック回路16,19,22から出力されているため、それぞれのタイミングは条件のバラツキに対して同様の傾向を示す。したがって、センスアンプイネーブル信号SAEが遅延した場合、ワード線パルス生成信号PLSDLYも同様に遅延する。これにより、ワード線WLのパルス幅が広がることになる。

以上の通り、図1および図9の構成によると、ワード線パルス生成信号PLSDLYとセンスアンプイネーブル信号SAEとは、そのタイミングが条件バラツキに対して同様の傾向を示す。したがって、センスアンプイネーブル信号SAEが遅延した場合、ワード線パルス生成信号PLSDLYも同様に遅延し、ワード線WLのパルス幅が広がることになる。よって、ビット線対BL,NBLの微小電位差も増大し、誤動作する確率を抑え、SRAMおよびSRAMを搭載する半導体集積回路の歩留まりを向上させることができる。

なお、センスアンプイネーブル信号SAEとワード線パルス生成信号PLSDLYは、同じ遅延クロック回路16,19,22からの出力ではあるが、必ずしも同じゲート段数から出力されていなくとも良い。

図11は図1のSRAM100におけるロウデコーダレプリカ(RDR)29の概略構成例を示す図である。図11において、ロウデコードレプリカ29は、ロウデコーダ9と同一構成からなり、アドレス信号ADを受ける代わりに、常に選択される様に、電源電圧VDDまたは電源電圧VDDに準ずる信号を受ける。すなわち、アドレス信号ADによって選択されたロウデコーダ9と同一タイミングで、パルス信号をワード線遅延信号WLDLYとして出力する。ロウデコーダレプリカ29から出力されたワード線遅延信号WLDLYは、遅延クロック回路16,19,22に入力クロック信号として入力される。

以上の通り、図11の構成によると、ロウデコーダ9と同一構成からなるロウデコーダレプリカ29から送られるワード線遅延信号WLDLYは、ワード線WLとほぼ同じタイミングで活性化される。このため、遅延クロック回路16,19,22に入力されるタイミングのバラツキを抑えることが可能である。なお、ワード線パルス生成信号PLSDLYは省略されても良い。

図12は図1のSRAM100において、メモリセルレプリカ32を用いた場合の動作を示すタイミング図である。図1において、メモリセルレプリカアレイ36は、メモリセル8と同一構成からなるメモリセルレプリカ32が複数個、行状に配置されたものである。そして、メモリセルレプリカ32の列に対してレプリカビット線対RBL,RNBLが設けられている。またメモリセルレプリカ遅延信号MEMDLYは、レプリカビット線対RBL,RNBLに所定の電位差が生じたか否かを示す信号であり、ここではレプリカビット線対RBL,RNBLに所定の電位差が生じたとき“H”になるものとする。そして、遅延クロック回路19は、メモリセルレプリカ遅延信号MEMDLY35を、第2の外部信号TEの代わりに、遅延クロック制御回路17における第2のP型トランジスタ18のゲートに受ける。

図1の構成によれば、メモリセル8のバラツキをメモリセルレプリカ32が反映することになる。このため、図12に示すように、メモリセル8およびメモリセルレプリカ32の電荷引き抜きが早い場合、遅延クロック回路19内の第2のP型トランジスタ18をオフするタイミングが早いため、センスアンプイネーブル信号SAEによってセンスアンプ20が起動するタイミングも早くなる。一方、メモリセル8およびメモリセルレプリカ32の電荷引き抜きが遅い場合、遅延クロック回路19内の第2のP型トランジスタ18がオンしている期間が長くなり、オフするタイミングが遅くなるため、センスアンプイネーブル信号SAEによってセンスアンプ20が起動するタイミングも遅くなる。

このように、メモリセル8のバラツキによらず、ビット線対BL,NBLの微小電位差が十分に確保された状態で、センスアンプ20が起動することになり、したがって、歩留まりを向上させることができる。

図13は図1のSRAM100における書き込み補助回路50の構成例を示す図である。図13の構成では、電源ソース51が電圧降下し過ぎない様に、P型トランジスタを用いて、電荷を引き抜いている。図1において、書き込み補助回路50はメモリセル8の列に対して設けられており、書き込み補助パルス信号PWPLSがパルスを出力している期間、メモリセルの電源ソース51の電位を下げる。書き込み補助パルス信号PWPLSは、書き込みイネーブル信号WEおよび、遅延クロック回路16,19,22から出力された遅延クロック信号としての書き込みパルス生成信号PWDLYから生成される。書き込みパルス生成信号PWDLYは書き込み補助パルス信号PWPLSのパルスエッジを生成する。

図14は図1のSRAM100において、書き込み補助回路50を用いた場合の動作を示すタイミング図である。上述したように、書き込み補助回路50の入力信号である書き込み補助パルス信号PWPLSは、そのパルスエッジが、書き込みパルス生成信号PWDLY5から生成されている。ここで、最も書き込みが行いにくいプロセスバラツキ、つまりP型トランジスタの駆動能力が大きくN型トランジスタの駆動能力が小さい場合、遅延回路16,19,22は、従来の遅延回路10と比較し、活性化するタイミングを遅延することができる。したがって、書き込みパルス生成信号PWDLYの活性化が遅延されることから、書き込み補助パルス信号PWPLSのパルス幅が大きくなる。これにより、書き込み補助回路50の出力である電源ソース51の電位を下げ、書き込みが行いやすいようにすることができる。

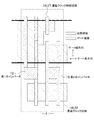

図15は図1のSRAM100のレイアウトの概略構成例を示す図である。図15において、16,19,21は遅延クロック回路、30はメモリセルアレイ、40はロウデコーダアレイ、70は複数のリード/ライト回路が列状に配列されたリード/ライト回路アレイ、80は信号制御回路である。遅延クロック制御回路14,17は、遅延クロック回路16,19,21との距離に対し、メモリセルアレイ30、ロウデコーダアレイ40およびリード/ライト回路アレイ70との距離の方が長くなる位置に配置されている。

図15の構成のように、信号制御回路80内に遅延クロック制御回路14,17を配置することによって、レイアウト面積の増大を抑え、ロウデコーダアレイ40およびリード/ライト回路アレイ70への配線リソースを確保することができる。

図16および図17は図3および図7の遅延クロック回路16,22のレイアウトの概略構成例を示す図である。図16および図17において、ゲート電極が延びる方向をゲート幅方向、ゲート幅方向の垂直方向をゲート長方向と定義すると、遅延クロック回路16,22は、第1のインバータ12のP型トランジスタのソース及びドレインと、第2のインバータ13のP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされている。また、第2のインバータ13のP型トランジスタのソース及びドレインと、遅延クロック制御回路14,17が有する第1のP型トランジスタ15のソース及びドレインとが、ほぼ一直線にレイアウトされている。

以上の通り、図16および図17の構成によれば、拡散領域が、ゲート長方向にほぼ一直線にレイアウトされている。これにより、トランジスタの特性バラツキを低減することができる。このため、遅延クロック回路16,22から出力される信号のタイミングバラツキを抑えることが可能となる。

図18は図3および図7の遅延クロック回路16,22のレイアウトの概略構成例を示す図である。図18において、ゲート電極が延びる方向をゲート幅方向、ゲート幅方向の垂直方向をゲート長方向と定義すると、遅延クロック回路16,22は、第1のインバータ12のP型トランジスタのソース及びドレインと、第2のインバータ13のP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされている。また、第1のインバータ12のP型トランジスタのソース及びドレインと、遅延クロック制御回路14,17が有する第1のP型トランジスタ15のソース及びドレインとが、ほぼ一直線にレイアウトされている。

以上の通り、図18の構成によれば、拡散領域が、ゲート長方向にほぼ一直線にレイアウトされている。これにより、トランジスタの特性バラツキを低減することができる。このため、遅延クロック回路16,22から出力される信号のタイミングバラツキを抑えることが可能となる。

なお、本発明は上述した実施形態に限定されるものではなく、その要旨を逸脱しない範囲で、種々変形して実施することができる。例えば、ここでは、SRAMを用いて説明を行ったが、DRAMやその他の半導体記憶装置でも変形して実施することができる。

本発明によると、回路面積の増大を招くことなく、半導体集積回路にトランジスタバラツキ耐性を持たせることができる。したがって例えば、センスアンプを含む半導体記憶装置、特にSRAM、詳しくは、マイクロプロセッサ用のキャッシュメモリ等として有用である。

16,19,22 遅延クロック回路

12 第1のインバータ

12a,12b N型トランジスタ

13 第2のインバータ

14,17 遅延クロック制御回路

15 第1のP型トランジスタ

18 第2のP型トランジスタ

23 P型トランジスタ用基板制御回路

24 N型トランジスタ用基板制御回路

8 メモリセル

30 メモリセルアレイ

20 センスアンプ

9 ロウデコーダ

29 ロウデコーダレプリカ

32 メモリセルレプリカ

36 メモリセルレプリカアレイ

50 書き込み補助回路

51 電源ソース

CLK 入力クロック信号

TE 第1の外部信号

BE 第2の外部信号

WL ワード線

BL,NBL ビット線対

AD アドレス信号

SAE センスアンプイネーブル信号

PLSDLY ワード線パルス生成信号

WLDLY ワード線遅延信号

RBL,RNBL レプリカビット線対

MEMDLY メモリセルレプリカ遅延信号

PWPLS 書き込み補助パルス信号

PWDLY 書き込みパルス生成信号

12 第1のインバータ

12a,12b N型トランジスタ

13 第2のインバータ

14,17 遅延クロック制御回路

15 第1のP型トランジスタ

18 第2のP型トランジスタ

23 P型トランジスタ用基板制御回路

24 N型トランジスタ用基板制御回路

8 メモリセル

30 メモリセルアレイ

20 センスアンプ

9 ロウデコーダ

29 ロウデコーダレプリカ

32 メモリセルレプリカ

36 メモリセルレプリカアレイ

50 書き込み補助回路

51 電源ソース

CLK 入力クロック信号

TE 第1の外部信号

BE 第2の外部信号

WL ワード線

BL,NBL ビット線対

AD アドレス信号

SAE センスアンプイネーブル信号

PLSDLY ワード線パルス生成信号

WLDLY ワード線遅延信号

RBL,RNBL レプリカビット線対

MEMDLY メモリセルレプリカ遅延信号

PWPLS 書き込み補助パルス信号

PWDLY 書き込みパルス生成信号

Claims (15)

- 入力クロック信号を遅延させる遅延クロック回路を備え、

前記遅延クロック回路は、

第1および第2のインバータを有する構成要素が、縦続接続されたものであり、

前記各構成要素は、

入力の遷移時において、前記第1および第2のインバータの接続ノードに貫通電流が流れ、電荷競合が所定時間発生するように動作する遅延クロック制御回路を備えている

ことを特徴とする半導体集積回路。 - 請求項1において、

前記所定時間は、前記入力クロック信号の立ち上がりエッジ間隔よりも短い

ことを特徴とする半導体集積回路。 - 請求項1において、

前記遅延クロック制御回路は、

電源線と前記接続ノードとの間に配置されており、ゲートに前記第2のインバータの出力を受ける第1のP型トランジスタを備え、

前記第1のインバータは、

接地線と前記接続ノードとの間に配置されており、多段に直列接続された複数のN型トランジスタを備えている

ことを特徴とする半導体集積回路。 - 請求項3において、

前記複数のN型トランジスタのゲート幅の和は、前記第1のP型トランジスタのゲート幅の2倍以上40倍以下である

ことを特徴とする半導体集積回路。 - 請求項3において、

前記遅延クロック制御回路は、

電源線と前記接続ノードとの間に配置されており、ゲートに第1の外部信号を受ける第2のP型トランジスタを備えている

ことを特徴とする半導体集積回路。 - 請求項5において、

前記複数のN型トランジスタのゲート幅の和は、前記第1および第2のP型トランジスタのゲート幅の和の2倍以上40倍以下である

ことを特徴とする半導体集積回路。 - 請求項5において、

前記第1の外部信号は、通常動作とテスト動作とを切り替える信号であり、テスト動作時に、前記第2のP型トランジスタをオンさせるものである

ことを特徴とする半導体集積回路。 - 請求項3において、

第2の外部信号に応じて、前記第1のP型トランジスタおよび前記複数のN型トランジスタの基板電位を制御する基板制御回路をさらに備えている

ことを特徴とする半導体集積回路。 - 請求項8において、

前記第2の外部信号は、通常動作とテスト動作とを切り替える信号であり、

前記基板制御回路は、

テスト動作時に、前記第1のP型トランジスタの基板に順バイアスを印加するとともに、前記複数のN型トランジスタの基板に逆バイアスを印加する

ことを特徴とする半導体集積回路。 - 請求項1において、

複数のメモリセルが行列状に配列されたメモリセルアレイと、

前記メモリセルの行に対してそれぞれ設けられた複数のワード線と、

前記メモリセルの列に対してそれぞれ設けられた複数のビット線対と、

前記ビット線対の微小電位差を増幅するセンスアンプと、

アドレス信号によって選択されたとき、前記ワード線にパルス信号を出力するロウデコーダとを備え、

前記センスアンプは、前記遅延クロック回路から出力された遅延クロック信号を、センスアンプイネーブル信号として受けるものであり、

前記ロウデコーダは、前記遅延クロック回路から出力された遅延クロック信号を、前記パルス信号のパルスエッジを生成するワード線パルス生成信号として受けるものである

ことを特徴とする半導体集積回路。 - 請求項10において、

前記ロウデコーダと同一構成からなり、アドレス信号を受けないで、選択された前記ロウデコーダと同一タイミングでパルス信号を出力するロウデコーダレプリカを備え、

前記ロウデコーダレプリカから出力された前記パルス信号が、前記遅延クロック回路に、前記入力クロック信号として入力される

ことを特徴とする半導体集積回路。 - 請求項5において、

複数のメモリセルが行列状に配列されたメモリセルアレイと、

前記メモリセルの行に対してそれぞれ設けられた複数のワード線と、

前記メモリセルの列に対してそれぞれ設けられた複数のビット線対と、

前記ビット線対の微小電位差を増幅するセンスアンプと、

前記メモリセルと同一構成からなるメモリセルレプリカが複数個、列状に配列されたメモリセルレプリカアレイと、

前記メモリセルレプリカの列に対して設けられたレプリカビット線対とを備え、

前記センスアンプは、前記遅延クロック回路から出力された遅延クロック信号を、センスアンプイネーブル信号として受けるものであり、

前記遅延クロック回路は、前記レプリカビット線対に所定の電位差が生じたか否かを示す信号を、前記第1の外部信号の代わりに、前記遅延クロック制御回路における前記第2のP型トランジスタのゲートに受けるものである

ことを特徴とする半導体集積回路。 - 請求項1において、

複数のメモリセルが行列状に配列されたメモリセルアレイと、

前記メモリセルの列に対して設けられており、書き込み補助パルス信号がパルスを出力している期間、前記メモリセルの電源ソースの電位を下げる書き込み補助回路とを備え、

前記書き込み補助パルス信号のパルスエッジは、前記遅延クロック回路から出力された遅延クロック信号によって生成されている

ことを特徴とする半導体集積回路。 - 請求項3において、

前記遅延クロック回路は、

前記第1のインバータのP型トランジスタのソース及びドレインと、前記第2のインバータのP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされており、かつ、

前記第2のインバータのP型トランジスタのソース及びドレインと、前記遅延クロック制御回路が有する前記第1のP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされている

ことを特徴とする半導体集積回路。 - 請求項3において、

前記遅延クロック回路は、

前記第1のインバータのP型トランジスタのソース及びドレインと、前記第2のインバータのP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされており、かつ、

前記第1のインバータのP型トランジスタのソース及びドレインと、前記遅延クロック制御回路が有する前記第1のP型トランジスタのソース及びドレインとが、ほぼ一直線にレイアウトされている

ことを特徴とする半導体集積回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007051170A JP2008219232A (ja) | 2007-03-01 | 2007-03-01 | 半導体集積回路 |

| US12/027,411 US20080211556A1 (en) | 2007-03-01 | 2008-02-07 | Semiconductor integrated circuit |

| CNA2008100809379A CN101256824A (zh) | 2007-03-01 | 2008-02-29 | 半导体集成电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007051170A JP2008219232A (ja) | 2007-03-01 | 2007-03-01 | 半導体集積回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008219232A true JP2008219232A (ja) | 2008-09-18 |

| JP2008219232A5 JP2008219232A5 (ja) | 2010-02-25 |

Family

ID=39732670

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007051170A Withdrawn JP2008219232A (ja) | 2007-03-01 | 2007-03-01 | 半導体集積回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20080211556A1 (ja) |

| JP (1) | JP2008219232A (ja) |

| CN (1) | CN101256824A (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5963647B2 (ja) * | 2012-01-30 | 2016-08-03 | エスアイアイ・セミコンダクタ株式会社 | 半導体記憶回路を備えた半導体装置 |

| CN110956990B (zh) * | 2018-09-26 | 2022-03-01 | 展讯通信(上海)有限公司 | Sram读取延时控制电路及sram |

| EP4033661B1 (en) | 2020-11-25 | 2024-01-24 | Changxin Memory Technologies, Inc. | Control circuit and delay circuit |

| EP4033312A4 (en) | 2020-11-25 | 2022-10-12 | Changxin Memory Technologies, Inc. | CONTROL CIRCUIT AND DELAY CIRCUIT |

| US11681313B2 (en) | 2020-11-25 | 2023-06-20 | Changxin Memory Technologies, Inc. | Voltage generating circuit, inverter, delay circuit, and logic gate circuit |

| EP4033664B1 (en) | 2020-11-25 | 2024-01-10 | Changxin Memory Technologies, Inc. | Potential generation circuit, inverter, delay circuit, and logic gate circuit |

| CN114545807B (zh) * | 2020-11-25 | 2024-03-26 | 长鑫存储技术有限公司 | 控制电路和延时电路 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3071915B2 (ja) * | 1991-12-20 | 2000-07-31 | 株式会社東芝 | 出力回路 |

| US5424985A (en) * | 1993-06-30 | 1995-06-13 | Sgs-Thomson Microelectronics, Inc. | Compensating delay element for clock generation in a memory device |

| US5841300A (en) * | 1994-04-18 | 1998-11-24 | Hitachi, Ltd. | Semiconductor integrated circuit apparatus |

| US6590423B1 (en) * | 1994-10-11 | 2003-07-08 | Derek Wong | Digital circuits exhibiting reduced power consumption |

| US5517136A (en) * | 1995-03-03 | 1996-05-14 | Intel Corporation | Opportunistic time-borrowing domino logic |

| US5661675A (en) * | 1995-03-31 | 1997-08-26 | Intel Corporation | Positive feedback circuit for fast domino logic |

| US6104213A (en) * | 1998-03-02 | 2000-08-15 | International Business Machines Corporation | Domino logic circuit having a clocked precharge |

| US6097207A (en) * | 1998-08-21 | 2000-08-01 | International Business Machines Corporation | Robust domino circuit design for high stress conditions |

| JP3358612B2 (ja) * | 1999-03-15 | 2002-12-24 | 日本電気株式会社 | 半導体集積回路 |

| JP3241686B2 (ja) * | 1999-03-26 | 2001-12-25 | 日本電気株式会社 | ダイナミック型論理回路及びドミノ論理素子 |

| US6137319A (en) * | 1999-04-30 | 2000-10-24 | Intel Corporation | Reference-free single ended clocked sense amplifier circuit |

| US6346831B1 (en) * | 1999-09-28 | 2002-02-12 | Intel Corporation | Noise tolerant wide-fanin domino circuits |

| US6549040B1 (en) * | 2000-06-29 | 2003-04-15 | Intel Corporation | Leakage-tolerant keeper with dual output generation capability for deep sub-micron wide domino gates |

| US6469953B1 (en) * | 2001-08-08 | 2002-10-22 | Intel Corporation | Latch circuit |

| US6429689B1 (en) * | 2001-10-10 | 2002-08-06 | International Business Machines Corporation | Method and apparatus for controlling both active and standby power in domino circuits |

| US6933744B2 (en) * | 2002-06-11 | 2005-08-23 | The Regents Of The University Of Michigan | Low-leakage integrated circuits and dynamic logic circuits |

| US7218151B1 (en) * | 2002-06-28 | 2007-05-15 | University Of Rochester | Domino logic with variable threshold voltage keeper |

| JP2004048313A (ja) * | 2002-07-11 | 2004-02-12 | Matsushita Electric Ind Co Ltd | ダイナミック回路 |

| US6765414B2 (en) * | 2002-09-17 | 2004-07-20 | Intel Corporation | Low frequency testing, leakage control, and burn-in control for high-performance digital circuits |

| US7034576B2 (en) * | 2003-06-27 | 2006-04-25 | Sun Microsystems, Inc. | Pulsed dynamic keeper gating |

| US7202705B2 (en) * | 2004-10-14 | 2007-04-10 | International Business Machines Corporation | Dynamic logic circuit apparatus and method for reducing leakage power consumption via separate clock and output stage control |

| US7282960B2 (en) * | 2005-06-28 | 2007-10-16 | International Business Machines Corporation | Dynamic logical circuit having a pre-charge element separately controlled by a voltage-asymmetric clock |

| JP2007096907A (ja) * | 2005-09-29 | 2007-04-12 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| US7764087B2 (en) * | 2006-02-01 | 2010-07-27 | Wisconsin Alumni Research Foundation | Low swing domino logic circuits |

| US7332938B2 (en) * | 2006-06-23 | 2008-02-19 | The Curators Of The University Of Missouri | Domino logic testing systems and methods |

-

2007

- 2007-03-01 JP JP2007051170A patent/JP2008219232A/ja not_active Withdrawn

-

2008

- 2008-02-07 US US12/027,411 patent/US20080211556A1/en not_active Abandoned

- 2008-02-29 CN CNA2008100809379A patent/CN101256824A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20080211556A1 (en) | 2008-09-04 |

| CN101256824A (zh) | 2008-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6646938B2 (en) | Static memory having self-timing circuit | |

| US8077493B2 (en) | Semiconductor memory device | |

| US10354722B2 (en) | Semiconductor device | |

| US8116119B1 (en) | Desensitizing static random access memory (SRAM) to process variations | |

| JP2008219232A (ja) | 半導体集積回路 | |

| JP2008210443A (ja) | 半導体記憶装置 | |

| JP2008219232A5 (ja) | ||

| US10897248B2 (en) | Semiconductor device | |

| JP2008257833A (ja) | センス増幅回路およびセンス増幅方法 | |

| JP2008103028A (ja) | 半導体記憶装置 | |

| JP5099674B2 (ja) | 半導体集積回路 | |

| JP2009020959A (ja) | 半導体記憶装置 | |

| US8625370B2 (en) | Semiconductor integrated circuit | |

| US8817551B2 (en) | Semiconductor memory device | |

| US8854901B2 (en) | Read self timing circuitry for self-timed memory | |

| JP4598420B2 (ja) | 半導体記憶装置、及びタイミング制御方法 | |

| JPWO2015001722A1 (ja) | 半導体記憶装置 | |

| US8649231B2 (en) | Semiconductor memory device with delay circuit and sense amplifier circuit | |

| JP2007250092A (ja) | 半導体記憶装置 | |

| US20120127811A1 (en) | Timing generation circuit, semiconductor storage device and timing generation method | |

| JP2007066392A (ja) | 半導体記憶装置 | |

| JP5057744B2 (ja) | 半導体集積回路装置 | |

| JP4580784B2 (ja) | 半導体記憶装置及びそのデータ読み出し方法 | |

| US20090046494A1 (en) | Semiconductor memory device | |

| US20120038406A1 (en) | Delay circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100108 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100108 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20110311 |