JP2007300088A - 複数の金属層から形成される半導体素子パッケージリードフレーム - Google Patents

複数の金属層から形成される半導体素子パッケージリードフレーム Download PDFInfo

- Publication number

- JP2007300088A JP2007300088A JP2007104458A JP2007104458A JP2007300088A JP 2007300088 A JP2007300088 A JP 2007300088A JP 2007104458 A JP2007104458 A JP 2007104458A JP 2007104458 A JP2007104458 A JP 2007104458A JP 2007300088 A JP2007300088 A JP 2007300088A

- Authority

- JP

- Japan

- Prior art keywords

- metal layer

- lead frame

- package

- die

- lead

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16245—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

Landscapes

- Lead Frames For Integrated Circuits (AREA)

Abstract

【解決手段】半導体素子パッケージの使用のための、隆起した形体を有するリードフレームは、少なくとも二つの金属層450、452を接合することによって作製される。第一の金属層450が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定し得る。第一の金属層に接合された第二の金属層452が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定し得る。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。

【選択図】図3A

Description

本非仮出願は、すべての点で参照により本明細書に組み入れられる、2005年6月15日に出願された、米国特許仮出願第60/690,958号の優先権を主張する。

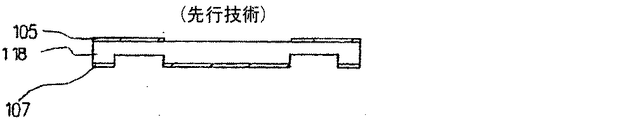

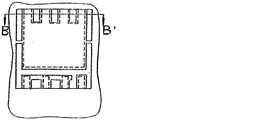

図1Aは、半導体素子を収容するために利用される従来のQFN(quad flat no-lead)パッケージの下面図を示す。図1Bは、PCボード上に配置された図1Aの従来のQFNパッケージをB-B'線から見た断面図を示す。

半導体素子パッケージのための、隆起した形体を有する本発明のリードフレームの態様は、少なくとも二つの金属層を接合することによって作製することができる。第一の金属層が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定する。第一の金属層に接合された第二の金属層が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定する。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。

リードフレームを画定する第一の金属層を設ける工程;

リードフレームの隆起した形体を画定する第二の金属層を設ける工程;および

該第一の金属層を該第二の金属層に接合する工程。

本発明(2)は、超音波溶接によって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(3)は、エポキシ樹脂によって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(4)は、はんだによって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(5)は、第二の金属層をパターン付けして、DPAK、D2PAK、TO-220、TO-247、SOT-223、TSSOP-x、SO-x、SSOP-x、TQFP、SE70-8、TSOP-8およびTSOP12からなる群より選択されるパワータイプパッケージのダイパッド上に隆起した形体を形成する、本発明(1)の方法である。

本発明(6)は、第二の金属層をパターン付けして、リードをプラスチックの本体内に固着するための段としての隆起した形体を形成する、本発明(1)の方法である。

本発明(7)は、第二の金属層をパターン付けして、パッケージ中の二つのダイを接続するトレースとしての隆起した形体を形成する、本発明(1)の方法である。

本発明(8)は、第二の金属層をパターン付けして、パッケージの周囲にダイ接点を接続分布させるトレースとしての隆起した形体を形成する、本発明(1)の方法である。

本発明(9)は、

リードフレームを画定する第一の金属層と、

該第一の金属層に接合され、該リードフレームの隆起した形体を画定する第二の金属層とを含む、

半導体素子パッケージのためのリードフレームである。

本発明(10)は、第二の金属層が第一の金属層に溶接されている、本発明(9)のリードフレームである。

本発明(11)は、第一の金属層と第二の金属層との間にエポキシ樹脂をさらに含む、本発明(9)のリードフレームである。

本発明(12)は、第一の金属層と第二の金属層との間にはんだをさらに含む、本発明(9)のリードフレームである。

本発明(13)は、隆起した形体が、リードをプラスチックのパッケージ本体内に固着する段を含む、本発明(9)のリードフレームである。

本発明(14)は、隆起した形体が、パッケージ中の二つのダイを接続する導電トレースを含む、本発明(9)のリードフレームである。

本発明(15)は、隆起した形体が、パッケージの周囲にダイ接点を分布させる導電トレースを含む、本発明(9)のリードフレームである。

本発明(16)は、リードフレーム上に支持されたダイを含み、該リードフレームが、第二の金属層に接合された第一の金属層を含み、該第二の金属層が、該リードフレームの隆起した形体を画定するものである半導体素子パッケージである。

本発明(17)は、第二の金属層が溶接、エポキシ樹脂またははんだによって第一の金属層に接合されている、本発明(16)のパッケージである。

本発明(18)は、隆起した形体が、リードをパッケージ本体内に固着する段、ダイを該パッケージ本体内の第二のダイと接続する導電トレース、または該パッケージ本体の周囲にダイ接点を分布させる導電トレースから選択される、本発明(16)のパッケージである。

半導体素子パッケージのための、隆起した形体を有する本発明の態様のリードフレームは、少なくとも二つの金属層を接合することによって作製することができる。第一の金属層が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定する。第一の金属層に接合された第二の金属層が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定する。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。

Claims (18)

- 以下の工程を含む、半導体素子パッケージのためのリードフレームを作製する方法:

リードフレームを画定する第一の金属層を設ける工程;

リードフレームの隆起した形体を画定する第二の金属層を設ける工程;および

該第一の金属層を該第二の金属層に接合する工程。 - 超音波溶接によって第一の金属層を第二の金属層に接合する、請求項1記載の方法。

- エポキシ樹脂によって第一の金属層を第二の金属層に接合する、請求項1記載の方法。

- はんだによって第一の金属層を第二の金属層に接合する、請求項1記載の方法。

- 第二の金属層をパターン付けして、DPAK、D2PAK、TO-220、TO-247、SOT-223、TSSOP-x、SO-x、SSOP-x、TQFP、SE70-8、TSOP-8およびTSOP12からなる群より選択されるパワータイプパッケージのダイパッド上に隆起した形体を形成する、請求項1記載の方法。

- 第二の金属層をパターン付けして、リードをプラスチックの本体内に固着するための段としての隆起した形体を形成する、請求項1記載の方法。

- 第二の金属層をパターン付けして、パッケージ中の二つのダイを接続するトレースとしての隆起した形体を形成する、請求項1記載の方法。

- 第二の金属層をパターン付けして、パッケージの周囲にダイ接点を接続分布させるトレースとしての隆起した形体を形成する、請求項1記載の方法。

- リードフレームを画定する第一の金属層と、

該第一の金属層に接合され、該リードフレームの隆起した形体を画定する第二の金属層とを含む、

半導体素子パッケージのためのリードフレーム。 - 第二の金属層が第一の金属層に溶接されている、請求項9記載のリードフレーム。

- 第一の金属層と第二の金属層との間にエポキシ樹脂をさらに含む、請求項9記載のリードフレーム。

- 第一の金属層と第二の金属層との間にはんだをさらに含む、請求項9記載のリードフレーム。

- 隆起した形体が、リードをプラスチックのパッケージ本体内に固着する段を含む、請求項9記載のリードフレーム。

- 隆起した形体が、パッケージ中の二つのダイを接続する導電トレースを含む、請求項9記載のリードフレーム。

- 隆起した形体が、パッケージの周囲にダイ接点を分布させる導電トレースを含む、請求項9記載のリードフレーム。

- リードフレーム上に支持されたダイを含み、該リードフレームが、第二の金属層に接合された第一の金属層を含み、該第二の金属層が、該リードフレームの隆起した形体を画定するものである半導体素子パッケージ。

- 第二の金属層が溶接、エポキシ樹脂またははんだによって第一の金属層に接合されている、請求項16記載のパッケージ。

- 隆起した形体が、リードをパッケージ本体内に固着する段、ダイを該パッケージ本体内の第二のダイと接続する導電トレース、または該パッケージ本体の周囲にダイ接点を分布させる導電トレースから選択される、請求項16記載のパッケージ。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/416,994 US20070130759A1 (en) | 2005-06-15 | 2006-05-02 | Semiconductor device package leadframe formed from multiple metal layers |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007300088A true JP2007300088A (ja) | 2007-11-15 |

| JP2007300088A5 JP2007300088A5 (ja) | 2011-06-23 |

Family

ID=38769289

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007104458A Pending JP2007300088A (ja) | 2006-05-02 | 2007-04-12 | 複数の金属層から形成される半導体素子パッケージリードフレーム |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2007300088A (ja) |

| CN (1) | CN101068005B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102117752A (zh) * | 2010-10-15 | 2011-07-06 | 日月光半导体制造股份有限公司 | 引脚框架封装结构及其制作方法 |

| US10847700B2 (en) | 2018-06-25 | 2020-11-24 | Nichia Corporation | Package, light emitting device, method of manufacturing package, and method of manufacturing light emitting device |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101521164B (zh) * | 2008-02-26 | 2011-01-05 | 上海凯虹科技电子有限公司 | 引线键合芯片级封装方法 |

| CN102915988A (zh) * | 2012-10-31 | 2013-02-06 | 矽力杰半导体技术(杭州)有限公司 | 一种引线框架以及应用其的倒装封装装置 |

| CN103928431B (zh) * | 2012-10-31 | 2017-03-01 | 矽力杰半导体技术(杭州)有限公司 | 一种倒装封装装置 |

| CN103594448A (zh) * | 2013-11-15 | 2014-02-19 | 杰群电子科技(东莞)有限公司 | 一种引线框架 |

| US11298775B2 (en) | 2018-05-24 | 2022-04-12 | Honda Motor Co., Ltd. | Continuous ultrasonic additive manufacturing |

| CN110524891A (zh) * | 2018-05-24 | 2019-12-03 | 本田技研工业株式会社 | 连续超声波增材制造 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2582013B2 (ja) * | 1991-02-08 | 1997-02-19 | 株式会社東芝 | 樹脂封止型半導体装置及びその製造方法 |

| JP3733114B2 (ja) * | 2000-07-25 | 2006-01-11 | 株式会社メヂアナ電子 | プラスチックパッケージベース及びエアキャビティ型パッケージ |

| JP2004281887A (ja) * | 2003-03-18 | 2004-10-07 | Himeji Toshiba Ep Corp | リードフレーム及びそれを用いた電子部品 |

-

2007

- 2007-04-09 CN CN 200710090879 patent/CN101068005B/zh active Active

- 2007-04-12 JP JP2007104458A patent/JP2007300088A/ja active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102117752A (zh) * | 2010-10-15 | 2011-07-06 | 日月光半导体制造股份有限公司 | 引脚框架封装结构及其制作方法 |

| US10847700B2 (en) | 2018-06-25 | 2020-11-24 | Nichia Corporation | Package, light emitting device, method of manufacturing package, and method of manufacturing light emitting device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101068005A (zh) | 2007-11-07 |

| CN101068005B (zh) | 2010-12-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6720207B2 (en) | Leadframe, resin-molded semiconductor device including the leadframe, method of making the leadframe and method for manufacturing the device | |

| US9824949B2 (en) | Packaging solutions for devices and systems comprising lateral GaN power transistors | |

| US20070130759A1 (en) | Semiconductor device package leadframe formed from multiple metal layers | |

| US9087827B2 (en) | Mixed wire semiconductor lead frame package | |

| US6667541B1 (en) | Terminal land frame and method for manufacturing the same | |

| TWI281238B (en) | Thermal enhanced package for block mold assembly | |

| US8222716B2 (en) | Multiple leadframe package | |

| KR101019369B1 (ko) | 리드프레임, 수지봉입형 반도체장치 및 그 제조방법 | |

| TWI453838B (zh) | 具有散熱器之無引線封裝 | |

| JP2007300088A (ja) | 複数の金属層から形成される半導体素子パッケージリードフレーム | |

| US20080299705A1 (en) | Chip Scale Package Having Flip Chip Interconnect on Die Paddle | |

| US20140071650A1 (en) | Wireless module with active devices | |

| DE112006001663T5 (de) | Halbleiterchip-Gehäuse und Verfahren zur Herstellung desselben | |

| TW200818458A (en) | Stackable packages for three-dimensional packaging of semiconductor dice | |

| JP2009094118A (ja) | リードフレーム、それを備える電子部品及びその製造方法 | |

| US8106491B2 (en) | Methods of forming stacked semiconductor devices with a leadframe and associated assemblies | |

| CN115605991A (zh) | 包含具有暴露背侧金属的下安装式裸片的半导体封装 | |

| JP3460646B2 (ja) | 樹脂封止型半導体装置およびその製造方法 | |

| JP2007287762A (ja) | 半導体集積回路素子とその製造方法および半導体装置 | |

| US8785253B2 (en) | Leadframe for IC package and method of manufacture | |

| JP2010050288A (ja) | 樹脂封止型半導体装置およびその製造方法 | |

| JP2006279088A (ja) | 半導体装置の製造方法 | |

| JP3699966B2 (ja) | リードフレーム,樹脂封止型半導体装置及びその製造方法 | |

| JP3965813B2 (ja) | ターミナルランドフレームの製造方法 | |

| JP2006032871A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071219 |

|

| A621 | Written request for application examination |

Effective date: 20100408 Free format text: JAPANESE INTERMEDIATE CODE: A621 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110401 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110511 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120416 |

|

| A131 | Notification of reasons for refusal |

Effective date: 20120620 Free format text: JAPANESE INTERMEDIATE CODE: A131 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120919 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130530 |