JP2006332694A - 半導体表面上に金属バンプを形成する方法 - Google Patents

半導体表面上に金属バンプを形成する方法 Download PDFInfo

- Publication number

- JP2006332694A JP2006332694A JP2006200592A JP2006200592A JP2006332694A JP 2006332694 A JP2006332694 A JP 2006332694A JP 2006200592 A JP2006200592 A JP 2006200592A JP 2006200592 A JP2006200592 A JP 2006200592A JP 2006332694 A JP2006332694 A JP 2006332694A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- metal

- pillar

- solder

- depositing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/11—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/1147—Manufacturing methods using a lift-off mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/119—Methods of manufacturing bump connectors involving a specific sequence of method steps

- H01L2224/11901—Methods of manufacturing bump connectors involving a specific sequence of method steps with repetition of the same manufacturing step

- H01L2224/11902—Multiple masking steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【解決手段】 パシベーション層中に作製された導体パッドに対する開口を含んだパシベーション層上にバリヤー層を付着させる。導体パッドと整列していて、導体パッドの表面にほぼ等しい直径を有していて、バリヤー層をオーバーレイする3つの金属層のカラムを形成させる。カラムを構成する3つの金属層は、バリヤー層と接触している層から始まって、ピラー金属層、アンダーバンプ金属層、およびはんだ金属層をこの順序にて含む。ピラー金属層の直径を減少させ、パシベーション層の表面からバリヤー層を選択的に除去し、その後にはんだ金属のリフロー処理を行って、本発明のはんだバンプを完成させる。

【選択図】 図1

Description

本発明は集積回路素子の製造に関し、さらに詳細には、信頼性の高い微細ピッチのはんだバンプを低コストで作製する方法に関する。

半導体素子の実装については、長年にわたって、半導体素子の機能サイズのさらなる減少(素子性能の向上と素子製造コストの減少という二重の要件によって促される)に重点が置かれている。こうした傾向に基づいて半導体素子密度の大幅な増大がもたらされており、素子またはパッケージのI/O能力に益々重点が置かれるようになっている。従って、集積回路と他の回路もしくはシステム部品とを接続する金属接続物がより一層重要になってきており、半導体素子のさらなる小型化と相俟って、回路の性能に対して益々好ましくない影響を及ぼすようになっている。金属相互接続物の寄生容量と抵抗が増大すると、チップの性能が大幅に低下することがある。この点に関して最も重要なのは、電源バス(power bus)もしくは接地バス(ground bus)に沿っての電圧低下、および臨界信号路(critical signal paths)のRC遅延である。より幅広の金属線を使用することによって抵抗を少なくしようとすると、これら金属線の容量がより高くなる。

Farnworthらによる米国特許第5,756,370号は、試験用半導体ダイとの一時的な接続を形成させるための規格適合の接点システム、および柔軟な接点システムを製造するための方法を開示している。

Linによる米国特許第6,103,552号は、はんだバンプの形成を含むウエハー・スケールの実装を達成するための方法とパッケージを開示している。

本発明の主要な目的は、微細ピッチのはんだバンプを作製する方法を提供することにある。

本発明のさらに他の目的は、はんだバンプの高さを増大させることによる、高信頼性の微細ピッチのはんだバンプを作製するための原価効率の良い方法を提供することにある。この目的は、はんだバンプの信頼性が、はんだボールと下側に存在する基板との間の距離の2乗に比例して向上する、という考え方に基づいている。

本発明のさらに他の目的は、はんだバンプ作製プロセスが完了した後のフラックスの清浄操作が容易なはんだバンプ作製法を提供することにある。

本発明の方法によれば、半導体表面上に導体パッドを形成し、これに誘電体の層がオーバーレイしている。導体パッドを保護するために、誘電体層を覆うようにパシベーション層を付着させ、導体パッドの表面を部分的に露出させる開口をパシベーション層中に作製する。パシベーション層中に作製した開口を含めて、パシベーション層を覆うようにバリヤー層を付着させる。バリヤー層をオーバーレイしていて、導体パッドと整列していて、導体パッドの表面にほぼ等しい直径を有する3つの金属層のカラムを形成する。これら3つの金属層は連続していて、バリヤー層と接触している層から始めて、ピラー金属の層、アンダーバンプ金属の層、およびはんだ金属の層で構成されている。ピラー金属層の直径を減少させ、はんだ金属のリフローにより本発明のはんだバンプの形成が完了した後に、パシベーション層の表面からバリヤー層を選択的に除去する。

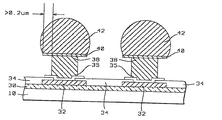

図5を参照すると、第1のプロフィールを有する本発明の完成はんだバンプの断面が示されている。“プロフィール”とは、はんだバンプ作製における最終工程のうちの一工程時に、バリヤー金属の層がエッチングされるときの違いを表わしている。

−10、その上にはんだバンプが作製される半導体表面であって、一般にはシリコン半導体基板の表面である;

−30、半導体表面10を覆うように付着させた誘電体層;

−32、誘電体層30の表面上に作製された導体パッド;

−34、誘電体層30の表面を覆うように付着させた、パターン焼き付けされたパシベーション層; パシベーション層34に開口が造られていて、導体パッド32の表面を部分的に露出させている;

−36、等方的にエッチングされたバリヤー金属層; このバリヤー金属層は等方的にエッチングされているので、バリヤー金属は、パシベーション層34の表面から完全に除去されている(但し、オーバーレイしているはんだバンプのピラー金属(38)によってバリヤー金属が被覆されている場合は除く);

−38、はんだバンプのピラー金属;

−40、はんだバンプのピラー金属38をオーバーレイするように作製されたアンダーバンプ金属の層;

−40、はんだ金属。

図7は、基板10の表面上部分の断面を示している。以下にエレメントについて記載する:

−10、シリコン基板であり、その表面上に金属導体パッド32が作製されている;

−30、基板10の表面を覆うように付着させた誘電体層;

−32、金属導体パッド、一般にはアルミニウムを含み、誘電体層30の表面上に作製される;

−34、誘電体層30の表面を覆うように付着させたパシベーション層であり、金属導体パッド32と整列していて、導体パッド32の表面を部分的に露出させている開口がパシベーション層34に作製されている;

−36、パシベーション層34の表面を覆うように作製されたバリヤー金属層であって、パシベーション層34に作製されている開口を含み、下側に存在する導体パッド32と接触している。

層40はニッケルを含むのが好ましく、約1〜10μmの厚さに施すのが好ましく、約4μmの厚さに施すのがさらに好ましい。

・本発明の準備にあたって、半導体表面を供給し、半導体表面上に誘電体層を付着させ、誘電体層上に導体パッドを供給し、導体パッドが露出表面を有し、前記導体パッドの表面を含めた半導体表面上にパシベーション層を付着させ、パシベーション層に対しパターン焼き付けとエッチングを施し、これによりパシベーション層中に開口を作製し、導体パッドの表面を部分的に露出させ、パシベーション層中の開口を導体パッドに関して中心に配置する。

・バリヤー層の表面上にフォトレジスト層を付着させる。

・パターン焼き付けされたフォトレジスト層をバリヤー層の表面から除去する。

・等方性エッチングまたは異方性エッチングを使用してバリヤー層をエッチングする。

・はんだ金属をリフローする。

・信頼性を高める上でボールの高さが極めて重要なポイントである。パッケージのオーバーレイ層間の熱的不整合を防止するために(たとえば、半導体素子と下側に存在するプリント回路基板など)、オーバーレイしているエレメント間の距離を増大させることが重要である。本発明では、こうしたことが達成される。

・高さを与えることなく小さなはんだボールが使用される場合、小さな隙間をアンダーフィルするのが極めて困難である。

・アンダーバンプ金属層のために使用される金属は、はんだリフロー時にオーバーレイしているはんだに対して良好な接着性を有していなければならないが、あまりにも早く溶解してはならず、また早く溶解した場合にははんだに対するバリヤーを形成しなければならない、という点において重要である。さらに、UBM金属は、空気にさらされると保護酸化物層を形成することがあり、従ってリフロープロセス時において、UBM金属の周りでのピラー金属に対するはんだウェッティングが妨げられる。従ってUBM金属にはニッケルが好ましい。

Claims (46)

- 半導体表面上に金属バンプを形成するための方法であって、

半導体表面を供給する工程;

導体パッドに対する開口を設けたパシベーション層をその上に有する、前記半導体表面を覆う導体パッドを供給する工程、このときパシベーション層の表面を覆うように、および前記開口中にバリヤー層が付着されている;

フォトレジスト層を、前記バリヤー層を覆うように付着させる工程;

前記フォトレジスト中に、導体パッドと整列したピラー開口を形成する工程;

前記ピラー開口中にピラー金属の層を付着させる工程;

アンダーバンプ金属の層を、前記ピラー金属を覆うように付着させる工程;

はんだ金属の層を、前記アンダーバンプ金属を覆うように付着させる工程;

フォトレジスト層を除去する工程;

ピラー金属層の直径を減少させる工程;

バリヤー層をエッチングする工程; および

はんだ金属をリフローして前記金属バンプを形成する工程;

を含む前記方法。 - 前記バリヤー層が、約500〜2000オングストロームの厚さに、さらに好ましくは約1000オングストロームの厚さに施されたチタンを含む、請求項1記載の方法。

- 前記フォトレジスト層が、約100〜200μmの厚さに、さらに好ましくは約150μmの厚さに施される、請求項1記載の方法。

- 前記ピラー金属層が、約10〜100μmの厚さに、さらに好ましくは約50μmの厚さに施された銅を含む、請求項1記載の方法。

- 前記アンダーバンプ金属層が、約1〜10μmの厚さに、さらに好ましくは約4μmの厚さに施されたニッケルを含む、請求項1記載の方法。

- 前記はんだ金属層が、約30〜100μmの厚さに、さらに好ましくは約50μmの厚さに施されたはんだを含む、請求項1記載の方法。

- 半導体表面;

前記半導体表面を覆う誘電体層;

第1の材料で造られた、前記誘電体層を覆う導体パッド;

前記導体パッドと整列した開口を有する、前記誘電体層を覆うパシベーション層;

前記パシベーション層中に造られた前記開口を含む、前記誘電体層を覆うように付着させたバリヤー層; および

導体パッドと整列していて、導体パッドの表面エリアにほぼ等しい直径を有していて、バリヤー層と接触しているある層からはじまっている、ピラー金属層、アンダーバンプ金属層、およびはんだ金属層の3つの金属層で構成されるスタック;

を含み、このとき

前記ピラー金属の直径が適度の量だけ減少されており;

前記バリヤー層が、等方性エッチング法または異方性エッチング法を使用して除去されており; そして

前記はんだ金属がリフローされている;

金属バンプ接点。 - 前記バリヤー層が、約500〜2000オングストロームの厚さに、さらに好ましくは約1000オングストロームの厚さに施されたチタンまたは銅を含む、請求項7記載の金属バンプ接点。

- 前記フォトレジスト層が、約100〜200μmの厚さに、さらに好ましくは約150μmの厚さに施される、請求項7記載の金属バンプ接点。

- 前記ピラー金属層が、約10〜100μmの厚さに、さらに好ましくは約50μmの厚さに施された銅を含む、請求項7記載の金属バンプ接点。

- 前記アンダーバンプ金属層が、約1〜10μmの厚さに、さらに好ましくは約4μmの厚さに施されたニッケルを含む、請求項7記載の金属バンプ接点。

- 前記はんだ金属層が、約30〜100μmの厚さに、さらに好ましくは約50μmの厚さに施されたはんだを含む、請求項7記載の金属バンプ接点。

- 半導体表面を供給し、導体パッドに対する開口を設けたパシベーション層をその上に有する、前記半導体表面を覆う導体パッドを供給する工程;

前記パシベーション層中に造られた開口を含んだバリヤー材料層を、前記パシベーション層の表面を覆うように付着させる工程;

金属の付着を妨げる材料の層を、バリヤー層の表面を覆うように付着させる工程;

金属の付着を妨げる材料の層をパターン焼き付け及びエッチングし、金属の付着を妨げる材料層中に、導体パッドと整列していて、導体パッドの表面エリアにほぼ等しい直径を有する開口を造る工程;

導体パッドと整列している表面エリア上のバリヤー層表面を部分的に露出させる工程;

ピラー金属の層を、バリヤー層の露出表面を覆うように付着させる工程;

アンダーバンプメタラージ(UBM)の層を、ピラー金属層の表面を覆うように付着させる工程;

バンプ金属の層を、UBM層の表面を覆うように付着させる工程;

金属の付着を妨げる材料の層をバリヤー層の表面上から取り除く工程;

ピラー金属の層をエッチングし、ピラー材料の直径を適度の量だけ減少させる工程;

等方性エッチング法または異方性エッチング法を使用して、前記パシベーション層の表面から前記バリヤー層を除去する工程; および

前記はんだ金属をリフローして金属バンプを形成する工程;

を含む、半導体表面上に金属バンプを形成する方法。 - 前記バリヤー層が、約500〜2000オングストロームの厚さに、さらに好ましくは約1000オングストロームの厚さに施されたチタンまたは銅を含む、請求項13記載の方法。

- 前記フォトレジスト層が、約100〜200μmの厚さに、さらに好ましくは約150μmの厚さに施される、請求項13記載の方法。

- 前記ピラー金属層が、約10〜100μmの厚さに、さらに好ましくは約50μmの厚さに施された銅を含む、請求項13記載の方法。

- 前記アンダーバンプ金属層が、約1〜10μmの厚さに、さらに好ましくは約4μmの厚さに施されたニッケルを含む、請求項13記載の方法。

- 前記はんだ金属層が、約30〜100μmの厚さに、さらに好ましくは約50μmの厚さに施されたはんだを含む、請求項13記載の方法。

- バリヤー層の露出表面に対してその場でのスパッタクリーンを行う工程をさらに含み、このとき前記追加工程は、前記ピラー金属層を付着させる工程の前に行う、請求項13記載の方法。

- 金属の付着を妨げる前記材料がフォトレジストを含む、請求項13記載の方法。

- 半導体表面上に金属バンプを形成するための方法であって、

表面もしくは表面上に導体パッドが設けられている半導体表面を供給する工程、このとき前記導体パッドは、下側に存在する誘電体層上に位置しており、前記支持体の表面もしくは表面上における電気接点の少なくとも1個所と電気的に接触している;

表面層としてのバリヤー層を有する、前記金属パンプのためのベース層を供給する工程;

ピラー金属層、アンダーバンプ金属層、およびはんだ金属層の3つの連続した層を含む、前記金属パンプのためのカラムを供給する工程; および

前記金属バンプを供給する工程;

を含む前記方法。 - 金属バンプのためのベース層を供給する前記工程が、

前記導体パッドの表面を含めて、導体パッドの下側に存在する前記誘電体層の表面を覆うようにパシベーション層を付着させる工程;

前記パシベーション層をパターン焼き付け及びエッチングし、前記パシベーション層に開口を作製し、そして前記導体パッドの表面を部分的に露出させる工程、このとき前記パシベーション層において作製された前記開口は、前記導体パッドの表面エリアより適度の量だけ小さい; および

前記パシベーション層において作製された開口を含めて、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させる工程;

を含む、請求項21記載の方法。 - 前記金属バンプのためのカラムを供給する前記工程が、

金属の付着を妨げる材料の層を、バリヤー層の表面を覆うように付着させる工程;

金属の付着を妨げる材料の層をパターン焼き付け及びエッチングし、導体パッドと整列していて、導体パッドの表面にほぼ等しい直径を有する開口を、金属の付着を妨げる材料の層において作製し、そして導体パッドと整列している表面エリア上のバリヤー層の表面を部分的に露出させる工程;

ピラー金属の層を、バリヤー層の露出表面を覆うように付着させる工程;

アンダーバンプメタラージ(UBM)の層を、ピラー金属層の表面を覆うように付着させる工程;

バンプ金属の層を、UBM層の表面を覆うように付着させる工程;

金属の付着を妨げる材料の層をバリヤー層の表面上から取り除く工程;

ピラー金属層をエッチングし、ピラー金属の直径を適度の量だけ減少させる工程;および

等方性エッチング法または異方性エッチング法を使用して、前記パシベーション層の表面から前記バリヤー層を取り除く工程;

を含む、請求項21記載の方法。 - 金属バンプを供給する前記工程が、前記はんだ金属をリフローして金属バンプを形成する工程を含む、請求項21記載の方法。

- 前記バリヤー層が、約500〜2000オングストロームの厚さに、さらに好ましくは約1000オングストロームの厚さに施されたチタンまたは銅を含む、請求項21記載の方法。

- 前記フォトレジスト層が、約100〜200μmの厚さに、さらに好ましくは約150μmの厚さに施される、請求項21記載の方法。

- 前記ピラー金属層が、約10〜100μmの厚さに、さらに好ましくは約50μmの厚さに施された銅を含む、請求項21記載の方法。

- 前記アンダーバンプ金属層が、約1〜10μmの厚さに、さらに好ましくは約4μmの厚さに施されたニッケルを含む、請求項21記載の方法。

- 前記はんだ金属層が、約30〜100μmの厚さに、さらに好ましくは約50μmの厚さに施されたはんだを含む、請求項21記載の方法。

- 前記半導体表面が、半導体基板、プリント回路基板、フレックス回路、金属化基板、ガラス基板、および半導体素子実装支持体からなる表面群から選択される、請求項21記載の方法。

- 前記半導体基板が、半導体基板、セラミック基板、ガラス基板、ガリウムヒ素基板、シリコン・オン・インシュレータ(SOI)基板、シリコン・オン・サファイア(SOS)基板からなる基板群から選択される、請求項30記載の方法。

- 前記導体パッドが、アルミニウム、銅、またはこれらの化合物を含む、請求項21記載の方法。

- バリヤー層の露出表面に対してその場でのスパッタクリーンを行う工程をさらに含み、このとき前記追加工程は、前記ピラー金属層を付着させる工程の前に行う、請求項23記載の方法。

- 金属の付着を妨げる前記材料がフォトレジストを含む、請求項23記載の方法。

- ピラー金属層の直径を減少させる前記工程が、直径を0.2μmより多く減少させることを含む、請求項1記載の方法。

- 前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして前記金属バンプを形成する工程の前に行う、請求項1記載の方法。

- 前記ピラー金属の直径が適度の量だけ減少されている、すなわち0.2μmより多く減少されている、請求項7記載の金属バンプ接点。

- 前記はんだ金属をリフローする前に、前記アンダーバンプ金属と前記ピラー金属が酸化されている、請求項7記載の金属バンプ接点。

- ピラー金属の直径を適度な量だけ減少させる前記工程が、直径を0.2μmより多く減少させることを含む、請求項13記載の方法。

- 前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして金属バンプを形成する工程の前に行う、請求項13記載の方法。

- ピラー金属の直径を適度の量だけ減少させる前記工程が、直径を0.2μmより多く減少させることを含む、請求項23記載の方法。

- 前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして金属バンプを形成する工程の前に行う、請求項24記載の方法。

- 前記バリヤー層を覆うようにシード層を付着させることに関して、前記パシベーション層の表面を覆うように及び開口中に前記バリヤー層を付着させた後に前記シード層を付着させる、請求項1記載の方法。

- 前記バリヤー層を覆うようにシード層を付着させた、請求項7記載の金属バンプ接点。

- 前記バリヤー層の表面を覆うようにシード層を付着させることに関して、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させた後に前記シード層を付着させる、請求項13記載の方法。

- 前記バリヤー層の表面を覆うようにシード層を付着させるという追加工程に関して、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させた後に前記シード層を付着させる、請求項22記載の方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006200592A JP2006332694A (ja) | 2006-07-24 | 2006-07-24 | 半導体表面上に金属バンプを形成する方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006200592A JP2006332694A (ja) | 2006-07-24 | 2006-07-24 | 半導体表面上に金属バンプを形成する方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002056997A Division JP2003258014A (ja) | 2002-03-04 | 2002-03-04 | 半導体表面上に金属バンプを形成する方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006332694A true JP2006332694A (ja) | 2006-12-07 |

| JP2006332694A5 JP2006332694A5 (ja) | 2008-11-27 |

Family

ID=37553969

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006200592A Pending JP2006332694A (ja) | 2006-07-24 | 2006-07-24 | 半導体表面上に金属バンプを形成する方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006332694A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015018958A (ja) * | 2013-07-11 | 2015-01-29 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 実装構造体および実装構造体製造方法 |

| JP2015216344A (ja) * | 2014-04-21 | 2015-12-03 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| KR20160102150A (ko) | 2013-12-27 | 2016-08-29 | 미쓰비시 마테리알 가부시키가이샤 | 유심 구조 땜납 범프 및 그 제조 방법 |

| JP2017183592A (ja) * | 2016-03-31 | 2017-10-05 | 株式会社荏原製作所 | 基板の製造方法及び基板 |

| CN118173454A (zh) * | 2024-05-14 | 2024-06-11 | 日月新半导体(威海)有限公司 | 一种3d半导体封装及其制造方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05335313A (ja) * | 1992-05-29 | 1993-12-17 | Toshiba Corp | インジウムバンプの製造方法 |

| JPH0637093A (ja) * | 1992-07-14 | 1994-02-10 | Sanken Electric Co Ltd | バンプ電極の形成方法 |

| JPH11163019A (ja) * | 1997-12-01 | 1999-06-18 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| JP2001093928A (ja) * | 1999-09-22 | 2001-04-06 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2001257210A (ja) * | 2000-03-10 | 2001-09-21 | Hitachi Ltd | 半導体集積回路装置 |

-

2006

- 2006-07-24 JP JP2006200592A patent/JP2006332694A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05335313A (ja) * | 1992-05-29 | 1993-12-17 | Toshiba Corp | インジウムバンプの製造方法 |

| JPH0637093A (ja) * | 1992-07-14 | 1994-02-10 | Sanken Electric Co Ltd | バンプ電極の形成方法 |

| JPH11163019A (ja) * | 1997-12-01 | 1999-06-18 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| JP2001093928A (ja) * | 1999-09-22 | 2001-04-06 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2001257210A (ja) * | 2000-03-10 | 2001-09-21 | Hitachi Ltd | 半導体集積回路装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015018958A (ja) * | 2013-07-11 | 2015-01-29 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 実装構造体および実装構造体製造方法 |

| KR20160102150A (ko) | 2013-12-27 | 2016-08-29 | 미쓰비시 마테리알 가부시키가이샤 | 유심 구조 땜납 범프 및 그 제조 방법 |

| JP2015216344A (ja) * | 2014-04-21 | 2015-12-03 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP2017183592A (ja) * | 2016-03-31 | 2017-10-05 | 株式会社荏原製作所 | 基板の製造方法及び基板 |

| CN118173454A (zh) * | 2024-05-14 | 2024-06-11 | 日月新半导体(威海)有限公司 | 一种3d半导体封装及其制造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6818545B2 (en) | Low fabrication cost, fine pitch and high reliability solder bump | |

| US6426556B1 (en) | Reliable metal bumps on top of I/O pads with test probe marks | |

| US8158508B2 (en) | Structure and manufacturing method of a chip scale package | |

| US20080050909A1 (en) | Top layers of metal for high performance IC's | |

| US6586323B1 (en) | Method for dual-layer polyimide processing on bumping technology | |

| US6426281B1 (en) | Method to form bump in bumping technology | |

| US6605524B1 (en) | Bumping process to increase bump height and to create a more robust bump structure | |

| US6756294B1 (en) | Method for improving bump reliability for flip chip devices | |

| US6642136B1 (en) | Method of making a low fabrication cost, high performance, high reliability chip scale package | |

| US8481418B2 (en) | Low fabrication cost, high performance, high reliability chip scale package | |

| US7456090B2 (en) | Method to reduce UBM undercut | |

| JP2007502530A (ja) | 歪み解放バンプ設計による半導体装置 | |

| US9269678B2 (en) | Bond pad structure and method of manufacturing the same | |

| JP2006332694A (ja) | 半導体表面上に金属バンプを形成する方法 | |

| US6479376B1 (en) | Process improvement for the creation of aluminum contact bumps | |

| JP2003258014A (ja) | 半導体表面上に金属バンプを形成する方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060823 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060823 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081008 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090304 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090309 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090406 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091030 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100301 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100804 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100826 |

|

| A912 | Removal of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20101203 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110422 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110427 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110530 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110602 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20111118 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20111125 |