JP2006216632A - Soiウエハの製造方法 - Google Patents

Soiウエハの製造方法 Download PDFInfo

- Publication number

- JP2006216632A JP2006216632A JP2005025868A JP2005025868A JP2006216632A JP 2006216632 A JP2006216632 A JP 2006216632A JP 2005025868 A JP2005025868 A JP 2005025868A JP 2005025868 A JP2005025868 A JP 2005025868A JP 2006216632 A JP2006216632 A JP 2006216632A

- Authority

- JP

- Japan

- Prior art keywords

- soi wafer

- gas

- silicon epitaxial

- epitaxial layer

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Landscapes

- Recrystallisation Techniques (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

Abstract

【解決手段】シリコン基板表面に開口部を有する絶縁層を形成する絶縁層形成工程と、シリコンエピタキシャル層を形成する第一成膜工程と、前記シリコンエピタキシャル層の端部を、上に開いた傾斜角の形状にするための気相エッチング工程と、前記シリコンエピタキシャル層を相互接触させて全面に成膜する第二成膜工程と、前記全面成膜されたシリコンエピタキシャル層を表面研磨して平坦化する平坦化工程とを含むSOIウエハの製造方法とする。

【選択図】 図1−4

Description

シリコン基板に多数のトレンチ(溝)を形成し、そのトレンチ内にシリコン基板と異なる導電型のシリコン単結晶をエピタキシャル成長させて前記トレンチを埋め込む方法が公開されている。その方法によれば、エピタキシャル成長層の界面に発生し易い結晶欠陥を抑える方法として、シリコンのエッチングガスとエピタキシャル成長させるためのジクロロシランガスとを同時に流しながらエピタキシャル成長を行う方法、およびジクロロシランガスとエッチングガスを交互に供給して成長を行う方法等が示されている(特許文献3)。

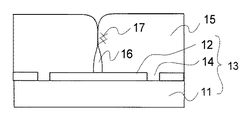

前記ボイド16については、エピタキシャル層15の上部成長速度が酸化膜12に近い下部より速い場合、成長と共にオーバーハング形状が著しくなり、その状態で隣接するエピタキシャル層が相互に接触することにより、閉じ込められた下部空間がボイド16となる。このオーバーハングの度合いは、前述のように成長層15の上下における成長速度の差に依存し、隣接する成長層との隙間および成膜ガスの付着確率によって決まる。成長速度の差は、一般に、隙間が小さくなるほど、また、付着確率が高くなるほど大きくなる。従って、隣接する成長層が相互に接触してから全面成膜されるような場合に、前記オーバーハング形状が著しくなり易く、その結果、巻き込まれたボイドなどが問題にされやすいのである。

本発明は、以上述べた問題点に鑑みてなされたものであり、その目的は、シリコンエピタキシャル成長層における、表面ラフネスの解消と上下層の成長速度差に基づいて形成されるオーバーハング形状の解消とを図ることにより、SOIウエハ製造工程において問題となっていたボイドや結晶欠陥の発生を抑えることのできるSOIウエハの製造方法を提供することである。これにより、SOIウエハを用いた高性能デバイスの製造が可能になる。

特許請求の範囲の請求項2記載の本発明によれば、前記開口部が島状または格子状である特許請求の範囲の請求項1のSOIウエハの製造方法とすることが好ましい。

特許請求の範囲の請求項4記載の本発明によれば、前記気相エッチング工程で、隣接するシリコンエピタキシャル層の端部を上に開いた傾斜角の形状にするために成膜ガスとエッチングガスとを同時に流す特許請求の範囲の請求項1記載のSOIウエハの製造方法とすることが好ましい。

特許請求の範囲の請求項5記載の本発明によれば、前記気相エッチング工程における成膜ガス流量を徐々に減らし、気相エッチングガスの流量を徐々に増加させるように制御する特許請求の範囲の請求項4記載のSOIウエハの製造方法とすることが好ましい。

特許請求の範囲の請求項7記載の本発明によれば、気相エッチングガスがHClガスを含む請求項1乃至6のいずれか一項に記載のSOIウエハの製造方法とすることが好ましい。

特許請求の範囲の請求項8記載の本発明によれば、前記シリコンエピタキシャル層の全面成膜後、SOIウエハを平坦化する工程の前後で、水素を含んだ1000℃以上のガス雰囲気中でアニールする工程を設ける特許請求の範囲の請求項1乃至5のいずれか一項に記載のSOIウエハの製造方法とすることが好ましい。

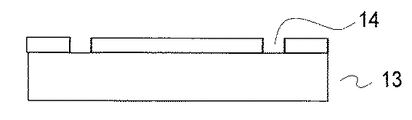

さらに、エピタキシャル層が全面に形成された後、シリコンエピタキシャル層表面を平坦化する工程の前後に、界面に存在するなお存在する結晶欠陥を消滅させるために、水素を含んだガス雰囲気中で高温アニールを行うことも望ましい。

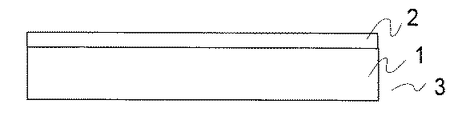

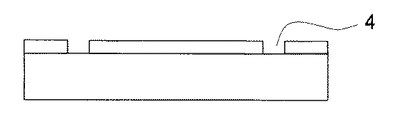

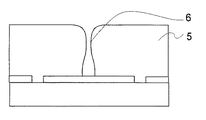

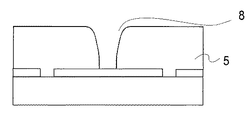

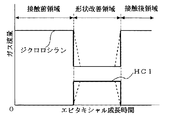

図1−1乃至図1−6は本発明のSOIウエハの製造方法にかかる製造工程をウエハの断面図により示したものである。図2は、本発明のSOIウエハの製造方法にかかる第二の実施例にかかるガスの流量プロファイル図である。

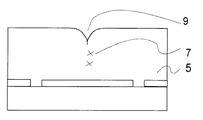

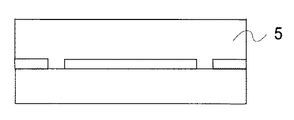

図面では、開口部の平面パターンを示していないが、ウエハ3全体としては、チップ化できるような周期的な構造であれば、一チップ内のパターンは溝、格子状あるいは小円あるいは正方形のドット状の何れでも良い。次に、開口部4を形成したウエハ3を図示しないエピタキシャル成長装置に搬入し、ウエハ3の酸化膜2側の表面にシリコンエピタキシャル層5を形成する。シリコンエピタキシャル層5を形成するための代表的なプロセスガスは、主ガスをジクロロシランあるいはトリクロロシランとし、水素ガスをキャリアガスとして用い、必要に応じて、ドーピングガスを添加したものを用いる。反応圧力を100〜760Torr(1Torr=133.3Pa)とし、ウエハ温度1000℃程度としてシリコンエピタキシャル層5を開口部4内のシリコン基板1面から成長させる。シリコンエピタキシャル層5の成長が、ウエハ面内の一チップパターン内に島状に配置された開口部4内において縦方向に始まり、開口部4を超えると、酸化膜2の面方向すなわち横方向にも成長する。隣接するシリコンエピタキシャル層5相互間の距離が接近して接触する前に主ガスの導入を停止する(図1−3)。

前記エッチングガス(HCl)導入を停止し、再度、前記主ガスを導入してシリコンエピタキシャル成長させることによりボイドレスなシリコンエピタキシャル層が全面に形成される(図1−5)。但し、前記HClによる1回の気相エッチング工程で、オーバーハングを解消するには不十分な場合は、前記気相エッチング工程とシリコンエピタキシャル成長工程を交互に複数回繰り返すことによりオーバーハングの解消された良好な膜が形成される。

複数の島状シリコンエピタキシャル層が接近した時点でジクロロシランの流量を減らし、エッチングガス(HCl)を新たに導入してシリコンエピタキシャル層の端部形状を改善する−気相エッチング工程(図2の形状改善領域)。

両層が接触した後は、HClエッチングガスの導入を停止し、再度ジクロロシランの流量を前記第一成膜工程と同程度に増やして高成長レートで全面に渡ってエピタキシャル層を成長させる。その後、前述の第一の実施例と同様の表面平坦化処理および必要に応じて高温水素アニール処理工程を行うことによりSOIウエハ製造工程が完了する。以上の説明では、第一成膜工程および第二成膜工程において、エッチングガスを導入しない場合について示したが、第一成膜工程および第二成膜工程においてエッチングガスを導入しても、もちろんかまわない。

2…シリコン酸化膜、

3…シリコンウエハ、

4…開口部、

5…シリコンエピタキシャル成長層、

6…オーバーハング

7…結晶欠陥

8…傾斜角形状、台形形状(テーパー形状)

9…凹部

16…結晶欠陥

17…ボイド。

Claims (8)

- シリコン基板表面に開口部を有する絶縁層を形成する絶縁層形成工程と、前記開口部に露出する前記シリコン基板表面からシリコンエピタキシャル層を形成する第一成膜工程と、前記シリコンエピタキシャル層が前記酸化膜上で相互に接触する前の段階における前記シリコンエピタキシャル層の端部を、上に開いた傾斜角の形状にするための気相エッチング工程と、前記シリコンエピタキシャル層を相互接触させて前記シリコン基板上の全面に成膜する第二成膜工程と、前記全面成膜されたシリコンエピタキシャル層を表面研磨して平坦化する平坦化工程とを含むことを特徴とするSOIウエハの製造方法。

- 前記開口部が島状または格子状であることを特徴とする請求項1記載のSOIウエハの製造方法。

- 前記第一成膜工程と前記気相エッチング工程が複数回行われることを特徴とする請求項1または2記載のSOIウエハの製造方法。

- 前記気相エッチング工程で、隣接するシリコンエピタキシャル層の端部を上に開いた傾斜角の形状にするために成膜ガスとエッチングガスとを同時に流すことを特徴とする請求項1記載のSOIウエハの製造方法。

- 前記気相エッチング工程における成膜ガス流量を徐々に減らし、気相エッチングガスの流量を徐々に増加させるように制御することを特徴とする請求項4記載のSOIウエハの製造方法。

- 前記成膜ガスがクロルシランガスを主ガスとして含むことを特徴とする請求項1乃至5のいずれか一項に記載のSOIウエハの製造方法。

- 前記気相エッチングガスがHClガスを含むことを特徴とする請求項1乃至6のいずれか一項に記載のSOIウエハの製造方法。

- 前記シリコンエピタキシャル層の全面成膜後、SOIウエハを平坦化する工程の前後で、水素を含んだ1000℃以上のガス雰囲気中でアニールする工程を設けることを特徴とする請求項1乃至7のいずれか一項に記載のSOIウエハの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005025868A JP2006216632A (ja) | 2005-02-02 | 2005-02-02 | Soiウエハの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005025868A JP2006216632A (ja) | 2005-02-02 | 2005-02-02 | Soiウエハの製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2006216632A true JP2006216632A (ja) | 2006-08-17 |

Family

ID=36979609

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005025868A Withdrawn JP2006216632A (ja) | 2005-02-02 | 2005-02-02 | Soiウエハの製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006216632A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009177202A (ja) * | 2007-04-02 | 2009-08-06 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法および基板処理装置 |

| JP2009272324A (ja) * | 2008-04-30 | 2009-11-19 | Fuji Electric Device Technology Co Ltd | 半導体装置の製造方法 |

| JP2010517268A (ja) * | 2007-01-18 | 2010-05-20 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | 電極の絶縁方法、及び絶縁電極対を有するナノワイヤベースのデバイス |

-

2005

- 2005-02-02 JP JP2005025868A patent/JP2006216632A/ja not_active Withdrawn

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010517268A (ja) * | 2007-01-18 | 2010-05-20 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | 電極の絶縁方法、及び絶縁電極対を有するナノワイヤベースのデバイス |

| JP2009177202A (ja) * | 2007-04-02 | 2009-08-06 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法および基板処理装置 |

| JP2009272324A (ja) * | 2008-04-30 | 2009-11-19 | Fuji Electric Device Technology Co Ltd | 半導体装置の製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5393772B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP5054886B2 (ja) | 半導体装置のための、SiまたはSiC上に厚い酸化物を形成する方法 | |

| JP5806600B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP2008166802A (ja) | チャンネル膜を有する半導体装置の製造方法 | |

| JP5015440B2 (ja) | 半導体基板の製造方法 | |

| JP2007123875A (ja) | 多孔質層を用いてゲルマニウム・オン・インシュレータ半導体構造を形成するための方法及びこれらの方法によって形成される半導体構造 | |

| US6818537B2 (en) | Method of manufacturing a contact plug for a semiconductor device | |

| JP2009081352A (ja) | 半導体基板の製造方法及び半導体基板 | |

| JP2013110238A5 (ja) | ||

| JP2008205296A (ja) | 炭化珪素半導体素子及びその製造方法 | |

| JP2019140395A (ja) | ボトムアップフィン構造形成方法 | |

| JP6035763B2 (ja) | ゲート酸化膜の形成方法及び炭化珪素半導体装置の製造方法 | |

| JP2008091917A (ja) | バルブ型埋め込みチャネルを備えた半導体素子及びその製造方法 | |

| KR20010009810A (ko) | 실리콘-게르마늄 에피택셜층을 이용한 트렌치 소자분리방법 | |

| JP2013153120A (ja) | 半導体装置の製造方法 | |

| JP5397253B2 (ja) | 半導体基板の製造方法 | |

| JP2006216632A (ja) | Soiウエハの製造方法 | |

| JP2003124314A (ja) | 半導体素子の製造方法 | |

| JP3883827B2 (ja) | 窒化物系半導体素子および窒化物系半導体の形成方法 | |

| JP2009094156A (ja) | 半導体基板および半導体装置 | |

| US7776679B2 (en) | Method for forming silicon wells of different crystallographic orientations | |

| CN100550307C (zh) | 具有球型凹陷沟道的半导体器件及其制造方法 | |

| JP4826373B2 (ja) | 単結晶ウェハの製造方法 | |

| JP4375154B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| KR20090006661A (ko) | 반도체 소자의 소자 분리막 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060703 |

|

| RD04 | Notification of resignation of power of attorney |

Effective date: 20060704 Free format text: JAPANESE INTERMEDIATE CODE: A7424 |

|

| A625 | Written request for application examination (by other person) |

Free format text: JAPANESE INTERMEDIATE CODE: A625 Effective date: 20071213 |

|

| A711 | Notification of change in applicant |

Effective date: 20080204 Free format text: JAPANESE INTERMEDIATE CODE: A711 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20081216 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090219 |

|

| A711 | Notification of change in applicant |

Effective date: 20091112 Free format text: JAPANESE INTERMEDIATE CODE: A712 |

|

| A711 | Notification of change in applicant |

Effective date: 20110422 Free format text: JAPANESE INTERMEDIATE CODE: A712 |

|

| A977 | Report on retrieval |

Effective date: 20110609 Free format text: JAPANESE INTERMEDIATE CODE: A971007 |

|

| A131 | Notification of reasons for refusal |

Effective date: 20110621 Free format text: JAPANESE INTERMEDIATE CODE: A131 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20110823 |