JP2005294841A - 半導体素子の製造方法 - Google Patents

半導体素子の製造方法 Download PDFInfo

- Publication number

- JP2005294841A JP2005294841A JP2005103548A JP2005103548A JP2005294841A JP 2005294841 A JP2005294841 A JP 2005294841A JP 2005103548 A JP2005103548 A JP 2005103548A JP 2005103548 A JP2005103548 A JP 2005103548A JP 2005294841 A JP2005294841 A JP 2005294841A

- Authority

- JP

- Japan

- Prior art keywords

- gas

- etching

- semiconductor device

- manufacturing

- lower electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/24—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials

- H10P50/242—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials of Group IV materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/01—Manufacture or treatment

- H10D1/041—Manufacture or treatment of capacitors having no potential barriers

- H10D1/042—Manufacture or treatment of capacitors having no potential barriers using deposition processes to form electrode extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/711—Electrodes having non-planar surfaces, e.g. formed by texturisation

- H10D1/716—Electrodes having non-planar surfaces, e.g. formed by texturisation having vertical extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/71—Etching of wafers, substrates or parts of devices using masks for conductive or resistive materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/26—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials

- H10P50/262—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by physical means only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/26—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials

- H10P50/262—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by physical means only

- H10P50/263—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by physical means only of silicon-containing layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/26—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials

- H10P50/264—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means

- H10P50/266—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only

- H10P50/267—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only using plasmas

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/26—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials

- H10P50/264—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means

- H10P50/266—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only

- H10P50/267—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only using plasmas

- H10P50/268—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only using plasmas of silicon-containing layers

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Memories (AREA)

- Drying Of Semiconductors (AREA)

Abstract

【課題】下部電極の損傷なしに下部電極の分離を単純に行うことができ、補助膜を用いる場合に発生するシングルビットフェイルを基本的に遮断できる半導体素子の製造方法を提供する。

【解決手段】半導体基板上部にキャパシタの下部電極29Aを画成するための複数のオープン部28を有する絶縁膜27を形成する工程と、前記オープン部28の形状によって前記前記絶縁膜27上に導電膜29を形成する工程と、前記オープン部28の内部より前記オープン部28の外部で前記導電膜29を速くエッチングし(垂直に入射し物理的エッチングを行う第1ガスと前記導電膜とプラズマ状態から化学的に反応がよく現われ、化学的エッチングを行う第2ガスの混合ガス用い、オープン部内部ボトム部分での物理的エッチングが最小化されるようにバイアスパワーを低く)下部電極29Aの分離を行う工程を含むことによって、工程費用を画期的に減少させることができる。

【選択図】図2B

【解決手段】半導体基板上部にキャパシタの下部電極29Aを画成するための複数のオープン部28を有する絶縁膜27を形成する工程と、前記オープン部28の形状によって前記前記絶縁膜27上に導電膜29を形成する工程と、前記オープン部28の内部より前記オープン部28の外部で前記導電膜29を速くエッチングし(垂直に入射し物理的エッチングを行う第1ガスと前記導電膜とプラズマ状態から化学的に反応がよく現われ、化学的エッチングを行う第2ガスの混合ガス用い、オープン部内部ボトム部分での物理的エッチングが最小化されるようにバイアスパワーを低く)下部電極29Aの分離を行う工程を含むことによって、工程費用を画期的に減少させることができる。

【選択図】図2B

Description

この発明は、半導体製造技術、特に、キャパシタを備えた半導体素子の製造方法に関する。

半導体素子の最小線幅が減少し、集積度が増加するに連れて、キャパシタが形成される面積も次第に狭くなっている。このようにキャパシタが形成される面積が狭くなっても、セル内のキャパシタは、最小限セル当り25fF以上のキャパシタンスを確保しなければならない。同様に、狭い面積上に高いキャパシタンスを有するキャパシタを形成するために、シリコン酸化膜(ε=3.8)、窒化膜(ε=7)に代えて、Ta2O5、Al2O3またはHFO2のような高い誘電率を有する物質を誘電体膜として利用する方法、下部電極の面積を効果的に増大させるために下部電極をシリンダ(cylinder)形、凹(concave)形等で立体化したり、下部電極の表面にMPS(Meta stable-Poly Silicon)を成長させて下部電極の有効表面積を1.7〜2倍程度増加させる方法などが提案された。

前記のシリンダ形または凹形キャパシタの製造時に、下部電極の分離(Bottom isolation)工程が必ず必要であるが、一般的に化学的機械的研磨(CMP)またはプラズマ全面エッチング法(Plasma blanket etch)を用いている。

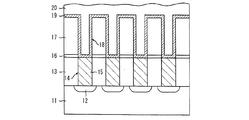

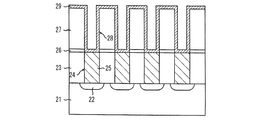

図1Aないし図1Dは、従来の技術に係るプラズマ全面エッチング法を用いた下部電極の分離方法を示す工程断面図である。

図1Aに示されたように、半導体基板11にトランジスタのソース/ドレインのような接合領域12を形成する。ここで、図示していないが、接合領域12の形成前には、周知の如く、素子間分離のためのフィールド酸化膜が形成され、半導体基板11の上部にはゲート電極が形成される。

次に、半導体基板11の上部に層間絶縁膜13を蒸着する。図示していないが、層間絶縁膜13の形成前には、ゲート電極を覆う層間絶縁膜工程、ビットライン工程が行われ、したがって、層間絶縁膜13は、多層構造の層間絶縁膜である。

次に、層間絶縁膜13をエッチングして、接合領域12を露出させるストレージノードコンタクトホール14を形成した後、該ストレージノードコンタクトホール14にストレージノードコンタクトプラグ15を埋め込む。ここで、ストレージノードコンタクトホール14に埋め込まれるストレージノードコンタクトプラグ15は、キャパシタとトランジスタとの間で信号処理を可能にするためのプラグである。

次に、ストレージノードコンタクトプラグ15を含んだ層間絶縁膜13上にエッチングバリア膜16とキャパシタ構造形成用絶縁膜17を順に蒸着した後、キャパシタ構造形成用絶縁膜17とエッチングバリア膜16を順次的にエッチングして、ストレージノードコンタクトプラグ15の表面を露出させるホール18を形成する。

次に、ホール18を含むキャパシタ構造形成用絶縁膜17上に下部電極として用いる導電膜、例えば、ポリシリコン膜19を蒸着する。以後、下部電極分離(Bottom electrode isolation)工程を行うが、下部電極分離の補助膜として感光膜20を塗布する。

次いで、図1Bに示されたように、感光膜20をプラズマ全面エッチングにより一部除去して、ホール18内部にだけ感光膜20を残留させる。

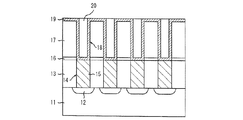

図1Cに示されたように、ホール18の内部に残留する感光膜20を残した状態でプラズマ全面エッチングを行ってキャパシタ構造形成用絶縁膜17上部のポリシリコン膜19を除去して、ホール18の内部にだけシリンダー形下部電極19Aを形成させる。

図1Dに示されたように、感光膜20を除去するための酸素プラズマを用いたストリップ工程を行った後、キャパシタ構造形成用絶縁膜17を除去してシリンダ型下部電極19Aだけを露出させる。

以上のように、従来の技術は、下部電極の分離工程時に、キャパシタ内部の損傷防止及び下部電極の表面積を増加させる後続工程進行にともなう汚染問題を防止するために下部電極分離の補助膜として感光膜(photoresist)を用いている。前記の感光膜は、下部電極に損傷を与えないで、酸素プラズマを利用して除去が容易な特性を有する。

しかし、従来の技術のように、下部電極の分離工程時に、プラズマ全面エッチング法を利用する場合には、下部電極分離補助膜の蒸着、補助膜の部分的除去、補助膜の完全除去及び洗浄工程など、最小限4つの追加工程が必要となるだけでなく、100nm以下のナノテク技術においては、補助膜を完壁に除去することが容易でない。例えば、感光膜を補助膜として用いる場合、全面エッチングが終わった後、補助膜を除去する工程において補助膜である感光膜がウェーハ上の任意の部分に完壁に除去されずに残留して、シングルビットフェイル(single bit fail)を誘発する。このような問題点は、下部電極として用いる導電膜にTiN、Ruなどの金属膜を適用する場合にも発生する。

この発明は、上述した従来の技術の問題点を解決するためになされたものであって、その目的は、下部電極の損傷なしに下部電極の分離を単純に行うことができるだけではなく、補助膜を用いる場合に発生するシングルビットフェイルを基本的に遮断できる半導体素子の製造方法を提供することである。

前記目的を達成するため、この発明による半導体素子の製造方法は、半導体基板上部にキャパシタの下部電極を画成するための複数のオープン部を有する絶縁膜を形成する工程と、前記オープン部の形状によって前記絶縁膜上に導電膜を形成する工程と、前記オープン部の内部よりも前記オープン部の外部の方から前記導電膜をより速くエッチングして、下部電極の分離を遂行する工程を含むことを特徴とし、前記下部電極の分離を遂行する工程は、垂直に入射して物理的エッチングを行う第1ガスと前記導電膜とプラズマ状態から化学的に反応がよく現われ、化学的エッチングを行う第2ガスの混合ガスを用いることを特徴とし、前記下部電極の分離を遂行する工程から前記オープン部の内部のボトム部分で物理的エッチングが最小化されるようにバイアスパワーを調節して行うことを特徴とし、前記下部電極の分離を行う工程は、垂直に入射し、物理的エッチングを行う第1ガスと前記導電膜とプラズマ状態から化学的に反応がよく現われ、化学的エッチングを行う第2ガスの混合ガスを用いて、前記オープン部の内部ボトム部分での物理的エッチングが最小化されるようにバイアスパワーを調節して行うことを特徴とする。

上述したこの発明は、補助膜を導入しないながらも、下部電極を分離することができるため、補助膜の導入に係る工程を単純化させることによって工程費用を画期的に減少させることができる効果がある。

また、補助膜除去の不良のために発生するシングルビットフェイルを基本的に除去することによって、不良率を最小化して収率を増大させることができる効果がある。

以下、この発明が属する技術の分野における通常の知識を有する者がこの発明の技術的思想を容易に実施できる程度に詳細に説明するために、この発明の最も好ましい実施の形態を添付の図面を参照して説明する。

後述するこの発明の実施の形態は、下部電極の分離工程時に、下部電極の内部及び底部のエッチング損失を防止するために感光膜のような補助膜を用いることに伴う複雑な工程を減らすために、補助膜を使用せず下部電極がプラズマにそのまま露出された状態でも、プラズマエッチングによるエッチング損傷なく、下部電極を分離しようとする。

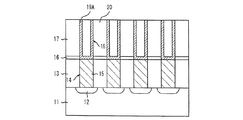

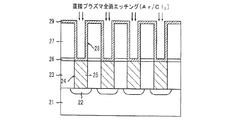

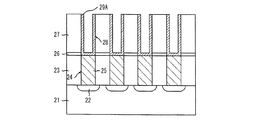

図2Aないし図2Dは、この発明の実施の形態に係る半導体素子の製造方法を示す工程断面図である。

図2Aに示すように、半導体基板21にトランジスタのソース/ドレインのような接合領域22を形成する。ここで、図示していないが、接合領域22の形成前には、周知の如く、素子間分離のためのフィールド酸化膜が形成され、半導体基板21の上部にはゲート電極が形成される。

次いで、半導体基板21の上部に層間絶縁膜23を蒸着する。図示していないが、層間絶縁膜23の形成前には、ゲート電極を覆う層間絶縁膜工程、ビットライン工程が行われ、したがって、層間絶縁膜23は、多層構造の層間絶縁膜である。

次いで、層間絶縁膜23をエッチングして接合領域22を露出させるストレージノードコンタクトホール24を形成した後、このストレージノードコンタクトホール24にストレージノードコンタクトプラグ25を埋め込む。ここで、ストレージノードコンタクトホール24に埋め込まれるストレージノードコンタクトプラグ25は、キャパシタとトランジスタとの間の信号処理を可能にするためのプラグである。

次いで、ストレージノードコンタクトプラグ25を含む層間絶縁膜23上にエッチングバリア膜26とキャパシタ構造形成用絶縁膜27を順に蒸着した後、キャパシタ構造形成用絶縁膜27とエッチングバリア膜26を順次にエッチングして、ストレージノードコンタクトプラグ25の表面を露出させる下部電極が形成される領域を定義するオープン部28を形成する。

次いで、オープン部28の現象によってキャパシタ構造の形成用絶縁膜27の上に下部電極として用いる導電膜29を蒸着する。ここで、下部電極として用いる導電膜29は、ドープドポリシリコン(doped polysilicon)、アンドープドポリシリコン/ドープドポリシリコン(undoped polysilicon/doped polysilicon)積層、タングステン(W)、チタンナイトライド(TiN)、ルテニウム(Ru)または白金(Pt)の中から選択される。

以後、図2Bに示すように、下部電極分離(Bottom electrode isolation)工程を行うが、下部電極分離の補助膜である感光膜を塗布しないで、直接プラズマ全面エッチングを行って導電膜からなるシリンダ形態の下部電極を形成する。ここで、下部電極として用いる導電膜29の種類によってエッチング条件が異なる。

以下、下部電極として用いる導電膜29がチタンナイトライド(TiN)の場合のプラズマ全面エッチングについて説明する。

通常のプラズマエッチング装置は、チャンバー(Chamber)、トップ電極(Top electrode)、ボトム電極(Bottom electrode)で構成されて、ボトム電極の上部には、エッチングされる物質が形成されたウェーハが位置する。ここで、トップ電極は、プラズマを発生させるためのソースパワー(source power)を印加するための電極であり、ボトム電極は、プラズマ内のイオン及びラジカルをウェーハ側に引き寄せるためのバイアスパワー(Bias power)を印加するための電極であり、トップ電極とボトム電極が分離されているため、ウェーハに入射するイオン及びラジカルのエネルギを独立に調節することができる。

上のようなプラズマエッチング装置を用いたプラズマエッチングは、物理的エッチング(Physical etching)、化学的エッチング(Chemical etching)、物理化学的エッチング(physico-chemical etching)に分類することができる。

まず、物理的エッチングは、Ar、He、Xeなどのような不活性ガス(Inert gas)を利用してプラズマを発生させ、そのプラズマ内の陽イオン(Positive ion)をウェーハでに垂直に入射させて純粋に被エッチング層を物理的にエッチングする方法であり、化学的エッチングは、被エッチング層とプラズマ状態から化学的に反応がよく起きるガスを選択してプラズマを発生させ、そのプラズマ内のアクティブになった中性のラジカル(radical)を用いて純粋に化学的にエッチングする方法であり、物理化学的エッチングは、プラズマ内の陽イオンをウェーハに入射させてイオンの強力な衝突エネルギを利用するとともに、被エッチング層と化学的反応がよく起きるラジカルを利用することによって、エッチング速度を一桁程度増加させることができるようにシナジー効果を得る方法である。

以上のような原理によって、この発明は、下部電極分離の工程時に、物理化学的エッチングを用いて全面エッチングを行う。

下部電極用導電膜29がチタンナイトライド(TiN)と仮定すると、チタンナイトライド(TiN)の物理化学的エッチングを誘導するために、ArガスとC12ガスを用いる。ここで、Arガスは、チタンナイトライド(TiN)の物理的エッチングのためのガスであり、C12ガスは、化学的エッチングのためのもので、チタンナイトライド(TiN)とよく化学反応するガスである。

もし、下部電極を形成するために感光膜のような補助膜なしでチタンナイトライド(TiN)をプラズマ全面エッチングすることにおいて、Arを用いた物理的エッチングだけを用いると、オープン部28の外部に形成されたチタンナイトライド(TiN)だけでなく、オープン部28の内部に形成されたチタンナイトライド(TiN)もエッチングされ、また物理的エッチングされ、跳ねてきたTiN原子がエッチングチャンバーのチャンバー壁に持続的に蒸着されることによって、パワーの伝達効率の減少とともに最終的には多くのパーティクルを誘発するようになる。

そして、下部電極を形成するために補助膜なしでC12を用いた化学的エッチングだけを用いれば、化学的エッチングは、方向性のない等方性エッチングが起きるので、オープン部28の外部及び内部の相当な深さのTiNまでもエッチングされて下部電極の高さが顕著に減少するだけでなく、TiNの結晶粒(grain)に沿ってC12が拡散しながらエッチングされて、下部電極のパターンが悪くなり、各TiNの結晶粒が小さな衝撃にも落ちて欠陥を誘発させることになる。さらに、縦横比(Aspect ratio)が小さい場合、オープン部28の内部ボトム部分に形成されたTiNまでも完全にエッチングされて、下部電極自体が全部エッチングされることになり得る。

したがって、この発明の補助膜なしにプラズマ全面エッチングだけで下部電極を好ましく分離するためには、オープン部の外部に形成されたTiNは、物理的エッチング及び化学的エッチングが同時に行われるようにして速い速度でエッチングする反面、ホール28の内部(オープン部の側壁及びボトム部分)に形成されたTiNは、化学的エッチングだけ起きるようにし、非常に遅い速度でエッチングできるようにエッチングガス及びエッチング条件を調節する。

一般的にポリシリコンや金属をエッチングする場合、イオンの直進性のため、オープン部28の内部側壁は、物理的エッチングが殆ど起こらない反面、オープン部28の内部ボトム部分は、物理的エッチングが起こる。この発明の場合のように、オープン部28の内部ボトム部分から物理的エッチングを最小化するためには、オープン部28内部の圧力を高め、垂直に入射して入ってくるイオンがオープン部28上部を通過し、オープン部28の内部ボトム部分まで下りてくるまでオープン部28内部の数多くの粒子と衝突し、そのエネルギを失うようにすればよい。このようにオープン部28内部の圧力を高める方法は、オープン部28内部の下部電極物質と化学的エッチングを起こすことができるエッチングガスを用いてプラズマエッチングを行えばよい。この時、オープン部28内部の下部電極物質と化学的エッチングによって発生するエッチング副産物が十分に多くなる場合、オープン部28内部の圧力を十分に増加させることができ、これによってオープン部28内部に入射し入ってきたイオンは、数多くのエッチング副産物と衝突し、そのエネルギを失うようになり、結局オープン部28の内部ボトム部分に到達しても、そのエネルギが急激に減少し物理的エッチングを起こすことができなくなる。

そして、オープン部28の内部ボトム部分の物理的エッチングを最小化、ないしはその影響を無くすためには、オープン部28内部の圧力の増加だけでなく、オープン部28に入ってくる入射イオンのエネルギ減少が必要である。換言すれば、オープン部28内部の圧力が高いとしても、入射イオンのエネルギが非常に高いならば、オープン部28の内部ボトム部分に到達したイオンのエネルギが物理的エッチングを起こすことができる。したがって、オープン部28の内部ボトム部分に到達するイオンのエネルギは、エッチング副産物によるオープン部28内部の圧力及び入射イオンのエネルギを決定するバイアスパワーの組合せによって決定される。

結局、エッチング副産物によるオープン部28内部の圧力の調節、すなわち、化学的エッチングによるエッチング副産物の量の調節には、化学的エッチングを起こし得るエッチングガスの選択は、もちろん、物理的エッチングのためのエッチングガスと化学的エッチングのためのエッチングガスとの含有量比の調節が重要であり、オープン部28の内部ボトム部分に到達するイオンのエネルギを最小化するためには、入射イオンのエネルギをできるだけ減少させることが好ましい。しかし、物理的エッチングを最小化するために、非常に低いバイアスパワーを用いると、オープン部28の外部に形成されたTiNさえも物理的エッチングが起こらない可能性があるため、適切なバイアスパワーを必要とする。

総合してみれば、補助膜なしに行うプラズマ全面エッチング工程は、オープン部28の外部に形成された下部電極物質は、物理的エッチング及び化学的エッチングが同時に起こらなければならない反面、オープン部28の内部側壁及びボトム部分の下部電極物質は、化学的エッチングだけが起きることができるようにエッチングガスの組合せ及び適切なエッチング条件が要求される。

例えば、チタニウムナイトライド(TiN)の場合、オープン部28の外部では、物理化学的エッチングが起こるようにAr/Cl2の混合ガスを用いて、オープン部28の内部ボトム部分で物理的エッチングを最小化するためにバイアスパワーを30W〜300Wに低く調節し、Cl2による化学的エッチングの程度を適切に調節するために、Cl2とArとの混合ガスでCl2含有量を1%〜50%に調節する。

併せて、エッチングチャンバの圧力は、物理的エッチング及び化学的エッチングが適切に起きるようにするために、1mtorr〜50mtorrに調節する。

最後に、プラズマ全面エッチング時に、トップ電極のパワーやチャンバの圧力、そしてトップ電極の温度及びチャンバの温度は、大きく影響を与えないが、各条件に合うように調節して用いる。

前記のような限界条件でプラズマ全面エッチングを行う場合、オープン部28の外部に形成されたチタニウムナイトライド(TiN)は、エッチング速度が非常に速くエッチングされる反面、オープン部28の内部側壁に形成されたチタニウムナイトライド(TiN)は、化学的エッチングが遅く起きるように調整されたエッチング条件(Cl2とArとの混合ガスでCl2の含有量を1%〜50%に調節)下でエッチングが行われるため、非常に微小な程度にエッチングされる。そして、オープン部28の内部側壁のTiNとラジカルとの反応により生じた反応副産物が、オープン部28の内部を満たすようになりながらオープン部28内部の圧力が増加され、バイアスパワーを30W〜300Wに低く調節することによって、プラズマからオープン部28の内部ボトム部分に入射する陽イオン及び拡散し入ってくるラジカルの流れを抑制することによって、オープン部28の内部ボトム部分に形成されたTiNは、微小な程度にだけエッチングが行われる。

結局、全体的に見ると、オープン部28の外部に形成されたチタニウムナイトライド(TiN)は、物理化学的エッチングによって速くエッチングされ、オープン部28の内部側壁やオープン部28の内部ボトム部分に形成されたチタニウムナイトライド(TiN)は、オープン部28の外部に比べ、相対的に非常に遅くエッチングされるため、傾斜エッチングではない垂直方向へのバリヤレスプラズマ全面エッチングをしても、下部電極の好ましいエッチングパターンを良好に作ることができる。

上述したTiNに対する全面エッチングの際に、オープン部28の外部でのエッチング速度に対するオープン部28の内部側壁及びボトム部分でのエッチング速度が1%〜70%になるように調節する。そして、オープン部28の内部側壁でのエッチング速度とボトム部分でのエッチング速度は、殆ど同じレベルに調節する。

このため、処理工程条件は、10mtorr、300W(S)、100W(B)、10Cl2:190Ar、40℃、EOP=16”±1”、OE=10”とする。ここで、300W(S)は、ソースパワーであり、100W(B)は、バイアスパワーであり、EOP(End of Point)は、終末点であり、OE(Over Etch)は、過度エッチングを意味する。

前記の処理工程条件で行う場合、TiNの厚さ300Å基準とすると、オープン部28の外部でのエッチング速度は、1120Å/分であり、オープン部28の内部側壁及びボトム部分では、エッチング速度は、オープン部28の外部に比べて顕著に低くなり、10Å/分に測定された。ここで、オープン部28の外部でのTiNエッチング速度は、エッチング条件により異なるが、概略500Å/分〜2000Å/分であり、したがって、オープン部28の内部でのTiNエッチング速度は、5Å/分〜140Å/分(2000Å/分の7%レベル)である。

そして、Cl2/Arの含有量調節にともなうエッチング速度の変化は、Cl2/Arの含有量が非常に低い場合、500Å/分以上であり、Cl2/Arの含有量が非常に高い場合、3000Å/分程度に変化させることができる。すなわち、Cl2/Arの含有量の調整により、エッチング速度は、500Å/分〜3000Å/分の範囲で変化させることができる。しかし、下部電極の厚さが薄いので、スループットは、大きな問題にならず、エッチングプロフィールや過度エッチング(Over Etch)(OE)のコントロールのために、エッチング速度を比較的遅くする方向にエッチング条件を調節する。

実質的に好ましいプラズマ全面エッチング条件は、圧力が5mtorr〜20mtorr、ソースパワーが300W〜800W、バイアスパワーが30W〜300W、Cl2+Ar混合ガス中のCl2ガスの割合が1%〜50%、電極温度が10℃〜40℃である。

前記の実施の形態において、TiNのプラズマ全面エッチング時に、化学的エッチングを伴うエッチングガスとしては、Cl2以外にHClまたはCCl4のようなCl系ガスを単独または混合して用いることができ、ArとCl系エッチングガスの混合ガス以外にプラズマ安定化、流量調節、エッチングガス希釈のためにAr、Xe、Heなどを単独でまたは混合して添加することができ、化学的エッチングが優勢に起きて下部電極が損傷されることを防止する保護(Passivation)または反応抑制剤(inhibitor)としてO2、N2などを単独または混合して添加することができる。

前記の実施の形態では、TiNを下部電極として用いる場合について説明したが、この発明は、下部電極として用いる導電膜の種類によってエッチング条件が異なる。

まず、下部電極用の導電膜としてシリコンSi系列を用いる場合には、プラズマ全面エッチング時、SF6、NF3、CF4のようなフッ素系、C12のような塩素系、HBrのようなブロム(Bromine)系ガスを化学的エッチングガスとして単独でまたは混合して用いる。

そして、下部電極用の導電膜としてタングステン(W)を用いる場合、プラズマ全面エッチング時に、エッチングガスとしてSF6、NF3またはCF4のようなフッ素系ガスを化学的エッチングガスとして単独または混合して用いる。

そして、下部電極用の導電膜としてルテニウム(Ru)または白金(Pt)のような貴金属系金属膜を用いる場合には、プラズマ全面エッチング時に、O2、C12を化学的エッチングガスとして単独でまたは混合して用いる。

以上のように、シリコン系列、タングステン、貴金属系金属膜を用いる場合のプラズマ全面エッチング時に、化学的エッチングガス以外に物理的エッチングガスとしては不活性ガスを用い、またプラズマ安定化、流量調節、メインエッチングガス希釈のためにAr、Xe、Heなどの不活性ガスを単独でまたは混合して添加することができる。そして、化学的エッチングガスに係よる化学的エッチング特性が最も優勢に起きる場合は、これを抑制するための保護(Passivation)または反応抑制剤(inhibitor)の目的でO2、N2などを単独でまたは混合して添加する。

前記のようなプラズマ全面エッチングのためのプラズマエッチング装置では、ICP(Inductively Coupled Plasma)、ECR(Electron Cyclotron Resonance)、マイクロウエーブ(Microwave)、CCP(Capacitively Coupled Plasma)などを用い、下部電極分離時に、オープン部の外部のエッチング形状を調節する目的でエッチングガスの比率、ソースパワー、バイアスパワー、圧力、トップ電極及びボトム電極の温度などの諸条件を調節する。

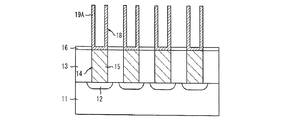

図2Bのような下部電極分離工程が完了した後には、図2Cに示すように、シリンダ形態の下部電極29Aが形成される。

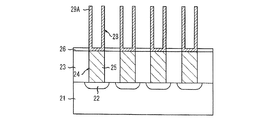

図2Dに示されたように、下部電極29Aの形成後に湿式ディップアウト工程によりキャパシタ構造形成用絶縁膜27を除去してシリンダ形下部電極29Aだけを露出させる。

上記の実施形態のようにプラズマエッチングを行う場合は、既存のプラズマエッチング装置をそのまま使用しながらエッチングガスを含むエッチング条件を調節するため、設備装置構成を変える必要がなくて設備装置の投資に対する費用負担がなく、垂直に入射する特性を有する物理的エッチングと等方性エッチング特性を有する化学的エッチングとを同時に行うことによって、全体的にエッチングの均一度が良好となるという付加的な効果が得られる。

また、感光膜のような補助膜なしにプラズマ全面エッチングを行っても、下部電極の分離が可能であり、また下部電極下部にパンチ(Punch)が発生しない効果が得られる。

なお、この発明は、上述の実施形態に限定されるものではなく、この発明に係る技術的思想から逸脱しない範囲内で、様々な変更が可能であり、それらはこの発明の技術的範囲に属する。

21…半導体基板、22…接合領域、23…層間絶縁膜、25…ストレージノードコンタクトプラグ、26…エッチングバリア膜、27…キャパシタ構造形成用絶縁膜、28…ホール、29A…下部電極。

Claims (20)

- 半導体基板の上部にキャパシタの下部電極を画成するための複数のオープン部を有する絶縁膜を形成する工程と、

該オープン部の形状によって前記絶縁膜上に導電膜を形成する工程と、

前記オープン部の内部より前記オープン部の外部から前記導電膜を速くエッチングし、下部電極の分離を遂行する工程と

を含んでなる半導体素子の製造方法。 - 前記下部電極の分離を行う工程が、垂直に入射し、物理的エッチングを行う第1ガスと、前記導電膜とプラズマ状態から化学的に反応がよく起こり、化学的エッチングを行う第2ガスとの混合ガスを用いる

ことを特徴とする請求項1に記載の半導体素子の製造方法。 - 前記混合ガスにおいて、前記第1ガスと前記第2ガスとの含有量を同一にするか又は前記第1ガスに対する前記第2ガスの含有量をより小さくしてエッチングを行う

ことを特徴とする請求項2に記載の半導体素子の製造方法。 - 前記混合ガスにおいて、前記第2ガスの含有量を1%〜50%にする

ことを特徴とする請求項3に記載の半導体素子の製造方法。 - 前記混合ガスに、O2またはN2を単独で添加するか、またはO2とN2とを混合して添加する

ことを特徴とする請求項2に記載の半導体素子の製造方法。 - 前記下部電極の分離を行う工程において、前記オープン部の外部より前記オプン部の内部ボトム部分で物理的エッチングが最小化されるようにバイアスパワーを調節して行う

ことを特徴とする請求項1に記載の半導体素子の製造方法。 - 前記バイアスパワーを30W〜300Wの範囲に調節して行う

ことを特徴とする請求項6に記載の半導体素子の製造方法。 - 前記下部電極の分離を行う工程は、

垂直に入射し、物理的エッチングを行う第1ガスと前記導電膜とプラズマ状態で化学的に反応がよく起きて化学的エッチングを行う第2ガスとの混合ガスを用い、前記オープン部の外部より前記オプン部の内部ボトム部分での物理的エッチングの方が最小化されるようにバイアスパワーを調節して行う

ことを特徴とする請求項1に記載の半導体素子の製造方法。 - 前記混合ガスにおいて、前記第1ガスと前記第2ガスとの含有量を同一にするか又は前記第1ガスに対する前記第2ガスの含有量をより小さくしてエッチングを行う

ことを特徴とする請求項8に記載の半導体素子の製造方法。 - 前記混合ガスにおいて、前記第2ガスの含有量を1%〜50%にする

ことを特徴とする請求項9に記載の半導体素子の製造方法。 - 前記混合ガスに、O2またはN2を単独で添加するか、またはO2とN2とを混合して添加する

ことを特徴とする請求項8に記載の半導体素子の製造方法。 - 前記バイアスパワーを30W〜300Wの範囲に調節する

ことを特徴とする請求項8に記載の半導体素子の製造方法。 - 前記導電膜をチタニウムナイトライドで形成し、前記第1ガスに不活性ガスを用い、前記第2ガスにCl系ガスを用いる

ことを特徴とする請求項2または請求項8に記載の半導体素子の製造方法。 - 前記Cl系ガスが、Cl2、HClまたはCCl4の中から選択されるか、または、前記Cl2、HClまたはCCl4の中から少なくとも2つのガスを混合して用いる

ことを特徴とする請求項13に記載の半導体素子の製造方法。 - 前記導電膜をシリコン膜系列で形成し、前記第2ガスとしてフッ素系ガス、塩素系ガスまたはブローム系ガスの中から選択された単独のまたは混合ガスを用い、前記第1ガスとして不活性ガスを用いる

ことを特徴とする請求項2または請求項8に記載の半導体素子の製造方法。 - 前記フッ素系ガスは、SF6、NF3または、CF4であり、前記塩素系ガスはC12であり、前記ブローム系ガスは、HBrである

ことを特徴とする請求項15に記載の半導体素子の製造方法。 - 前記導電膜をタングステン膜で形成し、前記第2ガスとしてフッ素系ガスを用い、前記第1ガスとして不活性ガスを用いる

ことを特徴とする請求項2または請求項8に記載の半導体素子の製造方法。 - 前記フッ素系ガスは、SF6、NF3、またはCF4を単独でまたは混合して用いる

ことを特徴とする請求項17に記載の半導体素子の製造方法。 - 前記導電膜を貴金属系の金属膜で形成し、前記第2ガスとしてO2またはC12を単独でまたは混合して用い、前記第2ガスとして不活性ガスを用いる

ことを特徴とする請求項2または請求項8に記載の半導体素子の製造方法。 - 前記下部電極の分離を行う工程は、プラズマ全面エッチングで行う

ことを特徴とする請求項1に記載の半導体素子の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR20040022061 | 2004-03-31 | ||

| KR1020050018765A KR100680437B1 (ko) | 2005-03-07 | 2005-03-07 | 보조열교환장치가 구비된 가스보일러 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294841A true JP2005294841A (ja) | 2005-10-20 |

Family

ID=35070659

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005103548A Pending JP2005294841A (ja) | 2004-03-31 | 2005-03-31 | 半導体素子の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2005294841A (ja) |

| DE (1) | DE102005015138A1 (ja) |

| TW (1) | TWI278035B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108811288A (zh) * | 2017-05-03 | 2018-11-13 | 释延豹 | 一种等离子体发生装置用电晕电极及其制作方法 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11647624B2 (en) | 2020-12-15 | 2023-05-09 | Micron Technology, Inc. | Apparatuses and methods for controlling structure of bottom electrodes and providing a top-support thereof |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000332221A (ja) * | 1999-05-12 | 2000-11-30 | Lucent Technol Inc | 集積回路とその方法 |

| JP2001189303A (ja) * | 1999-12-28 | 2001-07-10 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2001210802A (ja) * | 2000-01-26 | 2001-08-03 | Hitachi Ltd | 半導体装置及びその製造方法 |

-

2005

- 2005-03-31 TW TW094110285A patent/TWI278035B/zh not_active IP Right Cessation

- 2005-03-31 DE DE102005015138A patent/DE102005015138A1/de not_active Ceased

- 2005-03-31 JP JP2005103548A patent/JP2005294841A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000332221A (ja) * | 1999-05-12 | 2000-11-30 | Lucent Technol Inc | 集積回路とその方法 |

| JP2001189303A (ja) * | 1999-12-28 | 2001-07-10 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2001210802A (ja) * | 2000-01-26 | 2001-08-03 | Hitachi Ltd | 半導体装置及びその製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108811288A (zh) * | 2017-05-03 | 2018-11-13 | 释延豹 | 一种等离子体发生装置用电晕电极及其制作方法 |

| CN108811288B (zh) * | 2017-05-03 | 2023-10-03 | 深圳天基权健康科技集团股份有限公司 | 一种等离子体发生装置用电晕电极及其制作方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200532792A (en) | 2005-10-01 |

| TWI278035B (en) | 2007-04-01 |

| DE102005015138A1 (de) | 2005-11-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3976703B2 (ja) | 半導体装置の製造方法 | |

| US20070037101A1 (en) | Manufacture method for micro structure | |

| US7803518B2 (en) | Method for manufacturing micro structure | |

| KR20080086686A (ko) | 반도체 소자의 제조방법 | |

| KR102171265B1 (ko) | 금속 마스크를 이용한 패터닝 방법 및 그 패터닝 방법을 포함한 반도체 소자 제조방법 | |

| JP2006310749A (ja) | 半導体素子のトランジスタ製造方法 | |

| JP4711658B2 (ja) | 微細なパターンを有する半導体装置の製造方法 | |

| US7060628B2 (en) | Method for fabricating a hard mask polysilicon gate | |

| KR100670706B1 (ko) | 반도체 소자의 콘택 플러그 형성 방법 | |

| KR20080060376A (ko) | 반도체 소자의 제조방법 | |

| JP2005294841A (ja) | 半導体素子の製造方法 | |

| KR100745398B1 (ko) | 텅스텐 패턴 형성 방법 및 이를 이용한 반도체 소자의제조방법. | |

| KR100607650B1 (ko) | 반도체소자의 제조 방법 | |

| KR100661186B1 (ko) | 플래쉬 메모리 소자의 제조방법 | |

| KR100507872B1 (ko) | 반도체 장치 제조 방법 | |

| KR100875650B1 (ko) | 반도체 소자의 캐패시터 제조 방법 | |

| CN100358106C (zh) | 一种制造半导体器件的方法 | |

| KR100448855B1 (ko) | 반도체소자의 제조방법 | |

| KR20050038872A (ko) | 미세 패턴 형성이 가능한 반도체 장치 제조 방법 | |

| KR20050116314A (ko) | 반도체소자의 깊은 콘택홀 형성 방법 | |

| KR100695417B1 (ko) | 미세 패턴 형성이 가능한 반도체 장치 제조 방법 | |

| US6686234B1 (en) | Semiconductor device and method for fabricating the same | |

| JP2003045894A (ja) | 半導体装置の製造方法 | |

| JP2008198713A (ja) | 半導体装置の製造方法 | |

| KR100875674B1 (ko) | 캐패시터 누설을 방지하는 반도체소자 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110111 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110705 |