JP2005294760A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2005294760A JP2005294760A JP2004111380A JP2004111380A JP2005294760A JP 2005294760 A JP2005294760 A JP 2005294760A JP 2004111380 A JP2004111380 A JP 2004111380A JP 2004111380 A JP2004111380 A JP 2004111380A JP 2005294760 A JP2005294760 A JP 2005294760A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor

- semiconductor device

- heat

- insulating film

- interlayer insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

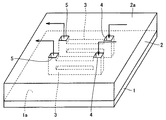

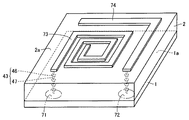

【解決手段】 半導体装置は、主表面1aを有する半導体基板1と、主表面1a上に形成され、主表面1aに設けられた半導体素子を覆う層間絶縁膜2と、層間絶縁膜2に形成され、冷却用流体が流れる冷却路3とを備える。冷却路3は、層間絶縁膜2の内部を循環するように形成されている。冷却路3は、冷却用流体が供給される一方端4と、冷却用流体が排出される他方端5とを含む。

【選択図】 図1

Description

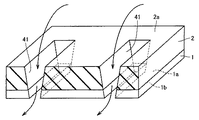

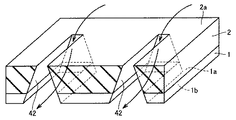

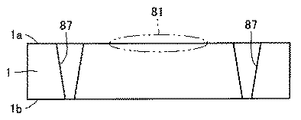

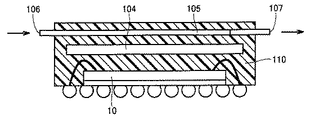

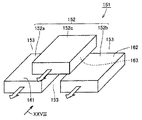

図1は、この発明の実施の形態1における半導体装置を示す斜視図である。図1を参照して、半導体装置は、主表面1aを有する半導体基板1と、駆動することより熱を発生する、主表面1aに形成された図示しない半導体素子と、主表面1a上に形成され、図示しない半導体素子を覆う層間絶縁膜2とを備える。層間絶縁膜2の内部には、冷却路3が形成されている。冷却路3は、層間絶縁膜2の頂面2a上の離れた位置にそれぞれ開口された一方端4および他方端5を有する。冷却路3は、主表面1aに形成された半導体素子の近傍を通過するように、一方端4から他方端5に向けて延びている。

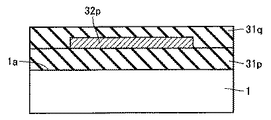

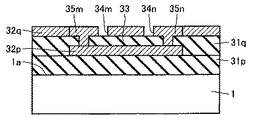

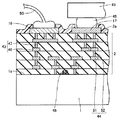

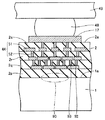

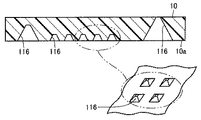

図10は、この発明の実施の形態2における半導体装置の一部を示す断面図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図10を用いて説明する冷却構造をさらに備える。なお図中において、実施の形態1に記載の半導体装置と比較して、同一またはそれに相当する部材には、同じ参照番号を付している。

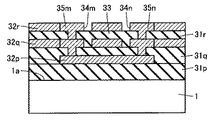

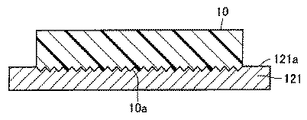

図13は、この発明の実施の形態3における半導体装置の一部を示す断面図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図13を用いて説明する冷却構造をさらに備える。なお図中において、既に説明した半導体装置と比較して、同一またはそれに相当する部材には、同じ参照番号を付している。

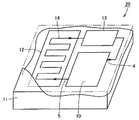

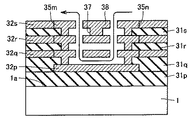

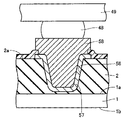

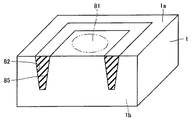

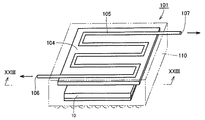

図14は、この発明の実施の形態4における半導体装置を示す斜視図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図14を用いて説明する冷却構造をさらに備える。なお図中において、既に説明した半導体装置と比較して、同一またはそれに相当する部材には、同じ参照番号を付している。

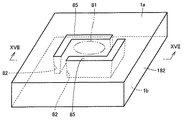

図15は、この発明の実施の形態5における半導体装置を示す斜視図である。図中には、半導体装置の断面が示されている。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図15を用いて説明する断熱構造をさらに備える。なお図中において、既に説明した半導体装置と比較して、同一またはそれに相当する部材には、同じ参照番号を付している。

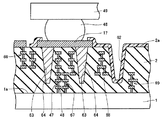

図20は、この発明の実施の形態6における半導体装置の一部を示す断面図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図20を用いて説明する冷却構造をさらに備える。なお図中において、既に説明した半導体装置と比較して、同一またはそれに相当する部材には、同じ参照番号を付している。

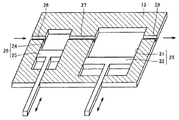

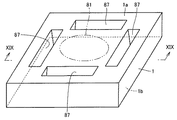

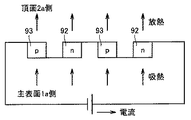

図22は、この発明の実施の形態7における半導体装置を示す斜視図である。図23は、図22中のXXIII−XXIII線上に沿った断面図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図22を用いて説明する冷却構造をさらに備える。

図24は、この発明の実施の形態8における半導体装置を示す断面図である。本実施の形態における半導体装置は、実施の形態1に記載の半導体装置が備える冷却構造に加えて、図24を用いて説明する冷却構造をさらに備える。

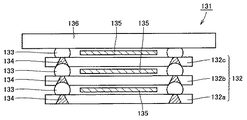

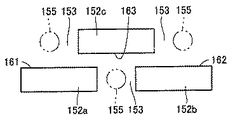

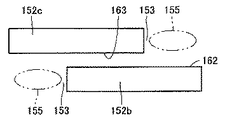

図26は、この発明の実施の形態9における半導体装置を示す断面図である。図29を参照して、半導体パッケージ131は、複数の半導体チップ132が内部に搭載されるマルチチップタイプの半導体パッケージである。半導体パッケージ131は、互いに所定の間隔を隔てて位置決めされた複数の半導体チップ132(132a、132bおよび132c)と、複数の半導体チップ132の間を接続するメタルバンプ133と、複数の半導体チップ132の間に配置された、たとえば銅などからなる放熱部材135とを備える。なお図示しないが、半導体パッケージ131には、複数の半導体チップ132間のフィラーとして、パッケージ樹脂やポリイミドなどの樹脂材料が設けられている。

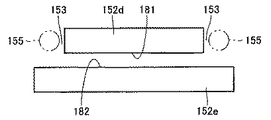

図27は、この発明の実施の形態10における半導体装置を示す斜視図である。図28は、図27中に示す矢印XXVIIIから見た半導体装置を示す正面図である。

Claims (21)

- 主表面を有する半導体基板と、

前記主表面上に形成され、前記主表面に設けられた半導体素子を覆う層間絶縁膜と、

前記層間絶縁膜に形成され、冷却用流体が流れる第1の冷却路とを備える、半導体装置。 - 前記第1の冷却路は、前記層間絶縁膜の内部を循環するように形成されている、請求項1に記載の半導体装置。

- 前記第1の冷却路は、冷却用流体が供給される一方端と、冷却用流体が排出される他方端とを含む、請求項1または2に記載の半導体装置。

- 前記半導体基板、前記層間絶縁膜および前記第1の冷却路を含む半導体チップと、

前記半導体チップを覆うように形成された樹脂部材と、

前記樹脂部材内に設けられたポンプ部および金属材料からなる放熱部とを備え、

前記ポンプ部は、前記一方端および前記他方端に接続されて、前記第1の冷却路に冷却用流体を循環させ、前記放熱部は、前記他方端から排出された冷却用流体の熱を放熱する、請求項3に記載の半導体装置。 - 前記層間絶縁膜に形成され、前記層間絶縁膜の熱伝導率に対して相対的に大きい熱伝導率を有する第1の放熱部材をさらに備える、請求項1から4のいずれか1項に記載の半導体装置。

- 前記第1の放熱部材は、ビアホールおよび金属配線を含む、請求項5に記載の半導体装置。

- 前記第1の放熱部材は、前記層間絶縁膜の表面から露出している、請求項5または6に記載の半導体装置。

- 前記層間絶縁膜の外部に配置され、前記層間絶縁膜の表面から露出する前記第1の放熱部材に接続された第2の放熱部材をさらに備える、請求項7に記載の半導体装置。

- 前記第2の放熱部材は、インダクタ素子およびアンテナ素子の少なくともいずれか一方を含む、請求項8に記載の半導体装置。

- 前記半導体基板には、半導体素子を取り囲むように、前記主表面側に開口する凹部が形成されている、請求項1から9のいずれか1項に記載の半導体装置。

- 前記層間絶縁膜に形成されたペルチェ素子をさらに備える、請求項1から10のいずれか1項に記載の半導体装置。

- 前記半導体基板、前記層間絶縁膜および前記第1の冷却路を含む半導体チップと、

前記半導体チップを覆うように形成された樹脂部材と、

前記樹脂部材に形成され、冷却用流体が流れる第2の冷却路とを備える、請求項1から11のいずれか1項に記載の半導体装置。 - 前記半導体チップの表面に接触して形成された第3の放熱部材をさらに備える、請求項12に記載の半導体装置。

- 前記半導体チップの表面が凹凸形状に形成されている、請求項12または13に記載の半導体装置。

- 半導体パッケージ内に複数の半導体チップが搭載されるマルチチップタイプの半導体装置であって、

互いに間隔を隔てて一方向に配列された複数の半導体チップと、

前記複数の半導体チップの各々に直接、接触し、隣り合う前記複数の半導体チップを互いに接続する金属配線と、

隣り合う前記複数の半導体チップ間に配置された放熱手段とを備える、半導体装置。 - 前記放熱手段は、冷却用流体が流れる冷却路および金属材料からなる放熱部材の少なくともいずれか一方を含む、請求項15に記載の半導体装置。

- 一方向に配列された前記複数の半導体チップのうち中間に位置する半導体チップから発生する熱量が、一方向に配列された前記複数の半導体チップのうち両端に位置する半導体チップから発生する熱量よりも小さい、請求項15または16に記載の半導体装置。

- 一方向に配列された前記複数の半導体チップのうち端に位置する半導体チップに隣り合い、前記半導体チップに接続された放熱板をさらに備える、請求項15から17のいずれか1項に記載の半導体装置。

- 前記放熱板が接続された前記半導体チップを除く他の前記複数の半導体チップから発生する熱量は、前記放熱部材が接続された前記半導体チップから発生する熱量よりも小さい、請求項18に記載の半導体装置。

- 半導体パッケージ内に複数の半導体チップが搭載されるマルチチップタイプの半導体装置であって、

互いに隣り合う位置に空間を規定するように配置された複数の半導体チップと、

前記空間に設けられた放熱手段とを備え、

前記複数の半導体チップは、互いに向い合う位置において異なる大きさの表面を有する2つの半導体チップおよび隣り合った位置においてずれて配置された2つの半導体チップの少なくともいずれか一方を含む、半導体装置。 - 前記放熱手段は、冷却用流体が流れる冷却路および金属材料からなる放熱部材の少なくともいずれか一方を含む、請求項20に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111380A JP4458906B2 (ja) | 2004-04-05 | 2004-04-05 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111380A JP4458906B2 (ja) | 2004-04-05 | 2004-04-05 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005294760A true JP2005294760A (ja) | 2005-10-20 |

| JP2005294760A5 JP2005294760A5 (ja) | 2007-05-10 |

| JP4458906B2 JP4458906B2 (ja) | 2010-04-28 |

Family

ID=35327313

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004111380A Expired - Fee Related JP4458906B2 (ja) | 2004-04-05 | 2004-04-05 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4458906B2 (ja) |

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007142276A (ja) * | 2005-11-21 | 2007-06-07 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2008047894A (ja) * | 2006-08-11 | 2008-02-28 | Dongbu Hitek Co Ltd | 半導体素子及びその製造方法 |

| JP2009521115A (ja) * | 2005-12-23 | 2009-05-28 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 犠牲相互接続部を用いたオンチップ相互接続スタック冷却 |

| EP2315243A1 (fr) * | 2009-10-23 | 2011-04-27 | STmicroelectronics SA | Plaque d'interface entre circuits intégrés |

| JP2013533612A (ja) * | 2010-06-02 | 2013-08-22 | コミサリア ア レネルジ アトミク エ オウ エネルジ アルタナティヴ | 熱輸送冷媒を流すことができるチャネルを有する電子チップ、電子コンポーネント、およびこの電子チップ内蔵のスイッチングアーム |

| JP2013251545A (ja) * | 2012-05-31 | 2013-12-12 | Freescale Semiconductor Inc | 熱に敏感な半導体デバイスの熱への露出を低減するための方法および構造体 |

| JP2018018908A (ja) * | 2016-07-26 | 2018-02-01 | パナソニックIpマネジメント株式会社 | 熱電変換器 |

| JP2018067561A (ja) * | 2016-10-17 | 2018-04-26 | Tdk株式会社 | 半導体チップおよび磁気記録装置 |

| JP2020515051A (ja) * | 2017-02-06 | 2020-05-21 | エルジー イノテック カンパニー リミテッド | 熱電焼結体および熱電素子 |

| CN111584438A (zh) * | 2019-02-15 | 2020-08-25 | 爱思开海力士有限公司 | 半导体装置 |

| CN113249692A (zh) * | 2021-04-29 | 2021-08-13 | 林梅琴 | 一种大功率半导体元器件的冷却板 |

| CN115172296A (zh) * | 2021-04-05 | 2022-10-11 | Jmj韩国株式会社 | 结合具有半导体芯片的半导体部件和冷却装置的冷却系统 |

| CN119289549A (zh) * | 2024-12-10 | 2025-01-10 | 安徽农业大学 | 一种半导体制冷结构以及冷凝器 |

-

2004

- 2004-04-05 JP JP2004111380A patent/JP4458906B2/ja not_active Expired - Fee Related

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007142276A (ja) * | 2005-11-21 | 2007-06-07 | Toshiba Corp | 半導体装置及びその製造方法 |

| US7936563B2 (en) | 2005-12-23 | 2011-05-03 | Nxp B.V. | On-chip interconnect-stack cooling using sacrificial interconnect segments |

| JP2009521115A (ja) * | 2005-12-23 | 2009-05-28 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 犠牲相互接続部を用いたオンチップ相互接続スタック冷却 |

| JP2008047894A (ja) * | 2006-08-11 | 2008-02-28 | Dongbu Hitek Co Ltd | 半導体素子及びその製造方法 |

| US8704363B2 (en) | 2009-10-23 | 2014-04-22 | Stmicroelectronics S.A. | Interface plate between integrated circuits |

| FR2951871A1 (fr) * | 2009-10-23 | 2011-04-29 | St Microelectronics Sa | Plaque d'interface entre circuits integres |

| EP2315243A1 (fr) * | 2009-10-23 | 2011-04-27 | STmicroelectronics SA | Plaque d'interface entre circuits intégrés |

| JP2013533612A (ja) * | 2010-06-02 | 2013-08-22 | コミサリア ア レネルジ アトミク エ オウ エネルジ アルタナティヴ | 熱輸送冷媒を流すことができるチャネルを有する電子チップ、電子コンポーネント、およびこの電子チップ内蔵のスイッチングアーム |

| JP2013251545A (ja) * | 2012-05-31 | 2013-12-12 | Freescale Semiconductor Inc | 熱に敏感な半導体デバイスの熱への露出を低減するための方法および構造体 |

| JP2018018908A (ja) * | 2016-07-26 | 2018-02-01 | パナソニックIpマネジメント株式会社 | 熱電変換器 |

| JP2018067561A (ja) * | 2016-10-17 | 2018-04-26 | Tdk株式会社 | 半導体チップおよび磁気記録装置 |

| JP2020515051A (ja) * | 2017-02-06 | 2020-05-21 | エルジー イノテック カンパニー リミテッド | 熱電焼結体および熱電素子 |

| JP7293116B2 (ja) | 2017-02-06 | 2023-06-19 | エルジー イノテック カンパニー リミテッド | 熱電焼結体および熱電素子 |

| US11937506B2 (en) | 2017-02-06 | 2024-03-19 | Lg Innotek Co., Ltd. | Thermoelectric element |

| US12274171B2 (en) | 2017-02-06 | 2025-04-08 | Lg Innotek Co., Ltd. | Thermoelectric element |

| CN111584438A (zh) * | 2019-02-15 | 2020-08-25 | 爱思开海力士有限公司 | 半导体装置 |

| CN115172296A (zh) * | 2021-04-05 | 2022-10-11 | Jmj韩国株式会社 | 结合具有半导体芯片的半导体部件和冷却装置的冷却系统 |

| CN113249692A (zh) * | 2021-04-29 | 2021-08-13 | 林梅琴 | 一种大功率半导体元器件的冷却板 |

| CN119289549A (zh) * | 2024-12-10 | 2025-01-10 | 安徽农业大学 | 一种半导体制冷结构以及冷凝器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4458906B2 (ja) | 2010-04-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102347316B (zh) | 三维集成电路结构 | |

| US7663230B2 (en) | Methods of forming channels on an integrated circuit die and die cooling systems including such channels | |

| US8030113B2 (en) | Thermoelectric 3D cooling | |

| EP2304792B1 (en) | Active thermal control for stacked ic devices | |

| TWI529877B (zh) | 半導體裝置 | |

| US8674491B2 (en) | Semiconductor device | |

| JP4458906B2 (ja) | 半導体装置 | |

| US20120063090A1 (en) | Cooling mechanism for stacked die package and method of manufacturing the same | |

| TWI878643B (zh) | 具有熱增強的三維ic封裝 | |

| CN101427368A (zh) | 电渗透泵和微通道 | |

| KR20160021752A (ko) | 집적된 열전 냉각 | |

| CN115565967A (zh) | 半导体结构 | |

| JP4942807B2 (ja) | フリップチップ半導体素子の熱電冷却器 | |

| CN105938821A (zh) | 热增强的散热器 | |

| CN101292348A (zh) | 具有增强的热和器件性能的可堆叠晶片或管芯封装 | |

| CN115579336A (zh) | 三维集成结构及其制作方法 | |

| CN110277361A (zh) | 热辐射装置、包括其的半导体封装件和半导体装置 | |

| CN119517867A (zh) | 半导体装置、集成电路器件及其制造方法 | |

| CN102194811B (zh) | 热电装置 | |

| JPH10233473A (ja) | 半導体素子の放熱構造とその放熱方法 | |

| CN110660759B (zh) | 散热结构及制造散热结构的方法 | |

| CN116884929B (zh) | 一种三维芯片封装结构及其制造方法 | |

| TW202527264A (zh) | 封裝結構、冷卻特徵、用於冷卻封裝結構之方法 | |

| CN121054495A (zh) | 形成封装结构的方法、以及封装结构 | |

| CN119317343A (zh) | 热电致冷芯片及其制作方法和封装结构 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070316 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070316 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090713 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090818 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091015 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100202 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100209 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130219 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130219 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140219 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |