JP2005285161A - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP2005285161A JP2005285161A JP2004093387A JP2004093387A JP2005285161A JP 2005285161 A JP2005285161 A JP 2005285161A JP 2004093387 A JP2004093387 A JP 2004093387A JP 2004093387 A JP2004093387 A JP 2004093387A JP 2005285161 A JP2005285161 A JP 2005285161A

- Authority

- JP

- Japan

- Prior art keywords

- current

- transistor

- current path

- output node

- output nodes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Dram (AREA)

- Static Random-Access Memory (AREA)

- Read Only Memory (AREA)

Abstract

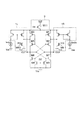

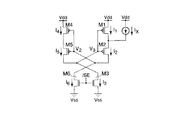

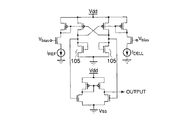

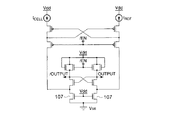

【解決手段】 相補の出力ノード(OUT,/OUT)と、相補の出力ノード(OUT,/OUT)間に初期電位差を、相補の出力ノード(OUT,/OUT)それぞれへの入力電流(IREF,IDATA)の入力電流量の差に応じて生じさせる電流−電圧変換部(M1,M2,M4,M5)と、相補の出力ノード(OUT,/OUT)それぞれのバイアス点をシフトし、相補の出力ノード(OUT,/OUT)間に生じた初期電位差を増幅する増幅部(M3,M6)と、相補の出力ノード(OUT,/OUT)間の増幅された電位差に基づいて、相補の出力ノードそれぞれの出力レベルを確定する出力レベル確定部(M1,M2,M4,M5,M7,M8)とを具備する。

【選択図】 図1

Description

Claims (4)

- 相補の出力ノードと、

前記相補の出力ノード間に初期電位差を、前記相補の出力ノードそれぞれへの入力電流の入力電流量の差に応じて生じさせる電流−電圧変換部と、

前記初期電位差を生じた相補の出力ノードそれぞれのバイアス点をシフトし、前記相補の出力ノード間に生じた初期電位差を増幅する増幅部と、

前記相補の出力ノード間の増幅された電位差に基づいて、前記相補の出力ノードそれぞれの出力レベルを確定する出力レベル確定部と

を具備することを特徴とする半導体集積回路装置。 - 前記増幅部は、

前記相補の出力ノードの一方に電流通路の一端を接続した第1のトランジスタと、

前記相補の出力ノードの他方に電流通路の一端を接続した第2のトランジスタとを含み、

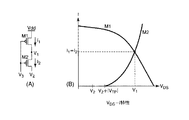

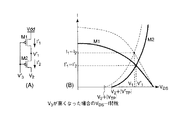

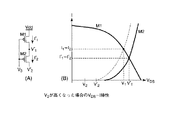

前記相補の出力ノード間の初期電位差は、前記第1のトランジスタ、及び前記第2のトランジスタそれぞれを線形領域で動作させて生じさせ、

前記初期電位差を生じた相補の出力ノードそれぞれのバイアス点は、前記第1のトランジスタ、及び前記第2のトランジスタそれぞれを動作状態から遮断状態の方向に変化させてシフトさせることを特徴とする請求項1に記載の半導体集積回路装置。 - 前記入力電流は、前記相補の出力ノードそれぞれに、カレントミラー回路のレプリカ電流を用いて入力されることを特徴とする請求項1及び請求項2いずれかに記載の半導体集積回路装置。

- 電流通路の一端に、第1の電源電位を受け、ゲートを第1の出力ノードに接続した第1導電型の第1のトランジスタと、

電流通路の一端に、前記第1のトランジスタからの電流と第1の入力電流とを受け、電流通路の他端を第2の出力ノードに接続し、ゲートを前記第1の出力ノードに接続した第1導電型の第2のトランジスタと、

電流通路の一端に、前記第1の電源電位を受け、ゲートを前記第2の出力ノードに接続した第1導電型の第3のトランジスタと、

電流通路の一端に、前記第3のトランジスタからの電流と第2の入力電流とを受け、電流通路の他端を前記第1の出力ノードに接続し、ゲートを前記第2の出力ノードに接続した第1導電型の第4のトランジスタと、

電流通路の一端に、前記第1の電源電位とは異なる第2の電源電位を受け、前記電流通路の他端を前記第2の出力ノードに接続し、ゲートに制御信号を受ける第2導電型の第5のトランジスタと、

電流通路の一端に、前記第2の電源電位を受け、前記電流通路の他端を前記第1の出力ノードに接続し、ゲートに前記制御信号を受ける第2導電型の第6のトランジスタと、

電流通路の一端に、前記第2の電源電位を受け、前記電流通路の他端を前記第2の出力ノードに接続し、ゲートを前記第1の出力ノードに接続した第2導電型の第7のトランジスタと、

電流通路の一端に、前記第2の電源電位を受け、前記電流通路の他端を前記第1の出力ノードに接続し、ゲートを前記第2の出力ノードに接続した第2導電型の第8のトランジスタと

を具備することを特徴とする半導体集積回路装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004093387A JP2005285161A (ja) | 2004-03-26 | 2004-03-26 | 半導体集積回路装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004093387A JP2005285161A (ja) | 2004-03-26 | 2004-03-26 | 半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005285161A true JP2005285161A (ja) | 2005-10-13 |

| JP2005285161A5 JP2005285161A5 (ja) | 2007-04-19 |

Family

ID=35183386

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004093387A Pending JP2005285161A (ja) | 2004-03-26 | 2004-03-26 | 半導体集積回路装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005285161A (ja) |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007172775A (ja) * | 2005-12-26 | 2007-07-05 | Toshiba Corp | センスアンプ及び半導体記憶装置 |

| JP2007323706A (ja) * | 2006-05-30 | 2007-12-13 | Toshiba Corp | センスアンプ |

| JP2008047205A (ja) * | 2006-08-14 | 2008-02-28 | Toshiba Corp | 半導体記憶装置 |

| US7495963B2 (en) | 2006-04-06 | 2009-02-24 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US7495965B2 (en) | 2006-05-17 | 2009-02-24 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US7573744B2 (en) | 2006-09-29 | 2009-08-11 | Kabushiki Kaisha Toshiba | Semiconductor memory device having different capacity areas |

| JP2010092562A (ja) * | 2008-10-10 | 2010-04-22 | Toshiba Corp | センスアンプ制御回路 |

| JP2012185892A (ja) * | 2011-03-07 | 2012-09-27 | Toshiba Corp | 半導体記憶装置 |

| US8537595B2 (en) | 2008-08-29 | 2013-09-17 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US9047946B2 (en) | 2011-08-31 | 2015-06-02 | Panasonic Intellectual Property Management Co., Ltd. | Read circuit and non-volatile memory using the read circuit |

| US9368197B2 (en) | 2014-01-29 | 2016-06-14 | Kabushiki Kaisha Toshiba | Memory system |

| JP2016225004A (ja) * | 2015-06-01 | 2016-12-28 | 凸版印刷株式会社 | 半導体集積回路 |

-

2004

- 2004-03-26 JP JP2004093387A patent/JP2005285161A/ja active Pending

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7522462B2 (en) | 2005-12-26 | 2009-04-21 | Kabushiki Kaisha Toshiba | Sense amplifier and semiconductor memory device with the same |

| JP2007172775A (ja) * | 2005-12-26 | 2007-07-05 | Toshiba Corp | センスアンプ及び半導体記憶装置 |

| US7495963B2 (en) | 2006-04-06 | 2009-02-24 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US7495965B2 (en) | 2006-05-17 | 2009-02-24 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US7787320B2 (en) | 2006-05-30 | 2010-08-31 | Kabushiki Kaisha Toshiba | Sense amplifier |

| JP2007323706A (ja) * | 2006-05-30 | 2007-12-13 | Toshiba Corp | センスアンプ |

| US7649792B2 (en) | 2006-05-30 | 2010-01-19 | Kabushiki Kaisha Toshiba | Sense amplifier |

| JP2008047205A (ja) * | 2006-08-14 | 2008-02-28 | Toshiba Corp | 半導体記憶装置 |

| US7573744B2 (en) | 2006-09-29 | 2009-08-11 | Kabushiki Kaisha Toshiba | Semiconductor memory device having different capacity areas |

| US8537595B2 (en) | 2008-08-29 | 2013-09-17 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US8067963B2 (en) | 2008-10-10 | 2011-11-29 | Kabushiki Kaisha Toshiba | Sense-amplifier control circuit and controlling method of sense amplifier |

| JP2010092562A (ja) * | 2008-10-10 | 2010-04-22 | Toshiba Corp | センスアンプ制御回路 |

| JP2012185892A (ja) * | 2011-03-07 | 2012-09-27 | Toshiba Corp | 半導体記憶装置 |

| US8830758B2 (en) | 2011-03-07 | 2014-09-09 | Kabushiki Kaisha Toshiba | Semiconductor storage device |

| US9047946B2 (en) | 2011-08-31 | 2015-06-02 | Panasonic Intellectual Property Management Co., Ltd. | Read circuit and non-volatile memory using the read circuit |

| US9368197B2 (en) | 2014-01-29 | 2016-06-14 | Kabushiki Kaisha Toshiba | Memory system |

| US9691474B2 (en) | 2014-01-29 | 2017-06-27 | Kabushiki Kaisha Toshiba | Memory system |

| JP2016225004A (ja) * | 2015-06-01 | 2016-12-28 | 凸版印刷株式会社 | 半導体集積回路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7038963B2 (en) | Current sense amplifier circuits having a bias voltage node for adjusting input resistance | |

| US9460760B2 (en) | Data-dependent self-biased differential sense amplifier | |

| US7573756B2 (en) | Sense amplifiers and semiconductor memory devices for reducing power consumption and methods for operating the same | |

| CN107103922B (zh) | 具有偏移补偿的动态感测放大器 | |

| TWI409824B (zh) | 使用動態參考電壓之單端感應放大器及其運作方法 | |

| JP2005285161A (ja) | 半導体集積回路装置 | |

| US6483351B2 (en) | Input-output line sense amplifier having small current consumption and direct current | |

| US6865129B2 (en) | Differential amplifier circuit with high amplification factor and semiconductor memory device using the differential amplifier circuit | |

| CN1937071B (zh) | 用于存储器系统的高性能读出放大器及相应的方法 | |

| US7405987B1 (en) | Low voltage, high gain current/voltage sense amplifier with improved read access time | |

| US8339871B2 (en) | Voltage sensing circuit capable of controlling a pump voltage stably generated in a low voltage environment | |

| KR100419015B1 (ko) | 전류 센스 증폭기 | |

| US11120862B2 (en) | Non-volatile memory read method for improving read margin | |

| US6721218B2 (en) | Semiconductor memory device and data read method thereof | |

| US8942053B2 (en) | Generating and amplifying differential signals | |

| JP2000306385A (ja) | 半導体メモリ装置の相補型差動入力バッファ | |

| US6243314B1 (en) | Apparatus for sensing a current direction of an input signal and amplifying the sensed input signal in semiconductor memory device | |

| US20070069767A1 (en) | Differential amplifier | |

| KR20090072337A (ko) | 펌핑전압 검출회로 | |

| KR102652188B1 (ko) | 전류 래치 센스 앰프 및 메모리 장치 | |

| US6829187B2 (en) | Memory device | |

| US20070164791A1 (en) | Low voltage detect and/or regulation circuit | |

| JP2005339704A (ja) | 強誘電体メモリ | |

| US7759981B2 (en) | Amplifying circuit of semiconductor integrated circuit | |

| KR100917640B1 (ko) | 펌핑전압 검출회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20070115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091019 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091104 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091221 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100126 |