JP2005181523A - 設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム - Google Patents

設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム Download PDFInfo

- Publication number

- JP2005181523A JP2005181523A JP2003419600A JP2003419600A JP2005181523A JP 2005181523 A JP2005181523 A JP 2005181523A JP 2003419600 A JP2003419600 A JP 2003419600A JP 2003419600 A JP2003419600 A JP 2003419600A JP 2005181523 A JP2005181523 A JP 2005181523A

- Authority

- JP

- Japan

- Prior art keywords

- planar shape

- design pattern

- pattern

- design

- calculating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/398—Design verification or optimisation, e.g. using design rule check [DRC], layout versus schematics [LVS] or finite element methods [FEM]

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

【解決手段】 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する設計パターン補正方法であって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出し、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出し、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出し、第3の平面形状から得られる評価量が所定値を満たすか否かを判定し、評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する。

【選択図】 図4

Description

図1に、単一レイヤーに対してOPC検証を行った結果を示す。これは、メタル配線(M1)での一例であり、設計パターン(ターゲットパターン)のエッジからのずれ量を黒塗りで示している。図2に、本実施形態による複数レイヤーを考慮したOPC検証手法を示す。これは、第1の設計パターンに基づく第1のレイヤーとしてのM1と第2の設計パターンに基づく第2のレイヤーとしてのコンタクトホール(CS)の一例であり、プロセス条件は共に露光量,焦点位置共にベスト条件での結果である。

(1)メタル配線の幅を大きくする

(2)コンタクトホールの穴径を大きくする

などの方法がある。

1.近傍に別のビアV2が存在するかどうか

2.ビアV2はビアV1に対してどういう方向に存在するのか

3.ビアV2とビアV1とは接触してもよいのかどうか(同電位に落ちるビアであれば

接触しても問題はない)

を判断し、その結果に基づいて、ビアV1を大きくするための方向と大きさとを決める必要がある。

次に、本発明の第2の実施形態について説明する。

2.面積公差の見直し

3.実効面積を増加させる

上記の1.では、目標とする合わせ精度ターゲットを見直す必要があり、2.では、デバイススペックから規定された面積公差が本当に正しいかどうかを再度調査する必要があるため、これらの見直しには比較的時間を要する。最も簡便な方法は3.であり、リングパターンとメタルパターンとのAND領域の実効面積分布を全体的に増加させることである。これを行うためには、メタルフリンジ量を増加させる方法、若しくはコンタクト面積を増大させる方法があるが、コンタクトサイズを変えると、他のレイヤー(例えば、ゲート層)との位置関係を考慮する必要があるので、メタルフリンジ量を増加させる方法が現実的である。

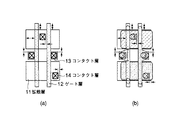

図11及び図12は、本発明の第3の実施形態を説明するための図であり、それぞれの(a)は設計レイアウト、(b)はウェハ上での仕上がり平面形状を示している。また、図中の11は拡散層、12はゲート層、13,14はコンタクト層を示している。なお、図12(a)(b)において、上図は距離aが短い場合、下図は距離aが長い場合を示している。

2.拡散層の仕上がり平面形状を算出する。

3.ゲート層の仕上がり平面形状のうち、拡散との重なり部分を引き算(ブーリアン演算ではNOTに対応)する。

5.4で出力された長さが所定の範囲内にあるかどうかを判定する。

6.所定範囲内に入っていれば、チップ面積を測定する。

8.現在のbの値でチップ面積が所定値を満たしていなければ、さらにbの値を小さくし(チップ面積を小さくして)1から再度検討する。

9.5で所定の長さの範囲内に入っていない場合には、図12のaを大きくする、もしくはbの長さを大きくするといったレイアウト作成、修正を行う。

10.9でできたレイアウトを1から検証する。

なお、本発明は上述した各実施形態に限定されるものではない。

以上説明したように本発明の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する設計パターン補正方法であって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する工程と、を含むことを特徴とする。

12…ゲート層

13,14…コンタクト層

21,22…メタル配線

31,33…ビア

Claims (9)

- 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する方法であって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、

前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する工程と、

を含むことを特徴とする設計パターン補正方法。 - 第1及び第2の平面形状のうち、少なくとも一方は対応する設計パターンに対して光近接効果補正を含むリサイズ処理を行った後のマスクパターンから算出されることを特徴とする請求項1記載の設計パターン補正方法。

- 前記ブーリアン演算処理を、第1及び第2の平面形状の少なくとも一方をリサイズ若しくは移動させた後に行うことを特徴とする請求項1記載の設計パターン補正方法。

- 第1又は第2の平面形状は、露光装置の露光波長,レンズ開口数,照明形状,マスク寸法,露光量,焦点位置,収差,合わせずれ量,レジスト拡散長のうち少なくとも1つを含むプロセス条件下でそれぞれ算出されることを特徴とする請求項1記載の設計パターン補正方法。

- 前記各工程を、第3の平面形状から得られる評価量が前記所定値を満たすまで繰り返し行うことを特徴とする請求項1記載の設計パターン補正方法。

- 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮したマスクパターン作成方法であって、

第1のレイヤーの第1の設計パターンに対して少なくとも1回のリサイズ処理を含む第1のマスクパターンを作成する工程と、

第2のレイヤーの第2の設計パターンに対して少なくとも1回のリサイズ処理を含む第2のマスクパターンを作成する工程と、

第1のマスクパターンから第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、

第2のマスクパターンから第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、

前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2のマスクパターンの少なくとも一方を修正する工程と、

を含むことを特徴とするマスクパターン作成方法。 - 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正するシステムであって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する手段と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手段と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手段と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手段と、

前記判定手段により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手段と、

を具備してなることを特徴とする設計パターン補正システム。 - 請求項1〜6の何れかに記載の設計パターン補正方法を用いて補正された設計パターンを基に半導体基板上に集積回路パターンを形成することを特徴とする半導体装置の製造方法。

- 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して、コンピュータ制御の下に設計パターンを補正するための設計パターン補正プログラムであって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する手順と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手順と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手順と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手順と、

前記判定手順により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手順と、

をコンピュータに実行させるためのコンピュータ読み取り可能な設計パターン補正プログラム。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003419600A JP2005181523A (ja) | 2003-12-17 | 2003-12-17 | 設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム |

| US11/012,613 US7266801B2 (en) | 2003-12-17 | 2004-12-16 | Design pattern correction method and mask pattern producing method |

| TW093139159A TWI256527B (en) | 2003-12-17 | 2004-12-16 | Design pattern correction method, mask producing method and semiconductor device producing method |

| CN2004101013575A CN1630032B (zh) | 2003-12-17 | 2004-12-17 | 设计图形校正方法、掩模制造方法及半导体器件制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003419600A JP2005181523A (ja) | 2003-12-17 | 2003-12-17 | 設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005181523A true JP2005181523A (ja) | 2005-07-07 |

| JP2005181523A5 JP2005181523A5 (ja) | 2005-08-25 |

Family

ID=34781449

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003419600A Pending JP2005181523A (ja) | 2003-12-17 | 2003-12-17 | 設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7266801B2 (ja) |

| JP (1) | JP2005181523A (ja) |

| CN (1) | CN1630032B (ja) |

| TW (1) | TWI256527B (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7673258B2 (en) | 2006-03-31 | 2010-03-02 | Kabushiki Kaisha Toshiba | Design data creating method, design data creating program product, and manufacturing method of semiconductor device |

| JP2011076124A (ja) * | 2009-09-29 | 2011-04-14 | Fujitsu Semiconductor Ltd | 検証装置、検証方法及び検証プログラム |

| JP2012014489A (ja) * | 2010-07-01 | 2012-01-19 | Renesas Electronics Corp | 半導体装置のレイアウト検証方法と装置及びプログラム |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7448012B1 (en) | 2004-04-21 | 2008-11-04 | Qi-De Qian | Methods and system for improving integrated circuit layout |

| JP4528558B2 (ja) * | 2004-05-28 | 2010-08-18 | 株式会社東芝 | パターンのデータ作成方法、及びパターン検証手法 |

| US7470492B2 (en) * | 2004-10-29 | 2008-12-30 | Intel Corporation | Process window-based correction for photolithography masks |

| JP4713962B2 (ja) * | 2005-06-27 | 2011-06-29 | 株式会社東芝 | パターン作成方法及び半導体装置製造方法 |

| JP4817746B2 (ja) * | 2005-07-27 | 2011-11-16 | 株式会社東芝 | 半導体装置の設計データ処理方法、そのプログラム、及び半導体装置の製造方法 |

| JP2007240949A (ja) * | 2006-03-09 | 2007-09-20 | Elpida Memory Inc | マスクデータ作成方法及びマスク |

| JP2008175959A (ja) * | 2007-01-17 | 2008-07-31 | Toshiba Corp | フォトマスク製造方法、及び半導体装置の製造方法 |

| JP4745256B2 (ja) * | 2007-01-26 | 2011-08-10 | 株式会社東芝 | パターン作成方法、パターン作成・検証プログラム、および半導体装置の製造方法 |

| JP4254871B2 (ja) * | 2007-02-09 | 2009-04-15 | ソニー株式会社 | 光近接効果補正方法、光近接効果補正装置、光近接効果補正プログラム、半導体装置の製造方法、パターン設計制約策定方法および光近接効果補正条件算出方法 |

| US20100023916A1 (en) * | 2007-07-31 | 2010-01-28 | Chew Marko P | Model Based Hint Generation For Lithographic Friendly Design |

| US8099685B2 (en) * | 2007-07-31 | 2012-01-17 | Mentor Graphics Corporation | Model based microdevice design layout correction |

| US8146023B1 (en) * | 2008-10-02 | 2012-03-27 | Kla-Tenor Corporation | Integrated circuit fabrication process convergence |

| JP2010164849A (ja) * | 2009-01-16 | 2010-07-29 | Toshiba Corp | パターンデータ作成方法およびパターンデータ作成プログラム |

| CN102809899A (zh) * | 2011-05-31 | 2012-12-05 | 无锡华润上华半导体有限公司 | 一种对位参数计算方法 |

| JP2013045070A (ja) * | 2011-08-26 | 2013-03-04 | Toshiba Corp | 原版評価方法、プログラム、および原版製造方法 |

| US8486587B2 (en) | 2011-12-20 | 2013-07-16 | United Microelectronics Corp. | Method for correcting layout pattern and method for manufacturing photomask |

| US8739078B2 (en) | 2012-01-18 | 2014-05-27 | International Business Machines Corporation | Near-neighbor trimming of dummy fill shapes with built-in optical proximity corrections for semiconductor applications |

| CN103576443B (zh) * | 2012-08-03 | 2016-05-11 | 无锡华润上华半导体有限公司 | 一种光学临近矫正方法 |

| US8977988B2 (en) | 2013-04-09 | 2015-03-10 | United Microelectronics Corp. | Method of optical proximity correction for modifying line patterns and integrated circuits with line patterns modified by the same |

| US9454635B2 (en) * | 2014-01-25 | 2016-09-27 | Synopsys, Inc. | Virtual layer generation during failure analysis |

| US10474781B2 (en) | 2014-05-24 | 2019-11-12 | Synopsys, Inc. | Virtual hierarchical layer usage |

| TWI612373B (zh) * | 2014-07-24 | 2018-01-21 | 聯華電子股份有限公司 | 光學鄰近修正驗證系統及其驗證方法 |

| US10444622B2 (en) | 2018-02-09 | 2019-10-15 | United Microelectronics Corp. | Method for generating masks for manufacturing of a semiconductor structure |

| CN112987485B (zh) * | 2019-12-18 | 2023-03-21 | 中芯国际集成电路制造(北京)有限公司 | 掩膜版图形的修正方法、掩膜版和半导体结构的形成方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US641542A (en) * | 1899-10-04 | 1900-01-16 | Adrian De Piniec-Mallet | Bedstead. |

| JP3328323B2 (ja) * | 1992-07-20 | 2002-09-24 | 株式会社日立製作所 | 位相シフトマスクの製造方法および半導体集積回路装置の製造方法 |

| US6470489B1 (en) * | 1997-09-17 | 2002-10-22 | Numerical Technologies, Inc. | Design rule checking system and method |

| US6316163B1 (en) * | 1997-10-01 | 2001-11-13 | Kabushiki Kaisha Toshiba | Pattern forming method |

| JP3892205B2 (ja) * | 2000-04-14 | 2007-03-14 | 松下電器産業株式会社 | レイアウトコンパクション方法 |

| US6425113B1 (en) | 2000-06-13 | 2002-07-23 | Leigh C. Anderson | Integrated verification and manufacturability tool |

| JP4077141B2 (ja) | 2000-06-30 | 2008-04-16 | 株式会社東芝 | デザインルール作成方法、デザインルール作成システム及び記録媒体 |

| JP3914085B2 (ja) | 2002-04-11 | 2007-05-16 | 株式会社東芝 | プロセスパラメータの作成方法、プロセスパラメータの作成システム及び半導体装置の製造方法 |

| TWI252516B (en) * | 2002-03-12 | 2006-04-01 | Toshiba Corp | Determination method of process parameter and method for determining at least one of process parameter and design rule |

| US6745372B2 (en) * | 2002-04-05 | 2004-06-01 | Numerical Technologies, Inc. | Method and apparatus for facilitating process-compliant layout optimization |

| JP4190796B2 (ja) * | 2002-04-24 | 2008-12-03 | Necエレクトロニクス株式会社 | 露光原版の作成方法 |

| US20050085085A1 (en) * | 2003-10-17 | 2005-04-21 | Yan Borodovsky | Composite patterning with trenches |

| US20050088633A1 (en) * | 2003-10-24 | 2005-04-28 | Intel Corporation | Composite optical lithography method for patterning lines of unequal width |

| US20060051680A1 (en) * | 2004-09-03 | 2006-03-09 | Tritchkov Alexander V | Combining image imbalance compensation and optical proximity correction in designing phase shift masks |

-

2003

- 2003-12-17 JP JP2003419600A patent/JP2005181523A/ja active Pending

-

2004

- 2004-12-16 TW TW093139159A patent/TWI256527B/zh active

- 2004-12-16 US US11/012,613 patent/US7266801B2/en active Active

- 2004-12-17 CN CN2004101013575A patent/CN1630032B/zh not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7673258B2 (en) | 2006-03-31 | 2010-03-02 | Kabushiki Kaisha Toshiba | Design data creating method, design data creating program product, and manufacturing method of semiconductor device |

| JP2011076124A (ja) * | 2009-09-29 | 2011-04-14 | Fujitsu Semiconductor Ltd | 検証装置、検証方法及び検証プログラム |

| JP2012014489A (ja) * | 2010-07-01 | 2012-01-19 | Renesas Electronics Corp | 半導体装置のレイアウト検証方法と装置及びプログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| US7266801B2 (en) | 2007-09-04 |

| US20050235245A1 (en) | 2005-10-20 |

| CN1630032B (zh) | 2010-05-12 |

| CN1630032A (zh) | 2005-06-22 |

| TW200532398A (en) | 2005-10-01 |

| TWI256527B (en) | 2006-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005181523A (ja) | 設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム | |

| JP4488727B2 (ja) | 設計レイアウト作成方法、設計レイアウト作成システム、マスクの製造方法、半導体装置の製造方法、及び設計レイアウト作成プログラム | |

| US6691297B1 (en) | Method for planning layout for LSI pattern, method for forming LSI pattern and method for generating mask data for LSI | |

| US7617475B2 (en) | Method of manufacturing photomask and method of repairing optical proximity correction | |

| US11138362B2 (en) | Integrated circuit layout method and system | |

| US7526748B2 (en) | Design pattern data preparing method, mask pattern data preparing method, mask manufacturing method, semiconductor device manufacturing method, and program recording medium | |

| KR100780775B1 (ko) | 자기 조립 더미 패턴이 삽입된 회로 레이아웃을 이용한반도체 소자 제조 방법 | |

| JP4817746B2 (ja) | 半導体装置の設計データ処理方法、そのプログラム、及び半導体装置の製造方法 | |

| US7600213B2 (en) | Pattern data verification method, pattern data creation method, exposure mask manufacturing method, semiconductor device manufacturing method, and computer program product | |

| JP4528558B2 (ja) | パターンのデータ作成方法、及びパターン検証手法 | |

| US11741288B2 (en) | Routing-resource-improving method of generating layout diagram, system for same and semiconductor device | |

| US11030372B2 (en) | Method for generating layout diagram including cell having pin patterns and semiconductor device based on same | |

| JP2006058413A (ja) | マスクの形成方法 | |

| US7614026B2 (en) | Pattern forming method, computer program thereof, and semiconductor device manufacturing method using the computer program | |

| JP2004004941A (ja) | Lsi用マスクデータの作成方法及びlsi用パターンの形成方法 | |

| US20220335193A1 (en) | Circuit Layout | |

| CN116710843A (zh) | 用于自由形状的光学邻近校正 | |

| CN219303642U (zh) | 半导体装置 | |

| US20230259686A1 (en) | Semiconductor device and method and system of arranging patterns of the same | |

| US20240070364A1 (en) | Circuit cells having power grid stubs | |

| US20230222278A1 (en) | Method for generating routing structure of semiconductor device | |

| KR100834234B1 (ko) | 반도체 장치 제조용 마스크 패턴 결정 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050420 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050420 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080401 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080520 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080722 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080909 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081110 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20081224 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20090130 |