JP2004222296A - クロック信号発生システム - Google Patents

クロック信号発生システム Download PDFInfo

- Publication number

- JP2004222296A JP2004222296A JP2004007252A JP2004007252A JP2004222296A JP 2004222296 A JP2004222296 A JP 2004222296A JP 2004007252 A JP2004007252 A JP 2004007252A JP 2004007252 A JP2004007252 A JP 2004007252A JP 2004222296 A JP2004222296 A JP 2004222296A

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- signal

- clock

- signals

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

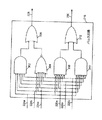

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/08—Clock generators with changeable or programmable clock frequency

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K21/00—Details of pulse counters or frequency dividers

- H03K21/08—Output circuits

- H03K21/10—Output circuits comprising logic circuits

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Manipulation Of Pulses (AREA)

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/346,689 US6856184B2 (en) | 2003-01-15 | 2003-01-15 | Clock divider circuit |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004222296A true JP2004222296A (ja) | 2004-08-05 |

| JP2004222296A5 JP2004222296A5 (enExample) | 2007-02-22 |

Family

ID=31715568

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004007252A Withdrawn JP2004222296A (ja) | 2003-01-15 | 2004-01-14 | クロック信号発生システム |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6856184B2 (enExample) |

| JP (1) | JP2004222296A (enExample) |

| GB (1) | GB2397418B (enExample) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9337948B2 (en) | 2003-06-10 | 2016-05-10 | Alexander I. Soto | System and method for performing high-speed communications over fiber optical networks |

| US7715386B2 (en) * | 2007-03-15 | 2010-05-11 | Microsoft Corporation | Reducing network traffic to teredo server |

| US7764691B2 (en) * | 2007-03-15 | 2010-07-27 | Microsoft Corporation | Allowing IPv4 clients to communicate using teredo addresses when both clients are behind a NAT |

| US8194683B2 (en) * | 2007-03-30 | 2012-06-05 | Microsoft Corporation | Teredo connectivity between clients behind symmetric NATs |

| GB2450564B (en) * | 2007-06-29 | 2011-03-02 | Imagination Tech Ltd | Clock frequency adjustment for semi-conductor devices |

| US8134389B2 (en) * | 2010-03-25 | 2012-03-13 | Apple Inc. | Programmable frequency divider |

| KR101849571B1 (ko) * | 2011-02-22 | 2018-05-31 | 엘지디스플레이 주식회사 | 게이트 구동회로 |

| US8604858B2 (en) * | 2011-02-22 | 2013-12-10 | Lg Display Co., Ltd. | Gate driving circuit |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4945229A (en) | 1988-12-29 | 1990-07-31 | Thomas & Betts Corporation | Fiber optic receiver and transceiver |

| US5055800A (en) * | 1990-04-30 | 1991-10-08 | Motorola, Inc. | Fractional n/m synthesis |

| EP0541840B1 (en) * | 1991-11-11 | 1993-07-14 | Hewlett-Packard GmbH | Formatter circuit |

| US5353311A (en) * | 1992-01-09 | 1994-10-04 | Nec Corporation | Radio transmitter |

| US5287296A (en) * | 1992-04-22 | 1994-02-15 | At&T Bell Laboratories | Clock generators having programmable fractional frequency division |

| KR100296832B1 (ko) * | 1992-11-13 | 2001-10-24 | 요트.게.아. 롤페즈 | 이산시간신호처리시스템 |

| US5528181A (en) * | 1994-11-02 | 1996-06-18 | Advanced Micro Devices, Inc. | Hazard-free divider circuit |

| US5682605A (en) * | 1994-11-14 | 1997-10-28 | 989008 Ontario Inc. | Wireless communication system |

| JPH09312635A (ja) | 1996-05-21 | 1997-12-02 | Nec Yonezawa Ltd | クロック信号伝送装置 |

| US6201820B1 (en) | 1997-03-05 | 2001-03-13 | Silkroad, Inc. | Optically modulated laser beam transceiver |

| DE19719547C1 (de) * | 1997-05-09 | 1998-11-12 | Lucent Tech Network Sys Gmbh | Digitaler Oszillator |

| US6487674B1 (en) * | 2000-03-08 | 2002-11-26 | Cirrus Logic, Inc. | Single wire interface for an analog to digital converter |

| US6456164B1 (en) * | 2001-03-05 | 2002-09-24 | Koninklijke Philips Electronics N.V. | Sigma delta fractional-N frequency divider with improved noise and spur performance |

| US6404840B1 (en) * | 2001-06-25 | 2002-06-11 | Agere Systems Inc. | Variable frequency divider |

-

2003

- 2003-01-15 US US10/346,689 patent/US6856184B2/en not_active Expired - Fee Related

-

2004

- 2004-01-06 GB GB0400161A patent/GB2397418B/en not_active Expired - Fee Related

- 2004-01-14 JP JP2004007252A patent/JP2004222296A/ja not_active Withdrawn

- 2004-07-15 US US10/892,802 patent/US6914469B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20040257138A1 (en) | 2004-12-23 |

| GB0400161D0 (en) | 2004-02-11 |

| US6856184B2 (en) | 2005-02-15 |

| US20040135615A1 (en) | 2004-07-15 |

| GB2397418B (en) | 2006-09-27 |

| US6914469B2 (en) | 2005-07-05 |

| GB2397418A (en) | 2004-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2174311B1 (en) | Remote control signaling infrared generator | |

| US8581529B2 (en) | Vibration motor driving apparatus using a serial interface | |

| JP2009528015A (ja) | 自己補正式デジタル・パルス幅変調器(dpwm) | |

| CN101395771B (zh) | 以对温度变化、老化和其它效用免疫的方式驱动激光二极管 | |

| JP2007104106A (ja) | 送受信装置 | |

| JP2004222296A (ja) | クロック信号発生システム | |

| JP5343966B2 (ja) | クロック信号分周回路および方法 | |

| KR20190065389A (ko) | 디바이스들의 멀티-디바이스 동기화를 위한 인코딩 | |

| JP2005304017A (ja) | パルス幅変調システムおよびパルス幅変調方法 | |

| US20020176138A1 (en) | Infrared encoder/decoder having hardware and software data rate selection | |

| JP2621414B2 (ja) | コードレスキーボードを有する情報処理装置 | |

| JP3790245B2 (ja) | 無線センサ・ネットワーク・システムの通信モジュール及び通信方法 | |

| CN101001095B (zh) | 可变带宽自动增益控制装置以及方法 | |

| CN115064133B (zh) | 多屏显示装置及其驱动方法 | |

| CN107395202B (zh) | 一种提升高速dac工作稳定度的结构及方法 | |

| JP4464605B2 (ja) | 光送信装置及びそれに用いられる符号変換回路 | |

| US7114092B2 (en) | Method of supplying a required clock frequency by a clock generator module through interface communication with a mainboard | |

| US7761068B2 (en) | System and method for a time alignment analog notch | |

| CN107222218B (zh) | 一种并行数据的产生电路、方法及电子设备 | |

| JP5678226B1 (ja) | デジタル回路システム及びブロックユニット | |

| KR100429554B1 (ko) | 프로그램 가능 카운터 회로 | |

| JP2012023486A (ja) | 半導体装置 | |

| WO2018136120A1 (en) | Offset system and method for multi-bit digital-to-analog converters | |

| JP2018046347A (ja) | 通信システム、及び、通信装置 | |

| KR101678770B1 (ko) | 저 지터 선형 디지털 제어 발진기에서의 프랙셔널 디더 제어 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070109 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070320 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070411 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20070501 |