JP2004021556A - 記憶制御装置およびその制御方法 - Google Patents

記憶制御装置およびその制御方法 Download PDFInfo

- Publication number

- JP2004021556A JP2004021556A JP2002174944A JP2002174944A JP2004021556A JP 2004021556 A JP2004021556 A JP 2004021556A JP 2002174944 A JP2002174944 A JP 2002174944A JP 2002174944 A JP2002174944 A JP 2002174944A JP 2004021556 A JP2004021556 A JP 2004021556A

- Authority

- JP

- Japan

- Prior art keywords

- control unit

- storage

- communication path

- internal communication

- control device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0766—Error or fault reporting or storing

- G06F11/0775—Content or structure details of the error report, e.g. specific table structure, specific error fields

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0706—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation the processing taking place on a specific hardware platform or in a specific software environment

- G06F11/0727—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation the processing taking place on a specific hardware platform or in a specific software environment in a storage system, e.g. in a DASD or network based storage system

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0751—Error or fault detection not based on redundancy

- G06F11/0754—Error or fault detection not based on redundancy by exceeding limits

- G06F11/0757—Error or fault detection not based on redundancy by exceeding limits by exceeding a time limit, i.e. time-out, e.g. watchdogs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

Abstract

【解決手段】本発明の記憶制御装置は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、を備える。

【選択図】 図1

Description

【発明の属する技術分野】

この発明は、外部通信路から入力されるデータ入出力指示を受信して記憶デバイスに対するデータ入出力制御を行い内部通信路で接続された複数の制御部を備える記憶制御装置に関し、とくに制御部間で交換する稼働情報の通信路として内部通信路を用い、稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に制御部間での稼働情報の監視機能を提供する技術に関する。

【0002】

【従来の技術】

近年、ストレージ製品の一つとして、内部にファイルシステムが実装され、ファイル指定によるデータ入出力要求を取り扱うことができるようにした記憶制御装置である、いわゆる、NAS(Network Attached Storage)サーバに対するニーズが高まっている。また、このようなNASサーバとしては、処理能力の向上等を目的として、それぞれがLAN等の外部通信路に接続し、それぞれが個別に外部通信路を通じて送られてくる処理要求に応答できるようにした複数の制御部を、同一の筐体内に収容する構成の製品が存在する。

【0003】

【発明が解決しようとする課題】

ところで、記憶制御装置はミッションクリティカルな状況で使用される場合が多く、一般に高い可用性が要求される。

ここで、LAN上のコンピュータ同士の障害検知に際しては、従来から、LAN上のコンピュータ間でハートビートメッセージを交換して互いの稼働状態を監視し合うことで、可用性を向上させる仕組みが知られている。

【0004】

例えば、特開2000−222373号公報には、クラスタ化コンピュータシステムにおいて、クラスタを構成するコンピュータ同士でLANを通じて定期的にハートビートメッセージを交換し、お互いに稼働状態を監視し合うようにし、ハートビートメッセージの交換が正常に行われていない場合には、適宜制御部のデータサービスは他の正常な制御部へ引き継ぐようにした仕組みが開示されている。また、特開2001−100943号公報には、2台のPCサーバが、ハートビートを行うための通信を、ディスク装置が接続してあるSCSIバスを用いて行うようにしたクラスタシステムが開示されている。

【0005】

一方、前記図1の構成の記憶制御装置のように、複数の制御部を備える構成の記憶制御装置においては、各制御部は同一筐体内に実装されてはいるものの、外部通信路からの要求に対してそれぞれが個別にサービスを提供している。

【0006】

そこで、このような構成の記憶制御装置においても、前記公報のように、制御部間で稼働状態を監視し、また、ある制御部における障害を検知した場合には、その業務を他の正常な制御部に引き継ぐ仕組みを設けることは、可用性の向上に有効であると考えられる。

【0007】

ここでこのような仕組みを設ける場合、稼働情報を伝達する通信路に何を用いるかが問題となる。例えば、前記公報のクラスタ化コンピュータシステムの場合には、このような稼働情報(この場合はハートビートメッセージ)の通信路として、コンピュータ間を結ぶLAN等の外部通信路や、専用の通信路を用いている。

【0008】

しかしながら、外部通信路は、経路途中の信頼性が充分で無く、また、通信速度も充分でない、もしくは、一定しないといった問題がある。また、専用の通信路を設ける場合は、専用の設備が必要となり、余分なコストが発生することになる。

【0009】

一方、前述した図1の構成の記憶制御装置においては、制御部間は、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力を行うための内部通信路により互いに接続されている。そして、内部通信路は一般にLANなどの外部通信路よりも伝送能力が高く信頼性も高い。従って、内部通信路を稼働情報の通信路として用いることで、信頼性の高い制御部間で稼働状態を監視する仕組みを、容易かつ安価に実現することは可能であると考えられる。

【0010】

本発明は、このような観点に基づいてなされたもので、内部通信路を用いて稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に稼働情報の監視機能を実現する記憶制御装置を提供することを目的とする。

【0011】

【課題を解決するための手段】

この目的を達成する本発明のうち主たる発明は、

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする。

【0012】

すなわち、一般に外部通信路に比べて信頼性が高く、高速大容量通信が可能な、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力を行うための内部通信路を通じて稼働情報を通知するようにしたことで、記憶制御装置の部品点数の削減が図られ、装置コストを抑えて信頼性の高いシステムを実現できる。

【0013】

【発明の実施の形態】

===開示の概要===

本明細書および添付図面の記載により、少なくとも、以下の事項が明らかとなる。

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする記憶制御装置。

この記憶制御装置によれば、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バスのようにデータ入出力指示及びデータ入出力を行うための内部通信路を通じて稼働情報(例えば、ハートビートメッセージ)を通知することで、記憶制御装置の部品点数の削減が図られ、装置コストを抑えて信頼性の高いシステムを実現できる。

【0014】

外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶する手段と、前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視する手段と、を備えることを特徴とする記憶制御装置。

このような構成の記憶制御装置によれば、制御部とは別体の前記メモリ(例えば、後述する制御メモリ)に存在する稼働情報(例えば、後述する「稼働状態管理テーブル」)に障害の状態を管理することが可能となるため、内部通信路の稼働状態に関する情報などと組み合わせて、障害の原因や発生部分をより細かく特定することができる。

【0015】

また、かかる記憶制御装置においては、例えば、前記制御部は、中央処理装置と、前記外部通信路に接続するための外部通信インタフェースと、前記内部通信路と接続するための内部通信インタフェースと、を備えることとする。

【0016】

また、かかる記憶制御装置においては、前記稼働情報には前記制御部の障害有無を示す情報が含まれており、前記制御部が前記監視手段により他の前記制御部に障害が生じていることを認知した場合、障害が生じている前記制御部が行っていた処理を他の前記制御部に引き継ぐ手段を備えることとする。これにより、記憶制御装置の可用性が確保されることになる。

【0017】

また、かかる記憶制御装置において、前記メモリは前記制御部が担当する処理に関するリソース情報を記憶する手段を備え、前記処理の引き継ぎ先となる前記制御部が、前記リソース情報にアクセスし当該制御部自身が引き継ぐべき前記処理を認知する手段を備えることとする。

【0018】

また、かかる記憶制御装置において、前記リソース情報には、例えば、前記制御部が前記外部通信路もしくは前記内部通信路による通信に必要な情報、前記データ入出力指示において指定する記憶領域指定情報、外部通信路上における前記制御部のネットワークアドレスが含まれることとする。

【0019】

また、かかる記憶制御装置において、前記稼働情報には、前記中央処理装置、前記外部通信インタフェース、前記内部通信インタフェースのいずれかについての障害の有無を示す情報が含まれることとする。

【0020】

また、かかる記憶制御装置において、前記障害の有無を示す情報が、前記制御部が前記内部通信路を介して前記メモリに一定間隔で送信され、前記制御部に対応づけて記憶されるタイムスタンプであり、前記監視手段は、ある前記制御部に対応する前記タイムスタンプが一定時間以上更新されていない場合に、そのタイムスタンプに対応づけられている前記制御部に障害が生じていると認知することとする。

【0021】

また、かかる記憶制御装置において、前記監視手段が、前記稼働情報にアクセスできない場合に、前記内部通信路に障害が生じていると判断する手段を備えることとする。また、前記監視手段が、前記稼働情報にアクセスできかつ前記のある制御部の前記タイムスタンプが一定時間以上更新されていない場合に、その制御部自体に障害が生じていると判断する手段を備えることとする。これにより、障害を細かく特定することが可能となる。

【0022】

また、かかる記憶制御装置において、前記記憶手段が、中央処理装置と、メモリと、ディスクドライブなどの記憶資源に対するデータ入出力を行うデバイスインタフェースとを備えることとする。

【0023】

また、前記稼働情報、もしくは、前記リソース情報は、前記メモリに記憶されることとする。

【0024】

また、かかる記憶制御装置において、前記稼働情報、もしくは、前記リソース情報は、前記記憶資源に記憶されることとしてもよい。

【0025】

また、かかる記憶制御装置において、前記制御部が、データ入出力要求をファイル名単位で行うファイルシステムを備え、ファイル名により指定されるデータを単位として前記記憶手段に対する前記データ入出力指示を送信する手段を備えることとする。すなわち、記憶制御装置が、例えば、NASサーバとして用いられる場合である。

【0026】

また、かかる記憶制御装置は、前記記憶手段が、ハードディスクなどの記憶資源に対するデータ入出力を制御するデバイスインタフェースと、キャッシュメモリと、キャッシュメモリを介して前記記憶資源に対するデータの読み書きを行う手段と、を備えることを特徴とする。また、かかる記憶制御装置は、前記内部通信路が、複数の通信経路により冗長構成されることとする。

【0027】

また、かかる記憶制御装置は、前記制御部が、前記内部通信路とは別に設けられ前記制御部間を接続する他の通信路(例えば、後述する専用通信路)を通じて他の前記制御部に自身の稼働情報を送信する手段を備え、前記他の通信路に対して送信される稼働情報を前記内部通信路に対して送信する変換手段(例えば、後述するエミュレーションドライバ)を備えることを特徴とする。これにより汎用のクラスタソフトウエアなどを用いて、簡単かつ安価に稼働状態監視の仕組みを実現することができる。

【0028】

また、本発明の記憶制御装置の制御方法は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路とを備える記憶制御装置の制御方法であって、前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部同士が他の前記制御部の稼働状態を監視することを特徴とする。

【0029】

また、本発明の他の記憶制御装置の制御方法は、外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、を備える記憶制御装置の制御方法であって、前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶し、前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視することとする。

【0030】

==第1実施例==

<装置構成>

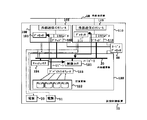

まず、本発明を前述の図1に示す記憶制御装置10に適用した実施例について説明する。

【0031】

記憶制御装置10は、例えば、回路基板上に形成されCPUとメモリを結ぶ制御バス(システムバス)のようにデータ入出力指示及びデータ入出力を行うための内部通信路20と、これに接続する複数の制御部100,110、記憶装置120、冗長構成された電源装置30,31を備える。制御部100,110や記憶装置120に接続するサービスプロセッサ40は、制御部100,110や記憶装置120の動作制御や各種設定、稼働状態監視などを行う。

【0032】

制御部100,110は、CPUなどで構成される中央処理装置としてのプロセッサ101,111、LANなどの外部通信路50に接続するための外部通信インタフェース102,112、内部通信路20に接続するブリッジなどで構成された内部通信インタフェース103,113などを備える。

【0033】

制御部100,110では、ファイルシステム(不図示)が稼働し、制御部100,110は外部通信路50からファイル名指定によるデータ入出力要求を取り扱う。つまり、制御部100,110は、それぞれLAN上のファイルサーバとして機能するコンピュータとしての機能を備え、記憶制御装置10は前述のNASサーバとして機能している。

【0034】

一方、記憶装置120は、システム管理情報などが記憶される制御メモリ121、ハードディスクなどの記憶資源122、制御部100,110から送信されてくる命令などに応じて記憶資源122に対するデータの書き込み/読み出しを実行するデバイスインタフェース123、キャッシュメモリ124などを備える。

【0035】

なお、記憶資源122は、図1に示すように記憶制御装置10に内蔵されている場合もあるし、また、記憶制御装置20の外部の別筐体内に存在し、デバイスインタフェース123と適宜なインタフェースで接続していることもある。

【0036】

<基本動作>

記憶制御装置10の基本的な動作について説明する。

記憶制御装置10がホストコンピュータなどの外部装置(不図示)から外部通信路50を通じて入力されるデータ入出力要求を受信すると、プロセッサ101,111は、この要求に対応する指示コマンドやデータなどからなるデータ入出力指示を、内部通信路20を介して制御メモリ121に送信する。制御メモリ121はこれを受信して記憶する。

【0037】

ここで、例えば、前記データ入出力指示に含まれる前記指示コマンドがライト(Write)コマンドであった場合、デバイスインタフェース123は、内部通信路20を介してプロセッサ101,111にデータ送信要求を送信する。この要求を受信したプロセッサ101,111は、キャッシュメモリ124にライトデータを格納し、また、デバイスインタフェース123に対して割込み要求を送信する。この割り込み要求を受信したデバイスインタフェース123は、適宜な機会に、キャッシュメモリ124上の前記ライトデータを記憶資源122に書き込む。

【0038】

一方、前記指示コマンドがリード(Read)コマンドであった場合、デバイスインタフェース123は、この指示コマンドに付帯指定される記憶資源122上の記憶領域に格納されているデータを読み出し、これをキャッシュメモリ124に格納し、さらに、読み出したデータを、内部通信路20を介してプロセッサ101,111に送信する。

【0039】

割り込み要求を受信したデバイスインタフェース123は、制御メモリ121に格納されている前記指示コマンドを参照し、キャッシュメモリ124内のデータと冗長データとを記憶資源122に転送する。

【0040】

<監視機能>

各制御部100,110は、互いに他の制御部100,110に障害が発生したかどうかを監視している。各制御部100,110がどの他のどの制御部100,110の監視を担当するかは、例えば、サービスプロセッサ40を介してオペレータなどが設定し、設定された情報は、制御メモリ121上に存在する図2に示す稼働状態管理テーブルの「監視対象の制御部」の項目251,254に登録される。

【0041】

各制御部100,110は、自身の監視対象として割り当てられている他の制御部100,110の稼働状態を監視する。この監視により自身が担当する制御部100,110に何らかの障害が生じていることを検知した場合、制御部100,110は、検知した障害の内容に応じた処理を実行する。

【0042】

以下、制御部100,110による監視機能と、異常を検知した場合に実行される記憶制御装置10の機能について、制御部110の障害を制御部100が検知する場合を例として図3のフローチャートとともに説明する。

【0043】

制御部110は、内部通信路20を通じて定期的(タイミングは任意に変更できる)に制御メモリ121にアクセスする(もしくは、ハートビートメッセージを送信する)。一方、記憶装置120は、前記アクセスがあると、アクセスのあった時刻をタイムスタンプとして稼働状態管理テーブルの制御部110のタイムスタンプの項目255に書き込む(S311)。すなわち、制御部110に異常が無ければタイムスタンプは定期的に更新されることになる。

【0044】

一方、制御部100は、稼働状態管理テーブルを参照するため、内部通信路20を通じて定期的(定期的以外にも任意に設定してもよい)に制御メモリ121にアクセスする(S312)。

【0045】

ここで制御部100は、制御メモリ121にアクセスできなかった場合(S313)、内部通信路20に何らかの障害が発生していると判断し、また、内部通信路20に障害が発生している場合は、記憶装置120へのデータ入出力が正常に行えない状態にある可能性があるので、制御部100は、例えば、サービスプロセッサ40に指示を出すなどして、制御部110の記憶装置120に対するデータ入出力処理を停止させるとともに、この処理に関して制御部110が取得中のリソースを開放させる(S314)。

【0046】

ここで、リソースとは、例えば、制御部100,110が外部通信路50もしくは内部通信路20による通信に際し必要となる、ネットワークアドレス(例えば、IPアドレス)などの情報、制御部100,110が記憶手段に対して送信するデータ入出力指示において指定する記憶領域指定情報(例えば、制御部110がマウントしていた記憶領域に関する情報)などである。

【0047】

一方、制御部100は、制御メモリ121にアクセスできた場合、稼働状態管理テーブルの制御部110のタイムスタンプ255を参照し(S315)、アクセスした時刻とタイムスタンプとの差が一定時間以上であるかどうかを調べる(S316)。

【0048】

ここで差が一定時間以上の場合には、制御部100は、制御部110に障害が発生していると判断し、制御部110が担当している処理やリソースを制御部100が引き継ぐ(S317)。

【0049】

一方、差が一定時間に満たない場合には、さらに、稼働状態管理テーブル中の監視対象の制御部110の「状態」項目の内容256を参照する(S318)。ここでその内容が『正常』である場合には、制御部100は、制御部110は正常に動作していると認知する(S319,S320)。他方、「状態」項目の内容256が『異常』であった場合には、制御部110に障害が発生したと判断し、前記と同様の方法により制御部110が担当している処理を引き継ぐ(S319,S317)。なお、稼働状態管理テーブルにおいて、『正常』もしくは『異常』は、ビット表現等の適宜な形式で記述される。

【0050】

ところで、記憶制御装置10において、稼働状態管理テーブルにおける「状態」項目の内容は、つぎのように管理されている。

例えば、制御部100,110は、図4に示すように外部通信インタフェース102に障害が発生している場合、そのことを外部通信インタフェース102,112からプロセッサ101,111への直接の障害報告、もしくは、外部通信インタフェース50に出した処理命令がタイムアウトする、といったことで認知する。

【0051】

制御部100,110は、外部通信インタフェース102,112に障害が発生していることを認知すると、内部通信路20を通じて制御メモリ121上の稼働状態管理テーブルにアクセスし、障害が発生している制御部100,110に対応する「状態」項目253,256に『異常』を書き込む。

【0052】

一方、制御部100,110は、図5に示すように内部通信インタフェース103,113に障害が発生している場合、そのことを内部通信インタフェース103,113からプロセッサ101,110への障害報告、もしくは、内部通信インタフェース103,113に出した処理命令のタイムアウトなどにより認知する。

【0053】

制御部100,110は、内部通信インタフェース103,113に障害が発生していることを認知すると、内部通信路20を通じて制御メモリ121上の稼働状態管理テーブルにアクセスし、障害が発生している制御部100,110に対応する「状態」項目に『異常』を書き込む。

【0054】

図6はプロセッサ101に障害が発生している場合である。この場合、制御部100は稼働状態管理テーブルに状態を書き込むことができない。しかしながら、制御部110のプロセッサ111が制御メモリ121を参照するため、プロセッサ101に障害している場合でも、その障害を検知することができる。

【0055】

以上の実施例では、制御部100が制御部110の監視を行う場合について説明したが、当然のことながら制御部110が制御部100を監視する場合も同様の処理により行われる。

【0056】

以上の実施例においては、制御メモリ121の稼働状態管理テーブルへの書き込みや参照などの制御部100,110における障害監視のための通信を、内部通信路20を介して行っている。このため、従来の外部通信路50や専用の通信路による方式に比べ、障害監視のための通信を高速に行える。また、一般に内部通信路20は、LANなどの外部通信路50に比べ伝送能力や信頼性に優れるため、障害監視のための通信を迅速かつ確実に行うことができる。

【0057】

また、本来、制御部100,110間やこれらと記憶装置120間で行われるデータ入出力処理等のために設けられている内部通信路20を、障害監視のための通信に流用しているので、専用の通信路を設ける場合のように余分なハードウエアを増設する必要が無く、障害監視のための通信の仕組みを、容易かつ安価に構築できる。

【0058】

内部通信路20を介して制御部100,110に接続する、制御部100,110とは別体の、記憶装置120の制御メモリに存在する稼働状態管理テーブルに障害の状態を管理する仕組みであるため、内部通信路20の稼働状態に関する情報などと組み合わせて、障害の原因や発生部分をより細かく特定することができる。

【0059】

また、制御部100,110が障害の発生を認知した場合における、処理引き継ぎのための各制御部100,110が取得しているリソースに関する情報についても制御メモリ121に管理されるため、制御部100,110に障害が発生した場合でも、記憶装置120は引き継ぐリソースを確認することができる。また、リソースの一元管理により管理負荷の軽減等が図られる。

【0060】

また、内部通信路が冗長構成されている場合には、障害監視のための通信の安全性や確実性がさらに担保される。

【0061】

なお、以上の実施例は、制御部が2つの場合であったが、これに限定されるものではなく、制御部が3つ以上の場合にも容易に拡張することができる。

【0062】

===既存クラスタシステムの利用===

前述の公報にも記載されているように、従来から、外部通信路や専用の通信路を利用してコンピュータ間で障害監視のための通信を行うソフトウエアが存在する。ここでは、このようなソフトウエアを用いて障害監視のための通信に、内部通信路20を利用する本発明の仕組みを実現する場合について説明する。

【0063】

図7は、本発明の制御部に対応する、コンピュータ720,730が、専用の通信路により接続され、この専用通信路750を介してハートビートメッセージを伝送することで、コンピュータ720,730がお互いに稼働状態を監視し合う、従来のシステム構成である。

【0064】

コンピュータ720,730は、それぞれ、クライアントからのファイルサービスの要求をネットワークインタフェース721、731、ネットワークドライバ722,732を経由しファイルシステム723,733で受信する。

【0065】

ファイルシステム723,733は、記憶装置726に対するデータ転送が必要な場合、ストレージドライバ724,734、ストレージインタフェース725,735を経由し記憶装置726とデータ転送を行う。クラスタソフトウエア727,737は、ハートビート用ネットワークドライバ728,738、ハートビートネットワークインタフェース729,739を経由し、コンピュータ730上のクラスタソフトウエア727,737に対しハートビートメッセージを送信する。

【0066】

このクラスタソフト727,737が導入されている図7の構成に、障害監視に内部通信路を利用する本発明を適用した場合が図8である。この図において、記憶制御装置810は、クラスタソフトウエア847,857からのアクセスを受領し、このアクセスをストレージドライバ844,854へのアクセスに変換するエミュレーションドライバ848,858を備えている。この構成により、汎用のクラスタソフトウエア847,857が発行したハートビートメッセージを内部通信路849を通じて伝送される稼働状態情報に変換すること、および、その逆の変換をすることができる。具体的には、例えば、エミュレーションドライバ848,858は、RS−232CやLANなどの他の通信路の伝送手順に従った通信によりクラスタソフトウエア847,857からのアクセスを受領して、これを内部通信路849上での通信に変換したり、逆に内部通信路849上での通信を前記他の通信路の伝送手順に変換してクラスタソフトウエア847,857に伝えるといった役割を果たす。なお、RS−232CやLANなどの他の通信路は、記憶制御装置10がハードウエア/ソフトウエアとして実際に備えていてもよいし、備えていなくてもよい。また、前記変換機能部分は、エミュレーションドライバ848,858の内部に設けるのでは無く、ストレージドライバ844,854や記憶装置846における内部通信インタフェース(不図示)の機能を提供するファームウエア(不図示)などに設けるようにしてもよい。

【0067】

以上に説明したように、既存のクラスタソフトウエアが導入されているシステムにおいては、エミュレーションドライバを導入するだけで本発明を実施することができる。

【0068】

また、既存のクラスタソフトウエアが導入されていない場合には、既存のクラスタソフトウエアにエミュレーションドライバを組み合わせて導入することで、クラスタソフトウエアの機能部分に対する開発費が抑えられるため、低廉なコストで本発明を実施することができる。

【0069】

===内部通信路の他の構成===

内部通信路が制御バスで無く、ファイバチャネル(FibreChannel)、Intelligent I/O、Rapid I/Oなどの他のプロトコルに準拠した通信路で構成される場合を説明する。

図9は内部通信路をファイバチャネル(FibreChannel)プロトコルによる通信路で構成した記憶制御装置971の構成を示す図である。制御部950,960は、内部通信インタフェースとしてファイバチャネルインタフェース953,963を備える。

【0070】

一方、記憶装置980もファイバチャネルインタフェース986,996を備え、制御部950、960とはファイバチャネルスイッチ956,966、ファイバチャネルインタフェース986,992を介して接続する。

【0071】

制御部950,960は、ファイバチャネルスイッチ956、966、ファイバチャネルインタフェース953,963を介して制御部950,960に接続され、制御メモリ982,992、書き込みデータ及びディスクドライブからの読出しデータを一時バッファリングするキャッシュメモリ983,993を備える。

【0072】

制御部950,960は、デバイスインタフェース994を介してディスクドライブ群985へ接続される。制御部950、960、記憶装置980は、同一の筐体に実装される冗長構成の電源972,973より給電され、保守機構974により、各種動作設定や稼働管理が行われる。

【0073】

制御部950がディスクドライブ群からなる記憶資源985とライト(Write)データ転送を行う場合を例として、制御の流れ、データの流れを説明する。制御部950がサービスネットワーク970によりデータサービスの依頼を受けると、プロセッサ952は、サービス依頼を記憶装置980に対するI/Oコマンドに変換し、ファイバチャネルインタフェース953、ファイバチャネルスイッチ956、ファイバチャネルインタフェース986を介して、記憶装置980へI/Oコマンドを送信する。

【0074】

送信されたI/Oコマンドは、制御メモリ982に格納される。I/Oコマンドがライトコマンドである場合、ファイバチャネルインタフェース986は、プロセッサ952にデータ転送を指示する。この指示によりプロセッサ952は、ファイバチャネルプロトコルに従い、記憶装置980に書き込みデータを送信する。記憶装置980は、送信されてきた書き込みデータを受信して、これを一旦キャッシュメモリ983に格納する。この書き込みデータは、デバイスインタフェース984により冗長データと共に記憶資源985に転送される。

【0075】

つぎに、 図9のシステムにおいて、制御部950が障害になった場合には制御部960で、制御部960が障害になった場合には制御部950で、それぞれ障害が発生している制御部のリソースを引継ぎ、自動的にデータサービスなどの記憶制御装置10の業務を続行できるようにした、記憶制御装置971の仕組みについて説明する。

【0076】

記憶資源985には、図10に示す稼働状態管理テーブルが格納されている。稼働状態管理テーブルには、各制御部を特定する情報1001,1002、監視すべき対象の制御部を特定する情報1003,1004についての項目がある。これらの項目は、例えば、フェイルオーバポリシーに従って設定される。タイムスタンプ1005,1006は、制御部950,960が稼働情報(ハートビートメッセージ)のI/Oを発行する際の制御部上の時刻を示す。また、この稼働状態管理テーブルの「状態」1007,1008項目には、制御部950,960の『正常』、『異常』を示す情報がセットされている。これらの項目にセットされる情報には、必要に応じてクラスタシステムを構築する際のサービスネットワーク1070上の制御部に割り当てられた名称などの固有の識別子が用いられる。

制御部950上のプロセッサ952は、適宜なタイミング(例えば、定期的に)で記憶資源985の稼働情報管理テーブルの読み出し命令を送信し、稼働情報管理テーブルに示す全データもしくは一部のデータを取得する。稼働情報管理テーブルを読み出すと、プロセッサ952は、全データから制御部ネーム領域1001,1002を参照し、制御部950が有する制御部ネーム「ServerA」に対応づけられている監視対象制御部の制御部ネームを参照する。そして、この例では、「ServerA」の監視担当制御部として「ServerB」が割り当てられているので「ServerB」のタイムスタンプ1006と状態情報1008とを参照し、フェイルオーバ処理を実行する必要性の有無を判断する。

【0077】

プロセッサ952は、「ServerB」のタイムスタンプ1006と現在時刻との差が一定時間以上であった場合、もしくは、「状態」項目1008に『異常』を示す情報がセットされていた場合には、制御部960に何らかの障害が発生していると認知する。また、プロセッサ952は、稼働状態管理テーブルにアクセスできることで、内部通信路に障害が発生していないと認知し、障害が制御部960におけるものであると判断して制御部960が行っていた処理やリソースの引き継ぎを開始する。

【0078】

なお、プロセッサ952は、制御部960の障害を検出するかどうかに関わらず、「ServerA」のタイムスタンプと状態情報である図10の1005,1007の項目の内容を適宜なタイミング(例えば定期的に)更新する。

【0079】

制御部950,960が定期的に以上の処理を行うことにより汎用I/Oインタフェースを通信路として用いた障害監視等の仕組みが実現されることになる。

【0080】

つぎに、ファイバチャネルスイッチ956に障害が生じた場合についての記憶制御装置の動作について説明する。

ファイバチャネルスイッチ956が障害となった場合、制御部950はI/O入出力が不可となるが、通常のフェイルオーバ方式により制御部960の処理を継続させた場合には制御部960に処理が集中し、性能が劣化する可能性がある。

【0081】

そこで、このような場合には、汎用I/O切り替えソフトウエア等により、制御部950の入出力経路を、ファイバチャネルインタフェース953→ファイバチャネルスイッチ956→ファイバチャネルインタフェース986という通常の経路から、ファイバチャネルインタフェース954→ファイバチャネルスイッチ966→ファイバチャネルインタフェース996という経路に変更してI/Oを継続する。また、同時に、ディスクボリューム群985に制御部950から行われていた制御部950のアクセス状態情報を格納、確認するためのI/Oも経路を切り替える。

【0082】

この例では、制御部950は、ファイバチャネルインタフェース954→ファイバチャネルスイッチ966→ファイバチャネルインタフェース996を順に経由して、図10におけるタイムスタンプ1005、制御部950の「状態」項目の内容1007をディスクボリューム群985に格納する。

【0083】

なお、以上はファイバチャネルスイッチ956が障害となった場合を例として説明したが、ファイバチャネルインタフェース953、ファイバチャネルスイッチ956、ファイバチャネルインタフェース986等に障害が発生した場合においても以上の処理を拡張できる。

【0084】

以上のように、この実施例では、制御部950,960の状態情報を搭載した稼働情報の伝送を、外部通信路や専用の通信路では無く、記憶装置980への汎用I/Oインタフェース上で行っている。これによりハートビート用ネットワークインタフェースの導入が必要でなく、その分、手間やコストが削減され、また、信頼性の高い汎用I/Oインタフェースの利用により、信頼性の高い稼働状態監視機能を実現できる。

【0085】

また、制御部の稼働状態を格納するディスクドライブ上に、クラスタ動作に必要な制御部ネットワークアドレス等のネットワーク属性、データが格納されているディスクドライブ等のリソース引継ぎ情報を格納することにより、各制御部より読み出し可能となるため、リソース引継ぎの設定管理を一元化し、管理コストの削減を図ることができる。

【0086】

また、図9では2つのファイバチャネルスイッチ956,966を含む構成であったが、ファイバチャネルスイッチを全く含まない構成や、3つ以上のファイバチャネルスイッチを含む構成である場合にも本発明を拡張して適用することができる。また、ファイバチャネル以外の汎用I/Oインタフェースを用いる場合にも適用できる。

【0087】

===稼働情報の格納方式===

つぎに、汎用クラスタソフトを使用して本発明のシステムを構築する際に、汎用クラスタソフトが送信する稼働情報を、記憶装置のディスクドライブなどの記憶資源(例えば、ディスクドライブ)上に格納するようにした実施例について説明する。

【0088】

図11はこのような構成の記憶制御装置1000の一例である。制御部1110,1150は、クライアントからのファイルサービスの依頼をネットワークインタフェース1111,1151、ネットワークドライバ1112,1152を経由してファイルシステム1113,1153で受信する。

【0089】

ファイルシステム1113,1153は、ストレージドライバ1114,1154、ファイバチャネルインタフェース1115,1155、ファイバチャネルスイッチ1116,1156を経由して記憶装置1119とデータ転送を行う。ストレージドライバ1114,1154内には、汎用I/O切り替えソフトウエアが組み込まれている。

【0090】

データの転送経路に障害が発生した場合、ストレージドライバ1114,1154は、データ転送の経路をファイバチャネルインタフェース1117,1157、ファイバチャネルスイッチ1116,1156を経由する経路に切り替える。

【0091】

このシステムにおいて、汎用クラスタソフトウエアは、ネットワークに対し制御部の状態情報を含む稼働情報を送信する。ここで当該稼働情報の要求をネットワークドライバとして受信し、汎用I/Oインタフェース経由で記憶装置へデータ転送を行う要求に変換するエミュレーションドライバ1120,1160を、各制御部において稼働させることで、汎用クラスタソフトウエアに対し、透過的に汎用I/Oインタフェース上でのハートビートの交換を行えるようにしている。

【0092】

また、ストレージドライバ1014は、汎用I/Oインタフェース上のハートビートであるI/Oに対しても、データ転送の経路障害時に経路をファイバチャネルインタフェース1117,1157、ファイバチャネルスイッチ1116,1156を経由する経路に切り替えてデータ転送を継続する。これにより信頼性の高い稼働状態監視のための仕組みが実現される。

【0093】

【発明の効果】

本発明の記憶制御装置にあっては、制御部間で交換する稼働情報の通信路として内部通信路を用い、稼働情報を効率よく管理し、性能や信頼性が高く構築が容易で安価に稼働情報の監視機能を提供することができる。

【図面の簡単な説明】

【図1】本発明の一実施例による記憶制御装置の構成を示す図である。

【図2】本発明の一実施例による稼働情報管理テーブルを示す図である。

【図3】本発明の一実施例として説明する記憶制御装置における、制御部が他の制御部が検知する処理を説明するフローチャートである。

【図4】本発明の一実施例として説明する記憶制御装置における、外部通信インタフェースに障害が発生している場合の障害認知等の処理を説明する図である。

【図5】本発明の一実施例として説明する記憶制御装置における、内部通信インタフェースに障害が発生している場合の障害認知等の処理を説明する図である。

【図6】本発明の一実施例として説明する記憶制御装置における、プロセッサに障害が発生している場合の障害認知等の処理を説明する図である。

【図7】従来における、コンピュータがお互いに稼働状態を監視し合う仕組みを説明する図である。

【図8】本発明の一実施例による、障害監視に内部通信路を用いた記憶制御装置の構成を示す図である。

【図9】本発明の一実施例による、内部通信路をファイバチャネルプロトコルの通信路で構成した記憶制御装置の構成を示す図である。

【図10】本発明の一実施例による稼働情報管理テーブルを示す図である。

【図11】本発明の一実施例による、汎用クラスタソフトを使用し、また、稼働情報をディスクドライブなどの記憶資源に格納するようにした記憶制御装置の構成を示す図である。

【符号の説明】

20 内部通信路

50 外部通信路

101,110 制御部

121 制御メモリ

124 キャッシュメモリ

122 記憶資源

123 デバイスインタフェース

Claims (21)

- 外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、

前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部が互いに他の前記制御部の稼働状態を監視する手段と、

を備えることを特徴とする記憶制御装置。 - 外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、

前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、

前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶する手段と、

前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視する手段と、

を備えることを特徴とする記憶制御装置。 - 前記制御部が、

中央処理装置と、前記外部通信路に接続するための外部通信インタフェースと、

前記内部通信路と接続するための内部通信インタフェースと、

を備えることを特徴とする請求項2に記載の記憶制御装置。 - 前記稼働情報には前記制御部の障害有無を示す情報が含まれており、

前記制御部が前記監視手段により他の前記制御部に障害が生じていることを認知した場合、障害が生じている前記制御部が行っていた処理を他の前記制御部に引き継ぐ手段を備えることを特徴とする請求項1または2のいずれかに記載の記憶制御装置。 - 前記メモリは前記制御部が担当する処理に関するリソース情報を記憶する手段を備え、

前記処理の引き継ぎ先となる前記制御部が、前記リソース情報にアクセスし当該制御部自身が引き継ぐべき前記処理を認知する手段を備えることを特徴とする請求項4に記載の記憶制御装置。 - 前記リソース情報には、前記制御部が前記外部通信路もしくは前記内部通信路による通信に必要な情報が含まれることを特徴とする請求項5に記載の記憶制御装置。

- 前記リソース情報には、前記データ入出力指示において指定する記憶領域指定情報が含まれることを特徴とする請求項5に記載の記憶制御装置。

- 前記リソース情報には、外部通信路上における前記制御部のネットワークアドレスが含まれることを特徴とする請求項5に記載の記憶制御装置。

- 前記稼働情報には、前記中央処理装置、前記外部通信インタフェース、前記内部通信インタフェースのいずれかについての障害の有無を示す情報が含まれることを特徴とする請求項3に記載の記憶制御装置。

- 前記障害の有無を示す情報が、前記制御部が前記内部通信路を介して前記メモリに一定間隔で送信され、前記制御部に対応づけて記憶されるタイムスタンプであり、

前記監視手段は、ある前記制御部に対応する前記タイムスタンプが一定時間以上更新されていない場合に、そのタイムスタンプに対応づけられている前記制御部に障害が生じていると認知することを特徴とする請求項9に記載の記憶制御装置。 - 前記監視手段が、前記稼働情報にアクセスできない場合に、前記内部通信路に障害が生じていると判断する手段を備えることを特徴とする請求項4に記載の記憶制御装置。

- 前記監視手段が、前記稼働情報にアクセスできかつ前記のある制御部の前記タイムスタンプが一定時間以上更新されていない場合に、その制御部自体に障害が生じていると判断する手段を備えることを特徴とする請求項4に記載の記憶制御装置。

- 前記記憶手段が、中央処理装置と、前記メモリと、ディスクドライブなどの記憶資源に対するデータ入出力を行うデバイスインタフェースとを備えることを特徴とする請求項2に記載の記憶制御装置。

- 前記稼働情報、もしくは、前記リソース情報は、前記メモリに記憶されることを特徴とする請求項13に記載の記憶制御装置。

- 前記稼働情報、もしくは、前記リソース情報は、前記記憶資源に記憶されることを特徴とする請求項13に記載の記憶制御装置。

- 前記制御部が、データ入出力要求をファイル名単位で行うファイルシステムを備え、ファイル名により指定されるデータを単位として前記記憶手段に対する前記データ入出力指示を送信する手段を備えることを特徴とする請求項2に記載の記憶制御装置。

- 前記記憶手段が、ハードディスクなどの記憶資源に対するデータ入出力を制御するデバイスインタフェースと、

キャッシュメモリと、

前記キャッシュメモリを介して前記記憶資源に対するデータの読み書きを行う手段と、

を備えることを特徴とする請求項2に記載の記憶制御装置。 - 前記内部通信路が、複数の通信経路により冗長構成されることを特徴とする請求項1に記載の記憶制御装置。

- 前記制御部が、前記内部通信路とは別に設けられ前記制御部間を接続する他の通信路を通じて他の前記制御部に自身の稼働情報を送信する手段を備え、

前記制御部が前記他の通信路を通じて送信しようとする前記稼働情報を前記内部通信路に対して送信する変換手段を備えることを特徴とする請求項2に記載の記憶制御装置。 - 外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段に対するデータ入出力指示を送信する複数の制御部と、前記制御部間のデータ入出力指示及びデータ入出力を行うための内部通信路と、を備える記憶制御装置の制御方法であって、

前記制御部が前記内部通信路を通じて他の前記制御部に自身の稼働情報を送信することで前記制御部同士が他の前記制御部の稼働状態を監視することを特徴とする記憶制御装置の制御方法。 - 外部通信路を通じて入力されるデータ入出力要求を受信して記憶手段にデータ入出力指示を送信する複数の制御部と、前記制御部間におけるデータ入出力指示及びデータ入出力を行い前記記憶手段が接続する内部通信路と、を備える記憶制御装置の制御方法であって、

前記制御部の稼働情報を前記制御部から前記内部通信路を通じて当該内部通信路に接続するメモリに送信しこれを当該メモリに記憶し、

前記制御部が前記内部通信路を通じて前記メモリにアクセスし前記稼働情報に基づいて他の前記制御部の稼働状況を監視することを特徴とする記憶制御装置の制御方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002174944A JP2004021556A (ja) | 2002-06-14 | 2002-06-14 | 記憶制御装置およびその制御方法 |

| DE60224369T DE60224369T2 (de) | 2002-06-14 | 2002-10-18 | Speichersteuerungssystem und Verfahren dazu |

| EP02023382A EP1372076B1 (en) | 2002-06-14 | 2002-10-18 | Storage control system and method |

| US10/282,769 US6959344B2 (en) | 2002-06-14 | 2002-10-28 | Method and apparatus for storage system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002174944A JP2004021556A (ja) | 2002-06-14 | 2002-06-14 | 記憶制御装置およびその制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004021556A true JP2004021556A (ja) | 2004-01-22 |

| JP2004021556A5 JP2004021556A5 (ja) | 2005-05-26 |

Family

ID=29561824

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002174944A Pending JP2004021556A (ja) | 2002-06-14 | 2002-06-14 | 記憶制御装置およびその制御方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6959344B2 (ja) |

| EP (1) | EP1372076B1 (ja) |

| JP (1) | JP2004021556A (ja) |

| DE (1) | DE60224369T2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005309838A (ja) * | 2004-04-22 | 2005-11-04 | Hitachi Ltd | 情報管理システムと情報管理方法、及び、そのための情報管理サブシステム |

| JP2010282326A (ja) * | 2009-06-03 | 2010-12-16 | Nec Corp | 情報処理システム、情報処理システムの障害対応機構、及び情報処理システムの障害対応方法 |

| US7889639B2 (en) | 2005-12-20 | 2011-02-15 | Fujitsu Limited | Fiber channel switch and computer system using the same |

| JP2012531656A (ja) * | 2009-11-10 | 2012-12-10 | 株式会社日立製作所 | 複数のコントローラを備えたストレージシステム |

| JP2017215966A (ja) * | 2016-06-01 | 2017-12-07 | シーゲイト テクノロジー エルエルシーSeagate Technology LLC | 記憶デバイスにおける性能変動を制限するための技術 |

| WO2018056044A1 (ja) * | 2016-09-21 | 2018-03-29 | 日本電気株式会社 | 計算機並びにクラスタ管理システム、方法及び非一時的なコンピュータ可読媒体 |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030187987A1 (en) * | 2002-03-29 | 2003-10-02 | Messick Randall E. | Storage area network with multiple pathways for command paths |

| JP4330889B2 (ja) | 2003-01-20 | 2009-09-16 | 株式会社日立製作所 | 記憶デバイス制御装置にソフトウエアをインストールする方法、記憶デバイス制御装置の制御方法、及び記憶デバイス制御装置 |

| JP2004362146A (ja) * | 2003-06-03 | 2004-12-24 | Hitachi Ltd | ストレージ制御装置の制御方法及びストレージ制御装置 |

| US7555569B1 (en) * | 2004-02-02 | 2009-06-30 | Emc Corporation | Quick configuration status |

| US7454533B2 (en) * | 2004-02-06 | 2008-11-18 | Nec Corporation | Redundant path control apparatus and redundant path control method |

| JP2005250938A (ja) * | 2004-03-05 | 2005-09-15 | Hitachi Ltd | 記憶制御システム及び方法 |

| US7200716B1 (en) * | 2004-04-30 | 2007-04-03 | Network Appliance, Inc. | Method and apparatus to offload operations in a networked storage system |

| JP4353005B2 (ja) * | 2004-06-29 | 2009-10-28 | 株式会社日立製作所 | クラスタ構成コンピュータシステムの系切替方法 |

| US7325163B2 (en) * | 2005-01-04 | 2008-01-29 | International Business Machines Corporation | Error monitoring of partitions in a computer system using supervisor partitions |

| US7624206B2 (en) * | 2005-09-29 | 2009-11-24 | Emc Corporation | RAID data storage system with SAS expansion |

| WO2007001728A1 (en) * | 2005-06-27 | 2007-01-04 | Emc Corporation | Raid data storage system with sas expansion |

| US7574542B2 (en) * | 2005-09-29 | 2009-08-11 | Emc Corporation | SAS expansion topology for RAID data storage including multiplexers and SAS expanders for interfacing with single or dual ports drives |

| GB0613239D0 (en) * | 2006-07-04 | 2006-08-09 | Ibm | Storage area network system |

| US20090025063A1 (en) * | 2007-07-18 | 2009-01-22 | Novell, Inc. | Role-based access control for redacted content |

| JP4633837B2 (ja) * | 2008-01-22 | 2011-02-16 | 富士通株式会社 | アドレス配信システム、方法およびそのためのプログラム |

| US7836335B2 (en) * | 2008-04-11 | 2010-11-16 | International Business Machines Corporation | Cost-reduced redundant service processor configuration |

| US8909816B2 (en) * | 2012-03-19 | 2014-12-09 | Kaminario Technologies Ltd. | Implementing a logical unit reset command in a distributed storage system |

| USRE48835E1 (en) * | 2014-04-30 | 2021-11-30 | Rubrik, Inc. | Network addressable storage controller with storage drive profile comparison |

| US10855515B2 (en) * | 2015-10-30 | 2020-12-01 | Netapp Inc. | Implementing switchover operations between computing nodes |

| US11055273B1 (en) * | 2016-11-04 | 2021-07-06 | Amazon Technologies, Inc. | Software container event monitoring systems |

| WO2021012179A1 (zh) * | 2019-07-23 | 2021-01-28 | 华为技术有限公司 | 存储系统中实现存储业务连续性的方法、前端接口卡和存储系统 |

| CN112363674B (zh) * | 2020-11-12 | 2022-04-22 | 新华三技术有限公司成都分公司 | 一种数据写入方法和装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3732869B2 (ja) * | 1995-06-07 | 2006-01-11 | 株式会社日立製作所 | 外部記憶装置 |

| US6279078B1 (en) | 1996-06-28 | 2001-08-21 | Compaq Computer Corporation | Apparatus and method for synchronizing a cache mode in a dual controller, dual cache memory system operating in a plurality of cache modes |

| US6073218A (en) * | 1996-12-23 | 2000-06-06 | Lsi Logic Corp. | Methods and apparatus for coordinating shared multiple raid controller access to common storage devices |

| US6073209A (en) | 1997-03-31 | 2000-06-06 | Ark Research Corporation | Data storage controller providing multiple hosts with access to multiple storage subsystems |

| US6009535A (en) * | 1997-06-30 | 1999-12-28 | Emc Corporation | SCSI adaptor failover for a disk drive system |

| US6457098B1 (en) | 1998-12-23 | 2002-09-24 | Lsi Logic Corporation | Methods and apparatus for coordinating shared multiple raid controller access to common storage devices |

| US6321298B1 (en) | 1999-01-25 | 2001-11-20 | International Business Machines Corporation | Full cache coherency across multiple raid controllers |

| JP2001256003A (ja) * | 2000-03-10 | 2001-09-21 | Hitachi Ltd | ディスクアレイ制御装置、そのディスクアレイ制御ユニットおよびその増設方法 |

| US6629264B1 (en) | 2000-03-30 | 2003-09-30 | Hewlett-Packard Development Company, L.P. | Controller-based remote copy system with logical unit grouping |

| US6732289B1 (en) * | 2000-08-31 | 2004-05-04 | Sun Microsystems, Inc. | Fault tolerant data storage system |

| US6792505B2 (en) | 2001-04-16 | 2004-09-14 | International Business Machines Corporation | System apparatus and method for storage device controller-based message passing having effective data channel bandwidth and controller cache memory increase |

| US6839788B2 (en) | 2001-09-28 | 2005-01-04 | Dot Hill Systems Corp. | Bus zoning in a channel independent storage controller architecture |

| JP2003140837A (ja) | 2001-10-30 | 2003-05-16 | Hitachi Ltd | ディスクアレイ制御装置 |

| JP2003162439A (ja) * | 2001-11-22 | 2003-06-06 | Hitachi Ltd | ストレージシステム及びその制御方法 |

| JP3714613B2 (ja) | 2001-12-12 | 2005-11-09 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 記憶装置、該記憶装置を含む情報処理装置および情報記憶システムのリカバリ方法 |

-

2002

- 2002-06-14 JP JP2002174944A patent/JP2004021556A/ja active Pending

- 2002-10-18 EP EP02023382A patent/EP1372076B1/en not_active Expired - Fee Related

- 2002-10-18 DE DE60224369T patent/DE60224369T2/de not_active Expired - Lifetime

- 2002-10-28 US US10/282,769 patent/US6959344B2/en not_active Expired - Lifetime

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005309838A (ja) * | 2004-04-22 | 2005-11-04 | Hitachi Ltd | 情報管理システムと情報管理方法、及び、そのための情報管理サブシステム |

| JP4500090B2 (ja) * | 2004-04-22 | 2010-07-14 | 株式会社日立製作所 | 情報管理システムと情報管理方法 |

| US7889639B2 (en) | 2005-12-20 | 2011-02-15 | Fujitsu Limited | Fiber channel switch and computer system using the same |

| JP2010282326A (ja) * | 2009-06-03 | 2010-12-16 | Nec Corp | 情報処理システム、情報処理システムの障害対応機構、及び情報処理システムの障害対応方法 |

| JP2012531656A (ja) * | 2009-11-10 | 2012-12-10 | 株式会社日立製作所 | 複数のコントローラを備えたストレージシステム |

| JP2017215966A (ja) * | 2016-06-01 | 2017-12-07 | シーゲイト テクノロジー エルエルシーSeagate Technology LLC | 記憶デバイスにおける性能変動を制限するための技術 |

| US11216345B2 (en) | 2016-06-01 | 2022-01-04 | Seagate Technology Llc | Technologies for limiting performance variation in a storage device |

| WO2018056044A1 (ja) * | 2016-09-21 | 2018-03-29 | 日本電気株式会社 | 計算機並びにクラスタ管理システム、方法及び非一時的なコンピュータ可読媒体 |

| JPWO2018056044A1 (ja) * | 2016-09-21 | 2019-07-04 | 日本電気株式会社 | 計算機並びにクラスタ管理システム、方法及びプログラム |

| US11119870B2 (en) | 2016-09-21 | 2021-09-14 | Nec Corporation | Calculator, cluster management system, method, and non-transitory computer readable medium |

| JP7006606B2 (ja) | 2016-09-21 | 2022-01-24 | 日本電気株式会社 | 計算機並びにクラスタ管理システム、方法及びプログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1372076A3 (en) | 2006-08-16 |

| US20030233502A1 (en) | 2003-12-18 |

| EP1372076B1 (en) | 2008-01-02 |

| DE60224369T2 (de) | 2008-12-18 |

| DE60224369D1 (de) | 2008-02-14 |

| EP1372076A2 (en) | 2003-12-17 |

| US6959344B2 (en) | 2005-10-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2004021556A (ja) | 記憶制御装置およびその制御方法 | |

| US6968369B2 (en) | Remote data facility over an IP network | |

| EP2659375B1 (en) | Non-disruptive failover of rdma connection | |

| US6970972B2 (en) | High-availability disk control device and failure processing method thereof and high-availability disk subsystem | |

| US7633856B2 (en) | Multi-node system, internodal crossbar switch, node and medium embodying program | |

| JP5959733B2 (ja) | ストレージシステムおよびストレージシステムの障害管理方法 | |

| JP2004220216A (ja) | San/nas統合型ストレージ装置 | |

| JP2007072571A (ja) | 計算機システム及び管理計算機ならびにアクセスパス管理方法 | |

| US20050080887A1 (en) | Redundant management control arbitration system | |

| JP2005215947A (ja) | 複数インタフェースを有する記憶装置、および、その記憶装置の制御方法 | |

| JP2004021556A5 (ja) | ||

| JP4964666B2 (ja) | 冗長化された通信経路を切り替える計算機、プログラム及び方法 | |

| WO1992006435A1 (en) | Message control system in a data communication system | |

| JP3765198B2 (ja) | 計算機システム | |

| JP4572138B2 (ja) | サーバ装置、サーバシステム、及びサーバシステムでの系切り換え方法 | |

| JP2007334668A (ja) | メモリダンプ方法、クラスタシステム、それを構成するノードおよびプログラム | |

| JP2008197907A (ja) | 監視ネットワークシステムおよびデータバックアップ方法 | |

| JP2000020336A (ja) | 二重化通信システム | |

| JP4779948B2 (ja) | サーバシステム | |

| JPH10161907A (ja) | コンピュータシステムの状態監視方法 | |

| JP3260435B2 (ja) | 情報通信システム | |

| KR20220069747A (ko) | 클러스터링 시스템을 위한 전원 공급 장치 | |

| JP2011216059A (ja) | コンピュータシステム、コンピュータシステムの管理方法、ゲートウェイ装置、及びプログラム | |

| JP2021082052A (ja) | 制御装置及び制御プログラム | |

| JP2010033379A (ja) | 仮想化システム及び仮想化の復旧方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040722 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040722 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20040722 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20040928 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060606 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060807 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060807 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070208 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070619 |