-

GEBIET DER ERFINDUNG

-

Die

vorliegende Erfindung betrifft das Gebiet der Computersysteme und

im Besonderen das Gebiet der Bereitstellung einer verbesserten Schnittstelle

zwischen Computerkomponenten.

-

STAND DER TECHNIK

-

Moderne

Computersysteme weisen Zentraleinheiten (CPU 101) auf,

die mit einem Systemspeicher 103 zwischenverbunden sind

(d.h. CPU/Speicher-Subsystem). Wie dies in der Abbildung aus 1 dargestellt ist,

werden Daten und weitere Signale zwischen der CPU und dem Systemspeicher über eine

Komponente übertragen,

die für

gewöhnlich

als Host-Brücke 105 bezeichnet

wird. Die Host-Brücke 105 kann

auch andere Komponenten und/oder Subsysteme in einem Computer mit

einer Schnittstelle zu dem CPU/Speicher-Subsystem versehen.

-

Wie

dies zum Beispiel ferner in 1 dargestellt

ist, können

periphere Komponenten (z.B. eine Tastatur 109, ein Plattenlaufwerk 110 und/oder

eine Maus 111) jeweils über

eine Ein-Ausgabe-Brücke (E/A-Brücke) 107 miteinander

verbunden werden. Die E/A-Brücke 107 kann

wiederum mit der Host-Brücke 105 verbunden

werden, um eine Schnittstelle zwischen den Peripheriegeräten und

dem CPU/Speicher-Subsystem bereitzustellen.

-

Darüber hinaus

können

auch externe Busse (z.B. ein PCI-Bus (Peripheral Component Interconnect-Bus) 113)

an der Schnittstelle zwischen der E/A-Brücke 107 und dem CPU/Speicher-Subsystem

vorgesehen sein. Folglich gestaltet sich die Schnittstelle zwischen

der E/A-Brücke 107 und

dem CPU/Speicher-Subsystem komplizierter und wird mehr eingeschränkt durch

die Spezifikationen/Anforderungen eines externen Busses 113 (z.B. PCI),

der der Schnittstelle zwischen der E/A-Brücke 107 und dem CPU/Speicher-Subsystem hinzugefügt wird.

-

Das

U.S. Patent

US-A-5.687.388 offenbart

eine Master-E/A-Konzentrator mit einem Downstream-Port, der als

ein A-Net-Port (ANP) konfiguriert ist, der mit einem Upstream-Port eines E/A-Konzentrators

verbunden ist. Der Master-E/A-Konzentrator behandelt die Umwandlung

zwischen einer busorientierten Struktur und einer Baumstruktur eines

E/A-Subsystems.

Nachrichten und Befehle werden in dem E/A-Subsystem in definierten

Paketen übertragen.

Verschiedene Lese-, Schreib- und Austauschbefehle werden eingesetzt,

wobei eine Leseantwort verwendet wird, um Split-Transaktions-Leseoperationen

zu ermöglichen.

Leseanforderungen werden durch Downstream-Vorrichtungen eingesetzt,

um aus dem Systemspeicher zu lesen, oder wobei sie von Upstream-Vorrichtungen

verwendet werden, um aus E/A-Vorrichtungen zu lesen. Leseanforderungen

sind Split-Transaktionen, die den Einsatz eines Kanals für andere

Nachrichten während einem

Zeitraum ermöglichen,

während

dem angeforderte Daten aus einer Vorrichtung oder dem Systemspeicher

gelesen werden. Offenbart wird jedoch keine Punkt-zu-Punkt-Schnittstelle

zwischen einem ersten Hub und einem zweiten Hub, exklusive eines

externen Busses, der direkt mit der Schnittstelle verbunden ist,

wobei die Schnittstelle Daten in Paketen über Split-Transaktionen überträgt.

-

Folglich

wird eine verbesserte Schnittstelle zwischen peripheren Komponenten

und Prozessor/Speicher-Subsystemen benötigt.

-

ZUSAMMENFASSUNG DER ERFINDUNG

-

Vorgesehen

ist gemäß der vorliegenden

Erfindung eine Schnittstelle gemäß dem gegenständlichen Anspruch

1.

-

Weitere

Ausführungsbeispiele

der vorliegenden Erfindung sind in den Unteransprüchen enthalten.

-

Vorgesehen

ist gemäß der vorliegenden

Erfindung somit eine Schnittstelle für eine Datenübertragung zwischen

getrennten Hubs in einem Computersystem, mit einem Datensignalpfad

zur Datenübertragung

zwischen Hubs in Paketen über

Split-Transaktionen. In einem Ausführungsbeispiel werden die Daten

in einem quellensynchronen Modus übertragen. In einem Ausführungsbeispiel

weisen die Pakete zur Datenübermittlung

ferner bei Bedarf ein Anforderungspaket und ein Vollzugspaket auf.

In einem Ausführungsbeispiel

weisen die Pakete ferner Transaktionsdeskriptoren auf.

-

KURZE BESCHREIBUNG DER ZEICHNUNGEN

-

Die

vorliegende Erfindung ist in den Abbildungen der beigefügten Zeichnungen

beispielhaft und ohne einzuschränken

veranschaulicht, wobei ähnliche

Elemente in den Abbildungen mit den gleichen Bezugszeichen bezeichnet

sind. Es zeigen:

-

1 ein

Computersystem, das eine Schnittstelle zwischen Computerkomponenten

gemäß dem Stand

der Technik implementiert;

-

2 ein

Blockdiagramm eines Ausführungsbeispiels

eines Computersystems, das die verbesserte Schnittstelle zwischen

Computerkomponenten implementiert;

-

3 ein

Zeitsteuerungs- bzw. Taktdiagramm einer Split-Transaktion, die durch

ein Ausführungsbeispiel

einer Schnittstelle implementiert wird;

-

4 ein

Blockdiagramm eines Ausführungsbeispiels

eines Computersystems, das eine Hierarchie mehrerer verbesserter

Schnittstellen zwischen Computerkomponenten implementiert;

-

5 ein

Zeitsteuerungsdiagramm der Arbitrierung und Übermittlung von Datenpaketen

gemäß einem

Ausführungsbeispiel;

-

6 ein

Zeitsteuerungsdiagramm der Flusssteuerung von Datenpaketen gemäß einem

Ausführungsbeispiel;

-

7 ein

Flussdiagramm der Schritt der Reaktion auf Ablaufsteuerungsoperationen

gemäß einem Ausführungsbeispiel;

-

8 die

physikalische Signalschnittstelle gemäß einem Ausführungsbeispiel;

-

9 ein

Zeitsteuerungsdiagramm der quellensynchronen Taktung gemäß einem

Ausführungsbeispiel;

und

-

10 ein

Computersystem mit mehreren Prozessoren, wobei eine verbesserte

Schnittstelle zwischen Computerkomponenten gemäß einem Ausführungsbeispiel

implementiert wird.

-

GENAUE BESCHREIBUNG

-

Beschrieben

wird eine verbesserte Schnittstelle zwischen Computerkomponenten.

Die Schnittstelle kann hierin als ein Hub-Link bezeichnet werden.

Der Hub-Link ist eine Schnittstelle zur Verbindung von Bausteinen

einer Kernlogik über

eine Schnittstelle mit schmaler und hoher Bandbreite.

-

Wie

dies in der Abbildung aus 2 veranschaulicht

wird, stellt ein Ausführungsbeispiel

des Hub-Link für

einzelne Komponenten eine Punkt-zu-Punkt-Schnittstelle bereit. In

alternativen Ausführungsbeispielen kann

der Hub-Link aber auch eine Schnittstelle zwischen drei oder mehr

Komponenten bereitstellen.

-

Im

Besonderen veranschaulicht die Abbildung aus 2 ein Ausführungsbeispiel

des Hub-Link 202, der

zur Verbindung von zwei getrennten Komponenten (z.B. Hub-Agenten)

in einem Chipsatz miteinander eingesetzt wird. Die Hub-Agenten stellen

eine zentrale Verbindung zwischen zwei oder mehr separaten Bussen und/oder

andersartigen Kommunikationsleitungen bereit.

-

Wie

dies in der Abbildung aus 2 näher dargestellt

ist, weist der Chipsatz zum Beipiel einen Memory Controller Hub 204 (MCH)

und einen Ein-Ausgabe-Hub (E/A-Hub) 206 auf. Der Memory

Controller Hub 204 stellt gemäß der Abbildung aus 2 eine

Zwischenverbindung/einen Hub zwischen einer oder mehreren Zentraleinheiten 208 (CPUs)

und dem Systemspeicher 210 bereit.

-

Der

E/A-Hub 206 stellt eine Zwischenverbindung zwischen verschiedenen

Peripheriekomponenten in dem System bereit (z.B. einer Tastatur 218,

einem Plattenlaufwerk 224, einem Scanner 212 und/oder

einer Maus 220). Ferner werden die externen Busse und deren

Agenten (z.B. PCI-Bus 212 und PCI-Agenten 214) indirekt über den

Hub-Link 202 mit dem Speicher 210 und der CPU 208 verbunden,

indem eine Zwischenverbindung mit dem E/A-Hub 206 hergestellt

wird anstatt eine direkte Zwischenverbindung mit dem Memory Controller

Hub 204.

-

Durch

den Einsatz eines Hub-Link zur Zwischenverbindung des Memory Controller

Hub 204 und des E/A-Hub 206 wird ein verbesserter

Zugriff zwischen E/A-Komponenten und dem CPU/Speicher-Subsystem bereitgestellt

(z.B. erhöhte

Bandbreite, Protokollunabhängigkeit

und geringere Latenz). Darüber

hinaus kann der Hub-Link auch die Skalierbarkeit eines Computersystems

verbessern (z.B. eine Erweiterung von einer Basis-Desktop-Plattform

zu einer Highend-Desktop-Plattform oder Workstation-Plattform),

indem ein Backbone für

E/A-Bausteine bereitgestellt

wird.

-

Zur

Bereitstellung der verbesserten Schnittstelle weist der Hub-Link

ein oder mehrere einzigartige Merkmale auf. In einem Ausführungsbeispiel

werden Transaktionen über

den Hub-Link unter Verwendung eines Split-Transaktionsprotokolls

auf Paketbasis übertragen.

Zum Beispiel wird ein Anforderungspaket eingesetzt, um eine Transaktion

zu beginnen, und wobei ein separates Vollzugspaket in der Folge

eingesetzt werden kann, um eine Transaktion zu beenden, sofern dies

erforderlich ist.

-

Die

Abbildung aus 3 veranschaulicht ein Beispiel

für eine

Split-Transaktion an dem Hub-Link. Wie dies in der Abbildung aus 3 dargestellt

ist, erlangt ein Hub-Agent anfänglich

die Herrschaft über

den Hub-Link durch Arbitrierung 302. Auf die Arbitrierungsphase

folgt eine Anforderungsphase 304. Sofern dies erforderlich

ist (z.B. für

den Fall der Datenrückführung für eine Lesetransaktion),

folgt auf die Anforderungsphase eine Vollzugsphase 308.

Vor der Vollzugsphase arbitriert 306 der antwortende Hub-Agent

jedoch um die Herrschaft über

den Hub-Link.

-

Zwischen

dem Zeitpunkt der Übertragung

eines Anforderungspakets und eines entsprechenden Vollzugspakets über den

Hub-Link können

separate, nicht im Verhältnis

zueinander stehende Pakete gemäß vorbestimmter

Regeln für

die Reihenfolge über

den Hub-Link übertragen

werden, wie dies nachstehend im Text näher beschrieben wird. Für den Fall

einer Leseanforderung von einem Peripheriegerät in den Speicher kann die

Bereitstellung der angeforderten Daten zum Beispiel mehrere Taktzyklen

in Anspruch nehmen, bis die Daten für die Rückführung in einem Vollzugspaket

bereit stehen. Während

dem Zeitraum, der benötigt wird,

um die angeforderten Daten zu erhalten, können separate, nicht im Verhältnis zueinander

stehende Vollzugs- und/oder Anforderungspakete, die in einer Warteschlange/Pipe

des Memory Controller Hub 204 warten, zu dem E/A-Hub 206 übertragen

werden.

-

Wie

dies in der Abbildung aus 3 dargestellt

ist, wird jede Anforderung oder jeder Vollzug ferner als ein Paket über die

Schnittstelle übertragen.

Bei Schreibtransaktionen sind Daten der Anforderung zugeordnet. Bei

Lesetransaktionen sind Daten dem Vollzug zugeordnet. In bestimmten

Fällen

gibt es mehr als einen Vollzug für

eine Anforderung, wenn das Vollzugspaket getrennt ist, wobei eine

effektive Aufteilung in mehrere Vollzugspakete erfolgt.

-

In

einem Ausführungsbeispiel

verwendet der Hub-Link darüber

hinaus Transaktionsdeskriptoren, um den Hub-Link-Verkehr zu leiten

sowie um die Attribute einer Transaktion zu identifizieren. Zum

Beispiel können die

Deskriptoren eingesetzt werden, um eine Transaktion als isochron

oder asynchron zu definieren, die als Folge dessen gemäß einem

vordefinierten Protokoll behandelt werden kann.

-

In

einem Ausführungsbeispiel

wird ferner die Bandbreite der Schnittstelle teilweise dadurch erhöht, dass

die Datenpakete über

einen quellensynchronen Taktmodus übertragen werden. In einem

Ausführungsbeispiel

stellt der Hub-Link ferner die erhöhte Bandbreite trotz einer

schmalen Verbindung bereit (z.B. weniger Pins/Anschlussflächen).

-

In

alternativen Ausführungsbeispielen

kann ein Hub-Link jedoch auch mit weniger als allen vorstehend beschriebenen

eindeutigen Merkmalen implementiert werden, ohne dabei von dem Umfang

der vorliegenden Erfindung abzuweichen. Ferner kann der Hub-Link

auch verwendet werden, um Brücken

miteinander zu verbinden und/oder die Komponenten in einem Chipsatz

oder außerhalb

eines Chipsatzes, ohne dabei vom Umfang der vorliegenden Erfindung

abzuweichen.

-

TRANSAKTIONS-, PROTOKOLL- UND PHYSIKALISCHE

SCHICHTEN

-

Zur

deutlicheren Veranschaulichung wird der Hub-Link hierein in drei

Abschnitten beschrieben: einer Transaktionsschicht, einer Protokollschicht

und einer physikalischen Schicht. Die Unterscheidungen zwischen den

Schichten dienen jedoch einem veranschaulichenden Zweck und haben

keine einschränkende

Funktion, und somit wird dadurch kein spezielles bevorzugtes Ausführungsbeispiel

impliziert.

-

TRANSAKTIONSSCHICHT

-

In

einem Ausführungsbeispiel

des Hub-Link unterstützt

die Transaktionsschicht das Routing bzw. Leiten separater Transaktionen,

die über

den Hub-Link übertragen

werden (wobei sie ein oder mehrere Pakete aufweisen können). In

einem Ausführungsbeispiel

erzeugt die Transaktionsschicht des Hub-Link zum Beispiel Transaktionsdeskriptoren,

die in den Anforderungs- und Datenpaketen enthalten sind. Die Transaktionsdeskriptoren

können

zur Unterstützung

der Arbitrierung zwischen Warteschlangen in einem Hub-Agenten (z.B. MCH)

eingesetzt werden und/oder zur Erleichterung des Routing von Anforderungen

und Datenpaketen durch den Hub-Link.

-

In

einem Ausführungsbeispiel

unterstützen

zum Beispiel die Transaktionsdeskriptoren das Leiten von Vollzugspaketen

zurück

zu dem die Anforderung einleitenden Agenten auf der Basis der ursprünglich bereitgestellten

(in einem Anforderungspaket) Routing-Informationen. Die Transaktionsdeskriptoren

unterstützen ferner

die Reduzierung oder möglicherweise

Minimierung der Paketdecodierungslogik in den Hub-Agenten.

-

In

alternativen Ausführungsbeispielen

stellen die Transaktionsdeskriptoren ferner die Fähigkeit

bereit, die Behandlung von Anforderungen auf der Basis ihrer entsprechenden

Transaktionsattribute zu unterscheiden. Zum Beispiel können die

in den Transaktionsdeskriptoren identifizierten Transaktionsattribute

Operationen als isochron identifizieren (d.h. Operationen, die feste

Datenmengen unregelmäßig transportieren;

wie zum Beispiel Video- oder Audio-Echtzeitoperationen). Als Folge

dessen können

die durch die Transaktionsattribute identifizierten Operationen

gemäß einem

entsprechenden vorbestimmten Routing-Protokoll behandelt werden,

um eine bestimmte Art von Operation zu unterstützen (z.B. isochron).

-

In

einem Ausführungsbeispiel

weisen die Transaktionsdeskriptoren zwei Felder auf: ein Routing-Feld und

ein Attributfeld. In alternativen Ausführungsbeispielen können mehr

oder weniger Felder verwendet werden, um eine oder mehrere der Funktionen

der Transaktionsdeskriptoren bereitzustellen, ohne dabei vom Umfang

der Erfindung abzuweichen.

-

In

einem Ausführungsbeispiel

handelt es sich bei dem Routing-Feld um ein Feld mit sechs Bit,

das für das

Paket-Routing eingesetzt wird, wie dies unten in Tabelle 1 dargestellt

ist. Die Größe des Routing-Felds sowie

des Attributfelds kann gemäß dem Umfang

der vorliegenden Erfindung variieren. Tabelle

1: Routing-Feld des Transaktionsdeskriptors

-

Wie

dies in Tabelle 1 dargestellt ist, werden drei Bits des Routing-Felds

für die

Hub-ID eingesetzt, welche den Hub-Agenten identifiziert, der die

Transaktion eingeleitet hat. In alternativen Ausführungsbeispielen können zusätzliche

Bits in dem Routing-Feld eingesetzt werden, um eine Hub-Link-Hierarchie

bereitzustellen, die 8 überschreitet.

-

In

einem System können

zum Beispiel mehrere Hub-Link-Hierarchiene existieren, wobei in

diesem Fall der Agent an der Spitze der Hierarchien in der Lage

sein sollte, Vollzüge

zurück

zur Basis der Hierarchie zu leiten. In diesem Zusammenhang umfasst "Hierarchie" mehrere verbundene

Hub-Link-Segmente, die mit einem Hub-Link "Wurzel"-Agenten (z.B. einem Memory Control

Hub) beginnen. Die Abbildung aus 2 veranschaulicht

zum Beispiel ein System, das nur eine Hub-Link-Hierarchie aufweist.

Die Abbildung aus 4 hingegen veranschaulicht ein

Beispiel für

ein System auf der Basis von zwei Hub-Link-Hierarchien. In Ausführungsbeispielen,

die nur eine Hub-Link-Hierarchie implementieren, kann ein Standardwert

von "000" in dem Hub-ID-Feld

verwendet werden.

-

Die

verbleibenden drei Bits des Routing-Felds können eingesetzt werden, um

interne Leitungen bzw. Pipes/Warteschlangen in einem Hub-Link-Agenten

zu identifizieren. Zum Beispiel kann der E/A Control Hub bzw. Steuerungs-Hub

den internen USB (Universal Serial Bus) Host-Controller-Verkehr

und den Bus Mastering-ID (BM-ID) Verkehr über separate Leitungen bzw. "Pipes" unterstützen. Dabei

kann die Pipe-ID dazu eingesetzt werden, dem behandelnden Agenten

(z.B. MCH) mitzuteilen, dass der durch verschiedene "Pipes" eingeleitete Verkehr

unterschiedliche Attribute aufweist und gemäß einem vorbestimmten Protokoll

behandelt werden kann. Wenn ein Hub-Link-Agent keine separaten internen

Pipes implementiert, so kann er in dem Feld Pipe-ID einen Standardwert

von "000" verwenden.

-

In

einem alternativen Ausführungsbeispiel

weisen die Transaktionsdeskriptoren ferner ein Attributfeld auf.

In einem Ausführungsbeispiel

handelt es sich bei dem Attributfeld um einen Drei-Bit-Wert, der

spezifiziert, wie eine Transaktion zu behandeln ist, wenn sie von

einem Ziel-Hub-Link-Agenten empfangen wird. In bestimmten Fällen unterstützt das

Attributfeld ein System bei der Unterstützung anspruchsvoller Anwendungsauslastungen,

welche auf der Bewegung bzw. dem Transport und der Verarbeitung

von Daten mit spezifischen Anforderungen oder anderen sich unterscheidenden

Eigenschaften beruhen.

-

Zum

Beispiel kann das Attributfeld die isochrone Datenbewegung zwischen

Vorrichtungen unterstützen,

wie diese von einigen in letzter Zeit entwickelten externen Bussen

(z.B. IEEE 1394 und USB) verwendet werden. Derartige Datenbewegungsanforderungen

müssen

erhalten werden, wenn Daten durch den Hub-Link zwischen E/A-Vorrichtungen

und dem CPU/Speicher-Subsystem fließen.

-

In

alternativen Ausführungsbeispielen

können

zusätzliche

Transaktionsattribute die Fähigkeit

umfassen, zwischen "snooped" Verkehr, bei dem

die Cache-Kohärenz

durch Hardware erzwungen wird (d.h. einen Chipsatz) und "non-snooped" Verkehr zu unterscheiden,

wobei letzterer auf Softwaremechanismen basiert, um eine Datenkohärenz in

dem System zu gewährleisten.

Ferner wäre

ein weiteres mögliches

Attribut ein Hinweis "ausdrücklich vorab

erfassbar", um eine

Form des Lesens des Caches zu unterstützen und eine effizientere

Nutzung der Hauptspeicher-Bandbreite zu ermöglichen.

-

Regeln zur Reihenfolge

-

Die

Transaktionsdeskriptoren können

auch zur Unterstützung

der Regeln zur Reihenfolge bzw. Anordnung zwischen über den

Hub-Link übertragenen

Transaktionen eingesetzt werden. In einem Ausführungsbeispiel werden zum Beispiel

Transaktionen mit identischen Transaktionsdeskriptoren strikt nach

Reihenfolge ausgeführt

(d.h. die erste Transaktion wird zu erst behandelt).

-

Transaktionen

mit dem gleichen Routing-Feld, jedoch unterschiedlichen Attributfeldern,

können

im Verhältnis

zueinander neu angeordnet werden. In einem Ausführungsbeispiel müssen zum

Beispiel isochrone Transaktionen nicht in strikter Reihenfolge in

Bezug auf asynchrone Transaktionen geordnet werden.

-

In

einem Ausführungsbeispiel

der Hub-Link-Schnittstelle können

Datenübertragungen

darüber

hinaus über

Anforderungen hinaus fortschreiten, und zwar entweder in die gleiche

Richtung oder in die entgegengesetzte Richtung. Lesevollzüge, die

in eine Richtung verlaufen, können

Leseanforderungen vorbeilaufen lassen, die in die gleiche Richtung

fließen.

Und Schreibanforderungen können

Leseanforderungen passieren lassen, die in die gleiche Richtung

verlaufen.

-

In

alternativen Ausführungsbeispielen

können

die Regeln für

die Anordnung bzw. die Reihenfolge von Transaktionen, die über die

Hub-Link-Schnittstelle verlaufen, jedoch gemäß dem Umfang der vorliegenden

Erfindung variieren. In einem Ausführungsbeispiel implementiert

der Hub-Link zum Beispiel die Regeln für die Anordnung, die in Peripheral

Component Interconnect (PCI) (Revision 2.2) bereitgestellt werden,

um den Verkehrsfluss über

den Hub-Link in entgegengesetzte Richtungen zu bestimmen.

-

PROTOKOLLSCHICHT

-

In

einem Ausführungsbeispiel

verwendet der Hub-Link ein Protokoll auf Paketbasis mit zwei Arten

von Paketen: Anforderung und Vollzug. Ein Anforderungspaket wird

für jede

Hub-Link-Transaktion

verwendet. Vollzugspakete werden nach Bedarf eingesetzt, wie zum

Beispiel zur Rückführung gelesener

Daten oder zur Bestätigung

der Ausführung

(Vollzug) bestimmter Arten von Schreibtransaktionen (z.B. E/A-Schreibtransaktionen und

Speicherschreibtransaktionen mit angefordertem Vollzug). Vollzugspakete

sind ihren entsprechenden Anforderungspaketen über Transaktionsdeskriptoren

und die Anordnung bzw. die Reihenfolge zugeordnet, wie dies vorstehend

in dem Abschnitt über

die Transaktionsschicht beschrieben worden ist.

-

Darüber hinaus

verwendet die Hub-Link-Schnittstelle in einem Ausführungsbeispiel

ein Arbitrierungsprotokoll, das symmetrisch ist und verteilt. Zum

Beispiel steuert jeder Hub-Agent

ein Anforderungssignal, das von dem anderen Agenten überwacht

wird, der mit der gleichen Schnittstelle verbunden ist. Es wird

kein Gewährungssignal

eingesetzt, und Agenten bestimmen die Herrschaft über die

Schnittstelle unabhängig.

-

In

einem Ausführungsbeispiel

wird ferner kein ausdrückliches

Rahmensignal bzw. Framing-Signal

eingesetzt. Es existiert ein impliziertes Verhältnis zwischen dem Arbitrierungsereignis,

das einem Agenten die Herrschaft über die Schnittstelle verleiht

und dem Beginn der Übertragung

des Agenten. In einem alternativen Ausführungsbeispiel können Framing-Signale eingesetzt

werden, ohne dabei vom Umfang der Erfindung abzuweichen.

-

Das

Ende der Paketübermittlung

tritt auf, wenn ein Hub-Link-Agent, der die Herrschaft über die Schnittstelle

besitzt (z.B. sich im Prozess der Übermittlung von Daten befindet),

die Steuerung der Schnittstelle durch Deaktivierung eines Anforderungssignals

freigibt. In einem Ausführungsbeispiel

wird die Ablaufsteuerung darüber

hinaus auch unter Verwendung eines Signals STOP (Stoppsignal) für einen

neuen Versuch oder zur Trennung von Paketen erreicht, wie dies nachstehend

im Text näher

beschrieben wird.

-

Paketdefinition

-

In

einem Ausführungsbeispiel

des Hub-Link werden Daten mit einem Vielfachen der Rate (z.B. 1x,

4x, 8x) des Hub-Link-Takts (HLCK) übertragen, bei dem es sich

in einem Ausführungsbeispiel

um einen gemeinsamen Takt handelt, den die mit dem Hub-Link verbundenen

Hub-Agenten gemeinsam nutzen.

-

Die

Daten werden über

einen Datensignalpfad (PD) des Hub-Link übertragen, der eine "Schnittstellenbreite" der gleichen Zweierpotenz

(z.B. 8, 16, 24, 32) aufweist. Somit kann der Hub-Link unterschiedliche

Datenübertragungs-Körnigkeiten

(d.h. Übertragungsbreiten)

aufweisen, abhängig

von der Übertragungsrate

und der Breite des Datensignalpfads. Zum Beispiel für den Fall

einer Schnittstellenbreite von acht Bit in dem 4x Modus entspricht

die Übertragungsbreite

32 Bits je HLCK. Durch Veränderung

bzw. Anpassung der Übertragungsrate

und/oder der Schnittstellenbreite des Datensignalpfads kann somit

die Übertragungsbreite

(d.h. die Anzahl der je HLCK übertragenen

Bytes) skaliert werden.

-

In

einem Ausführungsbeispiel

können

ferner Pakete größer sein

als die Übertragungsbreiten.

Somit werden die Pakete in mehreren Abschnitten übertragen (d.h. Paketbreiten).

In einem Ausführungsbeispiel

werden die Pakete in Paketbreiten aufgeteilt, welche die Größe von Doppelwörtern (32

Bits) aufweisen.

-

Für den Fall

einer Übertragungsbreite

von 32 Bits, werden die Bytes einer Paketbreite an der Schnittstelle

beginnend mit dem wertniedrigsten Byte (Byte 0) präsentiert,

wobei das werthöchste

Byte (Byte 3) den Abschluss bildet, wie dies nachstehend in Tabelle

2 dargestellt ist. Für

den Fall einer Übertragungsbreite

von 64 Bits (z.B. eine Schnittstelle mit einer Breite von sechzehn

Bit im 4x Modus) wird das wertniedrigste Doppelwort (Paketbreite)

auf den unteren Bytes des Datensignals (z.B. PD[0:7]) übertragen,

und das werthöhere

Doppelwort wird parallel auf den oberen Bytes des Datensignals (z.B.

PD[15:8]) übertragen.

Die beiden Beispiele sind nachstehend in Tabelle 2 dargestellt. Tabelle

2: Byte-Übertragungsreihenfolge

für Schnittstellenbreiten

von 8 und 16 Bit

-

Die

Protokollschicht der Hub-Link-Schnittstelle ist auch für das Begrenzen

bzw. Rahmen der Daten verantwortlich. Dabei definieren die durch

den Hub-Link implementierten Framing-Regeln, wie eine oder mehrere Paketbreiten

auf eine Reihe von Übertragungsbreiten

abgebildet werden. Zur Vereinfachung der Analyse bzw. des Parsing

der Pakete in Paketbreiten, werden in einem Ausführungsbeispiel des Hub-Link

die folgenden drei Begrenzungsregeln implementiert: ein Header-Abschnitt

eines Pakets beginnt bei dem ersten Byte einer Übertragungsbreite; ein Datenabschnitt

eines Pakets (sofern vorhanden) beginnt an dem ersten Byte einer Übertragungsbreite;

und ein Paket belegt eine integrale Anzahl von Übertragungsbreiten.

-

Jede

verfügbare Übertragungsbreite,

die von einem Paket nicht eingesetzt wird, kann mit einem Übertragung

eines Scheindoppelwortes (DW) gefüllt werden und wird von dem

empfangenden Hub-Agenten ignoriert. In alternativen Ausführungsbeispielen

können

mehr, weniger und/oder andere Begrenzungsregeln gemäß dem Umfang

der vorliegenden Erfindung durch den Hub-Link verwendet werden.

-

Die

nachstehend aufgeführten

Tabellen 3 und 4 veranschaulichen Beispiele für die vorstehend aufgeführten Begrenzungsregeln

in Bezug auf den Fall einer 64-Bit-Übertragungsbreite. Tabelle

3: Anforderung unter Verwendung einer 32-Bit-Adressierung und mit

drei Doppelwörtern

an Daten

Tabelle

4: Anforderung unter Verwendung einer 64-Bit-Adressierung und mit

drei Doppelwörtern

an Daten

-

Anforderungspakete

-

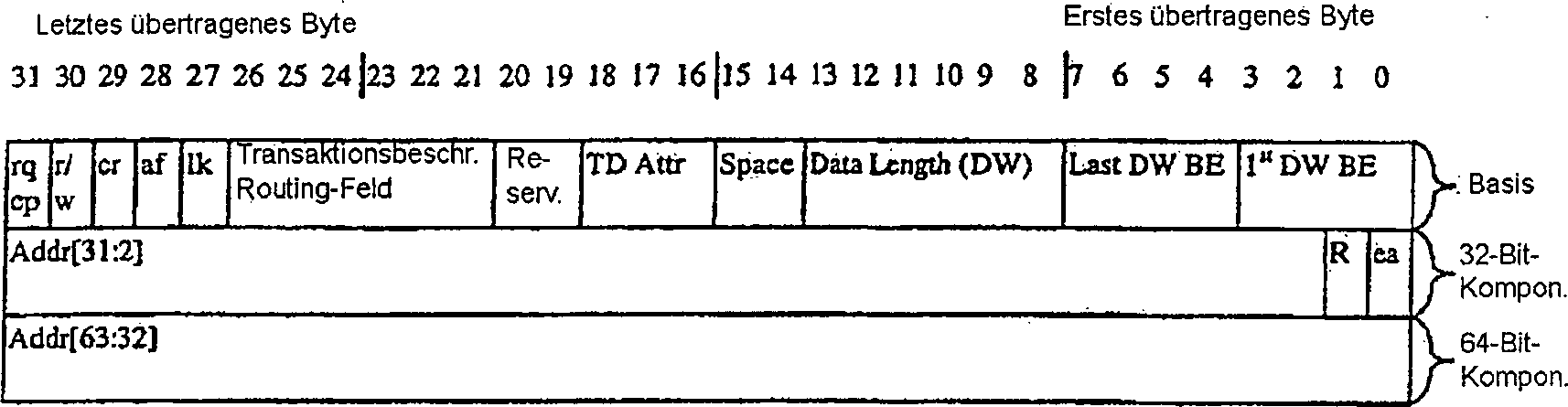

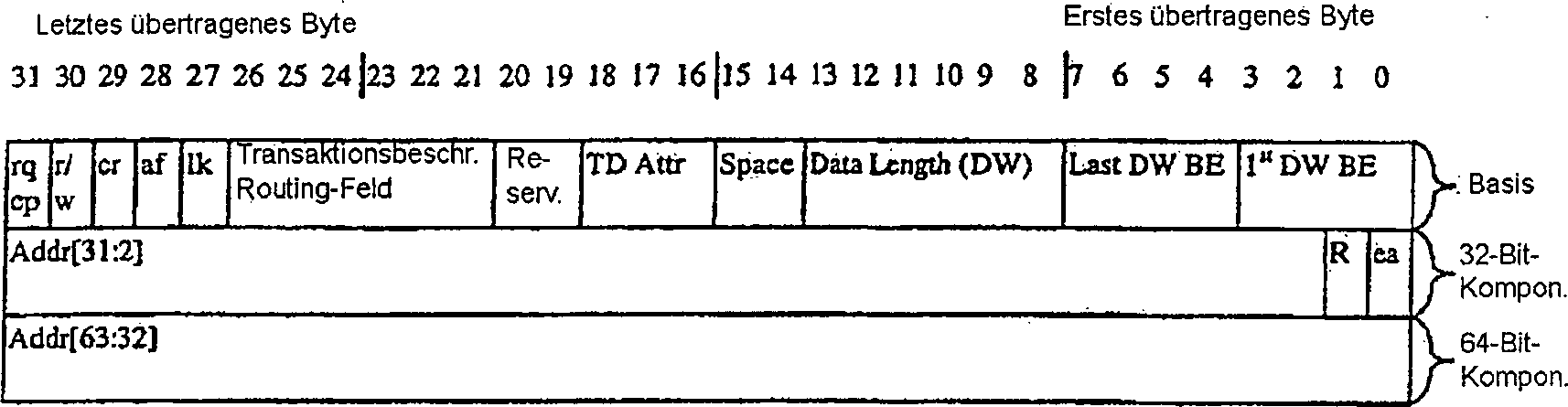

Das

Paket-Header-Format für

Anforderungspakete gemäß einem

Ausführungsbeispiel

ist in den Tabellen 5 und 6 dargestellt. In den Beispielen aus den

Tabellen 5 und 6 entspricht der Basis-Header einem Doppelwort, wobei

ein zusätzliches

Doppelwort für

die 32-Bit-Adressierung

benötigt

wird, und wobei zwei zusätzliche

Doppelwörter

für den

64-Bit- Adressierungsmodus

benötigt

werden. Die Felder der Header gemäß den Darstellungen in den

Tabelle 5 und 6 werden anschließend

an die Tabellen beschrieben.

-

In

alternativen Ausführungsbeispielen

des Hub-Link können

die Felder in dem Header des Anforderungspakets variieren, ohne

dabei vom Umfang der vorliegenden Erfindung abzuweichen. Zum Beispiel

kann der Header zusätzliche

Felder, weniger Felder oder andere Felder an Stelle der nachstehend

dargestellten Felder aufweisen. Ferner kann die Codierung der Felder

ebenfalls variieren, ohne dabei vom Umfang der vorliegenden Erfindung

abzuweichen. Tabelle

5: Anforderungspaket-Header-Format für 32-Bit-Adressierung

Tabelle

6: Anforderungspaket-Header-Format für 64-Bit-Adressierung

| Transaktionsdeskriptor | Die

Transaktionsdeskriptorfelder Routing und Attribut gemäß der vorstehenden

Beschreibung. |

| rq/cp | Anforderungspakete

sind an dieser Stelle mit '0' identifiziert; Vollzugspakete

mit '1'. |

| r/w | Lesen

('0') oder Schreiben

('1'). Dieses Feld zeigt

an, wenn Daten in einem Vollzug (Lesen) oder einer Anforderung (Schreiben)

enthalten sind. |

| Adressierungsformat

(af) | Das

Adressierungsformat ist entweder impliziert ('0')

oder 32/64 Bit ('1'). |

| Sperre

(lk) | Flagge

zum Anzeigen, dass die Anforderung Teil einer gesperrten Sequenz

ist. Bei Anforderungen und Vollzügen

in einer gesperrten Sequenz ist dieses Bit gesetzt. Hub-Agenten,

die eine Sperre nicht verstehen, ignorieren diese Flagge und füllen dieses

Feld mit '0'. |

| Datenlänge (Data

Length) | Die

Datenlänge

ist in Doppelwörtern

angegeben, so codiert, dass die Anzahl der dargestellten Doppelwörter eins

plus dieser Zahl entspricht. Somit stellt "000000" ein Doppelwort dar. |

| Raum

(Space) | Dieses

Feld wählt

die Art des Zielraums für

die Anforderung aus. In einem Ausführungsbeispiel zählen zu

den möglichen

Zielräumen

Speicher ("00") und EA ("01"). |

| 1st

DW BE | Bytefreigaben

für das

erste Doppelwort jeder Lese- oder Schreibanforderung an Speicher

oder EA. Bytefreigaben sind aktiv niedrig. Wenn nur ein Doppelwort

für eine

Anforderung gegeben ist, wird dieses Bytefreigabefeld verwendet.

In einem Ausführungsbeispiel

ist es unzulässig, eine

Speicher- oder EA-Leseoder Schreibanforderung auszugeben, wenn keine

Bytes freigegeben sind. |

| Last

DW BE | Bytefreigaben

für das

letzte Doppelwort jeder Lese- oder Schreibanforderung. Bytefreigaben

sind aktiv niedrig. Wenn nur ein Doppelwort für eine Anforderung gegeben

ist, muss dieses Feld inaktiv sein ("1111"). Bytefreigaben

können

nicht zusammenhängend

sein (z.B. "0101"). Dieses Feld wird

in Verbindung mit besonderen Zyklen nie verwendet, da es das Feld "Spezialzykluscodierung" überlappt. |

| Addr[31:2] | Die

32-Bit-Adresse wird wie bei PCI für die gleiche Zyklusart erzeugt. Dieses

Doppelwort ist für

die 32- und die 64-Bit-Adressierungsmodi enthalten (jedoch nicht

für den

implizierten Adressierungsmodus). |

| Erweiterte

Adresse (ea) | Zeigt

32-Bit-Adressierung ('0') oder 64-Bit-Adressierung ('1') an. |

| Konfig.typ

(ct) | Nur

für Konfigurationszyklen

wird dieses Bit verwendet, um den Konfigurationszyklustyp Typ 0

('0') oder Typ 1 ('1') anzuzeigen. Da Konfigurationszyklen

mit 32-Bit-Adressierung ausgeführt

werden, wird dieses Bit überlappt

von dem Bit "Erweiterte

Adresse". |

| Addr[63:32] | Die

oberen Adressbits für

den 64-Bit-Adressierungsmodus. Dieses Doppelwort ist für den 64-Bit-Adressierungsmodus

enthalten. |

-

Vollzugspakete

-

Das

Header-Format für

ein Vollzugspaket gemäß einem

Ausführungsbeispiel

ist nachstehend in Tabelle 7 dargestellt. In einem Ausführungsbeispiel

handelt es sich bei dem Header um ein Doppelwort. Die Felder der

Header gemäß der Darstellung

in Tabelle 8 werden im Anschluss an die Tabelle beschrieben.

-

In

alternativen Ausführungsbeispielen

des Hub-Link können

die in dem Header für

ein Vollzugspaket enthaltenen Felder jedoch variieren, ohne dabei

vom Umfang der vorliegenden Erfindung abzuweichen. Zum Beispiel

kann der Header zusätzliche

Felder, weniger Felder oder andere Felder an Stelle der beschriebenen und

nachstehend dargestellten Felder aufweisen. Ferner kann die Codierung

der Felder ebenfalls variieren, ohne dabei vom Umfang der Erfindung

abzuweichen.

Tabelle

7: Header-Format für

ein Vollzugspaket

| Transaktionsdeskriptor | Die

Transaktionsdeskriptorfelder Routing und Attribut gemäß der vorstehenden

Beschreibung in dem Transaktionsabschnitt. |

| rq/cp | Vollzugspakete

sind an dieser Stelle mit '1' identifiziert. |

| r/w | Lesen

('0') oder Schreiben

('1'). Dieses Feld zeigt

an, wenn Daten in einem Vollzug (Lesen) oder einer Anforderung (Schreiben)

enthalten sind. |

| Sperre

(lk) | Flagge

zum Anzeigen, dass die Ausführung

Teil einer gesperrten Sequenz ist. Bei Anforderungen und Vollzügen in einer

gesperrten Sequenz ist dieses Bit gesetzt. Agenten, die eine Sperre

nicht verstehen, ignorieren diese Flagge und füllen dieses Feld mit '0'. |

| Datenlänge (Data

Length) | Die

Datenlänge

ist in Doppelwörtern

angegeben, so codiert, dass die Anzahl der dargestellten Doppelwörter eins

plus dieser Zahl entspricht. Somit stellt "000000" ein Doppelwort dar. |

| Ausführungsstatus | Zeigt

Ausführungsstatus

unter Verwendung vorbestimmter Werte an. |

| Reserviert | Alle

reservierten Bits sind auf '0' gesetzt. |

-

In

einem Ausführungsbeispiel

des Hub-Link können

Ausführungen

bzw. Vollzüge

für Speicherleseoperationen

weniger als die vollständige

angeforderte Datenmenge bereitstellen, solange die vollständige Anforderung

letztlich ausgeführt

wird. In ähnlicher

Weise können

Vollzüge

für Speicherschreiboperationen

anzeigen, dass weniger als die ganze Anforderung ausgeführt worden

ist. Dies kann vorgenommen werden, um eine bestimmte Hub-Link-Schnittstellenlatenzanforderung

für eine

bestimmte Plattform zu erfüllen.

-

Für eine Anforderung,

welche einen Vollzug erfordert, verwaltet der Initiator in einem

Ausführungsbeispiel

darüber

hinaus Informationen über

die Anforderung, die in einem Puffer des einleitenden Hub-Agenten gespeichert

werden können.

Zum Beispiel können

diese Informationen den Transaktionsdeskriptor, die Größe des Pakets,

den Sperrstatus, Routing-Informationen,

etc. aufweisen. Beim Empfang des Vollzugs bzw. der Vollzüge passt

der Initiator ferner den Vollzug bzw. die Vollzüge an die entsprechende Anforderung

an. Für

den Fall mehrerer Vollzüge

akkumuliert der Initiator einen Zählwert der für die ursprüngliche Anforderung

ausgeführten

Daten, bis die ursprüngliche

Anforderung vollständig

ausgeführt

ist.

-

Schnittstellen-Arbitrierung

und Paketbegrenzung

-

Wenn

in einem Ausführungsbeispiel

der Hub-Schnittstelle sich die Schnittstelle im Ruhezustand befindet,

so gilt die Geltendmachung bzw. Aktivierung von einem mit der Schnittstelle

verbundenen Hub-Agenten als ein Arbitrierungsereignis. Der erste

Agent, der eine Anforderung stellt, gewinnt die Herrschaft über die Schnittstelle.

Wenn der Agent die Herrschaft gleichzeitig zu dem Zustand anfordert,

wenn der Hub-Link sich im Ruhezustand befindet, so ist der zuletzt

behandelte Hub-Agent erfolgreich. In einem Ausführungsbeispiel verfolgen alle

Hub-Agenten den zuletzt behandelten Status bzw. Zustand (z.B. über eine

Statusflagge eines internen Registers). In einem alternativen Ausführungsbeispiel

können

alternative Arbitrierungsroutinen gemäß dem Umfang der vorliegenden

Erfindung verwendet werden.

-

Nachdem

ein Hub-Agent die Herrschaft über

die Schnittstelle errungen hat, beherrscht er die Schnittstelle,

bis die Transaktion ausgeführt

ist oder bis eine zugewiesene zeitliche Bandbreite abgelaufen ist.

In einem Ausführungsbeispiel

ist zum Beispiel in jedem Hub-Agenten ein Zeitscheibenzähler bereitgestellt,

um die Bandbreitenzuordnung zu steuern bzw. zu regeln und um die

Dauer der Herrschaft über

eine Schnittstelle für einen

Agenten zu begrenzen. Die einem Hub-Agenten zugeordnete Zeit (d.h.

der Zeitscheibenwert) kann für die

Hub-Link-Agenten,

die mit der gleichen Schnittstelle verbunden sind, unterschiedlich

oder gleich sein. Der Zeitscheibenzähler startet mit dem Erlangen

der Herrschaft über

die Schnittstelle und zählt

Hub-Link-Basistaktperioden.

-

In

einem Ausführungsbeispiel

ist jeder Hub-Agent dafür

zuständig,

seine eigene Zeitscheibenzuordnung zu verwalten. In einem Ausführungsbeispiel

kann diesbezüglich

ein Zeitscheibenwert über

ein Hub-Link-Befehlsregister für

jede Schnittstelle in jedem Hub-Agenten

programmiert werden.

-

Die

Abbildung aus 5 veranschaulicht ein Beispiel

für die

Arbitrierung für

die Hub-Link-Schnittstelle zwischen

dem Hub-Agenten A und dem Agenten B sowie für die Übertragung von zwei Paketen.

Das Beispiel veranschaulicht die Arbitrierung aus einem ruhenden

Schnittstellenzustand bzw. Wartezustand, wobei die Schnittstelle

danach in den Ruhezustand zurückkehrt.

In dem veranschaulichten Beispiel verwendet die Schnittstelle ferner

einen 4x-Datenübertragungsmodus

mit einem Datensignalpfad (PD) von acht Bit. Der Agent A ist in

dem in der Abbildung aus 5 veranschaulichten Beispiel

der zuletzt behandelte (MRS) Agent. Folglich aktiviert der Agent

A sein externes Anforderungssignal (RQA) und tastet den Zustand

des Anforderungssignals des Agenten B (RQB) an der Taktflanke 1

(die inaktiv dargestellt ist) ab, bevor die Paketübermittlung

von der gleichen Flanke beginnt.

-

In

einem Ausführungsbeispiel

ist eine Verzögerung

um zwei Takte gegeben, bevor die übermittelten Daten (d.h. Daten

von dem Agenten A) in dem Empfänger

(d.h. Agent B) zur Verfügung

stehen, beginnend mit der Taktflanke 3. Das erste Paket besteht

aus zwei Doppelwörtern 502 und 504 und

erfordert zwei Basis- bzw. Grundtakte für die Übermittlung in dem 4x Modus.

Das zweite Paket weist drei Doppelwörter 506, 508 und 510 auf

und erfordert somit drei Basistakte in dem 4x Modus.

-

Flusssteuerung

-

In

einem Ausführungsbeispiel

können

Pakete durch einen empfangenden Agenten wiederholt oder getrennt

werden aufgrund des Fehlens von Anforderungswarteschlangenplatz,

Datenpufferplatz sowie aus anderen Gründen. In einem Ausführungsbeispiel

wird die Flusssteuerung unter Verwendung eines Signals STOP erreicht.

-

Die

Abbildung aus 6 veranschaulicht ein Beispiel

des Einsatzes des Signals STOP. Gemäß der Darstellung aktiviert

der Agent A sein externes Anforderungssignal (RQA) und tastet den

Zustand des Anforderungssignals (RQB) des Agenten B an der Taktflanke

1 (die inaktiv dargestellt ist) ab, bevor die Paketübermittlung

von der gleichen Flanke (z.B. der Taktflanke 1) einsetzt.

-

Nach

einer Verzögerung

um zwei Takte stehen die von dem Agenten A übermittelten Daten in dem Empfänger an

dem Agenten B zur Verfügung,

beginnend von der Taktflanke 3. In einem Ausführungsbeispiel besteht nach

dem Empfang der von dem Agenten A übermittelten Daten die erste

Möglichkeit

für den

Agenten B, die Flusssteuerung einzuleiten, indem das Signal STOP

geltend gemacht wird, wie dies in der Abbildung aus 6 dargestellt

ist, an der Taktflanke 4.

-

Wenn

ferner die Herrschaft über

das PD-Signal ferner von einem Hub-Agenten zu einem anderen Agenten

wechselt, wird auch die Herrschaft über das Signal STOP nach einer

vorbestimmten Anzahl von Takten ausgetauscht. In einem Ausführungsbeispiel

wird das Signal STOP ferner bei den Basistakten abgetastet, was

der letztendlichen Übertragung

einer Paketbreite entspricht. Zum Beispiel in einem 4x Modus (unter

Verwendung eines PD-Signals mit einer Breite von acht Bit) wird

das Signal STOP bei jedem Basistakt abgetastet. In Bezug auf einen

1x Modus wird das Signal STOP jedoch bei jedem vierten Takt abgetastet

(wobei der Anfang einer Transaktion als ein Referenzpunkt verwendet

wird).

-

Nach

dem Empfang eines Signals STOP, bestimmt der Hub-Agent, der das

Signal STOP empfängt, ob

er das Senden weiterer Pakete wiederholen soll. Die Abbildung aus 7 zeigt

ein Flussdiagramm der Schritte, die ein Hub-Agent während der

Bestimmung ausführt,

ob er nach dem Empfang eines Signals STOP gemäß einem Ausführungsbeispiel

das Senden eines Pakets wiederholen soll.

-

In

dem Schritt 702 empfängt

ein Hub-Agent, der gerade Pakete übermittelt, ein Signal STOP.

Als Reaktion darauf bestimmt der Hub-Agent, der das Signal STOP

empfangt, in dem Schritt 704, ob der andere Agent (der

das Signal STOP aktiviert hat), die Herrschaft über die Schnittstelle anfordert,

indem das Anforderungssignal (z.B. RQB) der anderen Hub-Agenten

abgetastet wird.

-

Wenn

der Empfänger

des Signals STOP bestimmt, dass der Agent, der das Signal STOP gesendet hat,

nicht die Herrschaft bzw. Kontrolle über die Schnittstelle anfordert,

so kann in dem Schritt 706 der aktuelle Eigentümer der

Schnittstelle versuche, nach der Wiederherstellung nach dem STOP

ein Paket zu übermitteln. Wenn

andererseits bestimmt wird, dass der Agent, der das Signal STOP

aktiviert hat, die Kontrolle anfordert, bestimmt in dem Schritt 708 der

aktuelle Eigentümer,

ob dessen Zeitscheibe bzw. Zeitschlitz abgelaufen ist.

-

Wenn

die Zeitscheibe für

den aktuellen Eigentümer

bzw. Herrscher über

die Schnittstelle abgelaufen ist, gibt der aktuelle Eigentümer in dem

Schritt 710 die Kontrolle frei. Wenn die Zeitscheibe für den aktuellen Eigentümer noch

nicht abgelaufen ist, kann der aktuelle Eigentümer ein Paket mit einem Attribut übermitteln, das

sich von dem unterbrochenen Paket unterscheidet. Im Besonderen bestimmt

der aktuelle Eigentümer

in dem Schritt 712, ob er ein Paket mit einem Attributtyp

aufweist, das sich von allen anderen Paketen unterscheidet, die

in der aktuellen Arbitrierungssitzung wiederholt worden sind (d.h.

dem Zeitraum der Verweildauer des aktuellen Eigentümers), das übermittelt

werden soll.

-

Wenn

der aktuelle Eigentümer

ei Paket mit einem anderen Attribut aufweist, kann der aktuelle

Eigentümer

in dem Schritt 714 versuchen, das Paket zu übermitteln.

Ansonsten gibt der aktuelle Eigentümer die Kontrolle über die

Schnittstelle frei.

-

PHYSIKALISCHE SCHNITTSTELLE

-

In

einem Ausführungsbeispiel

implementiert die Hub-Link-Schnittstelle eine physikalische Schnittstelle,

die mit einer Grundfrequenz von 66 MHz oder 100 MHz arbeitet. Andere

Frequenzen können

ebenfalls verwendet werden. Darüber

hinaus verwendet die physikalische Schnittstelle in einem Ausführungsbeispiel

eine quellensynchrone (SS) Datenübertragungstechnik,

die Vierfachtaktung aufweisen kann, um Daten mit dem vierfachen

Takt des Basis-Hub-Link-Takts zu übertragen. In einem Ausführungsbeispiel

mit einer 8-Bit-Datenschnittstelle (z.B. PD), die mit einer Basisfrequenz

von 66 MHz oder 100 MHz arbeitet, kann somit entsprechend eine Bandbreite

von 266 Megabyte pro Sekunde (MB/Sek.) oder 400 MB/Sek. erreicht

werden.

-

In

einem Ausführungsbeispiel

unterstützt

die Hub-Link-Schnittstelle ferner einen Spannungsbetrieb von 1,8

V und basiert auf einem Signalisierungsverfahren der CMOS-Technik (Komplementär-Metalloxid-Halbleiter).

In alternativen Ausführungsbeispielen

kann die Schnittstelle aber auch auf alternativen Frequenzen und/oder

Datenschnittstellen anderer Größen arbeiten

bzw. betrieben werden, so dass unterschiedliche Bandbreiten bereitgestellt

und alternative Betriebsspannungen unterstützt werden, auf der Basis einer

alternativen Signalverarbeitung, ohne dabei vom Umfang der Erfindung

abzuweichen.

-

Externe Signaldefinition

-

Die

Abbildung aus 8 veranschaulicht eine physikalische

Signalschnittstelle des Hub-Links

zwischen zwei Hub-Agenten gemäß einem

Ausführungsbeispiel.

Wie dies in der Abbildung aus 8 dargestellt ist,

verwendet die physikalische Schnittstelle des Hub-Link einen bidirektionalen

8-Bit-Datenbus (PD[7:0]) mit einem sich unterscheidenden Paar von

quellensynchronen Strobe-Signalen (PSTRBN, PSTRBP) für die Datentaktung.

In einem alternativen Ausführungsbeispiel

kann die Schnittstelle breiter gestaltet werden. Wie dies in der

Abbildung aus 8 dargestellt ist, kann zum

Beispiel ein zusätzlicher

8-Bit-Datenbus (PD[15:8]) ebenfalls in Verbindung mit einem zusätzlichen

Paar von quellensynchronen Strobe-Signalen (PUSTRBN, PUSTRBP) eingesetzt

werden. Ferner können

in einem alternativen Ausführungsbeispiel

unidirektionale Signale verwendet werden.

-

Darüber hinaus

verbindet ein unidirektionales Arbitrierungssignal jeden Agenten

mit dem anderen (RQa, RQb), und ein bidirektionales Signal STOP

wird von dem empfangenden Agenten eingesetzt, um den Datenfluss

zu steuern, wie dies vorstehend im Text beschrieben worden ist.

Zu weiteren Schnittstellensignalen zählen Systemrückstellung

(Reset), gemeinsamer Takt (HLCLK) und Spannungsreferenzsignale (HLVREF). Ebenfalls

enthalten sind ferner Signale für

jeden Hub-Agenten (ZCOMP) zur Anpassung dessen Treiberausgangsimpedanz

an den entsprechenden Wert, um Fertigungs- und Temperaturschwankungen

zu kompensieren.

-

Die

physikalischen Signale, die in der Schnittstelle aus

89 dargestellt sind, werden im Anschluss in

Tabelle 8 näher

beschrieben. In alternativen Ausführungsbeispielen des Hub-Link können die

in der physikalischen Schnittstelle enthaltenen Signale variieren,

ohne dabei vom Umfang der vorliegenden Erfindung abzuweichen. Zum

Beispiel kann die physikalische Schnittstelle mehr, weniger oder

andere Signale als die Signale aus der Abbildung aus

8,

die im Anschluss in Tabelle 8 beschrieben sind aufweisen. Tabelle 8: Hub-Link-Schnittstellensignale

für 8-Bit-Agenten

| Name | Bits

(Anschluss -flächen) | Typ | Taktmodus | Beschreibung |

| PD[7:0] | 8 | ASTS1 | SS2 | Paketdatenstifte.

Die Datenschnittstelle wird in einem Ausführungsbeispiel, wenn sie sich

im Wartezustand befindet, durch aktive Erhaltungseinrichtungen mindestens

auf dem Spannungswert gehalten, auf den Sie gesteuert worden ist. |

| PSTRBP | 1 | ASTS | SS | Der

negative PD-Schnittstellen-Strobe (Standardspannungswert = VSSHL)

und der positive PD-Schnittstellen-Strobe (Spannungswert im Ruhezustand

= VCCHL) stellen gemeinsam eine Taktung für die 4X und 1X Datenübertragung

an der PD[7:0] Schnittstelle bereit. Der Agent, der Daten bereitstellt,

steuert das Signal PSTRBN und PSTRBP sollten vollständig unterschiedlich an

dem Empfänger

gemessen werden. |

| PSTRBN | 1 | ASTS | SS | Positiver

PD-Schnittstellen-Strobe, siehe Beschreibung von PSTRBP oben. |

| RQa | 1 | E/A | CC3 | Aktiv

hohe Anforderung von Agenten A (Ausgabe von A, Eingabe in B) zum

Erhalt der Kontrolle über

die Hub-Link-Schnittstelle. RQa

wird aktiviert, wenn dem Agenten A Daten zum Senden zur Verfügung stehen,

und RQa wird deaktiviert, wenn entweder alle Daten des Agenten A

gesendet worden sind oder der Agent A bestimmt, dass er die Schnittstelle freigeben

sollte. Der Rückstellspannungswert

entspricht VSSHL. |

| RQb | 1 | E/A | CC | Anforderung

von Agent 13 (Ausgabe von B, Eingabe in A). Siehe Beschreibung oben

von RQa. |

| STOP | 1 | ASTS | CC | Eingesetzt

für die

Pipeline-Verarbeitung der Flusssteuerung zum Wiederholen oder Trennen

von Paketen. |

| HLCLK | 1 | 1 | - | Hub-Link-Basistakt,

in einem Ausführungsbeispiel

entweder 66 MHz oder 100 MHz. Dies stellt Taktinformationen für die gemeinsamen

Taktsignale bereit (nachstehend im Text näher beschrieben). |

| RESET# | 1 | 1 | CC | Aktiv

niedrige Rückstellanzeige an

Hub-Link-Agenten4. |

| HLVREF | 1 | 1 | - | Spannungsreferenz

(VCCHL/2) für

unterschiedliche Eingaben. In einem Ausführungsbeispiel wird die Spannung

auf der Hauptplatine durch einen Spannungsteiler erzeugt. |

| HLZCOMP | 1 | E/A | - | Stellt

die Impedanzkompensation bereit. |

| VCCHL | 4 | Leist. | - | 1,8

V |

| VSSHL | 4 | Erd. | - | |

| Insgesamt: | 25 | | | |

- 1ASTS

= Aktiv erhaltener Dreizustand

- 2SS = Quellensynchrones Modussignal

- 3CC = Gemeinamer Taktmodussignal

- 4In einem Ausführungsbeispiel handelt es sich

bei Reset um ein systemweites Signal; es ist eine Ausgabe einer Komponente

des Systems und eine Eingabe in die andere(n) Komponente(n). Ferner

ist Reset asynchron in Bezug auf HLCLK.

-

Betrieb im Übertragungsmodus

gemeinsamer Takt

-

In

einem Ausführungsbeispiel

werden zahlreiche der über

die Hub-Link-Schnittstelle übertragenen

Signale gemäß einem

gemeinsamen Taktmodus übertragen.

Im Besonderen steht die Taktung der Signale, die über den

gemeinsamen Taktmodus übertragen

werden, im Verhältnis

zu einem einzelnen Takt (z.B. dem Hub Link-Takt). In alternativen

Ausführungsbeispielen

können

die Signale mit einem Systemtakt gekoppelt werden, der außerhalb

der Hub-Link-Agenten liegt. Ferner können mehr als ein Hub-Link-Segment

vorhanden sein, wobei in diesem Fall unterschiedliche Basistakte

für die

verschiedenen Segmente eingesetzt werden können. Zum Beispiel kann eine

Komponente sowohl eine 66 MHz Basis-Hub-Link-Schnittstelle als auch

eine 100 MHz Basis-Hub-Link-Schnittstelle implementieren.

-

Betrieb im quellensynchronen Übertragungsmodus

-

In

einem Ausführungsbeispiel

werden die Pakete/Daten unter Verwendung eines quellensynchronen Taktmodus übermittelt,

der eine Technik zur Multiplikation der Datenübertragungsrate bereitstellt.

In einem Ausführungsbeispiel

unter Verwendung eines 4x quellensynchronen Taktmodus mit einem

8-Bit-Datensignalpfad, erfordert die Übermittlung eines Doppelwortes

(d.h. vier Byte) nur einen Hub-Link-Taktzyklus (HLCK). Alternativ

würde die Übermittlung

eines Doppelwortes unter Verwendung eines 1X quellensynchronen Taktmodus

auf einem 8-Bit-Datensignalpfad einen vollständigen Hub-Link-Taktzyklus

für die

vollständige

Ausführung erfordern.

-

Im

Besonderen werden in einem Ausführungsbeispiel

der quellensynchronen Übermittlung

Strobes (z.B. PSTRBN/PSTRBP) mit einer Datenübermittlung gemäß einem

vorbestimmten Taktverhältnis

zwischen den Strobes und den Daten gesendet. Die Strobes werden

danach von dem empfangenden Hub-Agenten zur Verriegelung der Daten

in dem empfangenden Hub-Agenten

verwendet.

-

Im

Besonderen werden in einem Ausführungsbeispiel

die Flanken der Strobes PSTRBP/S'PSTRBN von

dem empfangenden Hub-Agenten eingesetzt, um die Gegenwart und Taktung

der über

die Datensignalpfade übertragenen

Daten zu identifizieren. Wie dies zum Beispiel in dem Taktdiagramm

aus 9 veranschaulicht ist, entspricht in einem Ausführungsbeispiel

eine erste Datenübertragung

der Anstiegsflanke von PSTRBP und der abfallenden Flanke von PSTRBN.

Eine zweite Datenübertragung

entspricht der Anstiegsflanke von PSTRBN und der abfallenden Flanke

von PSTRBP.

-

In

einem weiteren Ausführungsbeispiel,

das in der Abbildung aus 9 dargestellt ist, sind die

Sendeflanken der Strobes PSTRBP/PRSTRBN ferner nahe der Mitte des

Fensters gültiger

Daten positioniert. Folglich wird für den empfangenden Agenten

ein Eingangsdaten-Abtastfenster

vorgesehen, um verschiedene Laufzeitunterschiede der Systemtaktung

zu berücksichtigen.

In einem Ausführungsbeispiel

werden ferner eine Flanke für

mindestens gültige

Daten vor dem Strobe (tDvb) und eine Flanke für mindestens gültige Daten

nach dem Strobe (tDva) ebenfalls von dem empfangenden Hub-Agenten

verwendet, um die übermittelten

Daten zu identifizieren und zu verriegeln bzw. zwischenzuspeichern.

Nachdem der empfangende Hub-Agent die eingehenden Daten verriegelt

hat, werden die Daten einen kurzen Zeitraum lang gehalten, um die

Daten neu mit dem Hub-Link-Takt (HLCK) zu synchronisieren, bevor

sie weiter in dem Hub-Agenten geleitet werden.

-

In

der vorstehenden Patentschrift wurde die vorliegende Erfindung in

Bezug auf bestimmte exemplarische Ausführungsbeispiele der Erfindung

beschrieben. Es ist jedoch ersichtlich, dass verschiedene Modifikationen

und Änderungen

diesbezüglich

vorgenommen werden können,

ohne dabei vom Umfang der Erfindung abzuweichen. Zum Beispiel kann

die Hub-Link-Schnittstelle

gemäß einem

Ausführungsbeispiel

in einem Computersystem mit mehreren Prozessoren implementiert werden,

wie dies in der Abbildung aus 10 veranschaulicht

ist. Die Beschreibung und die Zeichnungen dienen somit Zwecken der

Veranschaulichung und haben keine einschränkende Funktion.