-

GEBIET DER ERFINDUNG

-

Die

vorliegende Erfindung betrifft eine Technologie zum Aufzeichnen

digitaler Signale in mehreren Spuren durch Teilen einer Spur beim

Aufzeichnen in mehrere Blöcke,

Extrahieren wenigstens eines Blockes aus einer Spur und Wiedergeben

der Daten von einem Aufzeichnungsmedium, in dem Daten, die Fehlerkorrekturcode-Codieren

durch Interleaven von Signalen in mehreren Blöcken aus der Vielzahl von Spuren

durchlaufen, aufgezeichnet sind, und im Besonderen dieses Wiedergabeverfahren,

eine Wiedergabevorrichtung unter Verwendung dieses Verfahrens, eine

Aufzeichnungs- und Wiedergabevorrichtung kombiniert mit einer Aufzeichnungsvorrichtung

und ein Aufzeichnungsmedium, in dem dasselbe Verfahren darin aufgezeichnet

ist.

-

HINTERGRUND DER ERFINDUNG

-

Bei

der bisher vorgeschlagenen Wiedergabevorrichtung oder Aufzeichnungs-

und Wiedergabevorrichtung wird, wenn Korrektur bei dem Decodierprozess

von Fehlerkorrekturcode gesperrt ist, eine sogenannte Fehlerverbergung

zum Interpolieren von dem umgebenden Signal ausgeführt und

ausgegeben.

-

Jedoch

erfordert in dem Fall von Aufzeichnung und Wiedergabe durch Empfangen

eines Videosignals, das durch Informationsquellencodieren aus Bildframes

verarbeitet wird, wenn Korrektur bei Fehlerkorrekturcode gesperrt

ist, die sogenannte Fehlerverbergung durch Interpolieren von dem

umgebenden Signal wenigstens einen Teil von Informationsquellen-Codiervorrichtung

und -Decodiervorrichtung und daher ist der Schaltungsumfang sehr

groß und

dies ist nicht realistisch.

-

Im

Gegensatz dazu erscheint, wenn diese Fehlerverbergung nicht ausreichend

ist, Rauschen auf Grund eines in mehreren Stufen auftretenden Fehlers

auf dem Bildschirm, eine signifikante Bildverschlechterung tritt

auf und ein sehr unangenehmer Bildschirm wird wiedergegeben.

-

EP-A-0267029 offenbarte

eine Vorrichtung zum Aufzeichnen und/oder Wiedergeben digitaler

Daten, wobei die Daten mit Fehlerkorrekturcodes, die äußere Codes

und innere Codes enthalten, so codiert werden, dass jeweilige vorgegebene

Anzahlen von Symbolen oder Wörtern

jeweilige Blöcke,

zu denen Synchronisationsdaten hinzugefügt werden, bilden und dann

auf schräge

Spuren eines Bandmediums aufgezeichnet werden. Die redundanten Wörter des äußeren Fehlerkorrekturcodes

werden auf jeder Spur an dem Anfangsabschnitt des Videosektors aufgezeichnet.

-

EP-A-0481752 offenbart

einen Fehlerkorrekturcode-Codierer und -Decoder. Eine erste Codiereinrichtung

erzeugt einen ersten Fehlerkorrekturcode, der ein erster Paritätscode ist,

der zu einer ersten Codegruppe hinzugefügt wird, die eine vorgegebene

Anzahl aufeinanderfolgender Informationscodes einer Codesequenz aufweist.

Eine zweite Codiereinrichtung wird zum Erzeugen eines zweiten Fehlerkorrekturcodes

bereitgestellt, der ein zweiter Paritätscode ist, der zu einer zweiten

Codegruppe hinzugefügt

wird, die Informationscodes aufweist, die jeweils von einer ersten

Gruppe aus einer Vielzahl aufeinanderfolgender Codegruppen der Codesequenz

abgeleitet sind.

-

EP-A-0596826 offenbart

ein Verfahren und eine Vorrichtung zum Interleaven/De-Interleaven

für eine digitale

Videokassettenaufzeichnungsvorrichtung. Ein Interleaving/De-Interleaving-Bereich

wird gemäß einer vorgegebenen

Hochgeschwindigkeit bestimmt und Interleaving/De-Interleaving wird

darin durchgeführt.

-

US-A-4277807 beschreibt

ein Verfahren zum Aufzeichnen digitaler Videosignale und umfasst

das Anordnen der Wörter

auf einem Aufzeichnungsmedium unter Verwendung einer Vielzahl von

Spuren. Außerdem wird

eine Vorrichtung zum Durchführen

des Verfahrens offenbart.

-

ZUSAMMENFASSUNG DER ERFINDUNG

-

Es

ist folglich eine Aufgabe der Erfindung, eine Wiedergabevorrichtung,

die einen sehr kleinen Schaltungsumfang erfordert und frei ist von

merklicher Bildqualitätsverschlechterung,

die auf kontinuierliches Auftreten von Rauschen durch Fehler auf

dem Bildschirm zurückzuführen ist,

wenn Fehlerkorrektur während

der Wiedergabe gesperrt wird, und eine Aufzeichnungs- und Wiedergabevorrichtung,

die selbige verwendet, vorzulegen.

-

Die

vorliegende Erfindung stellt eine Wiedergabevorrichtung zur Wiedergabe

von auf einem Aufzeichnungsmedium gespeicherten Daten bereit, wobei

das Aufzeichnungsmedium eine Vielzahl von Spuren hat, die jede eine

Vielzahl von Blöcken

aufweisen, jeder mit einer Vielzahl von Synchronisationsblöcken, worin

die Daten aus der Vielzahl von Spuren interleaved sind und entsprechend

einem ersten Fehlerkorrekturcode, der einen entsprechenden vorgegebenen

Ganzwert t hat, der eine Funktion eines Mindestabstands d1 des Fehlercodes

ist, und entsprechend einem zweiten Fehlerkorrekturcode codiert

sind und wobei die Vorrichtung umfasst:

einen ersten Fehlerkorrekturcode-Decoder 10 zum

Decodieren des ersten Fehlerkorrekturcodes, Fehler in den Daten

korrigierend, und eine Anzahl von durch den ersten Fehlerkorrekturcode

korrigierten Fehlern, die jedem Synchronisationsblock entsprechen,

bereitstellend,

einen Speicher 12 zum De-Interleaving

der Daten,

einen zweiten Fehlerkorrekturcode-Decoder 13 zum

Decodieren des zweiten Fehlerkorrekturcodes und zum Ausgeben eines

Korrektur-Sperrsignals, das einem Synchronisationsblock der Daten

entspricht, wenn der zweite Fehlerkorrekturcode-Decoder einen Fehler

in den Daten in dem Synchronisationsblock nicht korrigiert hat,

dadurch

gekennzeichnet, dass die Vorrichtung des Weiteren umfasst:

einen

Speicherkontroller 11 zum Verhindern, dass der Speicher 12 den

Synchronisationsblock ausgibt, wenn das Korrektur-Sperrsignal, das

dem Synchronisationsblock entspricht, ausgegeben wird und wenn die

Anzahl von korrigierten Fehlern, die dem Synchronisationsblock entsprechen,

größer als

die vorgegebene Ganzzahl t ist, wobei t nicht d1/2 übersteigt.

-

Es

kann des Weiteren eine Aufzeichnungs- und Wiedergabevorrichtung

bereitgestellt werden, die die Aufzeichnungsvorrichtung der vorliegenden

Erfindung nutzt und des Weiteren eine Interleaving-Vorrichtung zum

Bereitstellen von interleaved Daten, einen Aufzeichnungsdaten-Konverter

zum Konvertieren der interleaved Daten in ein Signal, das zum Aufzeichnen

auf dem Aufzeichnungsmedium geeignet ist, umfasst.

-

Bei

dieser Struktur wird durch die Schaltung eines sehr kleinen Umfangs,

um zu steuern, dass kein Signal ausgegeben wird, das nicht korrigiert

werden kann, Rauschen bei der Wiedergabe so verringert, dass Verbesserung

von Bildqualität

verwirklicht werden kann.

-

KURZE BESCHREIBUNG DER ZEICHNUNGEN

-

1 ist

ein Blockdiagramm, das eine Struktur einer Aufzeichnungs- und Wiedergabevorrichtung nach

Ausführung

1 der Erfindung zeigt.

-

2 ist

ein Blockdiagramm, das eine Struktur einer Aufzeichnungs- und Wiedergabevorrichtung nach

Ausführung

2 der Erfindung zeigt.

-

3 ist

ein Blockdiagramm, das eine Struktur einer Wiedergabeeinheit einer

Aufzeichnungs- und Wiedergabevorrichtung nach Ausführung 3

der Erfindung zeigt.

-

4 ist

ein Blockdiagramm, das eine Struktur einer Wiedergabeeinheit einer

Aufzeichnungs- und Wiedergabevorrichtung nach Ausführung 4

der Erfindung zeigt.

-

5 ist

ein Blockdiagramm, das eine Struktur einer Wiedergabeeinheit einer

Aufzeichnungs- und Wiedergabevorrichtung nach der modifizierten

Ausführung

4 der Erfindung zeigt.

-

6 ist

ein Diagramm, das einen Speicherplatz bei einer Ausführung der

Erfindung zeigt.

-

7 ist

ein Diagramm, das ein Datenanordnungsbeispiel bei einer Ausführung der

Erfindung zeigt.

-

8 ist

ein Diagramm, das ein Beispiel für

dreidimensionales Shuffling eines Interleaving-Musters bei einer

Ausführung

der Erfindung zeigt.

-

9 ist

ein Diagramm, das ein Beispiel für

zweidimensionales Shuffling eines Interleaving-Musters bei einer

Ausführung

der Erfindung zeigt.

-

BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGEN

-

Es

wird nun Bezug auf die Zeichnungen genommen, wobei im Folgenden

bevorzugte Ausführungen der

Wiedergabevorrichtung und der Aufzeichnungs- und Wiedergabevorrichtung

ausführlich

beschrieben werden.

-

[Ausführung

1]

-

Zuerst

wird eine Aufzeichnungs- und Wiedergabevorrichtung nach Ausführung 1

der Erfindung erklärt. 1 ist

ein Blockdiagramm, das eine Struktur einer Aufzeichnungs- und Wiedergabevorrichtung

nach Ausführung

1 der Erfindung zeigt. 6 ist ein Diagramm eines Speicherplatzes. 7 ist

ein Beispiel für

einen Speicherbereich einer Fehlerkennzeichnung und 8 und 9 zeigen

Beispiele für

Interleaving.

-

In 1 ist

das Bezugszeichen 1 ein Speicherkontroller, 2 ist

ein Speicher, 3 ist ein zweiter Fehlerkorrekturcode-Codierer, 4 ist

ein erster Fehlerkorrekturcode-Codierer, 5 ist ein Aufzeichnungsdaten-Konverter, 6 ist

ein Aufzeichnungskopf, 7 ist ein Aufzeichnungsmedium, 8 ist

ein Wiedergabekopf, 9 ist ein Wiedergabedaten-Konverter, 10 ist

ein erster Fehlerkorrekturcode-Decoder, 11 ist ein Speicherkontroller, 12 ist

ein Speicher und 13 ist ein zweiter Fehlerkorrekturcode-Decoder.

-

Zur

Erleichterung des Verständnisses

dieser Ausführung

1 sei das Eingangssignal ein digitales Signal von MPEG2. Sie soll

außerdem

Daten durch Spiralabtastungstechnik in mehreren Spuren in einem

Magnetband aufzeichnen. Zuerst wird der Aufzeichnungsvorgang beschrieben.

-

Ein

Signal wird von einem Satelliten oder Ähnlichem gesendet und das Sendeformat

wird in einer Set-Top-Box oder Ähnlichem

decodiert und wird ausgegeben. Das Signal wird nach Verarbeitung

der Paketinformationen des Ausgangssignals von der Set-Top-Box in den Speicher 2 zugeführt.

-

Ein

Beispiel für

einen Speicherplatz des Speichers 2 wird in 6 gezeigt.

Hierin wird, da die Zuteilung des Speicherbereichs kein wichtiger

Punkt ist, als einfachster Fall angenommen, dass ein Bereich der

dreifachen Größe des Interleaving-Bereichs

des zweiten Fehlerkorrekturcodes besteht. Bei dem Speicherplatz

soll das untere Drittel des Bereichs ein Operationsbereich des zweiten

Fehlerkorrekturcodes sein, das mittlere Drittel des Bereichs soll

ein Eingangsbereich sein und das obere Drittel des Bereichs soll

ein Ausgangsbereich sein. Die Eingangsdaten in dem Speicher 2 werden

in dem Eingangsbereich des Speicherplatzes in 6 gespeichert.

-

Nach

einer spezifischen Regel werden die Daten von dem Speicher 2 in

den zweiten Fehlerkorrekturcode-Codierer 3 ausgesendet.

-

Zu

diesem Zeitpunkt werden die Daten mit einer bestimmten Regel interleaved.

Zum Beispiel werden Interleaving-Muster in 8 und 9 gezeigt.

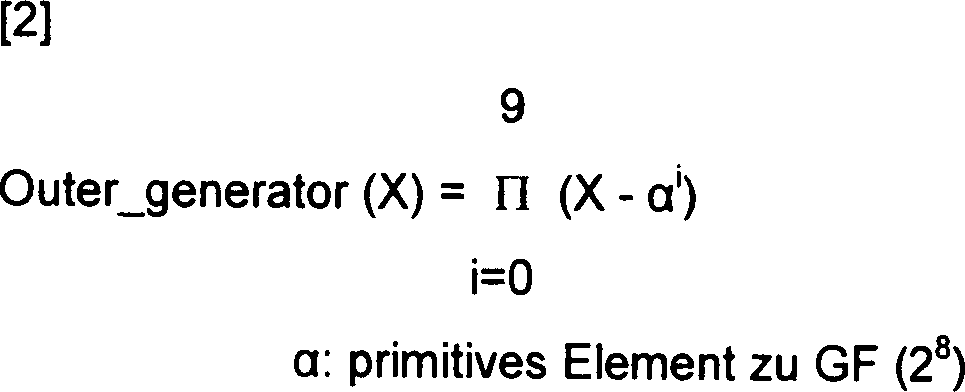

Das Interleaving-Format zu diesem Zeitpunkt wird in Polynom 1 gezeigt.

-

-

-

In

dem Polynom 1 bezeichnen t, s, d drei Richtungen der dreidimensionalen

Konfiguration der Daten, die so aufzuzeichnen sind, wie in 8 gezeigt,

und im Besonderen zeigt t die Spurrichtung an, in der aufzuzeichnen

ist, s ist die Synchronisationsblockrichtung und d ist die Richtung

der Anzahl von Bytes. Nebenbei bedeutet „O mod6" der „Rest, wenn O durch 6 geteilt

wird".

-

Mit

Bezugnahme auf 8 und 9 wird das

Interleaving-Muster im Folgenden kurz beschrieben. In 8 sind

die aufzuzeichnenden Daten dreidimensional angeordnet. Die sogenannte

X-Achsen-Richtung wird als die Byte-Richtung bezeichnet, die Z-Achsen-Richtung ist

die Synchronisationsblockrichtung und die Y-Achsen-Richtung ist

die Spurrichtung. Die Datenflusssequenz ist von der Byte-Richtung

zu der Synchronisationsblockrichtung und zu der Spurrichtung.

-

Unter

Extrahierung von Daten gemäß Polynom

1 wird ein zweiter Fehlerkorrekturcode erzeugt. Wie von dem Polynom

1 bekannt ist, ist die Anzahl von Spuren mit Interleaving-Beziehung 6, wobei

die benachbarten Daten in einem Codewort um jeweils 1 bei der Spurzahl

abnehmen (auf 0 folgt jedoch 5), die Synchronisationsblockzahl um

jeweils 3 zunimmt und die Byte-Zahl konstant ist. Da die Byte-Zahl

konstant ist, ist es folglich unter Weglassung der Byte-Richtung 9,

die den zweidimensionalen Interleave zeigt.

-

In 9 zeigt

dieselbe Markierung dasselbe Codewort an. Da der zweidimensionale

Interleave unter Ausschluss der Byte-Richtung auch bei der nächsten Byte-Zahl

derselbe ist, ist ein Satz zweidimensionaler Interleaves, die sich

lediglich in der Byte-Zahl unterscheiden, ein Block zweiten Fehlerkorrekturcodes.

Wie aus dem Umstand bekannt ist, dass es 18 Codewörter in

der Synchronisationsblockrichtung s in 9 gibt,

gibt es zu diesem Zeitpunkt 18 zweite Fehlerkorrekturcodeblöcke in sechs

Spuren.

-

Auf

diese Weise werden die aus dem Speicher 2 extrahierten

Daten zu dem zweiten Fehlerkorrekturcode-Codierer 3 gesendet

und die Paritätsdaten

werden zum Erzeugen des Codeworts für die bei der Technologie der

Fehlerkorrekturcode-Codierung sogenannte Mindestdistanz (hierin

d2) berechnet. Die Paritätsdatenberechnung

wird zum Beispiel gemäß Polynom

2 durchgeführt.

-

-

Bei

dem Polynom 2 bedeutet das Operationssymbol Π die Operation zum Multiplizieren

aller Elemente. Nebenbei ist GF die Galois-Form in der Fehlerkorrekturcode-Codierungstechnologie

und das primitive Element zeigt das Element an.

-

In

Polynom 2 ist d2 = 11. Die berechneten Paritätsdaten werden gemäß Polynom

1, das dasselbe Relationspolynom wie oben ist, in den Speicher 2 geschrieben.

Wenn 18 zweite Fehlerkorrekturcodeblöcke abgeschlossen sind, werden

sie über

den Speicher 2 in den ersten Fehlerkorrekturcode-Codierer 4 ausgegeben. Die

Steuerung von Daten, die in diesen Speicher 2 eingegeben

und von diesem ausgegeben werden, wird durch den Speicherkontroller 1 durchgeführt.

-

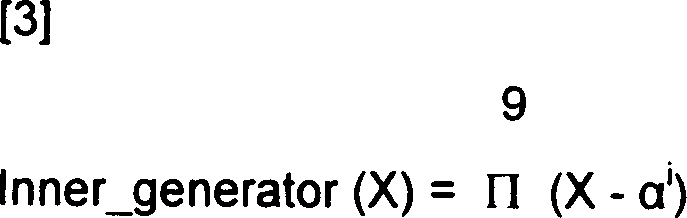

In

dem ersten Fehlerkorrekturcode-Codierer 4 werden Paritätsdaten

zum Erzeugen des Codeworts für die

bei der Technologie der Fehlerkorrekturcode-Codierung sogenannte

Mindestdistanz d1 berechnet. Zum Beispiel werden die Paritätsdaten

in dem Polynom 3 berechnet und zusammen mit Eingangsdaten in den

Aufzeichnungsdaten-Konverter 5 ausgesendet. In Polynom

3 ist d1 = 9. In dem Aufzeichnungsdaten-Konverter 5 wird

das Eingangssignal zu einem Signal, das zum Aufzeichnen geeignet

ist, konvertiert und wird in den Aufzeichnungskopf 6 ausgesendet.

-

-

-

Zum

Beispiel wird unter Hinzufügen

eines Synchronisationsbits und eines Identifikationsbits zu der

Codeworteinheit des ersten Fehlerkorrekturcodes ein Synchronisationsblock

erzeugt und dieser wird mit M-Längen-Code

verwürfelt,

Vorcode der Partial-Response-Klasse 4 wird

verarbeitet, Aufzeichnung wird entzerrt, um optimales Aufzeichnen

zu erreichen, so dass die Fehlerrate beim Wiedergeben am kleinsten

sein kann, und das Signal wird in den Aufzeichnungskopf 6 gesendet.

Das Signal wird dann durch den Aufzeichnungskopf 6 in dem

Aufzeichnungsmedium 7 aufgezeichnet. Als das Aufzeichnungsmedium 7 wird

ein Magnetband angenommen, aber selbstverständlich können eine Magnetplatte, eine

optische Platte oder andere Medien verwendet werden.

-

Im

Folgenden wird der Wiedergabevorgang beschrieben.

-

Der

Wiedergabekopf 8 nimmt ein Signal von dem Aufzeichnungsmedium 7 ab.

Zu diesem Zeitpunkt kann der Wiedergabekopf 8 derselbe

wie der Aufzeichnungskopf 6 oder ein unterschiedlicher

sein. Das von dem Wiedergabekopf 8 abgenommene Signal wird

in dem Wiedergabedaten-Konverter 9 korrekt verarbeitet und

wird in den ersten Fehlerkorrekturcode-Decoder 10 ausgegeben.

Hierin ist korrekte Verarbeitung durch den Wiedergabedaten-Konverter 9 zum

Beispiel Konvertieren eines Wiedergabesignals zu einem digitalen Mehrwertsignal

in jedem Takt, Decodieren zu einem binären digitalen Signal unter

Verwendung eines Viterbi-Decoders, Entwürfeln unter Verwendung des

M-Längen-Signals,

Erfassen eines Synchronisationsbits zum Bestimmen eines Synchronisationsblocks

und Decodieren eines Identifikationsbits und die Daten des erzielten Ergebnisses

werden in den ersten Fehlerkorrekturcode-Decoder 10 ausgegeben.

-

In

dem ersten Fehlerkorrekturcode-Decoder 10 wird der erste

Fehlerkorrekturcode gemäß dem Decodierverfahren

decodiert, das zum Beispiel in der Veröffentlichung „Coding

Theory" (Hideki

Imai, Society of Electronic Information and Communication) offengelegt

wird, und die Daten werden an den Speicher 12 ausgegeben.

Wenn das Korrigieren in dem ersten Fehlerkorrekturcode-Decoder 10 fehlschlägt, wird

ein erstes Fehlerkennzeichen an den Speicher 12 ausgegeben.

Hierin kann der Speicher 12 derselbe wie der Speicher 2 oder

ein unterschiedlicher sein.

-

Die

Daten von dem Speicher 12 werden gemäß dem Polynom 1, das das Interleaving-Polynom ist, an den

zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben und das

erste Fehlerkennzeichen, das Einzeldaten entspricht, wird an den

zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben. In dem

zweiten Fehlerkorrekturcode-Decoder 13 wird unter Verwendung

des ersten Fehlerkennzeichens der zweite Fehlerkorrekturcode gemäß dem Decodierverfahren,

das in der Veröffentlichung „Coding

Theory" offengelegt

wird, decodiert und die decodierten Daten werden in den Speicher 12 eingegeben.

Zu diesem Zeitpunkt wird in dem zweiten Fehlerkorrekturcode-Decoder 13,

wenn ein Codewort, das nicht korrigiert werden kann, auftritt, ein

zweites Fehlerkennzeichen an den Speicherkontroller 11 ausgegeben.

Dieses zweite Fehlerkennzeichen entspricht dem Korrektur-Sperrsignal,

das die Informationen sendet, die nicht fehlerkorrigiert werden

konnten.

-

Der

Speicherkontroller 11 steuert den Eingabe- und Ausgabevorgang

von Daten in dem Speicher 12 und bei Empfangen eines zweiten

Fehlerkennzeichens von dem zweiten Fehlerkorrekturcode-Decoder 13 steuert

er so, dass keine Daten für

den Abschnitt von sechs Spuren mit Interleaving-Beziehung durch

den Sechsspurimpuls von dem Wiedergabedaten-Konverter 9 ausgegeben

werden. Auf diese Weise werden lediglich die Daten der Spur, die

kein zweites Fehlerkennzeichen in dem zweiten Fehlerkorrekturcode-Decoder 13 ausgibt,

von dem Speicher 12 ausgegeben.

-

Somit

wird lediglich das Signal, das sicher fehlerkorrigiert ist, wiedergegeben

und es wird, auch wenn eine Möglichkeit

besteht, dass es auf Grund von Mangel an Wiedergabesignalen vorübergehend

ein Standbild wird, wenigstens ein auf Grund eines Fehlers in großem Maße gestörtes Bild

nicht wiedergegeben und es kann ein stabiles Wiedergabebild leicht

verwirklicht werden.

-

Unterdessen

können

sie, da der Speicherkontroller 11 die Funktion des Speicherkontrollers 1 enthält, gemeinsam

genutzt werden. Außerdem

können

der Speicher 2 und der Speicher 12 gemeinsam genutzt

werden. Ein Beispiel für

den Speicherbereich des Fehlerkennzeichens und den Speicherbereich

anderer Daten wird in 7 gezeigt.

-

Gemäß der Ausführung werden

wiedergegebene Daten in dem Speicher gespeichert und Ausgangsdaten

werden nach Wiedergabe-Sperrsignal (Fehlerkennzeichen) ausge wählt und

ausgegeben, aber derselbe Effekt wird durch Datensteuerung ohne

Verwendung von Speicher erzielt.

-

Bei

einem modifizierten Beispiel für

Ausführung 1 kann,

wenn der Speicherkontroller 11 ein zweites Fehlerkennzeichen

von dem zweiten Fehlerkorrekturcode-Decoder 13 empfängt, der

Speicherkontroller 11 so steuern, dass nicht der Codeblock

des zweiten Fehlerkorrekturcodes, der mit dem zweiten Fehlerkennzeichen verbunden

ist, ausgegeben wird. Auch in diesem Fall werden dieselben Effekte

wie oben erzielt.

-

Die

Erfindung enthält

außerdem

als eine Ausführung

die Wiedergabevorrichtung nur zur Wiedergabe unter Ausschluss des

Aufzeichnungsvorrichtungsabschnitts (wobei der Abschnitt aus dem

Speicherkontroller 1, dem Speicher 2, dem zweiten

Fehlerkorrekturcode-Codierer 3, dem ersten Fehlerkorrekturcode-Codierer 4, dem

Aufzeichnungsdaten-Konverter 5 und

dem Aufzeichnungskopf 6 besteht) aus der so gebildeten

Aufzeichnungs- und Wiedergabevorrichtung.

-

[Ausführung

2]

-

Im

Folgenden wird eine Aufzeichnungs- und Wiedergabevorrichtung nach

Ausführung

2 der Erfindung beschrieben. 2 ist ein

Blockdiagramm, das die Struktur der Aufzeichnungs- und Wiedergabevorrichtung der

Ausführung

2 der Erfindung zeigt. Der Unterschied zwischen der Ausführung 2

und der Ausführung

1 liegt in der Ausgabe des Fehlerkennzeichens von dem ersten Fehlerkorrekturcode-Decoder 10 und

dem Betrieb des Speicherkontrollers 11, des Speichers 12 und

des zweiten Fehlerkorrekturcode-Decoders 13.

-

In 2 ist

das Bezugszeichen 1 ein Speicherkontroller, 2 ist

ein Speicher, 3 ist ein zweiter Fehlerkorrekturcode-Codierer, 4 ist

ein erster Fehlerkorrekturcode-Codierer, 5 ist ein Aufzeichnungsdaten-Konverter, 6 ist

ein Aufzeichnungskopf, 7 ist ein Aufzeichnungsmedium, 8 ist

ein Wiedergabekopf, 9 ist ein Wiedergabedaten-Konverter, 10 ist

ein erster Fehlerkorrekturcode-Decoder, 11 ist ein Speicherkontroller, 12 ist

ein Speicher und 13 ist ein zweiter Fehlerkorrekturcode-Decoder.

-

Der

Aufzeichnungsprozess und der Betrieb bis zu der Ausgabe von dem

Wiedergabedaten-Konverter 9 sind dieselben wie bei Ausführung 1

und werden hierin weggelassen, und im Folgenden wird lediglich der Betrieb

des ersten Fehlerkorrekturcode-Decoders 10, des Speicherkontrollers 11,

des Speichers 12 und des zweiten Fehlerkorrekturcode-Decoders 13 beschrieben.

-

In

dem ersten Fehlerkorrekturcode-Decoder 10 wird, wenn Korrektursperren

bei einem Codewort in dem ersten Fehlerkorrekturcode auftritt, ein

erstes Fehlerkennzeichen an den Speicher 12 ausgegeben.

Unter der Annahme, dass die höchste

Ganzzahl d1/2 nicht übersteigt,

wobei dies die Hälfte

des Mindestabstands d1 ist, wobei dies in der Fehlerkorrekturcode-Codierungstechnologie

t genannt wird, wird, wenn t Codewörter des Fehlerkorrekturcodes

in dem ersten Fehlerkorrekturcode-Decoder 10 korrigiert

werden, ein zweites Fehlerkennzeichen ausgegeben. Hierin ist, da

d1 = 9 ist, dann 9/2 = 4,5 und daher ist die höchste Ganzzahl t, die diesen

Wert nicht übersteigt,

t = 4. Das erste Fehlerkennzeichen und das zweite Fehlerkennzeichen

werden beide zusammen mit den Daten in dem Speicher 12 gespeichert.

Gemäß dem Polynom

1, das das Interleaving-Polynom

ist, werden Daten von dem Speicher 12 in den zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben.

-

Der

Betrieb des zweiten Fehlerkorrekturcode-Decoders 13 und

der Betrieb des Speicherkontrollers 11 bei erfolgreicher

Korrektur in dem zweiten Fehlerkorrekturcode-Decoder 13 sind dieselben wie

bei Ausführung 1

und die Erklärung

wird hierin weggelassen. Wenn jedoch der zweite Fehlerkorrekturcode-Decoder 13 den zweiten

Fehlerkorrekturcode decodiert, während

gleichzeitig das erste Fehlerkennzeichen verwendet wird, und die

decodierten Daten zum Ausgeben in den Speicher 12 verarbeitet,

wird ein Fehlerkennzeichen, das an den Speicherkontroller 11 auszugeben

ist, wenn ein Korrektur-Sperrcodewort in dem zweiten Fehlerkorrekturcode-Decoder 13 auftritt,

als drittes Fehlerkennzeichen bezeichnet. In diesem Fall entspricht

das Fehlerkorrektur-Sperrsignal

diesem dritten Fehlerkennzeichen.

-

Wenn

der Speicherkontroller 11 ein drittes Fehlerkennzeichen

von dem zweiten Fehlerkorrekturcode-Decoder 13 empfängt, steuert

der Speicherkontroller 11 so, dass nicht das Codewort des

ersten Fehlerkorrekturcodes, der das erste Fehlerkennzeichen und

das zweite Fehlerkennzeichen trägt

und das Codewort des ersten Fehlerkorrekturcodes in dem zweiten

Fehlerkorrekturcodeblock ist, der das Codewort des nicht korrigierten

zweiten Fehlerkorrekturcodes enthält, aus dem Speicher 12 ausgegeben

wird.

-

Daher

wird die Steuerung zum Verhindern der Ausgabe des Korrektur-Sperrsignals

soweit wie möglich in

einem sehr kleinen Schaltungsumfang verwirklicht und das auf dem

Bildschirm erscheinende Rauschen kann verringert werden, ausgeprägte Störung des

Wiedergabebildschirms kann verhindert werden und folglich kann die

Bildqualität

verbessert werden.

-

Die

Erfindung enthält

außerdem

als eine Ausführung

die Wiedergabevorrichtung nur zur Wiedergabe unter Ausschluss des

Aufzeichnungsvorrichtungsabschnitts (wobei der Abschnitt aus dem

Speicherkontroller 1, dem Speicher 2, dem zweiten

Fehlerkorrekturcode-Codierer 3, dem ersten Fehlerkorrekturcode-Codierer 4, dem

Aufzeichnungsdaten-Konverter 5 und

dem Aufzeichnungskopf 6 besteht) aus der so gebildeten

Aufzeichnungs- und Wiedergabevorrichtung.

-

[Ausführung

3]

-

Im

Folgenden wird eine Aufzeichnungs- und Wiedergabevorrichtung nach

Ausführung 3 der

Erfindung beschrieben. 3 ist ein Blockdiagramm, das

die Struktur des Wiedergabevorrichtungsabschnitts der Aufzeichnungs-

und Wiedergabevorrichtung von Ausführung 3 der Erfindung zeigt.

Der Unterschied zwischen Ausführung

3 und den Ausführungen

1 und 2 liegt in der Ausgabe des Fehlerkennzeichens von dem ersten Fehlerkorrekturcode-Decoder 10 und

dem Betrieb des Speicherkontrollers 11, des Speichers 12 und

des zweiten Fehlerkorrekturcode-Decoders 13.

-

In 3 ist

das Bezugszeichen 7 ein Aufzeichnungsmedium, 8 ist

ein Wiedergabekopf, 9 ist ein Wiedergabedaten-Konverter, 10 ist

ein erster Fehlerkorrekturcode-Decoder, 11 ist ein Speicherkontroller, 12 ist

ein Speicher und 13 ist ein zweiter Fehlerkorrekturcode-Decoder.

-

Der

Aufzeichnungsprozess und der Betrieb bis zu der Ausgabe von dem

Wiedergabedaten-Konverter 9 sind dieselben wie bei Ausführung 1

und werden hierin weggelassen, und im Folgenden wird lediglich der Betrieb

des ersten Fehlerkorrekturcode-Decoders 10, des Speicherkontrollers 11,

des Speichers 12 und des zweiten Fehlerkorrekturcode-Decoders 13 beschrieben.

-

Das

von dem Wiedergabedaten-Konverter 9 wiedergegebene Signal

wird in den ersten Fehlerkorrekturcode-Decoder 10 zugeführt. In

dem ersten Fehlerkorrekturcode-Decoder 10 wird der erste

Fehlerkorrekturcode decodiert. Das Decodierverfahren kann zu diesem

Zeitpunkt dasselbe sein, wie oben beschrieben. Außerdem kann

die Art des Hinzufügens

des ersten Fehlerkennzeichens bei Korrektursperrung dieselbe sein

wie oben. Außerdem

wird jedoch das erste Paritätssymbol

in den Speicher 12 geschrieben.

-

Die

Daten in dem Speicher 12 werden gemäß dem Polynom 1, das das Interleaving-Polynom ist, in den

zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben. Außerdem wird

das erste Fehlerkennzeichen in den zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben.

-

Der

Betrieb des zweiten Fehlerkorrekturcode-Decoders 13 ist

derselbe wie oben, aber außerdem

wird der zweite Fehlerkorrekturcode in dem Abschnitt des ersten

Paritätssymbols

decodiert. Bei Eintreten von Korrektursperrung wird ein zweites

Fehlerkennzeichen an den Speicher 12 ausgegeben.

-

Die

korrigierten Daten, die in den Speicher 12 zugeführt werden,

werden erneut in den ersten Fehlerkorrekturcode-Decoder 10 in

der Synchronisationsblockeinheit ausgegeben. Gleichzeitig wird ein

zweites Fehlerkennzeichen ausgegeben. In dem ersten Fehlerkorrekturcode-Decoder 10 wird

der erste Fehlerkorrekturcode durch das Decodierverfahren unter

Verwendung des zweiten Fehlerkennzeichens, zum Beispiel durch Löschkorrektur,

decodiert. Zu diesem Zeitpunkt wird erneut ein erstes Fehlerkennzeichen

in dem Synchronisationsblock eingestellt, der nicht korrigiert werden

kann. Das heißt,

dass das erste Fehlerkennzeichen, wenn es bereits eingestellt ist,

so gelassen wird, wie es ist, und wenn nicht, wird es eingestellt.

Im Gegensatz dazu wird bei erfolgreicher Korrektur das erste Fehlerkennzeichen

entfernt. Zusammen mit dem ersten Fehlerkennzeichen wird das Signal

in dem Speicher 12 gespeichert. Der Synchronisationsblock,

der nicht das erste Fehlerkennzeichen trägt, wird von dem Speicher 12 ausgegeben.

-

Eine

solche Ein- und Ausgabesteuerung des Speichers 12 wird

durch den Speicherkontroller 11 durchgeführt.

-

In

diesem Fall entspricht der erste Fehlerkorrekturcode-Decoder 10 „einem

dritten Fehlerkorrekturcode-Decoder zum weiteren Decodieren des

ersten Fehlerkorrekturcodes in dem Synchronisationsblock, von dem

der zweite Fehlerkorrekturcode decodiert wird, um in dem Fall von

Korrektursperrung nicht die Daten in Bezug auf Korrektursperrung

auszugeben". Das

heißt,

dass der erste Fehlerkorrekturcode-Decoder 10 den dritten

Fehlerkorrekturcode-Decoder mitnutzt, und in diesem Fall ist die

Arbeitsgeschwindigkeit des ersten Fehlerkorrekturcode-Decoders 10 im

Vergleich zu dem, der nicht mitnutzt, zwei Mal höher. Unterdessen kann der dritte

Fehlerkorrekturcode-Decoder von dem bei der Ausführung 4 beschriebenen Generator

des Syndroms des ersten Fehlerkorrekturcodes 14 verwirklicht

werden.

-

Bei

Ausführung

3 stellt der erste Fehlerkorrekturcode-Decoder 10, der

außerdem

als der dritte Fehlerkorrekturcode-Decoder dient, das erste Fehlerkennzeichen

erneut in dem Korrektursperr-Synchronisationsblock in dem zweiten

Vorgang zum Decodieren des ersten Fehlerkorrekturcodes ein. Das

heißt,

dass das erste Fehlerkennzeichen, wenn es bereits eingestellt ist,

so gelassen wird, wie es ist, und wenn nicht, wird es eingestellt.

Im Gegensatz dazu wird bei erfolgreicher Korrektur das erste Fehlerkennzeichen

entfernt. Zusammen mit dem ersten Fehlerkennzeichen werden die Daten

in dem Speicher 12 gespeichert. Der Synchronisationsblock,

der nicht das erste Fehlerkennzeichen trägt, wird von dem Speicher 12 ausgegeben

und daher werden sowohl die Funktion der Verarbeitung zur sicheren

Fehlerkorrektur als auch die Funktion des Verhinderns der Ausgabe

des Fehlerkorrektur-Sperrsignals bereitgestellt, so dass die Bildqualität weiter

verbessert werden kann.

-

Wenn

die Ein- und Ausgabezeitgebung nicht nur durch einen Speicher 12,

wie dem Speicher für

zweites Decodieren des ersten Fehlerkorrekturcodes, geregelt wird,

kann übrigens

selbstverständlich

außerdem ein

anderer Speicher als der Speicher 12 verwendet werden.

-

Bei

erneutem Einstellen des ersten Fehlerkennzeichens kann unterdessen

das erste Fehlersignal erneut eingestellt werden, wenn die Zahl

der Korrekturen t oder mehr be trägt

(wobei t eine Ganzzahl ist, die d1/2 nicht übersteigt). Bei d1 = 9 ist

dies zum Beispiel t = 4.

-

Die

Erfindung enthält

außerdem

als eine Ausführung

die Wiedergabevorrichtung nur zur Wiedergabe unter Ausschluss des

nicht gezeigten Aufzeichnungsvorrichtungsabschnitts aus der so gebildeten

Aufzeichnungs- und Wiedergabevorrichtung.

-

[Ausführung

4]

-

Im

Folgenden wird eine Aufzeichnungs- und Wiedergabevorrichtung nach

Ausführung

4 der Erfindung beschrieben. 4 ist ein

Blockdiagramm, das die Struktur des Wiedergabevorrichtungsabschnitts

der Aufzeichnungs- und Wiedergabevorrichtung von Ausführung 4

der Erfindung zeigt. Der Unterschied zwischen Ausführung 4

und den Ausführungen

1, 2 und 3 liegt in der Struktur eines Generators des Syndroms des

ersten Fehlerkorrekturcodes 14 als dritter Fehlerkorrekturcode-Decoder,

der Ausgabe des Fehlerkennzeichens von dem ersten Fehlerkorrekturcode-Decoder 10 und

dem Betrieb des Speicherkontrollers 11, des Speichers 12 und

des zweiten Fehlerkorrekturcode-Decoders 13.

-

In 4 ist

das Bezugszeichen 7 ein Aufzeichnungsmedium, 8 ist

ein Wiedergabekopf, 9 ist ein Wiedergabedaten-Konverter, 10 ist

ein erster Fehlerkorrekturcode-Decoder, 11 ist ein Speicherkontroller, 12 ist

ein Speicher, 13 ist ein zweiter Fehlerkorrekturcode-Decoder und 14 ist

ein Generator des Syndroms des ersten Fehlerkorrekturcodes.

-

Der

Aufzeichnungsprozess und der Betrieb bis zu der Ausgabe von dem

Wiedergabedaten-Konverter 9 sind dieselben wie bei Ausführung 1

und werden hierin weggelassen, und im Folgenden wird lediglich der Betrieb

des Speicherkontrollers 11 und des ersten Fehlerkorrekturcode-Decoders 10 beschrieben.

-

Das

von dem Wiedergabedaten-Konverter 9 wiedergegebene Signal

wird in den ersten Fehlerkorrekturcode-Decoder 10 zugeführt. In

dem ersten Fehlerkorrekturcode-Decoder 10 wird der erste

Fehlerkorrekturcode decodiert. Das Decodierverfahren kann zu diesem

Zeitpunkt dasselbe sein, wie oben beschrieben. Außerdem kann

die Art des Hinzufü gens

des ersten Fehlerkennzeichens bei Korrektursperrung dieselbe sein

wie oben. Außerdem

wird jedoch das erste Paritätssymbol

in den Speicher 12 geschrieben.

-

Die

Daten in dem Speicher 12 werden gemäß dem Polynom 1, das das Interleaving-Polynom ist, in den

zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben. Außerdem wird

das erste Fehlerkennzeichen in den zweiten Fehlerkorrekturcode-Decoder 13 ausgegeben.

-

Der

Betrieb des ersten Fehlerkorrekturcode-Decoders 13 ist

derselbe wie oben, aber außerdem

wird der zweite Fehlerkorrekturcode in dem Abschnitt des ersten

Paritätssymbols

decodiert. Bei Eintreten von Korrektursperrung wird ein zweites

Fehlerkennzeichen an den Speicher 12 ausgegeben.

-

Die

korrigierten Daten, die in den Speicher 12 zugeführt werden,

werden erneut in den Generator des Syndroms des ersten Fehlerkorrekturcodes 14 in

der Synchronisationsblockeinheit ausgegeben.

-

Eine

solche Ein- und Ausgabesteuerung des Speichers 12 wird

durch den Speicherkontroller 11 durchgeführt.

-

In

dem Generator des Syndroms des ersten Fehlerkorrekturcodes 14 wird

das Syndrom des ersten Fehlerkorrekturcodes berechnet und lediglich

der Synchronisationsblock, der als fehlerfrei beurteilt wird, wird ausgegeben,

während

der Synchronisationsblock, bei dem das Syndrom nicht vollständig 0 ist,

nicht ausgegeben wird.

-

Wenn

die Ein- und Ausgabezeitgebung nicht nur durch einen Speicher 12,

wie dem Speicher für

zweites Decodieren des ersten Fehlerkorrekturcodes, geregelt wird,

kann übrigens

selbstverständlich

außerdem ein

anderer Speicher als der Speicher 12 verwendet werden.

-

An

Stelle des Generators des Syndroms des ersten Fehlerkorrekturcodes 14 kann

ein anderer erster Fehlerkorrekturcode-Decoder von nahezu derselben

Struktur wie der erste Fehlerkorrekturcode-Decoder 10 getrennt

hergestellt werden, und es können

nicht nur die Daten von dem Speicher 12, sondern außerdem das zweite

Fehlerkennzeichen zu geführt

werden, und durch das Decodierverfahren unter Verwendung des zweiten Fehlerkennzeichens,

zum Beispiel durch Löschkorrektur,

kann der erste Fehlerkorrekturcode decodiert werden, und der korrigierte

Synchronisationsblock kann ausgegeben werden, während das Ausgeben eines unkorrigierten

Synchronisationsblocks verhindert werden kann.

-

5 ist

ein Blockdiagramm der Durchführung

von Fehlerkorrektur des ersten Fehlerkorrekturcodes bei Ausführung 4

durch Exklusives-ODER, unter Verwendung des Speichers 12,

von Fehlerdaten von dem Wiedergabedaten-Konverter 9 und

Korrekturdaten von dem ersten Fehlerkorrekturcode-Decoder 10.

-

Übrigens

entspricht der Generator des Syndroms des ersten Fehlerkorrekturcodes 14 „einem

dritten Fehlerkorrekturcode-Decoder zum weiteren Decodieren des

ersten Fehlerkorrekturcodes in dem Synchronisationsblock, von dem

der zweite Fehlerkorrekturcode decodiert wird, um bei Korrektursperrung

nicht die Daten in Bezug auf Korrektursperrung auszugeben".

-

Daher

kann die Steuerung zum Verhindern der Ausgabe des Korrektur-Sperrsignals

in einem sehr kleinen Schaltungsumfang verwirklicht werden und das

auf dem Bildschirm erscheinende Rauschen kann verringert werden

und die Bildqualität

kann verbessert werden.

-

Die

Erfindung enthält

außerdem

als eine Ausführung

die Wiedergabevorrichtung nur zur Wiedergabe unter Ausschluss des

nicht gezeigten Aufzeichnungsvorrichtungsabschnitts aus der Aufzeichnungs-

und Wiedergabevorrichtung, die so gebildet ist, wie in 4 oder 5 gezeigt.

-

Durch

Ausführen

der Erfindung, wie hierin beschrieben, kann das wiedergegebene Bild

in einem schlimmsten Fall immer noch ein Bild sein, wobei jedoch

die Steuerung zum Verhindern der Ausgabe des Korrektur-Sperrsignals

automatisch verwirklicht wird und ein auf Grund eines Fehlers in

großem

Maße gestörter Bildschirm

nicht wiedergegeben wird, um dadurch das Wiedergabeverfahren, die

Wiedergabevorrichtung und die Aufzeichnungs- und Wiedergabevorrichtung

zu verwirklichen, die zu stabiler Wiedergabe bei einem kleinen Schaltungsumfang

fähig sind.

-

- 1

- Speicherkontroller

- 2

- Speicher

- 3

- Zweiter

Fehlerkorrekturcode-Codierer

- 4

- Erster

Fehlerkorrekturcode-Codierer

- 5

- Aufzeichnungsdaten-Konverter

- 6

- Aufzeichnungskopf

- 7

- Aufzeichnungsmedium

- 8

- Wiedergabekopf

- 9

- Wiedergabedaten-Konverter

- 10

- Erster

Fehlerkorrekturcode-Decoder

- 11

- Speicherkontroller

- 12

- Speicher

- 13

- Zweiter

Fehlerkorrekturcode-Decoder

- 14

- Generator

des Syndroms des ersten Fehlerkorrekturcodes