CN1316632C - 具有基体接触的薄膜晶体管组件 - Google Patents

具有基体接触的薄膜晶体管组件 Download PDFInfo

- Publication number

- CN1316632C CN1316632C CNB031216315A CN03121631A CN1316632C CN 1316632 C CN1316632 C CN 1316632C CN B031216315 A CNB031216315 A CN B031216315A CN 03121631 A CN03121631 A CN 03121631A CN 1316632 C CN1316632 C CN 1316632C

- Authority

- CN

- China

- Prior art keywords

- film transistor

- matrix

- contact

- thin

- impurity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

Abstract

一种具有基体接触的薄膜晶体管组件,应用于多晶硅薄膜晶体管液晶显示器,借助于薄膜晶体管制作隔离于栅极电极、源极区和漏极区的基体接触区,并借由在基体接触区掺杂与源极区和漏极区不同型态的杂质来施加基体触发(body-trigger)偏压于薄膜晶体管的基体,用来降低薄膜晶体管驱动电路的临界电压(Threshold Voltage),以增加其驱动电流。

Description

技术领域

本发明涉及一种薄膜晶体管组件,特别是关于一种应用于低温多晶硅薄膜晶体管液晶显示器的具有基体接触的薄膜晶体管组件。

背景技术

薄膜晶体管(Thin Film Transistor,TFT)为薄膜晶体管液晶显示器(TFTLCD)的重要组件,薄膜晶体管的技术主要分为非晶硅(Amorphous Silicon)与多晶硅(Polysilicon)二种,非晶硅薄膜晶体管目前技术成熟,为液晶显示器的主流产品。而多晶硅技术则需使非晶硅经再结晶转化成多晶硅结构,由于制作成本及显示品质上的考虑,其中又以低温多晶硅技术为目前的发展重点。多晶硅晶体管的电子移动速度较非晶硅提高百倍,具有显示画面反映速度快、高亮度、及高分辨率等优点。此外,由于多晶硅的电子移动速度快,因此可将外围驱动电路整合于多晶硅的玻璃基板上,以减轻其重量,达到轻薄化的要求。

然而,目前将薄膜晶体管及其驱动电路整合制作于多晶硅的玻璃基板的工艺,同利用互补金属氧化物半导体(Complementary Metal-OxideSemiconductor,CMOS)技术制作的驱动电路相比较,其具有临界电压较高以及电子迁移率较低的缺点。由此可知,在相同尺寸大小的情况下,薄膜晶体管组件所产生的驱动电流仍小于互补式金属氧化物半导体整合组件。而且,在薄膜晶体管液晶显示器朝向大尺寸与高分辨率发展的情况下,需要更高效能的薄膜晶体管驱动电路来加以配合。同时,制作于多晶硅的玻璃基板的驱动电路面积需受限于像素的间距,要如何在有限的面积内制作高效能的薄膜晶体管组件即成为目前的研究重点。

发明内容

为解决已有技术的问题,即在有限的驱动电路面积内增加薄膜晶体管的驱动电流。本发明提供一种具有基体接触的薄膜晶体管组件,利用施加基体触发(body-trigger)偏压于薄膜晶体管的基体,来降低薄膜晶体管的临界电压以增加其驱动电流。

为了达到上述目的,本发明所公开的具有基体接触的薄膜晶体管组件,其包含有:一绝缘基体、一多晶硅层、一绝缘层(其材质可为氧化硅)以及一栅极电极;多晶硅层形成于此绝缘基体的表面,此多晶硅层由一沟道区、一源极区及一漏极区所组成,源极区与漏极区为掺杂有适当的杂质且分别连接于沟道区;绝缘层为覆盖于多晶硅层的沟道区、部分的源极区和漏极区的表面;以及,一栅极电极形成于多晶硅层的沟道区的氧化硅层上方。其中,于沟道区具有连接绝缘基体与绝缘层的基体接触区,其基体接触区表面是具有贯穿绝缘层的接触层,并且,接触层未与栅极电极接触。此基体接触区需掺杂和源极区与漏极区不同型态的杂质,以提供基体触发(body-trigger)偏压于绝缘基体。

本发明提供了一种具有基体接触的薄膜晶体管组件,其由绝缘基体、多晶硅层、绝缘层与栅极电极组成,该多晶硅层包含有沟道区、源极区和漏极区,其特征在于:该源极区与该漏极区掺杂有适当的第一杂质且分别连接于该沟道区,该沟道区一端具有连接该绝缘基体与该绝缘层的基体接触区,该基体接触区表面具有贯穿该绝缘层的接触层,并且,该接触层未与该栅极电极接触,该基体接触区掺杂和该源极区与该漏极区不同价数的第二杂质,以提供基体触发偏压于该绝缘基体。

本发明还提供了一种具有基体接触的薄膜晶体管组件,其由绝缘基体、多晶硅层、绝缘层与栅极电极组成,该多晶硅层包含有沟道区、源极区和漏极区,其特征在于:该源极区与该漏极区掺杂有适当的第一杂质且分别连接于该沟道区,该沟道区一端具有连接该绝缘基体与该绝缘层的基体接触区,该基体接触区表面具有贯穿该绝缘层的接触层,该基体接触区与其上方的该接触层形成于该栅极电极所环绕的内部区域,且该接触层未与该栅极电极接触,该基体接触区掺杂和该源极区与该漏极区不同价数的第二杂质,以提供基体触发偏压于该绝缘基体。

为使对本发明的目的、构造特征及其功能有进一步的了解,配合附图详细说明如下:

附图说明

图1为本发明的薄膜晶体管驱动电路布局示意图;

图2为本发明第一实施例的结构俯视示意图;

图3为本发明第一实施例的结构的剖面示意图;

图4为本发明第二实施例的结构俯视示意图;

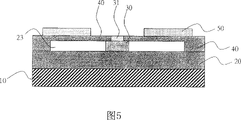

图5为本发明第二实施例的结构的剖面示意图;

图6为本发明第二实施例的结构的剖面示意图;

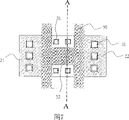

图7为本发明第三实施例的结构俯视示意图;及

图8为本发明第三实施例的结构的剖面示意图。

具体实施方式

首先以实际电路来说明本发明的作用情形,请参考图1,其为本发明的薄膜晶体管驱动电路示意图。其将具有基体接触的P型与N型薄膜晶体管组件(Mp和Mn)与负载电容(CL)、电源供应(VCC)、输入端(In)和输出端(Out)加以连接,当其输入端(In)接收一由低至高的信号时,基体触发电路所产生的偏压为分别施加于P型与N型薄膜晶体管组件;同时,亦使N型薄膜晶体管的临界电压下降,P型薄膜晶体管的临界电压上升。因此,使N型薄膜晶体管的驱动电流上升和P型薄膜晶体管的驱动电流下降,而减少输出端的下降时间(falling time)。

反之,在输入端(In)接收一由高至低的信号时,基体触发电路所产生的偏压为分别施加于P型与N型薄膜晶体管组件;同时,则使P型薄膜晶体管的临界电压下降,N型薄膜晶体管的临界电压上升。因此,使P型薄膜晶体管的驱动电流上升和N型薄膜晶体管的驱动电流下降,而减少输出端的上升时间(rising time)。

综上所述,由于基体触发(body-trigger)偏压的影响,可以增加P型与N型薄膜晶体管组件于反应时的驱动电流进而减少上升与下降时间。显示本发明可在不影响反应速度的前提下,减少薄膜晶体管的尺寸大小;藉此在有限的面积内制作更多的驱动电路与组件,以降低成本且具有良好的可靠度。

请参考图2与图3,图2为本发明第一实施例的结构俯视示意图;图3为本发明第一实施例的结构的剖面示意图,其剖面线为图2中的A’-A线段。本发明第一实施例是为一N型薄膜晶体管,由建立于一基板10的绝缘基体20、多晶硅层、氧化硅层40以与栅极电极50所组成;依次为栅极电极50、氧化硅层40、多晶硅层与绝缘基体20由上而下堆叠而成。其中,多晶硅层由一沟道区23、一源极区21及一漏极区22所组成,源极区21与漏极区22为掺杂有适当的五价施主且分别连接于沟道区23;以及,沟道区23的另外两端为分别具有连接绝缘基体20与氧化硅层40的基体接触区30,其基体接触区30表面为具有贯穿氧化硅层40的接触层31,并且,此接触层31未与栅极电极50接触。此基体接触区30是掺杂三价受主,以提供基体触发(body-trigger)偏压于绝缘基体20。

其实际层叠情形如图3中所示,多晶硅层形成于此绝缘基体20的表面,氧化硅层40覆盖于多晶硅层沟道区23的表面;以及,一栅极电极50形成于多晶硅层的沟道区23的氧化硅层40上方。其中,于沟道区23具有连接绝缘基体20与氧化硅层40的基体接触区30,其基体接触区30表面具有贯穿氧化硅层40的接触层31,并且,接触层31未与栅极电极50接触。此基体接触区30需掺杂和源极区21与漏极区22不同型态的三价受主,以提供基体触发(body-trigger)偏压于绝缘基体20。源极区21与漏极区22亦具有贯穿氧化硅层40的接触层31。

其中,此基体接触区可在其上方的接触层在不与栅极电极接触的前提之下,建立于沟道区的各个位置。甚或于栅极电极内挖出一穿孔以于穿孔内建立基体接触区及其接触层,如图4所示,其为本发明第二实施例的结构俯视示意图。此具有基体接触的薄膜晶体管组件是在其栅极电极50之内挖出露出氧化硅层40的八边型穿孔51,并且,于此八边型穿孔51内建立基体接触区30及其接触层31,即栅极电极50区域为环绕于此基体接触区30及其接触层31。再进一步说明其配置,请参考图5,其为本发明第二实施例的结构的剖面示意图,其剖面线为图4中的A’-A线段。由此可知栅极电极50、基体接触区30及其接触层31的相对位置。另外,请参考图6,其为本发明第二实施例的结构的剖面示意图,其剖面线为图4中的B’-B线段。除了表示出栅极电极50、基体接触区30及其接触层31的相对位置,亦显示多晶硅层的沟道区23、源极区21及漏极区22的配置关系。

此外,亦可于栅极电极的边缘形成延伸至沟道区上方的适当凹槽,并于凹槽所掏空的区域建立基体接触区及其接触层,如图7所示,其为本发明第三实施例的结构俯视示意图;使栅极电极50形成H形区域,并于其所产生的延伸至沟道区23上方的凹槽52建立数个掺杂三价受主的基体接触区及其接触层,掺杂五价施主的源极区21与漏极区22则分别连接于此栅极电极下方的沟道区23。再借由剖面图来说明本发明第三实施例的堆栈及配置情形,请参考图8,其为本发明第三实施例的结构的剖面示意图,其剖面线为图7中的A’-A线段。其显示第三实施例的栅极电极50、基体接触区30、接触层31、多晶硅层的沟道区23、源极区21及漏极区22的相对位置及配置。

其中,由上述实施例得知源极区与漏极区邻接于接触区,且借由基体接触区所掺杂的不同杂质来提供基体触发(body-trigger)偏压。而且,本发明的电极栅极可由铬与铝其中之一制成,以上所述的方法亦可实施在P型TFT晶体管上,以增加其驱动电流。

虽然本发明的较佳实施例公开如上所述,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与修改,因此本发明的专利保护范围须视本说明书所附的权利要求所界定者为准。

Claims (10)

1.一种具有基体接触的薄膜晶体管组件,由一绝缘基体、一多晶硅层、一绝缘层与一栅极电极所组成,该多晶硅层包含有一沟道区、一源极区和一漏极区,其特征在于:该源极区与该漏极区掺杂有适当的第一杂质且分别连接于该沟道区,该沟道区一端具有连接该绝缘基体与该绝缘层的一基体接触区,该基体接触区表面具有贯穿该绝缘层的一接触层,并且,该接触层未与该栅极电极接触,该基体接触区掺杂和该源极区与该漏极区不同价数的第二杂质,以提供一基体触发偏压于该绝缘基体。

2.如权利要求1所述的具有基体接触的薄膜晶体管组件,其中该第一杂质为一五价施主时,该第二杂质为一三价受主。

3.如权利要求1所述的具有基体接触的薄膜晶体管组件,其中该第一杂质为一三价受主时,该第二杂质为一五价施主。

4.如权利要求1所述的具有基体接触的薄膜晶体管组件,其中该栅极电极的边缘形成延伸至该沟道区上方的一凹槽,并于该凹槽所掏空的区域建立该基体接触区及该接触层。

5.如权利要求1所述的具有基体接触的薄膜晶体管组件,其中该电极栅极材料选自铬或铝。

6.一种具有基体接触的薄膜晶体管组件,由一绝缘基体、一多晶硅层、一绝缘层与一栅极电极所组成,该多晶硅层包含有一沟道区、一源极区和一漏极区,其特征在于:该源极区与该漏极区掺杂有适当的第一杂质且分别连接于该沟道区,该沟道区一端具有连接该绝缘基体与该绝缘层的一基体接触区,该基体接触区表面具有贯穿该绝缘层的一接触层,该基体接触区与其上方的该接触层形成于该栅极电极所环绕的一内部区域,且该接触层未与该栅极电极接触,该基体接触区掺杂和该源极区与该漏极区不同价数的第二杂质,以提供一基体触发偏压于该绝缘基体。

7.如权利要求6所述的具有基体接触的薄膜晶体管组件,其中该第一杂质为一五价施主时,该第二杂质为一三价受主。

8.如权利要求6所述的具有基体接触的薄膜晶体管组件,其中该第一杂质为一三价受主时,该第二杂质为一五价施主。

9.如权利要求6所述的具有基体接触的薄膜晶体管组件,其中该栅极电极的边缘形成延伸至该沟道区上方的一凹槽,并于该凹槽所掏空的区域建立该基体接触区及该接触层。

10.如权利要求6所述的具有基体接触的薄膜晶体管组件,其中该电极栅极材料选自铬或铝。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CNB031216315A CN1316632C (zh) | 2003-03-18 | 2003-03-18 | 具有基体接触的薄膜晶体管组件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CNB031216315A CN1316632C (zh) | 2003-03-18 | 2003-03-18 | 具有基体接触的薄膜晶体管组件 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1532946A CN1532946A (zh) | 2004-09-29 |

| CN1316632C true CN1316632C (zh) | 2007-05-16 |

Family

ID=34285760

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB031216315A Expired - Fee Related CN1316632C (zh) | 2003-03-18 | 2003-03-18 | 具有基体接触的薄膜晶体管组件 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN1316632C (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7453122B2 (en) * | 2005-02-08 | 2008-11-18 | Taiwan Semiconductor Manufacturing Co., Ltd. | SOI MOSFET device with reduced polysilicon loading on active area |

| JP4350106B2 (ja) | 2005-06-29 | 2009-10-21 | 三星モバイルディスプレイ株式會社 | 平板表示装置及びその駆動方法 |

| CN102664189B (zh) * | 2012-05-18 | 2016-08-31 | 中国科学院微电子研究所 | Soi mos晶体管 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1196832A (zh) * | 1996-06-28 | 1998-10-21 | 精工爱普生株式会社 | 薄膜晶体管及其制造方法和使用该薄膜晶体管的电路和液晶显示装置 |

| CN1272695A (zh) * | 1999-04-15 | 2000-11-08 | 株式会社半导体能源研究所 | 电光器件和电子设备 |

| JP2002057345A (ja) * | 2001-05-14 | 2002-02-22 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

-

2003

- 2003-03-18 CN CNB031216315A patent/CN1316632C/zh not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1196832A (zh) * | 1996-06-28 | 1998-10-21 | 精工爱普生株式会社 | 薄膜晶体管及其制造方法和使用该薄膜晶体管的电路和液晶显示装置 |

| CN1272695A (zh) * | 1999-04-15 | 2000-11-08 | 株式会社半导体能源研究所 | 电光器件和电子设备 |

| JP2002057345A (ja) * | 2001-05-14 | 2002-02-22 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1532946A (zh) | 2004-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP4297089A1 (en) | Display substrate and display panel | |

| US6310598B1 (en) | Matrix type liquid-crystal display unit | |

| CN102446488B (zh) | 半导体器件 | |

| US5536950A (en) | High resolution active matrix LCD cell design | |

| JP3402400B2 (ja) | 半導体集積回路の作製方法 | |

| CN101320181B (zh) | 显示装置及其制造方法 | |

| WO2020238013A1 (zh) | Goa 电路及阵列基板 | |

| US6091115A (en) | Semiconductor device including a crystalline silicon film | |

| US7038276B2 (en) | TFT with body contacts | |

| CN104779257B (zh) | Tft布局结构 | |

| CN101789434B (zh) | 影像显示系统及其制造方法 | |

| US7256457B2 (en) | Thin-film transistor device, utilizing different types of thin film transistors | |

| JP2005064477A (ja) | ゲートとボディーが電気的に連結された薄膜トランジスタとその製造方法及びこれを備えたディスプレイ装置 | |

| CN1316632C (zh) | 具有基体接触的薄膜晶体管组件 | |

| JPH0926600A (ja) | 液晶表示装置 | |

| JP2997737B2 (ja) | 液晶表示装置 | |

| JPH0864830A (ja) | アクティブマトリクス基板およびその製造方法 | |

| JPH08220506A (ja) | 液晶表示装置 | |

| CN208903642U (zh) | 反相器及goa电路 | |

| US11670253B2 (en) | Pixel driving circuit, array substrate and display panel | |

| US8164093B2 (en) | Display device | |

| US6825495B1 (en) | CMOS transistor and CMOS-based device | |

| US20080217619A1 (en) | Thin film transistor and display device | |

| JPH08220505A (ja) | 液晶表示装置 | |

| CN105206216A (zh) | 显示装置及其应用在栅极驱动电路中的移位寄存电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20070516 Termination date: 20160318 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |