CN116156791A - 一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 - Google Patents

一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 Download PDFInfo

- Publication number

- CN116156791A CN116156791A CN202310156575.1A CN202310156575A CN116156791A CN 116156791 A CN116156791 A CN 116156791A CN 202310156575 A CN202310156575 A CN 202310156575A CN 116156791 A CN116156791 A CN 116156791A

- Authority

- CN

- China

- Prior art keywords

- layer

- thickness

- components

- build

- core

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4697—Manufacturing multilayer circuits having cavities, e.g. for mounting components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/185—Components encapsulated in the insulating substrate of the printed circuit or incorporated in internal layers of a multilayer circuit

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

本申请提供一种在芯板层及增层均埋入元器件的PCB板结构及其制作方法,按照厚度范围将不同厚度的芯片分成若干组;将厚度低于内层芯板的第1厚度范围的芯片嵌埋于内层芯板所在层的第1腔体,然后制作第1增层,第1增层是第1厚度范围内的芯片的导电和/或散热层,将第2厚度范围的芯片埋设在第1增层厚度范围内的第2腔体,依次类推,将不同厚度的芯片分批次埋入,可实现充分布线和提升产品的空间利用率,解决了空腔上方填胶空洞和靠近空腔位置介电层厚度偏薄的问题;所有内埋元件上下各层均基本对称,避免了元件弯折甚至开裂的风险。

Description

技术领域

本申请涉及一种在PCB板结构中制作元器件的技术领域,尤其涉及一种在芯板层及增层均埋入元器件的PCB板结构及其制作方法。

背景技术

集成电路芯片的制造过程主要包括以下几个阶段:集成电路芯片的设计阶段、集成电路芯片的制作阶段、集成电路芯片的封装阶段、以及集成电路芯片的测试阶段。随着集成电路芯片的制造工艺的不断进步,电子产品向高速化、高集成度和高可靠性的方向迅速发展,对集成电路的制造工艺的要求也在不断提高。

目前嵌埋元器件的PCB板,内埋元件类型包括存储芯片、功率芯片、逻辑芯片这样的主动元器件,也包括贴片式的电容、电阻和电感等被动元件。不同属性的内埋元器件厚度往往不一致,即便是相同属性的元器件,也会因为元件型号的差异导致厚度不一致。如常规的C0402电容厚度为0.5mm,而常规的C0201电容厚度只有0.3mm。

而现有的内埋多种元器件的PCB板,如图3所示,采用的是所有元器件同层埋入的制作工艺流程:

(a)芯板层经贴膜→曝光→显影→蚀刻→褪膜流程,完成芯板层图形转移,其中内层芯板的厚度比最大的元件厚度大15-20um;如图3(a),其中芯板为3层结构,芯板包括中间的内层芯板。(b)芯板铣槽,铣槽加工方式可以是钢模冲切、机械铣、CO2镭射钻及UV切割中的一种或多种;

(c)芯板层背面用贴胶机贴高温胶带,胶带为25um厚的聚酰亚胺层和25um厚的亚克力胶层的组合;

(d)贴元器件,元件通过盲槽底部胶带固定。元器件包括各种类型的芯片,贴片式的电容、电阻和电感等;

(e)芯板层Top面排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将盲槽填满。粘结片包括PP或ABF半固化粘结片材,铜箔包括3um载体铜箔、12um铜箔、18um铜箔、35um铜箔等其中的一种或多种。

(f)撕掉芯板层背面的高温胶带;

(g)芯板层Bottom面排板,盖上粘结片及铜箔,然后进压机高温压合形成第1增层;

(h)第1增层做激光钻孔;

(i)第1增层做填孔电镀,填平激光钻盲孔;

(j)第1增层经贴膜→曝光→显影→蚀刻→褪膜流程,完成第1增层图形转移;

(k)上下两面排板,盖上粘结片及铜箔,然后进压机高温压合形成第2增层;

(l)第2增层做激光钻孔;

(m)第2增层做填孔电镀,填平激光钻盲孔;

然后,第2增层经贴膜→曝光→显影→蚀刻→褪膜流程,完成第2增层图形转移。重复上述步骤,最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

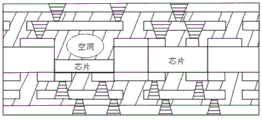

通过上述的工艺流程,制作出的PCB板结构如图4所示,发明人发现以上现有流程加工形成的产品结构有以下缺点:

1、比较薄的元器件(芯片)的上方出现了空洞,只有最厚的那款元器件可以双面都通过盲孔连接PCB网络并扇出信号,其余的都只能单面导通和扇出,这对于产品的整体布线和网络设计是一种浪费;

2、在现有产品结构中,薄元件上下严重不对称,部分元件受结构不对称产生的应力影响,造成元件弯折甚至开裂,最终导致产品报废。

针对上述问题,发明人认为有必要提供一种减少浪费结构空间,增加信号扇出通道,部分元件结构免受不对称应力影响的新型PCB板结构制作方式。

发明内容

本申请实施例提供一种在芯板层及增层均埋入元器件的PCB板结构的技术方案,用以解决现有技术中不同厚度芯片制作中浪费结构空间,部分元件受结构不对称产生的应力影响,容易导致产品报废的技术问题。

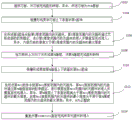

本申请实施例提供一种在芯板层及增层均埋入元器件的PCB板结构的制作方法,包括如下步骤:

S102,提供芯板,对芯板完成图形转移;其中,所述芯板为PCB基板;

S104,铣槽形成贯穿芯板上下表面的第1腔体;

S106,在所述第1腔体中贴第1厚度范围内的元器件,第1厚度范围内的元器件通过芯板底部的胶带固定,完成第1厚度范围内的元器件的埋入;其中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

S108,在芯板的上方与下方形成第N增层;对第N增层完成图形转移;

S110,铣槽形成贯穿第N增层上下表面的第N+1腔体;

S112,在所述第N+1腔体中贴第N+1厚度范围内的元器件,第N+1厚度范围内的元器件通过第N增层底部的胶带固定,完成厚度在第N+1范围内的元器件的埋入;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件的最大厚度;其中,N为正整数;

S114,重复步骤S108-S112直至完成所有元器件的埋入。

进一步的,所述芯板为双面覆铜板。

进一步的,步骤S106中,所述胶带贴在芯板底部覆盖第1腔体在芯板下表面的贯通口。

进一步的,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

进一步的,所述形成第N增层包括:

S1082,在芯板层上方排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将第N腔体填满;

S1084,去除所述胶带;

S1086,芯板层下方排板,盖上粘结片及铜箔,然后进压机高温压合形成第N增层。

进一步的,粘结片包括PP或ABF半固化粘结片材。

进一步的,铜箔包括3um载体铜箔、12um铜箔、18um铜箔或35um铜箔中的一种或多种。

进一步的,所述形成第N增层还包括做激光钻盲孔,电镀填平所述激光钻盲孔。

进一步的,所述图形转移包括贴膜、曝光、显影、蚀刻和褪膜流程。

进一步的,所述胶带为25um厚的聚酰亚胺层和25um厚的亚克力胶层的组合。

进一步的,所述铣槽包括钢模冲切、机械铣、CO2镭射钻或UV切割中的一种或多种。

进一步的,所述第N厚度范围内的元器件相互之间的厚度差不超过10um。

进一步的,还包括最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

进一步的,所述去除所述胶带通过人工去除或智能设备去除。

进一步的,第N增层包括芯板上方和下方的导电层和/或导热层。

本申请实施例还提供一种在芯板层及增层均埋入元器件的PCB板结构,包括芯板,所述芯板为PCB基板;其中,芯板具有贯穿芯板上下表面的第1腔体;第1厚度范围内的元器件嵌埋于所述第1腔体中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

第N增层;具有贯穿第N增层上下表面的第N+1腔体;

第N+1厚度范围内的元器件嵌埋于所述第N+1腔体中;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件的最大厚度;其中,N为正整数。

进一步的,所述芯板为双面覆铜板。

进一步的,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

进一步的,所述第N增层还包括芯板上方和下方的导电层和/或导热层。

进一步的,所述第N厚度范围内的元器件相互之间的厚度差不超过10um。

本申请实施例还提供一种电子器件,包括前述的在芯板层及增层均埋入元器件的PCB板结构。

本申请实施例还提供一种电子设备,包括前述的在芯板层及增层均埋入元器件的PCB板结构。

本申请提供的实施例至少具有以下有益效果:

本申请提供一种在芯板层及增层均埋入元器件的PCB板结构的制作方法,通过对现有的埋入元器件的PCB板结构制作工艺进行改造,按照厚度范围将不同厚度的芯片分成若干组;将厚度低于内层芯板的第1厚度范围的芯片嵌埋于内层芯板所在层的第1腔体内,制作第1增层,第1增层是第1厚度范围芯片的导电和/或散热层,将第2厚度范围的芯片埋设在第1增层厚度范围内的第2腔体,依次类推,将不同厚度的芯片分批次埋入,可实现充分布线和提升产品的空间利用率,解决了空腔上方填胶空洞和靠近空腔位置介电层厚度偏薄的问题;在新产品结构中,能有效减少浪费结构空间,增加信号扇出通道,部分元件结构免受不对称应力影响,延长使用寿命。

附图说明

此处所说明的附图用来提供对本申请的进一步理解,构成本申请的一部分,本申请的示意性实施例及其说明用于解释本申请,并不构成对本申请的不当限定。在附图中:

图1为本申请实施例提供的一种在芯板层及增层均埋入元器件的PCB板结构的方法流程图;

图2为本申请实施例提供的一种在芯板层及增层均埋入元器件的PCB板结构的工艺流程图;

图3为现有的埋入元器件的PCB板结构的工艺流程图;

图4为现有的埋入元器件的PCB板部分结构的剖面图;

图1-4中:202、芯板;204、第1腔体;206、胶带;208、第1厚度范围内的元器件;210、第1增层;212、激光钻盲孔;214、第N腔体;216、第N厚度范围内的元器件;218、第2增层;220、内层芯板。

具体实施方式

为使本申请的目的、技术方案和优点更加清楚,下面将结合本申请具体实施例及相应的附图对本申请技术方案进行清楚、完整地描述。显然,所描述的实施例仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

本申请的元器件包括各种类型的芯片,例如,贴片式的电容、电阻和电感等。目前市场上采用比较多的是存储芯片。事实上,本申请的技术方案也可以是其他任何芯片,本申请不作限制。

如图3-4,现有的埋入元器件的PCB板的制作工艺,都是将厚度不同的芯片一并埋入,发明人发现以现有流程加工形成的产品结构有以下缺点:

1、只有最厚的那款元器件可以双面都通过盲孔连接PCB网络并扇出信号,其余的都只能单面导通和扇出,这对于产品的整体布线和网络设计是一种浪费;在有些情况下,这种PCB板结构不能满足信号扇出的需求;

2、芯板厚度远大于较薄元件的厚度,第1增层压合时薄元件上方存在巨大空腔需要用流胶填满,导致该空腔存在填胶不足产生压合空洞的风险,并且在靠近空腔的位置第1增层与芯板层之间的粘结片因为贡献太多的流胶用于填空腔,容易造成该位置的介电层厚度严重偏薄以致不能满足客户的需求;

3、在现有产品结构中,薄元件上下严重不对称,部分元件受结构不对称产生的应力影响,造成元件弯折甚至开裂,最终导致产品报废;

4、芯板厚度必须保证比最厚的内埋元件厚15-20um,成品板厚也较大,不符合电子产品薄型化的发展需求。

为解决现有制作工艺对结构空间浪费大,扇出信号通道数量少,受不对称应力容易弯曲、折断的技术问题,如图1-2所示,本申请实施例提供一种在芯板202层及增层均埋入元器件的PCB板结构的制作方法,包括如下步骤:

S102,提供芯板202,对芯板202完成图形转移;其中,所述芯板202为PCB基板,如图2(a);

需要说明的是,所述芯板202(PCB基板)为覆铜板,可以是单面覆铜板,也可以是双面覆铜板,优选的,本申请采用双面覆铜板。事实上,也可以是其他类型的基板,具体类型根据实际加工需求而定,本申请不作具体限制。

S104,铣槽形成贯穿芯板202上下表面的第1腔体204,如图2(b);

需要说明的是,首先在芯板202的外层上形成光刻、刻蚀图形,通过芯板202上的图形窗口对内层芯板220铣槽形成贯穿芯板202上下表面的第1腔体204。如图2(a),芯板202包括中间的内层芯板220。

进一步的,所述铣槽包括钢模冲切、机械铣、CO2镭射钻或UV切割其中的一种或多种。事实上,本申请也可以不采用铣槽,也可以采用其他方法开槽,本申请不作特别的限制。

需要说明的是,所述第1腔体204是通槽,如果是盲槽,也可以采用其他方法制作。所述的第1腔体204可以包括在芯板202上形成的图形。所述第1腔体204的尺寸根据所需埋入的芯片进行确定,设计成比所需埋入的芯片略大即可。优选的,腔体单边比芯片的尺寸大80um。

S106,在所述第1腔体204中贴第1厚度范围内的元器件208,第1厚度范围内的元器件208通过芯板202底部的胶带206固定,进行第1厚度范围内的元器件208的埋入步骤直至完成埋入;其中,内层芯板220的厚度大于第1厚度范围内的元器件208的最大厚度,如图2(c)- 2(d);

需要说明的是,所述第1厚度范围的元器件,根据不同的层厚进行分组而得到,第1厚度范围内的元器件208的最大厚度是要小于内层芯板220的。优选的,内层芯板220的厚度比第1厚度范围内的元器件208的最大厚度大15-20um。优选的,内层芯板220的厚度比第1厚度范围内的元器件208的最大厚度大20um。优选的,内层芯板220的厚度比第1厚度范围内的元器件208的最大厚度大18um。

优选的,第1厚度范围内的元器件208之间的高度差不超过10um。

需要说明的是,可以采用贴片机在所述第1腔体204中贴第1厚度范围内的元器件208,所述的贴片机是高精度贴片机。

需要说明的是,步骤S106中,在芯板202底部预先贴上胶带206,所述的胶带206覆盖第一腔体的下表面,优选的,完全覆盖住腔体的下表面。

需要说明的是,所述胶带206为高温胶带206,所述高温胶带206贴在芯板202底部覆盖第1腔体204在芯板202下表面的贯通口。进一步的,所述胶带206为25um厚的聚酰亚胺层和25um厚的亚克力胶层贴合而成。

需要说明的是,采用高温胶带206是为了应对后续的热处理等具有高温的工艺,如果后续过程没有高温高热的工艺,也可以采用其他普通胶带206或其他类似的材料。

需要说明的是,高温胶带206覆盖住所述腔体在PCB基板的下表面的贯穿口,防止元器件滑出,也可以采用其他阻挡件达到类似的效果;利用所述高温胶带206固定所述芯片模组是临时性质的固定,后续需要去除胶带206。

S108,在芯板202的上方与下方形成第N增层,如图2(e)-图2(i);对第N增层完成图形转移,如图2(j);

需要说明的是,在所述PCB基板的上表面设置半固化片及铜箔形成上下层导电层和/或散热层的增层;

需要说明的是,金属具有良好的导电性和导热性,半固化片及铜箔形成的层用于导电层还是散热层,本领域技术人员可根据实际加工需求进行设计。

进一步的,如图2(g)-图2(i),所述形成第N增层包括:

S1082,在芯板202层上方排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将第N腔体214填满;

S1084,去除所述胶带206;

S1086,芯板202层下方排板,盖上粘结片及铜箔,然后进压机高温压合形成第N增层。

需要说明的是,粘结片包括PP或ABF半固化粘结片材。

需要说明的是,铜箔包括3um载体铜箔、12um铜箔、18um铜箔或35um铜箔中的一种或多种。

优选的,所述半固化片的型号为含胶量73%的106 PP,所述铜箔的厚度为12um。

需要说明的是,同样的,半固化片及铜箔形成的是下层导电层还是下层散热层,本领域技术人员可根据实际加工需求进行设计。

需要说明的是,所述形成第N增层还包括:为了第1厚度范围的芯片的导电或导热,还在相应位置,做激光钻孔,电镀填平激光钻盲孔212。所述的钻孔的直径可以不一样大,用于导电或导热等不同作用。

例如,ø200um激光钻盲孔212的作用是制作金属填充,用于导电和散热,在现有的工艺中,尚未见到做如此大直径的激光钻盲孔212。再例如,ø350um和ø400um两种全塞平通孔可用于连接外部元器件。

S110,铣槽形成贯穿第N增层上下表面的第N+1腔体,如图2(k);

需要说明的是,通过增层上的图形窗口铣槽形成贯穿第N增层上下表面的第N+1腔体。

S112,在所述第N+1腔体中贴第N+1厚度范围内的元器件,第N+1厚度范围内的元器件通过第N增层底部的胶带206固定,进行厚度在第N+1范围内的元器件的埋入步骤直至完成埋入;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件216的最大厚度;其中,N为正整数;参见图2(l)-图2(m);

需要说明的是,本领域技术人员很容易理解,图2(n)-图2(r)是在上下表面形成第二增层,以及在第二增层上形成导电或导热结构的流程。

S114,重复步骤S108-S112直至完成所有元器件的埋入。

需要说明的是,在第1增层210埋入第2厚度范围的芯片,在第2增层218,埋入第3厚度的芯片,以此类推,直至将所有芯片都埋入。本申请实施例的每一厚度范围的芯片与其相邻的增层进行电连接,能够扇出信号,充分利用了结构空间。在经过多增层的封装后,整个封装件受力更加均衡,不容易产生弯曲、折断等问题。

需要说明的是,第N增层上下表面的距离是上下铜箔之间的距离,可以是铜箔上表面之间的距离,或铜箔下表面之间的距离,或铜箔上下表面之间的距离,本领域技术人员应该理解,此种距离的设定可根据客户需求或加工工艺(例如,测量方便)而定,本申请不作严格的限制。

需要说明的是,所述图形转移包括贴膜、曝光、显影、蚀刻和褪膜流程,完成芯板202层图形转移。

进一步的,所述第N厚度范围内的元器件216相互之间的厚度差不超过10um。

进一步的,还包括最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

进一步的,所述去除所述胶带206通过人工去除或智能设备去除。

进一步的,第N增层包括芯板202上方和下方的导电层和/或导热层。

本申请实施例还提供一种在芯板202层及增层均埋入元器件的PCB板结构,包括芯板202,所述芯板202为PCB基板;其中,芯板202具有贯穿芯板202上下表面的第1腔体204;第1厚度范围内的元器件208嵌埋于所述第1腔体204中,内层芯板220的厚度大于第1厚度范围内的元器件208的最大厚度;

第N增层;具有贯穿第N增层上下表面的第N+1腔体;

第N+1厚度范围内的元器件嵌埋于所述第N+1腔体中;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件216的最大厚度;其中,N为正整数。

进一步的,其特征在于,所述芯板202为双面覆铜板。

进一步的,内层芯板220的厚度比第1厚度范围内的元器件208的最大厚度大15-20um。

进一步的,所述第N增层还包括芯板202上方和下方的导电层和/或导热层。

进一步的,所述第N厚度范围内的元器件216相互之间的厚度差不超过10um。本申请实施例还提供一种电子器件,包括前述的在芯板202层及增层均埋入元器件的PCB板结构。

需要说明的是,这里的电子器件应当包括任何电子器件,也就是说任何采用本申请的在芯板202层及增层均埋入元器件的PCB板结构的电子器件均应包含在本申请的应有含义范围内。

本申请实施例还提供一种电子设备,包括前述的在芯板202层及增层均埋入元器件的PCB板结构。

同样需要说明的是,这里的电子设备应当包括任何电子设备,也就是说任何采用本申请的在芯板202层及增层均埋入元器件的PCB板结构的电子设备均应包含在本申请的应有含义范围内。

综上所述,相比于传统的产品结构和加工方法,采用本申请的新加工方法以及形成的新产品结构具有以下优势:

1、不同厚度的元器件双面均可以都通过盲孔连接PCB网络并扇出信号,可实现充分布线和提升产品的空间利用率;

2、内埋元件所在的空腔容积与元件体积接近,压合时填充空腔所需的流胶量小,解决了空腔上方填胶空洞和靠近空腔位置介电层厚度偏薄的问题;

3、内埋元件各层结构不对称会产生额外的应力,导致元件弯折甚至开裂,本申请的内埋元件上下各层基本对称,避免了该问题;

4、最厚的元器件没有埋在芯板202层而是埋在厚度比元件大15-20um的某一增层,因此新产品结构的厚度比原有结构显著减小,符合电子产品薄型化的发展要求。

Claims (22)

1.一种在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,包括如下步骤:

S102,提供芯板,对芯板完成图形转移;其中,所述芯板为PCB基板;

S104,铣槽形成贯穿芯板上下表面的第1腔体;

S106,在所述第1腔体中贴第1厚度范围内的元器件,第1厚度范围内的元器件通过芯板底部的胶带固定,完成第1厚度范围内的元器件的埋入;其中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

S108,在芯板的上方与下方形成第N增层;对第N增层完成图形转移;

S110,铣槽形成贯穿第N增层上下表面的第N+1腔体;

S112,在所述第N+1腔体中贴第N+1厚度范围内的元器件,第N+1厚度范围内的元器件通过第N增层底部的胶带固定,完成厚度在第N+1范围内的元器件的埋入;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件的最大厚度;其中,N为正整数;

S114,重复步骤S108-S112直至完成所有元器件的埋入。

2.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述芯板为双面覆铜板。

3.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,步骤S106中,所述胶带贴在芯板底部覆盖第1腔体在芯板下表面的贯通口。

4.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

5.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述形成第N增层包括:

S1082,在芯板层上方排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将第N腔体填满;

S1084,去除所述胶带;

S1086,芯板层下方排板,盖上粘结片及铜箔,然后进压机高温压合形成第N增层。

6.根据权利要求5所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,粘结片包括PP或ABF半固化粘结片材。

7.根据权利要求5所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,铜箔包括3um载体铜箔、12um铜箔、18um铜箔或35um铜箔中的一种或多种。

8.根据权利要求5所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述形成第N增层还包括做激光钻盲孔,电镀填平所述激光钻盲孔。

9.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述图形转移包括贴膜、曝光、显影、蚀刻和褪膜流程。

10.根据权利要求5所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述胶带为25um厚的聚酰亚胺层和25um厚的亚克力胶层的组合。

11.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述铣槽包括钢模冲切、机械铣、CO2镭射钻或UV切割中的一种或多种。

12.根据权利要求3所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述第N厚度范围内的元器件相互之间的厚度差不超过10um。

13.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,还包括最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

14.根据权利要求5所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,所述去除所述胶带通过人工去除或智能设备去除。

15.根据权利要求1所述的在芯板层及增层均埋入元器件的PCB板结构的制作方法,其特征在于,第N增层包括芯板上方和下方的导电层和/或导热层。

16.一种在芯板层及增层均埋入元器件的PCB板结构,其特征在于,包括芯板,所述芯板为PCB基板;其中,芯板具有贯穿芯板上下表面的第1腔体;第1厚度范围内的元器件嵌埋于所述第1腔体中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

第N增层;具有贯穿第N增层上下表面的第N+1腔体;

第N+1厚度范围内的元器件嵌埋于所述第N+1腔体中;其中,第N增层上下表面的距离大于第N+1厚度范围内的元器件的最大厚度,且第N+1厚度范围内的元器件的最小厚度大于等于第N厚度范围内的元器件的最大厚度;其中,N为正整数。

17.根据权利要求16所述的在芯板层及增层均埋入元器件的PCB板结构,其特征在于,所述芯板为双面覆铜板。

18.根据权利要求16所述的在芯板层及增层均埋入元器件的PCB板结构,其特征在于,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

19.根据权利要求16所述的在芯板层及增层均埋入元器件的PCB板结构,其特征在于,所述第N增层还包括芯板上方和下方的导电层和/或导热层。

20.根据权利要求16所述的在芯板层及增层均埋入元器件的PCB板结构,其特征在于,所述第N厚度范围内的元器件相互之间的厚度差不超过10um。

21.一种电子器件,其特征在于,包括权利要求16-20中任一项所述的在芯板层及增层均埋入元器件的PCB板结构。

22.一种电子设备,其特征在于,包括权利要求16-20中任一项所述的在芯板层及增层均埋入元器件的PCB板结构。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202310156575.1A CN116156791A (zh) | 2023-02-23 | 2023-02-23 | 一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202310156575.1A CN116156791A (zh) | 2023-02-23 | 2023-02-23 | 一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN116156791A true CN116156791A (zh) | 2023-05-23 |

Family

ID=86352366

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202310156575.1A Pending CN116156791A (zh) | 2023-02-23 | 2023-02-23 | 一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN116156791A (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116562201A (zh) * | 2023-07-11 | 2023-08-08 | 广州添利电子科技有限公司 | 一种多层pcb压合后整板厚度的计算方法 |

-

2023

- 2023-02-23 CN CN202310156575.1A patent/CN116156791A/zh active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116562201A (zh) * | 2023-07-11 | 2023-08-08 | 广州添利电子科技有限公司 | 一种多层pcb压合后整板厚度的计算方法 |

| CN116562201B (zh) * | 2023-07-11 | 2023-12-12 | 广州添利电子科技有限公司 | 一种多层pcb压合后整板厚度的计算方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6991718B2 (ja) | 配線基板の製造方法 | |

| KR100733253B1 (ko) | 고밀도 인쇄회로기판 및 그 제조방법 | |

| TWI296492B (en) | Un-symmetric circuit board and method for fabricating the same | |

| WO2021052061A1 (zh) | 一种导热pcb的制作方法及pcb | |

| WO2013000207A1 (zh) | 金属基电路板及其制造方法 | |

| KR20140086824A (ko) | 배선 기판의 제조 방법 | |

| CN102256450A (zh) | 埋入式无源器件的电路板及其制造方法 | |

| CN109327957B (zh) | 一种导热铜基板及其制作方法 | |

| US20120175162A1 (en) | Printed circuit board | |

| CN116156791A (zh) | 一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法 | |

| CN114222445B (zh) | 一种电路板制作方法及电路板 | |

| CN114126259A (zh) | 一种上侧壁非金属化而下侧壁金属化的阶梯孔的制作方法 | |

| JP2017135357A (ja) | 印刷配線板およびその製造方法 | |

| CN110740564B (zh) | 一种密集网络多层印制电路板的加工方法 | |

| KR20090066781A (ko) | 인쇄회로기판의 제조방법 | |

| KR100716809B1 (ko) | 이방전도성필름을 이용한 인쇄회로기판 및 그 제조방법 | |

| JP7333454B2 (ja) | モールド成形プロセスに基づくパッケージ基板及びその製造方法 | |

| JPH0719970B2 (ja) | 多層印刷配線板の製造方法 | |

| CN110785028A (zh) | 一种内埋嵌陶瓷片的pcb板制作方法及其pcb板 | |

| CN213694310U (zh) | 一种元件嵌入式封装填充结构 | |

| JP2004214273A (ja) | 片面積層配線基板の製造方法 | |

| CN117528915A (zh) | 一种基于软硬基板的高导热高绝缘的多层线路板及其制作方法 | |

| KR20080100111A (ko) | 고밀도 패키지 기판 제조 방법 | |

| KR100648235B1 (ko) | 다층 인쇄회로기판 제조방법 | |

| KR20090070117A (ko) | 아노다이징을 이용한 금속 기판 및 이의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication |