CN111324552B - 存储器系统及其操作方法 - Google Patents

存储器系统及其操作方法 Download PDFInfo

- Publication number

- CN111324552B CN111324552B CN201911213480.9A CN201911213480A CN111324552B CN 111324552 B CN111324552 B CN 111324552B CN 201911213480 A CN201911213480 A CN 201911213480A CN 111324552 B CN111324552 B CN 111324552B

- Authority

- CN

- China

- Prior art keywords

- mapping

- memory

- mapped

- mapping information

- unmap

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0646—Configuration or reconfiguration

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0873—Mapping of cache memory to specific storage devices or parts thereof

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0638—Organizing or formatting or addressing of data

- G06F3/064—Management of blocks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0658—Controller construction arrangements

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0868—Data transfer between cache memory and other subsystems, e.g. storage devices or host systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0871—Allocation or management of cache space

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1016—Performance improvement

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/31—Providing disk cache in a specific location of a storage system

- G06F2212/312—In storage controller

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/46—Caching storage objects of specific type in disk cache

- G06F2212/466—Metadata, control data

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

- G06F2212/657—Virtual address space management

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7201—Logical to physical mapping or translation of blocks or pages

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Memory System (AREA)

Abstract

本文描述了存储器系统及其操作方法。一种存储器系统包括:存储器装置,用于存储与针对取消映射命令的目标逻辑地址相关联的第一映射信息和第二映射信息;以及控制器,用于从存储器装置加载第一映射信息和第二映射信息,将与目标逻辑地址相对应的目标映射数据的大小与阈值进行比较,基于比较的结果将与包括目标逻辑地址的多个目标逻辑组分别映射的多个映射段分类到多个区域,并且对区域中包括的映射段中的每一个执行取消映射操作,其中第一映射信息包括关于多个映射段与多个目标逻辑组之间的映射关系的信息,并且第二映射信息包括关于目标逻辑地址与对应的物理地址之间的映射关系的信息。

Description

相关申请的交叉引用

本申请要求于2018年12月17日提交的韩国专利申请号10-2018-0163281的优先权,其全部内容通过引用并入本文。

技术领域

各种实施例涉及存储器系统,并且更具体地涉及能够有效地处理取消映射命令的存储器系统以及存储器系统的操作方法。

背景技术

计算机环境范例已过渡到普适计算,这使得能够随时随地使用计算系统。结果,诸如移动电话、数码相机和膝上型计算机的便携式电子装置的使用迅速增加。这些便携式电子装置通常使用具有一个或多个存储器装置的存储器系统以用于存储数据。存储器系统可以用作便携式电子装置的主存储器装置或辅助存储器装置。

由于它们不具有移动部件,存储器系统提供诸如出色的稳定性和耐用性、高信息访问速度以及低功耗等优点。具有这种优点的存储器系统的示例包括通用串行总线(USB)存储器装置、具有各种接口的存储器卡以及固态驱动器(SSD)。

发明内容

本发明的各种实施例针对可以有效地处理从主机提供的取消映射命令的存储器系统。

根据一个实施例,一种存储器系统包括:存储器装置,适于存储与针对取消映射命令的目标逻辑地址相关联的第一映射信息和第二映射信息;以及控制器,适于从存储器装置加载第一映射信息和第二映射信息,将与目标逻辑地址相对应的目标映射数据的大小与阈值进行比较,基于比较的结果来将与包括目标逻辑地址中的一个或多个的多个目标逻辑组分别映射的多个映射段分类到多个区域,并且对多个区域中包括的映射段中的每一个执行取消映射操作,其中第一映射信息包括关于多个映射段与多个目标逻辑组之间的映射关系的信息,并且第二映射信息包括关于目标逻辑地址与对应的物理地址之间的映射关系的信息。

根据一个实施例,一种存储器系统的操作方法,该操作方法包括:接收取消映射命令;从存储器装置加载与对应于取消映射命令的目标逻辑地址相关联的第一映射信息和第二映射信息,并且将第一映射信息和第二映射信息存储在存储器中;将对应于目标逻辑地址的目标映射数据的大小与阈值进行比较;基于比较的结果,将与包括一个或多个目标逻辑地址的多个目标逻辑组分别映射的多个映射段分类到多个区域;以及对多个区域中的任一个中包括的每个映射段执行取消映射操作,其中第一映射信息包括关于多个映射段与多个目标逻辑组之间的映射关系的信息,并且第二映射信息包括关于目标逻辑地址与对应物理地址之间的映射关系的信息。

根据一个实施例,一种存储器系统包括:存储器装置,适于存储第一映射信息和第二映射信息,第一映射信息包括关于多个映射段与多个逻辑组之间的映射的信息,每个逻辑组包括一个或多个逻辑地址,并且第二映射信息包括关于多个逻辑地址与多个物理地址之间的映射的信息;以及控制器,包括存储器,适于从存储器装置将与取消映射命令相关联的第一映射信息和第二映射信息加载到存储器中;将包括第一映射段、最后映射段和其余映射段的多个映射段划分到包括第一映射段的第一组、包括其余映射段的第二组和包括最后映射段的第三组;以及将针对第一组和第三组的第二映射信息取消映射,并且将针对第二组的第一映射信息取消映射。

附图说明

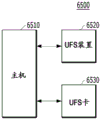

图1是图示根据本发明的实施例的包括存储器系统的数据处理系统的框图。

图2是图示图1的存储器系统中采用的存储器装置的示意图。

图3是图示存储器装置中的存储器块的存储器单元阵列的电路图。

图4是图示存储器装置的示例性三维结构的框图。

图5A是图示根据本发明的实施例的第一表的结构的图。

图5B是图示根据本发明的实施例的第二表的结构的图。

图6A至图6E是图示根据本发明的实施例的存储器系统的操作的图。

图7是图示根据本发明的实施例的存储器系统的操作过程的流程图。

图8至图16是示意性地图示根据本发明的各个实施例的数据处理系统的应用示例的图。

具体实施方式

下面参考附图来更详细地描述本发明的各种实施例。以下描述集中于与本发明的特征和方面有关的细节。为了不模糊这样的描述,可以省略公知的技术信息。另外,在整个说明书中,对“一个实施例”、“另一实施例”等的引用不一定仅是一个实施例,并且对任何这样的短语的不同引用不一定是相同的(一个或多个)实施例。

图1是图示根据本发明的实施例的数据处理系统100的框图。

参考图1,数据处理系统100可以包括可操作地耦合到存储器系统110的主机102。

主机102可以包括诸如移动电话、MP3播放器和膝上型计算机的各种便携式电子装置中的任一个或者诸如台式计算机、游戏机、电视(TV)以及投影仪的各种非便携式电子装置中的任一个。

主机102可以包括至少一个操作系统(OS),OS可以管理和控制主机102的整体功能和操作,并且使用数据处理系统100或存储器110来提供主机102和用户之间的操作。OS可以支持与用户的使用目的和使用情况相对应的功能和操作。例如,主机102可以向存储器系统110提供写入命令、读取命令、擦除命令和取消映射命令,并且存储器系统110可以执行与命令相对应的操作。

存储器系统110可以响应于主机102的请求而进行操作来存储用于主机102的数据。存储器系统110的非限制性示例包括固态驱动器(SSD)、多媒体卡(MMC)、安全数字(SD)卡、通用存储总线(USB)装置、通用闪存(UFS)装置、紧凑型闪存(CF)卡、智能媒体卡(SMC)、个人计算机存储器卡国际协会(PCMCIA)卡和记忆棒。MMC可以包括嵌入式MMC(eMMC)、尺寸减小的MMC(RS-MMC)和微型MMC等。SD卡可以包括小型SD卡和微型SD卡。

存储器系统110可以由各种类型的存储装置中的任何一种来体现。这样的存储装置的示例包括但不限于诸如动态随机存取存储器(DRAM)和静态RAM(SRAM)的易失性存储器装置以及诸如只读存储器(ROM)、掩码ROM(MROM)、可编程ROM(PROM)、可擦除可编程ROM(EPROM)、电可擦除可编程ROM(EEPROM)、铁电RAM(FRAM)、相变RAM(PRAM)、磁阻式RAM(MRAM)、电阻式RAM(RRAM或ReRAM)和闪存的非易失性存储器装置。

存储器系统110可以包括控制器130和存储器装置150。

控制器130和存储器装置150可以集成到单个半导体装置中。例如,控制器130和存储器装置150可以集成为一个半导体装置来构成固态驱动器(SSD)。当存储器系统110用作SSD时,可以提高连接到存储器系统110的主机102的操作速度。另外,控制器130和存储器装置150可以集成为一个半导体装置来构成存储器卡。例如,控制器130和存储器装置150可以构成诸如个人计算机存储器卡国际协会(PCMCIA)卡、紧凑型闪存(CF)卡、智能媒体(SM)卡、记忆棒、包括尺寸减小的MMC(RS-MMC)和微型MMC的多媒体卡(MMC)、包括小型SD卡、微型SD卡和SDHC卡的安全数字(SD)卡或通用闪存(UFS)装置之类的存储器卡。存储器系统110的非限制性应用示例包括计算机、智能电话和便携式游戏机。

存储器装置150可以是非易失性存储器装置,并且即使不供电也可以保持存储在其中的数据。存储器装置150可以通过写入操作来存储从主机102提供的数据,并且可以通过读取操作将存储在其中的数据提供给主机102。存储器装置150可以包括多个存储器块。多个存储器块152中的每一个可以包括多个页,并且每个页可以包括耦合到字线的多个存储器单元。存储器装置150可以包括多个平面并且包括多个存储器管芯,多个平面中的每一个可以包括多个存储器块152,多个存储器管芯中的每一个可以包括多个平面。在一个实施例中,存储器装置150可以是闪存。闪存可以具有3维(3D)堆叠结构。

由于下面参照图2至图4详细描述包括其3D堆叠结构的存储器装置150的结构,这里省略对这些元件和特征的进一步描述。

控制器130可以响应于来自主机102的请求来控制存储器装置150。例如,控制器130可以将从存储器装置150读取的数据提供给主机102,并且将从主机102提供的数据存储到存储器装置150中。对于该操作,控制器130可以控制存储器装置150的读取、编程和擦除操作。

更具体地,控制器130可以包括主机接口(I/F)132、处理器134、存储器接口(I/F)142、存储器144和取消映射管理器146。

主机接口(I/F)132可以被配置为对主机102的命令和数据进行处理,并且可以通过各种接口协议(诸如通用串行总线(USB)、多媒体卡(MMC)、外围部件互连快速(PCI-e或PCIe)、小型计算机系统接口(SCSI)、串行连接的SCSI(SAS)、串行高级技术附件(SATA)、并行高级技术附件(PATA)、增强型小磁盘接口(ESDI)和集成驱动电子装置(IDE))中的一个或多个与主机102通信。主机I/F 132可以通过被称为主机接口层(HIL)的固件来被驱动,以便与主机交换数据。

存储器I/F 142可以用作用于将控制器130和存储器装置150对接的存储器/存储接口,使得控制器130响应于来自主机102的请求来控制存储器装置150。

存储器144可以用作存储器系统110和控制器130的工作存储器,并且存储用于驱动存储器系统110和控制器130的数据。

存储器144可以由易失性存储器来体现。例如,存储器144可以由静态随机存取存储器(SRAM)或动态随机存取存储器(DRAM)来体现。存储器144可以设置在控制器130之内或之外。在一个实施例中,图1例示了设置在控制器130内的存储器144。在另一实施例中,存储器144可以由具有在存储器144和控制器130之间传输数据的存储器接口的外部易失性存储器来体现。

如上所述,存储器144可以存储在主机102和存储器装置150之间执行数据写入/读取操作所需的数据以及在数据写入/读取操作被执行时的数据。为了存储这样的数据,存储器144可以包括程序存储器、数据存储器、写入缓冲器/高速缓存、读取缓冲器/高速缓存、数据缓冲器/高速缓存、映射缓冲器/高速缓存等。

此外,存储器144可以在处理器134的控制下存储映射段和从存储器装置150加载的映射数据。映射数据可以指示与从主机102提供的数据相对应的逻辑块地址和与从主机102提供的数据实际存储在存储器装置150中的位置相对应的物理块地址之间的关系。映射段可以是由多个映射数据组成的映射数据组。例如,一个映射段可以包含100个映射数据。此外,存储器144可以在处理器134的控制下将映射段和映射数据中的每一个作为表来进行管理。

处理器134可以控制存储器系统110的整体操作。处理器134可以驱动固件来控制存储器系统110的整体操作。固件可以被称为闪存转换层(FTL)。而且,处理器134可以被实现为微处理器或中央处理单元(CPU)。

例如,控制器130可以通过处理器134执行由主机102请求的操作。换言之,控制器130可以执行与从主机102接收的命令相对应的命令操作。控制器130可以执行前台操作作为与从主机102接收的命令相对应的命令操作。例如,控制器130可以执行与写入命令相对应的编程操作、与读取命令相对应的读取操作、与擦除命令相对应的擦除操作以及与设置参数命令或设置特征命令相对应的参数设置操作。

取消映射管理器146可以根据从主机102提供的取消映射命令来执行取消映射操作。当将来自主机102的取消映射命令被提供给控制器130时,取消映射管理器146可以在处理器134的控制下,接收针对从主机102提供的取消映射命令的目标逻辑地址。随后,取消映射管理器146可以将与每个目标逻辑地址相对应的映射数据的整体大小与可以被预先确定的阈值进行比较。当映射数据的整体大小大于或等于阈值时,取消映射管理器146可以将包括映射数据的多个映射段分类为多个区域。取消映射管理器146可以针对每个区域以不同的方式来执行对映射段或映射数据进行取消映射的取消映射操作。尽管图1图示了取消映射管理器146是与处理器134分离的部件,但是取消映射管理器146可以根据设计方案被包括在处理器134中。

此外,尽管在附图中未示出,但是控制器130可以进一步包括纠错码(ECC)部件和功率管理单元(PMU)。

ECC部件可以纠正在存储器装置150中处理的数据的错误位,并且包括ECC编码器和ECC解码器。

ECC编码器可以通过对待编程到存储器装置150中的数据执行纠错编码来生成具有奇偶校验位的数据,并且具有奇偶校验位的数据可以被存储在存储器装置150中。当读取存储在存储器装置150中的数据时,ECC解码器检测和纠正从存储器装置150读取的数据中包括的错误。

ECC部件可以通过诸如低密度奇偶校验(LDPC)码、Bose-Chaudhri-Hocquenghem(BCH)码、turbo码、Reed-Solomon码、卷积码、递归系统码(RSC)、网格编码调制(TCM)和块编码调制(BCM)的编码调制来执行纠错。然而,ECC部件不限于任何特定的纠错技术或结构。ECC部件可以包括用于纠错的任何和所有电路、模块、系统或装置。

PMU可以提供和管理控制器130的功率。

参考图2至图4详细描述根据本发明的实施例的存储器系统的存储器装置。

图2是图示存储器装置150的示意图。图3是图示存储器装置150中的存储器块的存储器单元阵列的示例性配置的电路图。图4是图示存储器装置150的示例性三维(3D)结构的示意图。

参考图2,存储器装置150可以包括多个存储器块BLOCK0(210)、BLOCK1(220)、BLOCK2(230)以及BLOCKN-1(240)。存储器块210、220、230和240中的每一个可以包括多个页,例如,2M个页,页的数目可以根据电路设计而变化。例如,在一些应用中,每个存储器块可以包括M个页。每个页可以包括耦合到字线WL的多个存储器单元。

存储器装置150不仅可以包括多级单元(MLC)存储器块(每个MLC存储器块包括由能够在一个存储器单元中存储两位数据的存储器单元实现的多个页),而且还可以包括三级单元(TLC)存储器块(每个TLC存储器块包括由能够在一个存储器单元中存储三位数据的存储器单元实现的多个页)、四级单元(QLC)存储器块(每个QLC存储器块包括由能够在一个存储器单元中存储四位数据的存储器单元实现的多个页)和/或更高级别的单元存储器块(每个存储器块包括由能够在一个存储器单元中存储五位或更多位数据的存储器单元实现的多个页)。

根据本发明的实施例,存储器装置150被描述为非易失性存储器,诸如闪存,例如NAND闪存。然而,存储器装置150可以被实现为相变随机存取存储器(PCRAM)、电阻式随机存取存储器(RRAM或ReRAM)、铁电随机存取存储器(FRAM)、自旋转移力矩磁性随机存取存储器(STT-RAM或STT-MRAM)中的任一个。

存储器块210、220、230、…240可以通过编程操作来存储从主机102传输的数据,并且通过读取操作将存储在其中的数据传输至主机102。

参考图3,可以与存储器系统110的存储器装置150中的多个存储器块152至156中的任一个相对应的存储器块330可以包括耦合到多个对应位线BL0至BLm-1的多个单元串340。每一列的单元串340可以包括一个或多个漏极选择晶体管DST和一个或多个源极选择晶体管SST。在漏极选择晶体管DST和源极选择晶体管SST之间,多个存储器单元或存储器单元晶体管MC0至MCn-1可以串联耦合。在一个实施例中,存储器单元MC0至MCn-1中的每一个可以由能够存储多个位的数据信息的MLC来体现。单元串340中的每一个可以电耦合到多个位线BL0至BLm-1之中的对应位线。例如,如图3所示,第一单元串耦合到第一位线BL0,并且最后单元串耦合到最后位线BLm-1。为了参考,在图3中,“DSL”表示漏极选择线、“SSL”表示源极选择线、且“CSL”表示公共源极线。

尽管图3图示了NAND闪存单元,但是本发明不限于该方式。注意,存储器单元可以是NOR闪存单元、或者是包括组合在其中的两个或更多个种类的存储器单元的混合闪存单元。此外,应注意,存储器装置150可以是包括导电浮栅作为电荷存储层的闪存装置或包括绝缘层作为电荷存储层的电荷捕获闪存(CTF)装置。

存储器装置150可以进一步包括电压供应310,电压供应310根据操作模式将包括编程电压、读取电压和通过电压的字线电压提供给字线。电压供应310的电压生成操作可以由控制电路(未示出)控制。在控制电路的控制下,电压供应310可以选择存储器单元阵列的存储器块(或扇区)中的一个,选择所选择的存储器块的字线中的一个并且根据需要将字线电压提供给所选择的字线和未选择的字线。

存储器装置150可以包括由控制电路控制的读取和写入(读取/写入)电路320。在验证/正常读取操作期间,读取/写入电路320可以作为用于从存储器单元阵列读取数据的感测放大器进行操作。在编程操作期间,读取/写入电路320可以作为用于根据待存储在存储器单元阵列中的数据来驱动位线的写入驱动器进行操作。在编程操作期间,读取/写入电路320可以从缓冲器(未示出)接收待存储到存储器单元阵列中的数据,并且根据所接收的数据来驱动位线。读取/写入电路320可以包括分别对应于列(或位线)或列对(或位线对)的多个页缓冲器322至326,并且页缓冲器322至326中的每一个可以包括多个锁存器(未示出)。

存储器装置150可以由二维(2D)或三维(3D)存储器装置体现。特别地,如图4所示,存储器装置150可以由具有3D堆叠结构的非易失性存储器装置来体现。当存储器装置150具有3D结构时,多个存储器块BLOCK0至BLOCKN-1中的每一个也可以具有3D结构。

存储器装置150中包括的每个存储器块330可以包括在第二方向上延伸的多个NAND串NS、以及在第一方向和第三方向上延伸的多个NAND串NS(未示出)。每个NAND串NS可以耦合到位线BL、至少一个漏极选择线DSL、至少一个源极选择线SSL、多个字线WL、至少一个虚设字线DWL(未示出)和公共源极线CSL,并且每个NAND串NS可以包括多个晶体管结构。

简而言之,存储器装置150的每个存储器块330可以耦合到多个位线BL、多个漏极选择线DSL、多个源极选择线SSL、多个字线WL、多个虚设字线DWL和多个公共源极线CSL,并且每个存储器块330可以包括多个NAND串NS。此外,在每个存储器块330中,一个位线BL可以耦合到多个NAND串NS,以在一个NAND串NS中实现多个晶体管。而且,每个NAND串NS的漏极选择晶体管DST可以耦合到对应的位线BL,并且每个NAND串NS的源极选择晶体管SST可以耦合到公共源极线CSL。存储器单元MC可以设置在每个NAND串NS的漏极选择晶体管DST和源极选择晶体管SST之间。换言之,可以在存储器装置150的每个存储器块330中实现多个存储器单元。

如参考图1所描述,存储器144可以在处理器134的控制下使用表来管理每个映射段和每个映射数据。例如,如图5A和图5B所示,关于映射段的信息可以存储在第一表510中,并且关于映射数据的信息可以存储在第二表530中。参考图5A至图5B来描述第一表510和第二表530。

图5A是图示根据实施例的第一表510的结构的图。

参考图5A,第一表510可以表示映射段与包括多个逻辑地址的逻辑地址组之间的映射关系(第一映射)。多个第一映射信息可以存储在第一表510中。第一映射信息可以包括映射段、逻辑地址或逻辑块地址(LBA)以及第一标志信息(Flag)。第一标志信息可以指示第一映射是否被执行。第一表510指示具有第一标志信息“M”的第一映射段与包括第1至第K逻辑地址LBA<1:K>的第一逻辑组进行映射。此外,第一表510指示具有第一标志信息“U”的第二映射段未与包括第(K+1)至第2K逻辑地址LBA<K+1:2K>的第二逻辑地址进行映射。类似地,第一表510针对其余映射段中的每一个而指示是否与对应逻辑地址进行映射。

图5B是图示根据实施例的第二表530的结构的图。

参考图5B,第二表530可以表示逻辑地址信息和物理地址信息之间的映射关系(第二映射)。多个第二映射信息可以存储在第二表530中。第二映射信息可以包括逻辑地址(LBA)、物理地址(PBA)和第二标志信息(Flag)。第二标志信息可以指示第二映射是否被执行。例如,第二表530可以指示具有第二标志信息“M”的第1逻辑地址LBA 1与第56物理地址PBA56进行映射。此外,第二表530可以指示具有第二标志信息“U”的第三逻辑地址LBA3没有与第11物理地址PBA 11进行映射。类似地,第二表530针对其余逻辑地址中的每一个而指示是否与对应的物理地址进行映射。

第二表530基于映射段表示第二映射信息。第二表530表示与第一映射段进行映射的第1至第K逻辑地址中的每一个的第二映射信息。虽然图5B仅图示与第一映射段映射的第1至第K逻辑地址中的每一个的第二映射信息,但是这仅是示例,并且第二表530可以针对多个映射段中的每一个来被配置。

图5A和图5B中所示的第一表510和第二表530可以在处理器134的控制下分别存储在存储器装置150中。

再次参考图1,处理器134可以将第一表510和第二表530从存储器装置150加载到存储器144中,以对从主机102提供的取消映射命令进行处理。

取消映射管理器146可以参考存储在存储器144中的第一表510和第二表530来处理从主机102提供的取消映射命令。取消映射管理器146可以根据从主机102提供的取消映射命令来执行对第一映射和/或第二映射进行取消映射的取消映射操作。特别地,根据本实施例的存储器系统110可以针对多个逻辑地址根据取消映射命令来有效地执行取消映射操作。下面详细描述根据实施例的存储器系统110的操作。

图6A至图6E是图示根据实施例的存储器系统110的操作的图。例如,假设每个映射段与100个逻辑地址进行映射。此外,假设第一映射段与第1至第100逻辑地址进行映射,并且第二映射段与第101至第200逻辑地址进行映射。以相同的方式,假设第三映射段至第十一映射段中的每一个与100个逻辑地址的对应组进行映射。假设针对从主机102提供的取消映射命令的映射数据的整体大小大于或等于可以被预先确定的阈值。以下描述的存储器系统110的操作仅是一个示例。

参考图6A,主机102可以向存储器系统110提供针对第10至第1050逻辑地址LBA<10:1050>的取消映射命令。当从主机102接收取消映射命令时,控制器130的处理器134可以从存储器装置150加载与目标逻辑地址相关联的第一映射信息和第二映射信息。目标逻辑地址指示第10至第1050逻辑地址LBA<10:1050>。换言之,处理器134可以从存储器装置150读取关于第一映射段至第十一映射段的第一映射信息以及关于第10至第1050逻辑地址LBA<10:1050>中的每个逻辑地址的第二映射信息,并且将第一映射信息和第二映射信息存储在存储器144中。另外,处理器134可以从存储器装置150加载分别存储有第一映射信息和第二映射信息的第一表610和第二表630。特别地,即使第一映射信息和第二映射信息已存储在存储器144中,处理器134也可以从存储器装置150读取第一映射信息和第二映射信息,并且将所读取的信息再次存储在存储器144中。由于存储在存储器装置150中的第一映射信息和第二映射信息是最近更新的信息,当接收取消映射命令时,处理器134可以从存储器装置150加载第一映射信息和第二映射信息。

参考图6B,取消映射管理器146可以将从主机102提供的取消映射命令的映射数据的整体大小与阈值进行比较。阈值可以根据系统或处理考虑来设置。当针对取消映射命令的映射数据的整体大小大于或等于阈值时,取消映射管理器146可以基于存储在存储器144中的第一表610,将多个映射段分类为第一区域(例如,头部区域)、第二区域(例如,主体区域)和第三区域(例如,尾部区域)。

具体地,取消映射管理器146可以将映射段分类为第一区域或第三区域。第一区域或第三区域中的映射段可以与其中多个逻辑地址中只有一些是目标逻辑地址的逻辑组进行映射。另一方面,取消映射管理器146可以将映射段分类到第二区域中。第二区域中的映射段可以与其中所有逻辑地址都是目标逻辑地址的逻辑组进行映射。例如,取消映射管理器146可以将第一映射片段分类到第一区域(或头部区域)中。第一映射段可以与包括第10逻辑地址LBA 10(其是目标逻辑地址的起始逻辑地址)的逻辑组进行映射。取消映射管理器146可以将第11映射段分类到第三区域(或尾部区域)中。第11映射段可以与包括第1050逻辑地址LBA 1050(其是目标逻辑地址的最后逻辑地址)的逻辑组进行映射。取消映射管理器146可以将第二至第十映射段分类到第二区域(或主体区域)中。

取消映射管理器146可以以不同的方式在第一区域至第三区域上执行取消映射操作。

参考图6C,取消映射管理器146可以针对多个逻辑地址(其被包括在与第一区域中的第一映射段进行映射的逻辑组中)之中的目标逻辑地址的第二映射执行取消映射操作。在图6C中,第二表630_1指示在执行取消映射操作之前的第二表630的状态,并且第二表630_3指示在执行取消映射操作之后的第二表630的状态。具体地,与第一映射段映射的逻辑组中包括的多个逻辑地址之中的目标逻辑地址是第10逻辑地址LBA 10至第100逻辑地址LBA 100。取消映射管理器146可以根据取消映射命令,将第10逻辑地址LBA 10至第100逻辑地址LBA 100中的每个逻辑地址的第二映射独立地取消映射。取消映射管理器146可以将与存储在第二表630_3中的第10逻辑地址LBA 10至第100逻辑地址LBA 100中的每一个相对应的第二标志信息从“M”更新为“U”。处理器134可以在存储器装置150中存储第二表630_3,其中存储了关于第10逻辑地址LBA 10至第100逻辑地址LBA 100中的每一个的取消映射信息。

参考图6D,取消映射管理器146可以对第二区域中的第二映射段至第十映射段中的每一个的第一映射执行取消映射操作。在图6D中,第一表610_1指示在执行取消映射操作之前的第一表610的状态,并且第一表610_3指示在执行取消映射操作之后的第一表610的状态。与第二区域中的多个映射段中的每一个进行映射的逻辑组中包括的多个逻辑地址均被包括在目标逻辑地址中。换言之,映射到第二映射段至第十映射段中的每一个的逻辑组可以包括作为目标逻辑地址中的一些的第101至第1000逻辑地址LBA<101:1000>。因此,取消映射管理器146不像第一区域那样针对第二映射执行取消映射操作。

在该情况下,取消映射管理器146可以对第二映射段至第十映射段中的每一个的第一映射进行取消映射。换言之,取消映射管理器146可以基于第一表610_1,去除第二映射段与第101至第200逻辑地址LBA<101:200>之间的映射关系。另外,取消映射管理器146可以去除第三映射段与第201至第300逻辑地址LBA<201:300>之间的映射关系。以相同的方式,取消映射管理器146可以去除与第四映射段至第十映射段中的每一个进行映射的多个逻辑地址之间的映射关系。

当第101逻辑地址LBA 101至第1000逻辑地址LBA 1000中的每一个的第二映射要被取消映射时,必须执行总共900个取消映射操作。然而,取消映射管理器146可以通过对多个映射段中的每一个的第一映射进行取消映射来执行总共9个取消映射操作。

取消映射管理器146可以将第一标志信息从“M”更新为“U”。第一标志信息可以对应于存储在第一表610_1中的第二映射段至第十映射段中的每一个。处理器134可以在存储器装置150中存储第一表610_1,其中存储了关于第二映射段至第十映射段中的每一个的取消映射信息。处理器134可以在存储器装置150中不存储第二表,其中存储了与第二映射段至第十映射段中的每一个相对应的映射数据。

参考图6E,取消映射管理器146可以针对与多个逻辑地址(其被包括在与第三区域中的第十一映射段进行映射的逻辑组中)之中与目标逻辑地址相对应的逻辑地址的第二映射执行取消映射操作。在图6E中,第二表630_5指示在执行取消映射操作之前的第二表630的状态,并且第二表630_7指示在执行取消映射操作之后的第二表630的状态。具体地,与第十一映射段映射的逻辑组中包括的多个逻辑地址之中的目标逻辑地址是第1001逻辑地址LBA1001至第1050逻辑地址LBA 1050。取消映射管理器146可以根据取消映射命令,对第1001逻辑地址LBA 1001至第1050逻辑地址LBA 1050中的每一个的第二映射进行取消映射。此外,取消映射管理器146可以将第二标志信息从“M”更新为“U”。第二标志信息可以对应于存储在第二表630_5中的第1001逻辑地址LBA1001至第1050逻辑地址LBA 1050。处理器134可以在存储器装置150中存储第二表630_7,其中存储有关于第1001逻辑地址LBA 1001至第1050逻辑地址LBA 1050的取消映射信息。

尽管未示出,但是当针对从主机102提供的取消映射命令的映射数据的整体大小小于阈值时,取消映射管理器146可以执行对目标逻辑地址的第二映射进行取消映射的操作。在这种情况下,取消映射管理器146不执行对第一映射进行取消映射的操作。

图7是图示根据实施例的存储器系统110的操作过程的流程图。特别地,图7图示了存储器系统110对从主机102接收的取消映射命令进行处理的过程。

参考图7,在步骤S701中,处理器134可以从存储器装置150加载第一映射信息和第二映射信息,并且将所加载的信息存储在存储器144中。

在步骤S703中,取消映射管理器146可以将与目标逻辑地址相对应的映射数据(即,目标映射数据)的整体大小与可以被预先确定的阈值进行比较。

当确定目标映射数据的整体大小大于或等于阈值时(即,在步骤S703中为“是”),在步骤S705中,取消映射管理器146可以将多个映射段分类(或划分)到多个区域或组中。例如,取消映射管理器146可以将多个映射段分类为第一、第二和第三组或区域。如参考图6B所描述,取消映射管理器146可以将映射段分类为第一区域或第三区域。第一区域和第三区域的映射段可以与其中多个逻辑地址中的一些是目标逻辑地址的逻辑组进行映射。取消映射管理器146可以将映射段分类到第二区域中。第二区域的映射段可以与其中所有逻辑地址都是目标逻辑地址的逻辑组进行映射。

在步骤S707中,取消映射管理器146可以针对多个逻辑地址(其被包括在与第一区域和第三区域中包括的映射段进行映射的逻辑组中)之中的目标逻辑地址的第二映射执行取消映射操作。

在步骤S709中,处理器134可以在存储器装置150中存储关于在步骤S707中执行取消映射操作的每个目标逻辑地址的第二映射信息。另外,处理器134可以在存储器装置150中存储其中存储有第二映射信息的第二表。

在步骤S711中,取消映射管理器146可以针对第二区域中包括的映射段的第一映射执行取消映射操作。

在步骤S713中,处理器134可以在存储器装置150中存储关于在步骤S711中执行取消映射操作的映射段的第一映射信息。另外,处理器134可以将记录有第一映射信息的第二表存储在存储器装置150中。

当确定目标映射数据的整体大小小于阈值时(即,在步骤S703中为“否”),在步骤S715中,取消映射管理器146可以针对目标逻辑地址的第二映射执行取消映射操作。

在步骤S717中,处理器134可以在存储器装置150中存储关于在步骤S715中执行取消映射操作的每个目标逻辑地址的第二映射信息。另外,处理器134可以在存储器装置150中存储其中存储有第二映射信息的第二表。

图8至图16是示意性地图示根据各种实施例的图1至图7的数据处理系统的应用示例的图。

图8是示意性地图示根据实施例的包括存储器系统的数据处理系统的图。例如,图8示意性地图示了应用根据实施例的存储器系统的存储器卡系统6100。

参考图8,存储器卡系统6100可以包括存储器控制器6120、存储器装置6130和连接器6110。

更具体地,存储器控制器6120可以连接到由非易失性存储器(NVM)体现的存储器装置6130并且被配置为访问存储器装置6130。例如,存储器控制器6120可以被配置为控制存储器装置6130的读取、写入、擦除和后台操作。存储器控制器6120可以被配置为提供存储器装置6130和主机(未示出)之间的接口,并且驱动固件以用于控制存储器装置6130。即,存储器控制器6120可以对应于参考图1描述的存储器系统110的控制器130,并且存储器装置6130可以对应于参考图1描述的存储器系统110的存储器装置150。

因此,如图1所示,存储器控制器6120可以包括随机存取存储器(RAM)、处理器、主机接口、存储器接口和纠错部件。

存储器控制器6120可以通过连接器6110与外部装置(例如,图1的主机102)通信。例如,如参考图1所述,存储器控制器6120可以被配置为通过各种通信协议(诸如通用串行总线(USB)、多媒体卡(MMC)、嵌入式MMC(eMMC)、外围部件互连(PCI)、PCI快速(PCIe)、高级技术附件(ATA)、串行ATA、并行ATA、小型计算机系统接口(SCSI)、增强型小型磁盘接口(EDSI)、集成驱动电子装置(IDE)、火线、通用闪存(UFS)、无线保真(Wi-Fi或WiFi)和蓝牙)中的一个或多个与外部装置通信。因此,根据实施例的存储器系统和数据处理系统可以应用于有线/无线电子装置或特别地应用于移动电子装置。

存储器装置6130可以由非易失性存储器实现。例如,存储器装置6130可以由各种非易失性存储器装置(诸如可擦除可编程ROM(EPROM)、电可擦除可编程ROM(EEPROM)、NAND闪存、NOR闪存、相变RAM(PRAM)、电阻式RAM(ReRAM)、铁电式RAM(FRAM)和自旋转移力矩磁性RAM(STT-RAM))中的任一个来实现。

存储器控制器6120和存储器装置6130可以集成到单个半导体装置中。例如,存储器控制器6120和存储器装置6130可以被集成以形成固态驱动器(SSD)。而且,存储器控制器6120和存储器装置6130可以形成诸如PC卡(例如,个人计算机存储器卡国际协会(PCMCIA))、紧凑型闪存(CF)卡、智能媒体卡(例如,SM和SMC)、记忆棒、多媒体卡(例如,MMC、RS-MMC、MMCmicro和eMMC)、安全数字(SD)卡(例如,miniSD卡、microSD卡和SDHC卡)和通用闪存(UFS)的存储器卡。

图9是示意性图示根据实施例的包括存储器系统的数据处理系统6200的另一示例的图。

参考图9,数据处理系统6200可以包括具有一个或多个非易失性存储器(NVM)的存储器装置6230和用于控制存储器装置6230的存储器控制器6220。如参考图1所描述,数据处理系统6200可以用作诸如存储器卡(CF卡、SD卡等)或USB装置的存储介质。存储器装置6230可以对应于图1所示的存储器系统110中的存储器装置150,并且存储器控制器6220可以对应于图1所示的存储器系统110中的控制器130。

存储器控制器6220可以响应于主机6210的请求来控制对存储器装置6230的读取、写入或擦除操作,并且存储器控制器6220可以包括一个或多个中央处理单元(CPU)6221、缓冲存储器(诸如随机存取存储器(RAM))6222、纠错码(ECC)电路6223、主机接口6224和存储器接口(诸如NVM接口)6225。

CPU 6221可以控制存储器装置6230上的整体操作(例如,读取、写入、文件系统管理和坏页管理操作)。RAM 6222可以根据CPU 6221的控制来操作,并且用作工作存储器、缓冲存储器或高速缓存存储器。当RAM 6222用作工作存储器时,由CPU 6221处理的数据可以被临时存储在RAM 6222中。当RAM 6222用作缓冲存储器时,RAM 6222可以用于缓冲从主机6210发送到存储器装置6230或从存储器装置6230发送到主机6210的数据。当RAM 6222用作高速缓存存储器时,RAM 6222可以辅助存储器装置6230以高速操作。

ECC电路6223可以对应于图1中所示的控制器130的ECC部件138。如参考图1所述,ECC电路6223可以生成用于纠正从存储器装置6230提供的数据的故障位或错误位的纠错码(ECC)。ECC电路6223可以对提供给存储器装置6230的数据执行纠错编码,从而形成具有奇偶校验位的数据。奇偶校验位可以存储在存储器装置6230中。ECC电路6223可以对从存储器装置6230输出的数据执行纠错解码。ECC电路6223可以使用奇偶校验位来纠正错误。例如,如参考图1所述,ECC电路6223可以使用低密度奇偶校验(LDPC)码、Bose-Chaudhri-Hocquenghem(BCH)码、turbo码、Reed-Solomon码、卷积码、递归系统代码(RSC)或编码调制(诸如网格编码调制(TCM)或块编码调制(BCM))来纠正错误。

存储器控制器6220可以通过主机接口6224与主机6210交换数据,并且通过NVM接口6225与存储器装置6230交换数据。主机接口6224可以通过并行高级技术附件(PATA)总线、串行高级技术附件(SATA)总线、小型计算机系统接口(SCSI)、通用串行总线(USB)、外围部件互连快速(PCIe)或NAND接口连接到主机6210。存储器控制器6220可以利用移动通信协议(诸如无线保真(WiFi)或长期演进(LTE))具有无线通信功能。存储器控制器6220可以连接到外部装置(例如,主机6210或另一外部装置),然后向外部装置发送数据和/或从外部装置接收数据。特别地,由于存储器控制器6220被配置为通过各种通信协议中的一个或多个与外部装置通信,根据实施例的存储器系统和数据处理系统可以应用于有线和/或无线电子装置、特别是移动电子装置。

图10是示意性地图示根据实施例的包括存储器系统的数据处理系统的另一示例的图。例如,图10示意性地图示了可以应用存储器系统的固态驱动器(SSD)6300。

参考图10,SSD 6300可以包括控制器6320和包括多个非易失性存储器(NVM)的存储器装置6340。控制器6320可以对应于图1的存储器系统110中的控制器130,并且存储器装置6340可以对应于图1的存储器系统中的存储器装置150。

更具体地,控制器6320可以通过多个信道CH1至CHi连接到存储器装置6340。控制器6320可以包括一个或多个处理器6321、纠错码(ECC)电路6322、主机接口6324、缓冲存储器6325和存储器接口(例如,非易失性存储器接口)6326。

缓冲存储器6325可以临时存储从主机6310提供的数据或从被包括在存储器装置6340中的多个闪存NVM提供的数据,或者临时存储多个闪存NVM的元数据(例如,包括映射表的映射数据)。缓冲存储器6325可以由各种易失性存储器(诸如动态随机存取存储器(DRAM)、同步DRAM(SDRAM)、双倍数据速率(DDR)SDRAM、低功率DDR(LPDDR)SDRAM以及图形RAM(GRAM))或非易失性存储器(诸如铁电式RAM(FRAM)、电阻式RAM(RRAM或ReRAM)、自旋转移力矩磁性RAM(STT-MRAM)和相变RAM(PRAM))中的任一个来实现。例如,图10图示了缓冲存储器6325设置在控制器6320中。然而,缓冲存储器6325可以设置在控制器6320的外部并且与控制器6320通信。

ECC电路6322可以在编程操作期间计算待编程到存储器装置6340的数据的纠错码(ECC)值,在读取操作期间基于ECC值来对从存储器装置6340读取的数据执行纠错操作,以及在失败数据恢复操作期间对从存储器装置6340恢复的数据执行纠错操作。

主机接口6324可以提供与外部装置(例如,主机6310)的接口功能,并且非易失性存储器接口6326可以提供与通过多个信道连接的存储器装置6340的接口功能。

此外,可以提供应用图1的存储器系统110的多个SSD 6300来实现数据处理系统(例如,独立盘冗余阵列(RAID)系统)。RAID系统可以包括多个SSD 6300和用于控制多个SSD6300的RAID控制器。当RAID控制器响应于从主机6310提供的写入命令而执行编程操作时,RAID控制器可以根据多个RAID级(即,SSD 6300中的从主机6310提供的写入命令的RAID级信息)来选择一个或多个存储器系统或SSD 6300,并且将与写入命令相对应的数据输出到所选择的SSD 6300。此外,当RAID控制器响应于从主机6310提供的读取命令来执行读取命令时,RAID控制器可以根据多个RAID级(即,SSD 6300中的从主机6310提供的读取命令的RAID级信息)来选择一个或多个存储器系统或SSD 6300,并且将从所选择的SSD 6300中读取的数据提供给主机6310。

图11是示意性地图示根据实施例的包括存储器系统的数据处理系统的另一示例的图。图11示意性地图示了可以应用存储器系统的嵌入式多媒体卡(eMMC)6400。

参考图11,eMMC 6400可以包括控制器6430和由一个或多个NAND闪存实现的存储器装置6440。控制器6430可以对应于图1的存储器系统110中的控制器130,并且存储器装置6440可以对应于图1的存储器系统110中的存储器装置150。

更具体地,控制器6430可以通过多个信道连接到存储器装置6440。控制器6430可以包括一个或多个核6432、主机接口(I/F)6431和存储器接口(例如,NAND接口(I/F))6433。

核6432可以控制eMMC 6400的整体操作,主机接口6431可以在控制器6430和主机6410之间提供接口功能,并且NAND接口6433可以在存储器装置6440和控制器6430之间提供接口功能。例如,主机接口6431可以用作并行接口(例如,参考图1描述的MMC接口)。此外,主机接口6431可以用作串行接口(例如,超高速(UHS)-I和UHS-II接口)。

图12至图15是示意性图示根据一个或多个实施例的包括存储器系统的数据处理系统的其他示例的图。图12至图15示意性地图示了可以应用存储器系统的通用闪存(UFS)系统。

参考图12至图15,UFS系统6500、6600、6700和6800可以分别包括主机6510、6610、6710和6810、UFS装置6520、6620、6720、和6820以及UFS卡6530、6630、6730和6830。主机6510、6610、6710和6810可以用作有线和/或无线电子装置或者特别是移动电子装置的应用处理器,UFS装置6520、6620、6720和6820可以用作嵌入式UFS装置。UFS卡6530、6630、6730和6830可以用作外部嵌入式UFS装置或可移除UFS卡。

相应UFS系统6500、6600、6700和6800中的主机6510、6610、6710和6810、UFS装置6520、6620、6720和6820以及UFS卡6530、6630、6730和6830可以通过UFS协议与外部装置(例如,有线和/或无线电子装置或者特别是移动电子装置)通信。UFS装置6520、6620、6720和6820以及UFS卡6530、6630、6730和6830可以由图1所示的存储器系统110来体现。例如,在UFS系统6500、6600、6700和6800中,UFS装置6520、6620、6720和6820可以以参考图9至图11所描述的数据处理系统6200、SSD 6300或eMMC 6400的形式来体现,并且UFS卡6530、6630、6730和6830可以以参考图8描述的存储器卡系统6100的形式来体现。

此外,在UFS系统6500、6600、6700和6800中,主机6510、6610、6710和6810、UFS装置6520、6620、6720和6820以及UFS卡6530、6630、6730和6830可以通过UFS接口(例如,MIPI(移动行业处理器接口)中的MIPI M-PHY和MIPI UniPro(统一协议))彼此通信。此外,UFS装置6520、6620、6720和6820以及UFS卡6530、6630、6730和6830可以通过除了UFS协议以外的各种协议(例如,通用存储总线(USB)闪存驱动器(UFD)、多媒体卡(MMC)、安全数字(SD)、小型SD和微型SD)彼此通信。

在图12中所示的UFS系统6500中,主机6510、UFS装置6520和UFS卡6530中的每一个可以包括UniPro。主机6510可以执行切换操作以便与UFS装置6520和UFS卡6530通信。特别地,主机6510可以通过链路层切换(例如,以UniPro的L3切换)与UFS装置6520或UFS卡6530通信。UFS装置6520和UFS卡6530可以通过主机6510的UniPro处的链路层切换彼此通信。在图12中,通过示例图示了一个UFS装置6520和一个UFS卡6530连接到主机6510的配置。然而,多个UFS装置和UFS卡可以并联或以星形的形式连接到主机6510,并且多个UFS卡可以并联或以星形的形式连接到UFS装置6520,或者以串联或以链的形式连接到UFS装置6520。

在图13所示的UFS系统6600中,主机6610、UFS装置6620和UFS卡6630中的每一个可以包括UniPro,并且主机6610可以通过执行切换操作的切换模块6640(例如,通过以UniPro执行链路层切换(例如,L3切换)的切换模块6640)与UFS装置6620或UFS卡6630通信。UFS装置6620和UFS卡6630可以通过UniPro处的切换模块6640的链路层切换来彼此通信。在图13中,通过示例的方式图示了一个UFS装置6620和一个UFS卡6630连接到切换模块6640的配置。然而,多个UFS装置和UFS卡可以并联或以星形的形式连接到切换模块6640,并且多个UFS卡可以串联或以链的形式连接到UFS装置6620。

在图14所示的UFS系统6700中,主机6710、UFS装置6720和UFS卡6730中的每一个可以包括UniPro。主机6710可以通过执行切换操作的切换模块6740(例如,通过以UniPro执行链路层切换(例如,L3切换)的切换模块6740)与UFS装置6720或UFS卡6730通信。UFS装置6720和UFS卡6730可以通过UniPro处的切换模块6740的链路层切换来彼此通信,并且切换模块6740可以与UFS装置6720作为一个模块集成在UFS装置6720内部或外部。在图14中,通过示例的方式图示了一个UFS装置6720和一个UFS卡6730连接到切换模块6740的配置。然而,各自包括切换模块6740和UFS装置6720的多个模块可以并联或以星形的形式连接到主机6710,或者串联或以链的形式彼此连接。此外,多个UFS卡可以并联或以星形的形式连接到UFS装置6720。

在图15所示的UFS系统6800中,主机6810、UFS装置6820和UFS卡6830中的每一个可以包括M-PHY和UniPro。UFS装置6820可以执行切换操作,以便与主机6810和UFS卡6830通信。特别地,UFS装置6820可以通过用于与主机6810通信的M-PHY和UniPro模块和用于与UFS卡6830通信的M-PHY和UniPro模块之间的切换操作(例如,通过目标标识符(ID)切换操作)与主机6810或UFS卡6830通信。主机6810和UFS卡6830可以通过在UFS装置6820的M-PHY和UniPro模块之间的目标ID切换来彼此通信。在图15中,通过示例的方式图示了一个UFS装置6820连接到主机6810并且一个UFS卡6830连接到UFS装置6820的配置。但是,多个UFS装置可以并联或以星形的形式连接到主机6810,或者串联或以链的形式连接到主机6810,并且多个UFS卡可以并联或以星形的形式连接到UFS装置6820,或者串联或以链的形式连接到UFS装置6820。

图16是示意性地图示根据实施例的包括存储器系统的数据处理系统的另一示例的图。图16是示意性地图示可以应用存储器系统的用户系统6900的图。

参考图16,用户系统6900可以包括用户接口6910、存储器模块6920、应用处理器6930、网络模块6940和存储模块6950。

更具体地,应用处理器6930可以驱动用户系统6900中包括的部件(例如,操作系统OS)并且包括对用户系统6900中包括的部件进行控制的控制器、接口和图形引擎。应用处理器6930可以被设置为片上系统(SoC)。

存储器模块6920可以用作用户系统6900的主存储器、工作存储器、缓冲存储器或高速缓存存储器。存储器模块6920可以包括易失性随机存取存储器(RAM)(诸如动态RAM(DRAM)、同步DRAM(SDRAM)、双倍数据速率(DDR)SDRAM、DDR2 SDRAM、DDR3 SDRAM、LPDDRSDARM、LPDDR2 SDRAM或LPDDR3 SDRAM)或非易失性RAM(诸如相变RAM(PRAM)、电阻式RAM(ReRAM)、磁阻式RAM(MRAM)或铁电式RAM(FRAM))。例如,可以基于堆叠封装(PoP)来封装和安装应用处理器6930和存储器模块6920。

网络模块6940可以与外部装置通信。例如,网络模块6940不仅可以支持有线通信,而且可以支持各种无线通信协议(诸如码分多址(CDMA)、全球移动通信系统(GSM)、宽带CDMA(WCDMA)、CDMA-2000、时分多址(TDMA)、长期演进(LTE)、全球微波接入互通(Wimax)、无线局域网(WLAN)、超宽带(UWB)、蓝牙、无线显示(WI-DI)),从而与有线/无线电子装置或特别是移动电子装置进行通信。因此,根据本发明的实施例,存储器系统和数据处理系统可以应用于有线/无线电子装置。网络模块6940可以被包括在应用处理器6930中。

存储模块6950可以存储数据(例如,从应用处理器6930接收的数据),然后可以将所存储的数据传输到应用处理器6930。存储模块6950可以由诸如相变RAM(PRAM)、磁性RAM(MRAM)、电阻式RAM(ReRAM)、NAND闪存、NOR闪存和3D NAND闪存的非易失性半导体存储器装置来实现,并且被设置为用户系统6900的可移除存储介质(诸如存储器卡或外部驱动器)。存储模块6950可以对应于参考图1描述的存储器系统110。此外,存储模块6950可以被实现为以上参考图10至图15描述的SSD、eMMC和UFS。

用户接口6910可以包括用于向应用处理器6930输入数据或命令或向外部装置输出数据的接口。例如,用户接口6910可以包括用户输入接口(诸如键盘、小键盘、按钮、触摸面板、触摸屏、触摸板、触摸球、相机、麦克风、陀螺仪传感器、振动传感器和压电元件)以及用户输出接口(诸如液晶显示器(LCD)、有机发光二极管(OLED)显示装置、有源矩阵OLED(AMOLED)显示装置、LED、扬声器和电机)。

此外,当图1的存储器系统110应用于用户系统6900的移动电子装置时,应用处理器6930可以控制移动电子装置的整体操作,并且网络模块6940可以用作用于控制与外部装置的有线和/或无线通信的通信模块。用户接口6910可以在移动电子装置的显示/触摸模块上显示由应用处理器6930处理的数据或者支持从触摸面板接收数据的功能。

根据本发明实施例的存储器系统可以有效地处理针对大容量映射数据的取消映射命令,从而提高了存储器系统的取消映射性能。

虽然已关于特定实施例图示和描述了本发明,但是根据本公开,对于本领域技术人员而言显而易见的是,在不脱离如所附权利要求限定的本发明的精神和范围的情况下,可以进行各种改变和修改。

Claims (20)

1.一种存储器系统,包括:

存储器装置,适于存储与针对取消映射命令的目标逻辑地址相关联的第一映射信息和第二映射信息;以及

控制器,适于从所述存储器装置加载所述第一映射信息和所述第二映射信息,将与所述目标逻辑地址相对应的目标映射数据的大小与阈值进行比较,基于所述比较的结果来将与包括所述目标逻辑地址中的一个或多个的多个目标逻辑组分别映射的多个映射段分类到多个区域,并且对所述多个区域中包括的所述映射段中的每一个执行取消映射操作,

其中所述第一映射信息包括关于所述多个映射段与所述多个目标逻辑组之间的映射关系的信息,并且所述第二映射信息包括关于所述目标逻辑地址与对应物理地址之间的映射关系的信息。

2.根据权利要求1所述的存储器系统,其中所述控制器包括:

存储器,适于存储所述第一映射信息和所述第二映射信息;

处理器,适于将所述第一映射信息和所述第二映射信息从所述存储器装置加载到所述存储器中;以及

取消映射管理器,适于将所述目标映射数据的所述大小与所述阈值进行比较,基于所述比较的结果来将所述多个映射段分类到所述多个区域,并且对所述多个区域中的所述映射段中的每一个的所述第一映射信息执行所述取消映射操作。

3.根据权利要求2所述的存储器系统,其中当所述目标映射数据的所述大小大于或等于所述阈值时,所述取消映射管理器将与其中所述多个逻辑地址中的仅一些是所述目标逻辑地址的第一逻辑组映射的映射段分类到第一区域和第三区域,并且将与其中所有逻辑地址是所述目标逻辑地址的第二逻辑组映射的映射段分类到第二区域。

4.根据权利要求3所述的存储器系统,其中所述取消映射管理器将与包括所述第一逻辑组中的所述目标逻辑地址的起始逻辑地址的逻辑组映射的映射段分类到所述第一区域,并且将与包括所述第一逻辑组中的所述目标逻辑地址的最后逻辑地址的逻辑组映射的映射段分类到所述第三区域。

5.根据权利要求3所述的存储器系统,其中所述取消映射管理器对所述第二区域中的所述映射段中的每一个的所述第一映射信息执行第一取消映射操作,并且对与所述第一区域的相应映射段和所述第三区域的相应映射段映射的逻辑组的所述目标逻辑地址的所述第二映射信息执行第二取消映射操作。

6.根据权利要求5所述的存储器系统,其中在所述第一取消映射操作被执行之后,所述处理器将所述第一映射信息存储在所述存储器装置中。

7.根据权利要求5所述的存储器系统,其中在所述第二取消映射操作被执行之后,所述处理器将所述第二映射信息存储在所述存储器装置中。

8.根据权利要求2所述的存储器系统,其中当所述目标映射数据的整体大小小于所述阈值时,所述取消映射管理器对所述目标逻辑地址的所述第二映射信息执行第三取消映射操作。

9.根据权利要求8所述的存储器系统,其中在所述第三取消映射操作被执行之后,所述处理器将所述第二映射信息存储在所述存储器装置中。

10.根据权利要求2所述的存储器系统,其中所述存储器存储其中存储有所述第一映射信息的第一表和其中存储有所述第二映射信息的第二表。

11.一种存储器系统的操作方法,所述操作方法包括:

接收取消映射命令;

从存储器装置加载与针对所述取消映射命令的目标逻辑地址相关联的第一映射信息和第二映射信息,并且将所述第一映射信息和所述第二映射信息存储在存储器中;

将对应于所述目标逻辑地址的目标映射数据的大小与阈值进行比较;

基于所述比较的结果,将与包括所述目标逻辑地址中的一个或多个的多个目标逻辑组分别映射的多个映射段分类到多个区域;以及

对所述多个区域中的任一个中包括的每个映射段执行取消映射操作,

其中所述第一映射信息包括关于所述多个映射段与所述多个目标逻辑组之间的映射关系的信息,并且所述第二映射信息包括关于所述目标逻辑地址与对应物理地址之间的映射关系的信息。

12.根据权利要求11所述的操作方法,其中将所述多个映射段分类到所述多个区域包括:当所述目标映射数据的所述大小大于或等于所述阈值时,将与所述目标逻辑组映射的所述多个映射段分类到所述多个区域。

13.根据权利要求12所述的操作方法,其中将所述多个映射段分类到所述多个区域包括:在所述多个映射段之中,将与其中多个逻辑地址中的仅一些是所述目标逻辑地址的第一逻辑组映射的映射段分类到第一区域和第三区域,并且将与其中所有逻辑地址是所述目标逻辑地址的第二逻辑组映射的映射段分类到第二区域。

14.根据权利要求13所述的操作方法,其中将所述多个映射段分类到所述多个区域包括:

将与包括所述第一逻辑组中的所述目标逻辑地址的起始逻辑地址的逻辑组映射的映射段分类到所述第一区域,以及

将与包括所述第一逻辑组中的所述目标逻辑地址的最后逻辑地址的逻辑组映射的映射段分类到所述第三区域。

15.根据权利要求13所述的操作方法,其中执行所述取消映射操作包括:

对所述第二区域中的所述映射段中的每一个的所述第一映射信息进行第一取消映射操作;以及

对与所述第一区域的相应映射段和所述第三区域的相应映射段映射的逻辑组中的所述目标逻辑地址的所述第二映射信息执行第二取消映射操作。

16.根据权利要求15所述的操作方法,进一步包括:在执行所述第一取消映射操作之后,将所述第一映射信息存储在所述存储器装置中。

17.根据权利要求15所述的操作方法,进一步包括:在执行所述第二取消映射操作之后,将所述第二映射信息存储在所述存储器装置中。

18.根据权利要求11所述的操作方法,其中执行所述取消映射操作包括:当所述目标映射数据的所述大小小于所述阈值时,对所述目标逻辑地址的所述第二映射信息执行第三取消映射操作。

19.根据权利要求18所述的操作方法,进一步包括:在执行所述第三取消映射操作之后,将所述第二映射信息存储在所述存储器装置中。

20.一种存储器系统,包括:

存储器装置,适于存储第一映射信息和第二映射信息,所述第一映射信息包括关于多个映射段与多个逻辑组之间的映射的信息,每个逻辑组包括一个或多个逻辑地址,并且所述第二映射信息包括关于多个逻辑地址与多个物理地址之间的映射的信息;以及

控制器,包括存储器,适于:

将与取消映射命令相关联的所述第一映射信息和所述第二映射信息从所述存储器装置加载到所述存储器中;

将包括第一映射段、最后映射段和其余映射段的所述多个映射段划分到包括所述第一映射段的第一组、包括所述其余映射段的第二组和包括所述最后映射段的第三组;以及

将针对所述第一组和所述第三组的所述第二映射信息取消映射,并且将针对所述第二组的所述第一映射信息取消映射。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2018-0163281 | 2018-12-17 | ||

| KR1020180163281A KR102761223B1 (ko) | 2018-12-17 | 2018-12-17 | 메모리 시스템 및 그것의 동작방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN111324552A CN111324552A (zh) | 2020-06-23 |

| CN111324552B true CN111324552B (zh) | 2023-03-03 |

Family

ID=71072566

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201911213480.9A Active CN111324552B (zh) | 2018-12-17 | 2019-12-02 | 存储器系统及其操作方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US11016881B2 (zh) |

| KR (1) | KR102761223B1 (zh) |

| CN (1) | CN111324552B (zh) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11733918B2 (en) * | 2020-07-28 | 2023-08-22 | Samsung Electronics Co., Ltd. | Systems and methods for processing commands for storage devices |

| US11755490B2 (en) * | 2020-12-15 | 2023-09-12 | Micron Technology, Inc. | Unmap operation techniques |

| US20230013048A1 (en) * | 2021-07-16 | 2023-01-19 | International Business Machines Corporation | Handling partition data |

| US11711488B2 (en) * | 2021-08-31 | 2023-07-25 | Micron Technology, Inc. | Configurable storage granularity for video/image recording |

| CN115904226B (zh) | 2022-10-10 | 2025-10-28 | 阿里巴巴(中国)有限公司 | 固态驱动器、设备及固态驱动器的操作方法 |

| EP4495783A4 (en) * | 2023-05-31 | 2025-09-10 | Yangtze Memory Tech Co Ltd | MEMORY SYSTEM, ITS OPERATING METHOD, STORAGE MEDIUM AND MEMORY CONTROL DEVICE |

| CN117234959A (zh) * | 2023-08-29 | 2023-12-15 | 中电云计算技术有限公司 | 一种数据处理方法、装置、设备及存储介质 |

| CN117891416B (zh) * | 2024-03-18 | 2024-05-14 | 厦门大学 | 基于scsi协议的取消映射操作优化方法、装置及可读介质 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4758951A (en) * | 1985-04-09 | 1988-07-19 | Tektronix, Inc. | Method for translating virtual addresses into real addresses |

| WO2015048140A1 (en) * | 2013-09-24 | 2015-04-02 | Intelligent Intellectual Property Holdings 2 Llc | Systems and methods for storage collision management |

| CN107220184A (zh) * | 2017-05-10 | 2017-09-29 | 杭州宏杉科技股份有限公司 | 一种lun存储单元的管理方法及装置 |

| CN108073470A (zh) * | 2016-11-07 | 2018-05-25 | 三星电子株式会社 | 执行地址映射表的纠错的存储器系统及其控制方法 |

| CN108694128A (zh) * | 2017-04-10 | 2018-10-23 | 桑迪士克科技有限责任公司 | 存储器系统中的使用单次地址更新的折叠操作 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7552308B2 (en) | 2006-04-04 | 2009-06-23 | International Business Machines Corporation | Method and apparatus for temporary mapping of executable program segments |

| US8417912B2 (en) * | 2010-09-03 | 2013-04-09 | International Business Machines Corporation | Management of low-paging space conditions in an operating system |

| US9069657B2 (en) | 2011-12-12 | 2015-06-30 | Apple Inc. | LBA bitmap usage |

| US9323667B2 (en) | 2012-04-12 | 2016-04-26 | Violin Memory Inc. | System and method for managing trim operations in a flash memory system using mapping tables and block status tables |

| US9558125B2 (en) * | 2014-10-27 | 2017-01-31 | Sandisk Technologies Llc | Processing of un-map commands to enhance performance and endurance of a storage device |

| JP2018116329A (ja) * | 2017-01-16 | 2018-07-26 | 富士通株式会社 | ストレージ制御装置、およびストレージ制御プログラム |

| US10459636B2 (en) * | 2017-03-24 | 2019-10-29 | Sandisk Technologies Llc | System and method for managing data in non-volatile memory systems having multiple mapping layers |

| US11182106B2 (en) * | 2018-03-21 | 2021-11-23 | Arm Limited | Refresh circuit for use with integrated circuits |

| KR20200019430A (ko) * | 2018-08-14 | 2020-02-24 | 에스케이하이닉스 주식회사 | 컨트롤러 및 그것의 동작방법 |

| US10909030B2 (en) * | 2018-09-11 | 2021-02-02 | Toshiba Memory Corporation | Enhanced trim command support for solid state drives |

| KR102679967B1 (ko) * | 2018-09-12 | 2024-07-02 | 에스케이하이닉스 주식회사 | 메모리 시스템에서의 유효 데이터 관리 방법 및 장치 |

| KR102711044B1 (ko) * | 2018-09-20 | 2024-09-27 | 에스케이하이닉스 주식회사 | 메모리 시스템에서의 유효 데이터 체크 방법 및 장치 |

| US10901649B2 (en) * | 2019-01-23 | 2021-01-26 | Vmware, Inc. | Storage reclamation for distributed storage systems |

-

2018

- 2018-12-17 KR KR1020180163281A patent/KR102761223B1/ko active Active

-

2019

- 2019-11-14 US US16/684,037 patent/US11016881B2/en active Active

- 2019-12-02 CN CN201911213480.9A patent/CN111324552B/zh active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4758951A (en) * | 1985-04-09 | 1988-07-19 | Tektronix, Inc. | Method for translating virtual addresses into real addresses |

| WO2015048140A1 (en) * | 2013-09-24 | 2015-04-02 | Intelligent Intellectual Property Holdings 2 Llc | Systems and methods for storage collision management |

| CN108073470A (zh) * | 2016-11-07 | 2018-05-25 | 三星电子株式会社 | 执行地址映射表的纠错的存储器系统及其控制方法 |

| CN108694128A (zh) * | 2017-04-10 | 2018-10-23 | 桑迪士克科技有限责任公司 | 存储器系统中的使用单次地址更新的折叠操作 |

| CN107220184A (zh) * | 2017-05-10 | 2017-09-29 | 杭州宏杉科技股份有限公司 | 一种lun存储单元的管理方法及装置 |

Non-Patent Citations (2)

| Title |

|---|

| Using Memory Mapping to Support Cactus Stacks in Work-Stealing Runtime Systems;I-Ting Angelina Lee .etc;《2010 19th International Conference on Parallel Architectures and Compilation Techniques(PACT)》;20100915;1-10 * |

| 片上多核处理器共享末级缓存动静结合地址映射机制;曹非;《计算机科学》;20120815;第39卷(第8期);304-310 * |

Also Published As

| Publication number | Publication date |

|---|---|

| US11016881B2 (en) | 2021-05-25 |

| KR20200074647A (ko) | 2020-06-25 |

| US20200192792A1 (en) | 2020-06-18 |

| CN111324552A (zh) | 2020-06-23 |

| KR102761223B1 (ko) | 2025-02-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107562649B (zh) | 存储器系统及其操作方法 | |

| CN111324552B (zh) | 存储器系统及其操作方法 | |

| CN108268212B (zh) | 控制器及操作方法 | |

| CN109697171B (zh) | 控制器及其操作方法 | |

| CN110716883B (zh) | 存储器系统及其操作方法 | |

| CN111309638B (zh) | 存储器系统及其操作方法 | |

| CN108304141A (zh) | 存储器系统及其操作方法 | |

| CN110765029B (zh) | 控制器及用于操作该控制器的方法 | |

| CN108121665A (zh) | 存储器系统及其操作方法 | |

| CN107957849A (zh) | 存储器系统及其操作方法 | |

| CN111367827B (zh) | 存储器系统及其操作方法 | |

| CN110750207B (zh) | 存储器系统及其操作方法 | |

| CN111290970B (zh) | 存储器系统及其操作方法 | |

| CN108932203A (zh) | 数据处理系统和数据处理方法 | |

| CN111367468A (zh) | 存储器系统及其操作方法 | |

| CN110489271B (zh) | 存储器系统及其操作方法 | |

| CN107728932B (zh) | 存储器系统及其操作方法 | |

| CN110727397A (zh) | 存储器系统以及用于操作该存储器系统的方法 | |

| CN110197695B (zh) | 存储器系统及其操作方法 | |

| CN108363547A (zh) | 控制器及其操作方法 | |

| CN108665920B (zh) | 存储器系统及其操作方法 | |

| CN111273856B (zh) | 控制器以及控制器的操作方法 | |

| CN110716880B (zh) | 存储器系统及其操作方法 | |

| CN110716881B (zh) | 存储器系统及其操作方法 | |

| CN107767896B (zh) | 包括多接口的存储器系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |