CN107911092B - 一种宽带高线性度的射频发射前端电路 - Google Patents

一种宽带高线性度的射频发射前端电路 Download PDFInfo

- Publication number

- CN107911092B CN107911092B CN201710937103.4A CN201710937103A CN107911092B CN 107911092 B CN107911092 B CN 107911092B CN 201710937103 A CN201710937103 A CN 201710937103A CN 107911092 B CN107911092 B CN 107911092B

- Authority

- CN

- China

- Prior art keywords

- transistor

- drain

- resistor

- source

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000009977 dual effect Effects 0.000 claims abstract 3

- 239000003990 capacitor Substances 0.000 claims description 30

- 238000010586 diagram Methods 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 5

- 239000000306 component Substances 0.000 description 5

- 230000008859 change Effects 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 238000000034 method Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000001228 spectrum Methods 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- JJWKPURADFRFRB-UHFFFAOYSA-N carbonyl sulfide Chemical compound O=C=S JJWKPURADFRFRB-UHFFFAOYSA-N 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000008358 core component Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007123 defense Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000012886 linear function Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers

- H03G3/20—Automatic control

- H03G3/30—Automatic control in amplifiers having semiconductor devices

- H03G3/3036—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers

- H03G3/3042—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers in modulators, frequency-changers, transmitters or power amplifiers

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S7/00—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00

- G01S7/02—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00 of systems according to group G01S13/00

- G01S7/03—Details of HF subsystems specially adapted therefor, e.g. common to transmitter and receiver

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Remote Sensing (AREA)

- Amplifiers (AREA)

Abstract

本发明涉及一种宽带高线性度的射频发射前端电路,在基带和本振端口采用基于共栅放大器‑共源放大器结构的巴伦实现超宽带输入匹配,在射频端口采用基于推挽结构的A类功率放大器实现超宽带输出匹配,包括:基带单转双模块、本振单转双模块、混频器模块、可变增益放大器模块及驱动放大器模块;混频器模块采用正交双平衡吉尔伯特结构,将基带单转双模块提供的中频信号通过与本振单转双模块提供的本振信号进行电流换向调制,转换为射频差分信号提供给可变增益放大器模块。

Description

技术领域

本发明属于集成电路设计技术领域,涉及一种射频发射前端电路。

背景技术

自第二次世界大战崭露头角后,雷达的应用范围不断扩大,除了应用在导弹防御、目标侦查等军事领域,还广泛应用于气象探测、宇宙观测等民用领域,其重要性不断凸显。相比传统机械雷达,基于有源电扫阵列架构的相控阵雷达具有扫描速度快、跟踪目标多、作用距离远、分辨率高、可靠性高、环境适应力强等诸多优势,已经成为现代雷达发展的重要方向之一。除了相控阵雷达的基础结构外,实现射频收发功能的T/R组件对其性能也有着深远影响。通常一部大型相控阵雷达中包含数个阵面、每个阵面又由成百上千个T/R组件构成,对于单个T/R组件的优化将带来系统性能的显著提升、成本的大幅下降。

T/R组件中最重要的部分就是射频收发前端。作为核心组成之一的射频发射前端对来自上位机的基带信号进行混频、放大、滤波,将其频谱搬移至高频频段从而实现有效发射。目前主流的射频发射前端主要基于传统的直接上变频和超外差式发射机架构。前者电路结构简单,不产生镜像信号,但由于本振信号与输出信号频率相同,因此输出信号噪声较大。后者无本振牵引效应,但结构复杂,功耗较大。大多数射频发射前端针对单一频段应用进行设计,相对带宽较窄。同时发射功率固定,不可根据应用场景进行调节。

发明内容

本发明的目的是在保证低噪声、高输出频谱纯净度的前提下,提供一种宽带、高线性度、输出功率可控的新型射频发射前端电路。利用其宽带和输出功率连续可调的特点,满足多种应用的要求。技术方案如下:

一种宽带高线性度的射频发射前端电路,在基带和本振端口采用基于共栅放大器-共源放大器结构的巴伦实现超宽带输入匹配,在射频端口采用基于推挽结构的A类功率放大器实现超宽带输出匹配,包括:基带单转双模块、本振单转双模块、混频器模块、可变增益放大器模块及驱动放大器模块,其中,

基带单转双模块将单端中频输入信号转换为差分形式,提供给混频器模块的跨导单元,输入匹配网络由第一晶体管(M1)、串联在第一晶体管(M1)栅极与地端之间的第一电容(C1)共同组成,用以实现基带端口5M~200MHz的宽带输入匹配;

本振单转双模块将单端本振输入信号转换为差分形式,提供给混频器模块的开关单元,输入匹配网络由第三晶体管(M3)、串联在第三晶体管(M3)栅极与地端之间的第二电容(C2)及串联在输入端与第三晶体管(M3)栅极之间的第三电感(L3)组成,用以实现本振端口400M~0.2GHz的宽带输入匹配;

混频器模块采用正交双平衡吉尔伯特结构,将基带单转双模块提供的中频信号通过与本振单转双模块提供的本振信号进行电流换向调制,转换为射频差分信号提供给可变增益放大器模块;

可变增益放大器模块采用基于跨导可变的共源共栅放大器对混频器输出的射频信号进行增益控制,并将信号提供给驱动放大器模块;

驱动放大器模块采用基于源级跟随器-共源放大器结构的双转单巴伦和基于推挽结构的A类功率放大器,将可变增益放大器提供的差分射频信号转换为单端信号,并提供一定功率增益。

优选地,所述基带单转双模块还包括第二晶体管(M2)及第一电阻(R1)、第二电阻(R2)、第三电阻(R3);

其中,所述第一晶体管(M1)的栅极与第一电容(C1)第一端连接,源极与第三电阻(R3)第一端连接,漏极与第一电阻(R1)第一端连接;所述第二晶体管(M2)的栅极与第三电阻(R3)第一端连接,源极与地端连接,漏极与第二电阻(R2)第一端连接;所述第一电容(C1)第二端与地端连接;所述第三电阻(R3)第二端与地端连接;所述第一电阻(R1)和第二电阻(R2)的第二端均与电源VDD连接。

所述本振单转双模块还包括:第四晶体管(M4)及第四电阻(R4)、第五电阻(R5)、第六电阻(R6)、第一电感(L1)和第二电感(L2);

其中,所述第三晶体管(M3)的栅极与第二电容(C2)第一端连接,源极与第六电阻(R6)第一端连接,漏极与第一电感(L1)第一端连接;所述第四晶体管(M4)的栅极与第六电阻(R6)第一端连接,源极与地端连接,漏极与第二电感(L2)第一端连接;所述第一电感(L1)的第二端与第四电阻(R4)的第一端连接;所述第二电感(L2)的第二端与第五电阻(R5)的第一端连接;所述第二电容(C2)第二端与地端连接;所述第六电阻(R4)第二端与地端连接;所述第四电阻(R4)和第五电阻(R5)的第二端均与电源VDD连接。

所述混频器模块包括:第五晶体管(M5)、第六晶体管(M6)、第七晶体管(M7)、第八晶体管(M8)、第九晶体管(M9)、第十晶体管(M10)、第十一晶体管(M11)、第十二晶体管(M12)、第十三晶体管(M13)、第十四晶体管(M14)和第十五晶体管(M15)、第十六晶体管(M16)及第七电阻(R7)、第八电阻(R8)、第四电感(L4)、第五电感(L5);

其中,所述第五晶体管(M5)的栅极与负相I本振信号(LO-I-)连接、漏极与第七电阻(R7)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第六晶体管(M6)的栅极与正相I本振信号(LO-I+)连接、漏极与第八电阻(R8)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第七晶体管(M7)的栅极与正相I本振信号(LO-I+)连接、漏极与第七电阻(R7)第一端连接、源极与第十四晶体管(M14)漏极连接;所述第八晶体管(M8)的栅极与负相I本振信号(LO-I-)连接、漏极与第八电阻(R8)第一端连接、源极与第十四晶体管(M14)漏极连接;所述第九晶体管(M9)的栅极与负相Q本振信号连接、漏极与第七电阻(R7)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第十晶体管(M10)的栅极与正相Q本振信号(LO-Q+)连接、漏极与第八电阻(R8)第一端连接、源极与第十五晶体管(M15)漏极连接;所述第十一晶体管(M11)的栅极与正相Q本振信号(LO-Q+)连接、漏极与第七电阻(R7)第一端连接、源极与第十六晶体管(M16)漏极连接;第所述十二晶体管(M12)的栅极与负相Q本振信号(LO-Q-)连接、漏极与第八电阻(R8)第一端连接、源极与第十六晶体管(M16)漏极连接;所述第十三晶体管(M13)的栅极与正相Q中频信号(LO-Q+)连接;所述第十四晶体管(M14)的栅极与负相Q中频信号(LO-Q-)连接、源极与地端连接;所述第十五晶体管(M15)的栅极与负相I中频信号(LO-I-)连接、源极与地端连接;所述第十六晶体管(M16)的栅极与正相I中频信号(LO-I+)连接、源极与地端连接;所述第四电感(L4)的第一端口与第七电阻(R7)的第二端口连接,第二端口与电源VDD连接;所述第五电感(L5)的第一端口与第八电阻(R8)的第二端口连接,第二端口与电源VDD连接。

所述可变增益放大器模块包括:第十七晶体管(M17)、第十八晶体管(M18)、第十九晶体管(M19)、第二十晶体管(M20)及第九电阻(R9)、第十电阻(R10)和电流源;

其中,所述第十七晶体管(M17)的栅极与控制电压源连接,漏极与第九电阻(R9)的第一端连接,源极与第十九晶体管(M19)的漏极连接;所述第十八晶体管(M18)的栅极与控制电压源连接,漏极与第十电阻(R10)的第一端连接,源极与第二十晶体管(M20)的漏极连接;所述第十九晶体管(M19)的栅极与正向射频输入信号连接,漏极与第十七晶体管(M17)的源极连接,源极与电流源第一端连接;所述第二十晶体管(M20)的栅极与负向射频输入信号连接,漏极与第十八晶体管(M18)的源极连接,源极与电流源第一端连接;所述第九电阻(R9)第一端与第十七晶体管(M17)的漏极连接,第二端与电源VDD连接;所述第十电阻(R10)第一端与第十八晶体管(M18)的漏极连接,第二端与电源VDD连接;所述电流源第一端与第十九晶体管(M19)、第二十晶体管(M20)的源极连接,第二端与地端连接。

所述驱动放大器模块包括:第二十一晶体管(M21)、第二十二晶体管(M22)、第二十三晶体管(M23)、第二十四晶体管(M24)及第五电容(C5)、第四电容(C4)、第四电感(L4);

其中所述第二十一晶体管(M21)的栅极与正向射频输入信号连接,漏极与电源(VDD)连接,源极与第二十二晶体管(M22)的漏极连接;所述第二十二晶体管(M22)的栅极与负向射频输入信号连接,漏极与第二十一晶体管(M21)的源极连接,源极地端(GND)连接;所述第二十三晶体管(M23)的栅极与第四电容(C4)的第二端连接,漏极与电源(VDD)连接,源极与第二十四晶体管(M24)的漏极连接;所述第二十四晶体管(M24)的栅极与第五电容(C5)的第二端连接,源极与地端(GND)连接,漏极与第二十三晶体管(M23)的源极连接;所述第五电容(C5)第一端与第二十一晶体管(M21)的源极和第二十二晶体管(M22)的漏极连接,第二端与第二十三晶体管(M23)的栅极连接;所述第四电容(C4)第一端与第二十一晶体管(M21)的源极和第二十二晶体管(M22)的漏极连接,第二端与第二十四晶体管(M24)的栅极连接;所述第四电感(L4)的第一端与第二十三晶体管(M23)的栅极、第二十四晶体管(M24)的漏极连接,第二端与输出端连接。

所述第二十三晶体管(M23)为PMOS晶体管,其余均为NMOS晶体管。

本发明的实质性特点和有益效果是:

1.采用共栅-共源低噪声放大器作为系统输入级,通过设计共栅MOS管的宽长比,同时采用片上电容对输入阻抗的虚部进行补偿,从而实现基带端口与本振端口的宽带输入匹配;通过设计驱动放大器的直流偏置点与MOS管宽长比,同时采用由电感搭建的匹配网络,最终实现射频端口的宽带输出匹配。

2.采用推挽放大结构作为输出驱动放大器,通过设计NMOS/PMOS的参数使驱动放大器等效跨导、栅源寄生电容等趋于常数,进而提高线性度;通过使用片上电容对混频器跨导级的栅源寄生电容进行补偿,进一步提高系统线性度。

3.采用共源共栅作为增益可变放大器的基本结构,使共栅MOS管工作在饱和区,共源级MOS管工作在线性区。通过改变共栅MOS管的栅极电压改变共源级MOS管的跨导,进而使系统具有一定的增益动态范围。

4.采用感性阻抗结构来补偿晶体管的增益滚降;同时调整各级电路增益随频率变化趋势,使各级增益的变化相互叠加相消,从而使系统具有良好的带内增益起伏特性。

附图说明

图1射频发射前端系统架构示意图

图2基带端口LNA-Balun结构电路图原理图

图3本振端口LNA-Balun结构电路图原理图

图4双平衡正交混频器电路原理图

图5增益可变放大器电路原理图

图6驱动放大器电路原理图

具体实施方式

本发明基于直接上变频方式,结合系统工作频带、输出功率、端口数量等要求,对传统结构进行优化,系统架构见图1。首先,电路采用全差分结构,以抑制共模噪声、降低键合线电感对电路的影响。同时为了减少系统I/O端口数量,LNA采用单入双出(Single-to-double,S2D)结构。其次,考虑到IF信号的工作范围,混频器须采用正交双平衡吉尔伯特结构。该结构一方面能够起到提高端口隔离度、抑制偶次谐波的作用,另一方面使得输出射频信号中仅包含希望的和频成分,避免了复杂滤波器的使用。第三,在Mixer与DA之间增加一级小动态范围的VGA,以精确控制系统增益,同时减小系统带内增益起伏带来的影响。下面集结合附图对各级电路实施方式进行具体说明。

1.低噪声放大器

为了提高电路的噪声性能及谐波抑制比,同时节约芯片I/O端口,本发明使用低噪声放大器-巴伦合并结构(LNA-Balun Combination)作为发射通道的首级电路。基带端口的低噪声放大器电路结构如图2所示,本振端口的低噪声放大器电路结构如图3所示。

该电路在实现巴伦功能的同时可抵消共栅极带来的噪声及非线性。

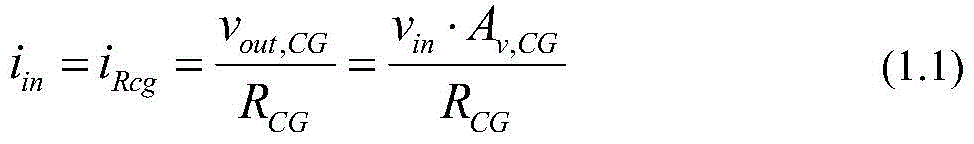

考虑电路的巴伦特性,晶体管M1的电流满足下式:

当电路满足输入匹配时,有Rin=RS,因此其输入阻抗Rin可以写为:

可推出:

当M2满足下式时电路具有巴伦功能:

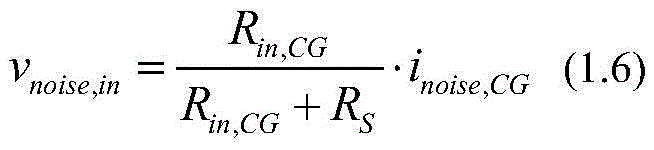

考虑由M1带来的噪声,将M1的热噪声等效为一个大小为Inoise的电流源,则噪声在节点IN引起的电压为:

可得节点A、B中包含的噪声分别为:

vnoise,CG=vnoise,in·AV,CG (1.7)

vnoise,CS=vnoise,in·AV,CS=-vnoise,CG (1.8)

由此可知电路消除了M1的热噪声。

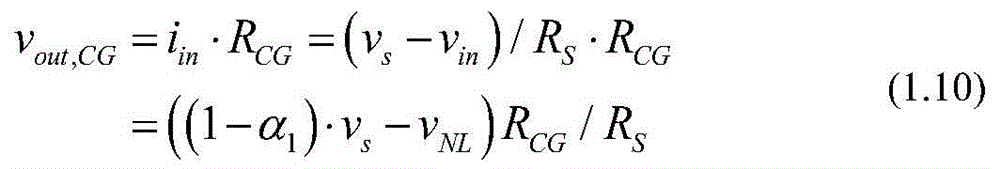

考虑电路的非线性,M1的非线性漏源电流ids将对vin产生影响,又ids由电源电压vs决定,因此可以用vs表示vin:

其中α1表示一阶泰勒展开系数,vNL表示所有非线性项。则输出节点A、B的电压可以分别表示为:

vout,CS=-vin·RCG/RS=-(α1·vs+vNL)·RCG/RS (1.11)

电路差分输出为:

vout,diff=vout,CG-vout,CS=vs·RCG/RS (1.12)

上式中不包含非线性项,可见由M1导致的非线性在电路的差分输出端口抵消。

考虑到电路IF工作范围,在设计时需要额外考虑LNA的低频噪声。M2对电路噪声的贡献与其跨导gm,CS成反比,因此本发明对M2的跨导、面积与功耗进行了折衷。同时使用Poly电阻作为负载,进一步降低电路的1/f噪声。通过调节M1的参数使其跨导接近1/RS,同时在M1的栅极并联对地电容C以补偿输入信号的幅度与相位,能够使电路在5M~200M内获得良好的输入匹配。采用片上电阻R代替电流源为M2提供偏置,不仅能够节约芯片面积,而且有助于改善电路的匹配特性。

考虑到本振端口需要在更大的范围内实现宽带输入匹配,同时为了降低增益滚降对系统性能的影响,本振端口的低噪声放大器采用电阻电感串联结构作为负载,并在输入端添加电感进行匹配,其他结构与基带端口LNA结构相同。

2.混频器

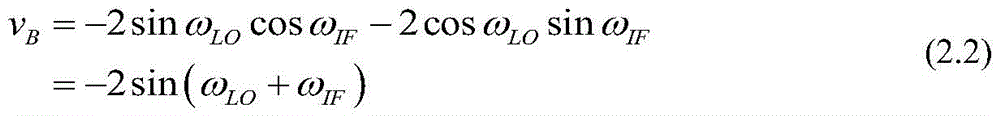

本发明采用的双平衡正交混频器电路结构如图4所示。

考察该电路输出节点A、B的电压:

由此可见输出信号中仅包含和频成分,因此该结构免除了滤波器的使用。

电路中跨导管M9~M12将输入IF电压信号转换为电流形式,开关管M1~M8由本振信号驱动工作于截止区与饱和区之间,对该电流进行开关调制,负载R1、R2将输出RF电流转换为电压信号,从而实现混频功能。同时在负载中串联电感L1、L2,目的是补偿高频增益衰减。

考虑到IF信号最低频率仅有5MHz,跨导级中的低频噪声经过频率转换后会对输出RF信号产生较大影响。该噪声幅度与输出RF频率和LO频率的差值成反比,主要来源为跨导级的1/f噪声。本发明通过增大跨导管面积,提高提高跨导管gm,适当增大LO信号摆幅来减小该噪声。开关级的噪声不经过任何频率转换直接输出,本发明通过减小开关级偏置电流,降低噪声脉冲的高度从而减小其噪声。

该电路的非线性主要由跨导级决定,其三阶交调点表达式为:

可以简化为:

|IM3(2ω1-ω2)|∝|1+jωCgsZs(ω)| (2.4)

由于jωCgsZs(ω)项为负值,因此IM3的幅度与Zs和Cgs成反比。本设发明通过在跨导管栅源之间添加并联电感以提高晶体管原有Cgs,不以牺牲面积、增益或功耗为前提而增加线性度。

3.可变增益放大器

为精确控制系统增益,同时降低带内增益起伏对输出信号功率的影响,本发明在Mixer与DA之间使用了一级具有20dB动态范围的可变增益放大器,电路结构如图5所示。

该VGA采用线性区工作的差分共源共栅结构。晶体管M1、M2能够起到提高增益、反向隔离度,以及减小晶体管M3、M4的密勒电容,改善稳定性等作用。

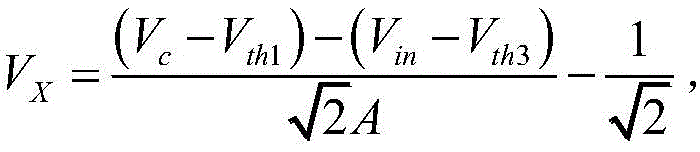

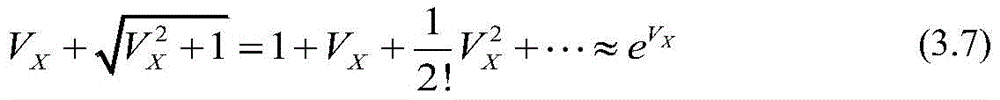

输入对管M3、M4工作在线性区,其等效跨导是漏源电压Vds3、Vds4的线性函数,可以写为:

gm3=μ0COXW/L·Vds3 (3.1)

M1、M2的跨导以及电路的电流可以表达为:

gm1=μ0COXW/L·(Vgs1-Vth1)2 (3.2)

Ids1=μ0COXW/2L·(Vgs1-Vth1)2 (3.3)

Ids3=μ0COXW/L·[(Vgs3-Vth3)-Vds3/2]·Vds3 (3.4)

联立式(3.3)和式(3.4),可以解出:

对上式进行泰勒展开变换,可以得到:

因此,在电路电流及负载保持恒定的情况下,通过对M3、M4栅电压的控制,可以使其跨导呈指数趋势变化,从而使VGA具有dB线性(Linear-in-dB)增益控制特性。

4.驱动放大器

由于差分信号在系统中能够实现的噪声性能、隔离度及线性度等性能较单端信号具有明显优势,因此本发明在芯片内部使用差分信号,对于本级电路模块而言需要实现双端信号到单端信号的转换,同时还需对输出端口进行阻抗匹配设计。其电路拓扑结构如图6所示。

本发明采用共源放大器和源级跟随器来实现信号的双转单功能。晶体管M1作为源级跟随器,虽无电压增益,但其高输入阻抗、低输出阻抗使其拥有一定的功率增益。通过合理设计M1、M2的宽长比及偏置电压,利用源级跟随器对信号同相放大、共源放大器对信号进行反相放大的特点,实现信号的双转单功能。

射频驱动放大器需要实现高输出功率,其线性度指标至关重要。本发明采用推挽放大器作为输出驱动放大器的结构,核心部分由上图中的晶体管M3(PMOS)、M4(NMOS)组成。M3和M4相反的工作状态,使得电路等效跨导、栅源电容等电路参数能够实现互补。通过对晶体管尺寸的设计,可使电路的g′m和g″m分别叠加抵消,从而消除跨导非线性。同时M3与M4的Cgs随输出电压变化方向相反,因而能够降低电路Cin的变化,减小AM-PM失真。

考察该电路的输出阻抗,该输出阻抗的实部可以表达为:

因此通过合理设计电路偏置以及MOS管尺寸,可以实现电路良好的宽带阻抗匹配性能。电感L为匹配电路。

本发明的具体结构如下:

其中基带LNA为:晶体管M1的栅极与电容C一端相连,源极与电阻R一端相连,漏极与电阻R1相连;晶体管M2的栅极与电阻R的一端相连,源极接地,漏极与电阻R2的一端连接;电容C另一端接地;电阻R另一端接地;电阻R1另一端接电源;电阻R2另一端接电源。

其中本振LNA为:晶体管M1的栅极与电容C一端相连,源极与电阻R一端相连,漏极与电感L1相连,L1另一端与电阻R1相连;晶体管M2的栅极与电感L和电阻R的一端相连,源极接地,漏极与电感L2相连,L2另一端电阻R2的一端连接;电容C另一端接地;电阻R另一端接地;电阻R1另一端接电源;电阻R2另一端接电源。

其中混频器为:第一晶体管M1、第四晶体管M4的栅极连接反向本振I信号LO-I-,第二晶体管M2、第三晶体管M3的栅极连接正向本振I信号LO-I+,第五晶体管M5、第八晶体管M8的栅极连接反向本振I信号LO-I-,第六晶体管M6、第七晶体管M7的栅极连接正向本振I信号LO-I+。第一晶体管、第三晶体管、第五晶体管、第七晶体管的漏极与电阻R1的一端相连,R1的另一端与电感L1的一端相连,L1另一端接电源。第二晶体管、第四晶体管、第六晶体管、第八晶体管的漏极与电阻R2的一端相连,R2的另一端与电感L2的一端相连,L2另一端接电源。第一晶体管、第二晶体管的源极接第九晶体管M9的漏极。第三晶体管、第四晶体管的源极接第十晶体管M10的漏极。第五晶体管、第六晶体管的源极接第十一晶体管M11的漏极。第七晶体管、第八晶体管的源极接第十二晶体管M12的漏极。第九晶体管的栅极接正向中频信号QIF-Q+,源极接地。第十晶体管的栅极接反向中频信号Q(IF-Q-)。第十一晶体管的栅极接反向中频信号IIF-I-,源极接地。第十二晶体管的栅极接正向中频信号(IF-I+),源极接地。

其中VGA为:第一晶体管M1的漏极接电阻R1的一端,R1另一端接电源;栅极接控制电压Vc;漏极接第三晶体管M3的漏极。第二晶体管M2的漏极接电阻R2的一端,R2另一端接电源;栅极接控制电压Vc;漏极接第四晶体管M4的漏极。第三晶体管的栅极接正向输入信号IN+,源极接电流源。第四晶体管的栅极接反向输入信号IN-,源极接电流源。

其中驱动放大器模块为:第一晶体管M1的漏极接电源,栅极接正向输入信号IN+,源极接第二晶体管M2的漏极。第二晶体管的栅极接反向输入信号IN-,源极接地。第三晶体管M3的栅极通过电容连接到第一晶体管的源极,漏极接电源,源极接第四晶体管M4的漏极。第四晶体管的栅极通过电容连接到第二晶体管的漏极,漏极接电感L的一端,L另一端为输出,源极接地。

Claims (8)

1.一种宽带高线性度的射频发射前端电路,在基带和本振端口采用基于共栅放大器-共源放大器结构的巴伦实现超宽带输入匹配,在射频端口采用基于推挽结构的A类功率放大器实现超宽带输出匹配,包括:基带单转双模块、本振单转双模块、混频器模块、可变增益放大器模块及驱动放大器模块,其中,

基带单转双模块将单端中频输入信号转换为差分形式,提供给混频器模块的跨导单元,输入匹配网络由第一晶体管(M1)、串联在第一晶体管(M1)栅极与地端之间的第一电容(C1)共同组成,用以实现基带端口5M~200MHz的宽带输入匹配;

本振单转双模块将单端本振输入信号转换为差分形式,提供给混频器模块的开关单元,输入匹配网络由第三晶体管(M3)、串联在第三晶体管(M3)栅极与地端之间的第二电容(C2)及串联在输入端与第三晶体管(M3)栅极之间的第三电感(L3)组成,用以实现本振端口400M~0.2GHz的宽带输入匹配;

混频器模块采用正交双平衡吉尔伯特结构,将基带单转双模块提供的中频信号通过与本振单转双模块提供的本振信号进行电流换向调制,转换为射频差分信号提供给可变增益放大器模块;

可变增益放大器模块采用基于跨导可变的共源共栅放大器对混频器输出的射频信号进行增益控制,并将信号提供给驱动放大器模块;

驱动放大器模块采用基于源级跟随器-共源放大器结构的双转单巴伦和基于推挽结构的A类功率放大器,将可变增益放大器提供的差分射频信号转换为单端信号,并提供一定功率增益。

2.根据权利要求1所述的射频发射前端电路,其特征在于,所述基带单转双模块还包括第二晶体管(M2)及第一电阻(R1)、第二电阻(R2)、第三电阻(R3);

其中,所述第一晶体管(M1)第六电阻的栅极与第一电容(C1)第一端连接,源极与第三电阻(R3)第一端连接,漏极与第一电阻(R1)第一端连接;所述第二晶体管(M2)的栅极与第三电阻(R3)第一端连接,源极与地端连接,漏极与第二电阻(R2)第一端连接;所述第一电容(C1)第二端与地端连接;所述第三电阻(R3)第二端与地端连接;所述第一电阻(R1)和第二电阻(R2)的第二端均与电源VDD连接。

3.根据权利要求2所述的射频发射前端电路,其特征在于,所述本振单转双模块还包括:第四晶体管(M4)及第四电阻(R4)、第五电阻(R5)、第六电阻(R6)、第一电感(L1)和第二电感(L2);

其中,所述第三晶体管(M3)的栅极与第二电容(C2)第一端连接,源极与第六电阻(R6)第一端连接,漏极与第一电感(L1)第一端连接;所述第四晶体管(M4)的栅极与第六电阻(R6)第一端连接,源极与地端连接,漏极与第二电感(L2)第一端连接;所述第一电感(L1)的第二端与第四电阻(R4)的第一端连接;所述第二电感(L2)的第二端与第五电阻(R5)的第一端连接;所述第二电容(C2)第二端与地端连接;所述第六电阻(R6)第二端与地端连接;所述第四电阻(R4)和第五电阻(R5)的第二端均与电源VDD连接。

4.根据权利要求3所述的射频发射前端电路,其特征在于,所述混频器模块包括:第五晶体管(M5)、第六晶体管(M6)、第七晶体管(M7)、第八晶体管(M8)、第九晶体管(M9)、第十晶体管(M10)、第十一晶体管(M11)、第十二晶体管(M12)、第十三晶体管(M13)、第十四晶体管(M14)和第十五晶体管(M15)、第十六晶体管(M16)及第七电阻(R7)、第八电阻(R8)、第四电感(L4)、第五电感(L5);

其中,所述第五晶体管(M5)的栅极与负相I本振信号(LO-I-)连接、漏极与第七电阻(R7)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第六晶体管(M6)的栅极与正相I本振信号(LO-I+)连接、漏极与第八电阻(R8)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第七晶体管(M7)的栅极与正相I本振信号(LO-I+)连接、漏极与第七电阻(R7)第一端连接、源极与第十四晶体管(M14)漏极连接;所述第八晶体管(M8)的栅极与负相I本振信号(LO-I-)连接、漏极与第八电阻(R8)第一端连接、源极与第十四晶体管(M14)漏极连接;所述第九晶体管(M9)的栅极与负相Q本振信号(LO-Q-)连接、漏极与第七电阻(R7)第一端连接、源极与第十三晶体管(M13)漏极连接;所述第十晶体管(M10)的栅极与正相Q本振信号(LO-Q+)连接、漏极与第八电阻(R8)第一端连接、源极与第十五晶体管(M15)漏极连接;所述第十一晶体管(M11)的栅极与正相Q本振信号(LO-Q+)连接、漏极与第七电阻(R7)第一端连接、源极与第十六晶体管(M16)漏极连接;第所述十二晶体管(M12)的栅极与负相Q本振信号(LO-Q-)连接、漏极与第八电阻(R8)第一端连接、源极与第十六晶体管(M16)漏极连接;所述第十三晶体管(M13)的栅极与正相Q中频信号(LO-Q+)连接;所述第十四晶体管(M14)的栅极与负相Q中频信号(LO-Q-)连接、源极与地端连接;所述第十五晶体管(M15)的栅极与负相I中频信号(LO-I-)连接、源极与地端连接;所述第十六晶体管(M16)的栅极与正相I中频信号(LO-I+)连接、源极与地端连接;所述第四电感(L4)的第一端口与第七电阻(R7)的第二端口连接,第二端口与电源VDD连接;所述第五电感(L5)的第一端口与第八电阻(R8)的第二端口连接,第二端口与电源VDD连接。

5.根据权利要求4所述的射频发射前端电路,其特征在于,所述可变增益放大器模块包括:第十七晶体管(M17)、第十八晶体管(M18)、第十九晶体管(M19)、第二十晶体管(M20)及第九电阻(R9)、第十电阻(R10)和电流源;

其中,所述第十七晶体管(M17)的栅极与控制电压源连接,漏极与第九电阻(R9)的第一端连接,源极与第十九晶体管(M19)的漏极连接;所述第十八晶体管(M18)的栅极与控制电压源连接,漏极与第十电阻(R10)的第一端连接,源极与第二十晶体管(M20)的漏极连接;所述第十九晶体管(M19)的栅极与正向射频输入信号连接,漏极与第十七晶体管(M17)的源极连接,源极与电流源第一端连接;所述第二十晶体管(M20)的栅极与负向射频输入信号连接,漏极与第十八晶体管(M18)的源极连接,源极与电流源第一端连接;所述第九电阻(R9)第一端与第十七晶体管(M17)的漏极连接,第二端与电源VDD连接;所述第十电阻(R10)第一端与第十八晶体管(M18)的漏极连接,第二端与电源VDD连接;所述电流源第一端与第十九晶体管(M19)、第二十晶体管(M20)的源极连接,第二端与地端连接。

6.根据权利要求5所述的射频发射前端电路,其特征在于,所述驱动放大器模块包括:第二十一晶体管(M21)、第二十二晶体管(M22)、第二十三晶体管(M23)、第二十四晶体管(M24)及第五电容(C5)、第四电容(C4)、第四电感(L4);

其中所述第二十一晶体管(M21)的栅极与正向射频输入信号连接,漏极与电源VDD连接,源极与第二十二晶体管(M22)的漏极连接;所述第二十二晶体管(M22)的栅极与负向射频输入信号连接,漏极与第二十一晶体管(M21)的源极连接,源极地端(GND)连接;所述第二十三晶体管(M23)的栅极与第四电容(C4)的第二端连接,漏极与电源VDD连接,源极与第二十四晶体管(M24)的漏极连接;所述第二十四晶体管(M24)的栅极与第五电容(C5)的第二端连接,源极与地端(GND)连接,漏极与第二十三晶体管(M23)的源极连接;所述第五电容(C5)第一端与第二十一晶体管(M21)的源极和第二十二晶体管(M22)的漏极连接,第二端与第二十三晶体管(M23)的栅极连接;所述第四电容(C4)第一端与第二十一晶体管(M21)的源极和第二十二晶体管(M22)的漏极连接,第二端与第二十四晶体管(M24)的栅极连接;所述第四电感(L4)的第一端与第二十三晶体管(M23)的栅极、第二十四晶体管(M24)的漏极连接,第二端与输出端连接。

7.根据权利要求6所述的射频发射前端电路,其特征在于,所述第二十三晶体管(M23)为PMOS晶体管,其余均为NMOS晶体管。

8.根据权利要求7所述的射频发射前端电路,其特征在于,所述电源VDD提供直流偏置电压,且电压值为3.3V。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710937103.4A CN107911092B (zh) | 2017-10-10 | 2017-10-10 | 一种宽带高线性度的射频发射前端电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710937103.4A CN107911092B (zh) | 2017-10-10 | 2017-10-10 | 一种宽带高线性度的射频发射前端电路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN107911092A CN107911092A (zh) | 2018-04-13 |

| CN107911092B true CN107911092B (zh) | 2020-11-27 |

Family

ID=61841222

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201710937103.4A Expired - Fee Related CN107911092B (zh) | 2017-10-10 | 2017-10-10 | 一种宽带高线性度的射频发射前端电路 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN107911092B (zh) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108957409A (zh) * | 2018-07-12 | 2018-12-07 | 中国船舶重工集团公司第七二四研究所 | 一种宽带收发组件提高抗干扰能力及小型化的设计方法 |

| CN108736847B (zh) * | 2018-07-24 | 2023-09-01 | 成都嘉纳海威科技有限责任公司 | 基于精确谐振回路控制的高效率逆d类堆叠功率放大器 |

| CN109104160A (zh) * | 2018-08-22 | 2018-12-28 | 广东工业大学 | 一种射频功率放大器及无线通信系统 |

| CN109743023B (zh) * | 2018-12-24 | 2020-10-30 | 武汉大学 | 一种可上下变频复用的24GHz混频器 |

| CN113728550B (zh) | 2019-03-30 | 2024-06-18 | 华为技术有限公司 | 一种可变增益放大器及相控阵收发机 |

| GB202007234D0 (en) * | 2020-05-15 | 2020-07-01 | Nordic Semiconductor Asa | Radio-frequency modulator apparatus |

| CN113572440B (zh) * | 2020-06-16 | 2022-11-08 | 锐石创芯(深圳)科技股份有限公司 | 功放输出匹配电路、射频前端模组和无线装置 |

| CN113098485B (zh) * | 2021-04-02 | 2022-12-02 | 南方科技大学 | 一种双转单驱动电路 |

| CN113437941B (zh) * | 2021-06-11 | 2022-10-14 | 电子科技大学 | 一种高边带抑制的高线性度单边带混频器 |

| CN113746431B (zh) * | 2021-08-06 | 2024-01-05 | 天津大学 | 一种带镜像抑制功能的超宽带高线性度混频器 |

| CN114046881B (zh) * | 2021-11-15 | 2024-05-28 | 深圳知微创新技术有限公司 | 一种基于薄膜晶体管的高灵敏度颜色传感器 |

| CN114584076B (zh) * | 2022-03-03 | 2024-04-16 | 北京大学 | 一种针对发射机无源上混频器抑制谐波的校正方法 |

| CN114598267B (zh) * | 2022-04-12 | 2025-03-04 | 中国科学院空天信息创新研究院 | 双向混频器 |

| CN114785287B (zh) * | 2022-06-17 | 2022-09-20 | 成都旋极星源信息技术有限公司 | 一种发射机电路与电子设备 |

| CN114978074B (zh) * | 2022-07-25 | 2022-11-11 | 成都嘉纳海威科技有限责任公司 | 一种三通道收发放大芯片 |

| CN115276573A (zh) * | 2022-08-01 | 2022-11-01 | 浙江大学 | 一种基于晶体管可变电容器的相位温度补偿放大器集成电路 |

| CN117674816B (zh) * | 2023-10-25 | 2024-09-20 | 隔空微电子(深圳)有限公司 | 共本振芯片、级联结构及工作方法 |

| CN118018044B (zh) * | 2024-04-09 | 2024-06-04 | 成都信息工程大学 | 一种超宽带发射前端系统 |

| CN119561558B (zh) * | 2024-11-27 | 2025-07-08 | 广州润芯信息技术有限公司 | 一种电流型发射机前端电路及发射系统 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102096079B (zh) * | 2009-12-12 | 2013-12-11 | 杭州中科微电子有限公司 | 一种多模式多频段卫星导航接收机射频前端构成方法及其模块 |

| US9300264B2 (en) * | 2014-08-22 | 2016-03-29 | Mediatek Inc. | Receiver arrangement and method of performing operations of receiver |

| CN105139049B (zh) * | 2015-08-25 | 2018-02-27 | 华东师范大学 | 工作于860~960MHz的CMOS全集成UHF RFID读写器射频接收前端电路 |

| CN105281802A (zh) * | 2015-11-30 | 2016-01-27 | 武汉中元通信股份有限公司 | 一种适用于无线电台的宽频段射频通用收/发单元 |

| CN106385240B (zh) * | 2016-11-30 | 2018-09-21 | 东南大学 | 一种增益连续可调的射频前端电路 |

| CN107134980B (zh) * | 2017-06-14 | 2023-07-25 | 苏州大学 | 射频单端转差分跨导互补型高性能下混频器 |

-

2017

- 2017-10-10 CN CN201710937103.4A patent/CN107911092B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN107911092A (zh) | 2018-04-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107911092B (zh) | 一种宽带高线性度的射频发射前端电路 | |

| CN107786168B (zh) | 一种高增益高隔离毫米波双平衡无源亚谐波混频器 | |

| JP5612034B2 (ja) | アクティブポストディストーション線形化を有する差動増幅器 | |

| CN101834567B (zh) | 宽带增益可调低噪声放大器 | |

| CN103401508B (zh) | 一种低噪声放大器和混频器融合系统 | |

| CN101494441B (zh) | 宽带低噪声放大器 | |

| CN102946230A (zh) | 一种超宽带单端输入差分输出低噪声放大器 | |

| CN110635769B (zh) | 差分低噪声放大器 | |

| CN107645300A (zh) | 一种电流复用低功耗射频接收机 | |

| CN107070425A (zh) | 应用于无线传感器网络的宽带低功耗低噪声放大器 | |

| CN107196611A (zh) | 宽带单端转差分低噪声放大器 | |

| CN107733375A (zh) | 超宽带低噪声放大器 | |

| CN114553147B (zh) | 可配置增益的双平衡无源混频器 | |

| CN104124923B (zh) | 一种低噪声混频器电路 | |

| CN103633947A (zh) | 一种无电感高增益cmos宽带低噪声放大器 | |

| US6980055B2 (en) | CMOS differential buffer circuit | |

| CN211579935U (zh) | 一种应用于低噪声放大器芯片的自适应偏置电路 | |

| CN112910416A (zh) | 一种应用于汽车雷达的高增益毫米波混频器 | |

| CN117118466A (zh) | 一种p波段变频发射方法及系统 | |

| WO2020000614A1 (zh) | 混频器电路 | |

| CN104104336B (zh) | 一种具有噪声抵消的低功耗宽带射频前端电路 | |

| CN106603013B (zh) | 一种cmos互补结构的混频器电路 | |

| CN111478671A (zh) | 一种应用于Sub-GHz频段的新型低噪声放大器 | |

| CN114938206A (zh) | 一种低噪声超宽带有源巴伦 | |

| CN206712752U (zh) | 应用于无线传感器网络的宽带低功耗低噪声放大器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20201127 Termination date: 20211010 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |