CN102779829A - 显示装置和电子设备 - Google Patents

显示装置和电子设备 Download PDFInfo

- Publication number

- CN102779829A CN102779829A CN2012101357055A CN201210135705A CN102779829A CN 102779829 A CN102779829 A CN 102779829A CN 2012101357055 A CN2012101357055 A CN 2012101357055A CN 201210135705 A CN201210135705 A CN 201210135705A CN 102779829 A CN102779829 A CN 102779829A

- Authority

- CN

- China

- Prior art keywords

- voltage

- pixel

- electrode

- display unit

- driving transistors

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0876—Supplementary capacities in pixels having special driving circuits and electrodes instead of being connected to common electrode or ground; Use of additional capacitively coupled compensation electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

Abstract

本发明提供了显示装置和电子设备,其中,该显示装置具有包括电光元件和晶体管的像素。各个像素具有在与晶体管的栅电极同一层的金属层与形成有晶体管的源区和漏区的半导体层之间通过向该金属层施加电压而形成的电容元件。

Description

技术领域

本发明涉及显示装置和电子设备。特别地,本发明涉及包括电光元件的像素按矩阵配置的平板(平面)显示装置以及具有该显示装置的电子设备。

背景技术

作为平板显示装置,有机EL(电致发光)显示装置、LCD(液晶显示器)装置、PDP(等离子体显示面板)装置等已广泛应用。

在这样的显示装置中,包括电光元件和晶体管的像素(像素电路)在基板(面板)上按矩阵配置。此外,显示装置中的像素,例如有机EL显示装置中的像素,除了电光元件和晶体管之外,还可以包括诸如存储电容器、辅助电容器的电容元件(例如,参见日本未审查专利申请公开第2008-51990号)。

发明内容

配置有包括电容元件的像素的显示装置,例如日本未审查专利申请公开第2008-51990号所披露的有机EL显示装置,一般采用如下构造,将相对的金属层之间的绝缘膜用作电介质从而在其间形成电容元件。如果要在该像素内制造的电容元件可以在除了这些金属层之间的区域以外的区域中形成,则可以提高像素的截面结构的自由度。

因此,期望能够提供这样的显示装置,其中,在像素内制造的电容元件形成在除了金属层之间的区域以外的区域,从而可以提高像素的截面结构的自由度,并且能够提供具有该显示装置的电子设备。

根据本发明的实施方式,提供了一种显示装置,其具有包括电光元件和晶体管的像素。每个像素具有在与晶体管的栅电极同一层的金属层与形成有晶体管的源区和漏区的半导体层之间通过向金属层施加电压而形成的电容元件。该显示装置可以在各种电子设备中用作显示装置。

当向在形成与晶体管的栅电极同一层的金属层与形成有晶体管的源区和漏区的半导体层的结构中的金属层施加相对于半导体层的电压更高的电压时,在半导体层的表面形成沟道,并且利用栅绝缘膜作为电介质形成电容器。即,在向金属层施加电压时,在半导体层的表面形成沟道,利用在金属层和半导体层之间的栅绝缘膜形成电容器。将该电容器用作要制作为像素的电容元件使得电容元件形成在除了金属层之间的区域以外的区域中。

根据本发明,因为要在像素内制作的电容元件可以形成在除了金属层之间的区域以外的区域中,所以能够提高像素的截面结构的自由度。

附图说明

图1是示出了应用本发明实施方式的有源矩阵型有机EL显示装置的基本构造的概要的系统框图。

图2是示出了一个像素(像素电路)的具体电路构造的一个实例的电路图。

图3是示出了应用本发明实施方式的有机EL显示装置的基本电路操作的定时波形图。

图4A至图4D是示出了应用本发明实施方式的有机EL显示装置的基本电路操作的示图(部分1)。

图5A至图5D是示出了施加本发明实施方式的有机EL显示装置的基本电路操作的示图(部分2)。

图6A是示出了由驱动晶体管的阈值电压变化所导致的问题的示图,以及图6B是示出了驱动晶体管的迁移率变化所导致的问题的示图。

图7是示出了具有顶栅结构的晶体管的截面结构的截面图。

图8A至图8C示出了为何对金属层施加电压以在金属层与半导体层之间形成电容元件。

图9是示出了根据本发明实施方式的像素的截面结构的截面图。

图10是示出了根据第一实施方式的像素电路的电路图。

图11示出了用于对辅助电容器的第二电极外部施加恒定电压的面板布局示例。

图12是示出了当相对于半导体层的电位金属层的电位降低时亮度降低的机制的定时波形图;

图13示出了半导体电容的电容特性;

图14是示出了像素中有机EL元件的操作点变化导致亮度不均匀的机制的定时波形图;

图15是示出了第二实施方式的定时波形图;

图16是示出了根据第二实施方式的示例性驱动定时的定时波形图表;

图17是示出了用于实现根据第二实施方式的示例性驱动定时的面板构造的实例的系统框图;

图18是根据第二实施方式的修改例的像素电路的电路图;

图19是示出了应用本发明实施方式的电视机的外观的透视图;

图20A和图20B分别是示出了应用本发明实施方式的数码相机的外观的前透视图和后透视图;

图21是示出了应用本发明实施方式的笔记本式个人计算机的外观的透视图;

图22是示出了应用本发明实施方式的视频摄像机的外观的透视图;

图23A至图23G是应用本发明实施方式的移动电话的外部视图,图23A是移动电话打开时的前视图,图23B是其侧视图,图23C是移动电话关闭时的前视图,图23D是左侧视图,图23E是右侧视图,图23F是顶视图,以及图23G是底视图。

具体实施方式

下面将参考附图,详细说明用于实现根据本发明的技术的模式(下文称作“实施方式”)。说明以如下顺序给出:

1.应用了本发明实施方式的有机EL显示装置

1-1.系统构造

1-2.基本电路操作

1-3.底栅结构和顶栅结构

2.实施方式

2-1.第一实施方式

2-2.第二实施方式

3.应用例

4.电子设备

<1.应用本发明实施方式的有机EL显示装置>

[1-1.系统构造]

图1是示出了应用本发明实施方式的有源矩阵型显示装置的基本构造的概述的系统框图。

在有源矩阵型有机显示装置中,设置在与设置有电光元件的像素相同的像素内的有源元件(例如绝缘栅型场效应晶体管)控制在有机EL元件中流动的电流。绝缘栅型场效应晶体管通常使用TFT(薄膜晶体管)实现。

此处将给出这样的有源矩阵型有机EL显示装置的实例的说明,其中,将发光亮度根据装置中流经的电流值变化的电流驱动型电光元件(例如有机EL元件)用作像素(像素电路)的发光元件。

如图1所示,根据本应用例的有机EL显示装置10具有:包括有机EL元件的像素20;像素阵列部30,其中像素20按照矩阵二维配置;以及驱动电路部,设置在像素阵列部30的附近。驱动电路部包括写入扫描电路40、电源扫描电路50以及信号输出电路60等,以驱动像素阵列部30中的像素20。

当有机EL显示装置10是彩色显示装置时,用作形成彩色图像的一个单位的单个像素(单位像素)由多个子像素构成,这些子像素对应于图1的像素20。更具体地说,在彩色显示装置中,一个像素由例如发红色(R)光的子像素、发绿色(G)光子像素和发蓝色(B)光的子像素这3个子像素构成。

但是,一个像素不限于包括RGB三原色的子像素的组合。即,可以对三原色子像素进一步增加另外一种颜色的子像素或另外几种颜色的子像素,从而形成单个像素。更加具体地,例如为了提高亮度,可以增加发白色(W)光的子像素以构成单个像素,或者为了扩大色彩再现范围,可以增加至少一个发出补色的子像素以构成单个像素。

对于像素阵列部30中的以m行×n列配置的像素20,以像素行为单位沿着行方向(即,像素行中像素20的配置方向)配置扫描线31(311至31m)和电源供应线32(321至32m)。此外,对于以m行×n列配置的像素20,以像素列为单位沿着列方向(即,像素列中像素20的配置方向)配置信号线33(331至33n)。

扫描线311至31m连接至写入扫描电路40的相应行的输出端。电源供应线321至32m连接至电源扫描电路50的相应行的输出端。信号线331至33n连接至信号输出电路60的相应列的输出端。

通常,像素阵列部30设置在诸如玻璃基板的透明绝缘基板上。这样,有机EL显示装置10具有平板结构。像素阵列部30中像素20的驱动电路可以使用非晶硅TFT或低温多晶硅TFT制造。当使用低温多晶硅TFT时,如图1所示,可以在包括像素阵列部30的显示面板(基板)70上设置写入扫描电路40、电源扫描电路50和信号输出电路60。

写入扫描电路40包括移位寄存器电路等,其与时钟脉冲ck同步地将起始脉冲sp顺序移位(转移)。在向像素阵列部30的像素20写入视频信号的信号电压写入期间,写入扫描电路40向相应扫描线31(311至31m)顺序地提供写入扫描信号WS(WS1至WSm),从而顺序地逐行扫描(线顺序扫描)像素阵列部30中的像素20。

电源扫描电路50包括移位寄存器电路等,其与时钟脉冲ck同步地将起始脉冲sp顺序移位。该电源扫描电路50与写入扫描电路40执行的线顺序扫描同步地提供电源电位DS(DS1至DSm)给相应电源供应线32(321至32m)。每个电源电位DS可以在第一电源电位Vccp和低于该第一电源电位Vccp的第二电源电位Vini之间切换。通过电源电位DS在电源电位Vccp和Vini之间的切换,控制像素20的发光和非发光。

信号输出电路60选择性地输出与从信号源(未示出)提供的亮度信息相对应的视频信号的信号电压Vsig和参考电压Vofs。参考电压Vofs用作视频信号的信号电压Vsig的参考电位(并且例如对应于视频信号的黑色电平的电压),并且用于阈值校正处理(下述)。

对于由扫描电路40的扫描所选择的各个像素行,将从信号输出电路60选择性地输出的信号电压Vsig和参考电位Vofs通过信号线33(331至33n)写入到像素阵列部30中的相应像素20。即,信号输出电路60具有线顺序写入驱动系统,用于逐行(逐线)写入信号电压Vsig。(像素电路)

图2是示出了一个像素(像素电路)20的具体电路构造的一个实例的电路图。像素20具有包括有机EL元件21的发光部,该有机EL元件21是电流驱动型电光元件。有机EL元件21的发光亮度根据装置中流经的电流值而变化。

如图2所示,像素20除了包括有机EL元件21以外,还包括用于通过使电流流入有机EL元件21而驱动有机EL元件21的驱动电路。有机EL元件21具有连接至公共的电源供应线34的阴极电极,该公共电源供应线34连接至所有像素20(也被称为“公共配线”)。

用于驱动有机EL元件21的驱动电路具有驱动晶体管22、写入晶体管23、存储电容器24和辅助电容器25。驱动晶体管22和写入晶体管23可以由n-沟道TFT实现。然而,所示的驱动晶体管22写入晶体管23的导电类型的组合仅是一个示例,并且导电类型的组合不限于此。此外,晶体管、存储电容器和有机EL器件等的配线连接关系不限于所公开的关系。

驱动晶体管22的第一电极(源/漏电极)连接至有机EL元件21的阳极电极,并且驱动晶体管22的第二电极(源/漏电极)连接至电源供应线32(321到32m)中的相应一个。

写入晶体管23第一电极(源/漏电极)连接至信号线33(331到33n)中的相应一个,并且写入晶体管23的第二电极(源/漏电极)连接至驱动晶体管22的栅电极。写入晶体管23的栅电极连接至扫描线31(311到31m)中的相应一个。

驱动晶体管22和写入晶体管23中的表述“第一电极”表示电连接至源/漏区的金属配线;表述“第二电极”表示电连接至漏/源区的金属配线。根据第一电极和第二电极之间的电位关系,第一电极用作源电极或漏电极,或第二电极也用作漏电极或源电极。

存储电容器24的第一电极连接至驱动晶体管22的栅电极,并且存储电容器24的第二电极连接至驱动晶体管22的第一电极和有机EL元件21的阳极电极。

辅助电容器25的第一电极连接至有机EL元件21的阳极电极,并且辅助电容器25的第二电极连接至公共电源供应线34。辅助电容器25用作有机EL元件21的等效电容的辅助,从而补偿有机EL元件21的设备电容的不足,并且从而提高对于存储电容器24的视频信号的写入增益。

在这种情况下,虽然辅助电容器25的第二电极连接至公共电源供应线34,但是辅助电容器25的第二电极可以连接至固定电位的节点,而不是公共电源供应线34。辅助电容器25的第二电极与固定电位的节点的连接能够补偿有机EL元件21的电容不足,并且能够实现对于存储电容器24的视频信号的写入增益的提高。

具有上述构造的像素20中的写入晶体管23响应于通过扫描线31从写入扫描电路40提供至写入晶体管23的栅电极的高(即,激活,active)写入扫描信号WS而进入导通状态。然后写入晶体管23采样视频信号(对应于亮度信息)的信号电压Vsig或通过信号线33从信号输出电路60提供的参考电位Vofs,并将采样的信号电压Vsig或参考电压Vofs写入像素20。写入的信号电压Vsig或参考电压Vofs被施加至驱动晶体管22的栅电极并由存储电容器24存储。

当电源供应线32(321到32m)中的相应一个的电源电位DS是第一电源电位Vccp时,驱动晶体管22在饱和区进行操作,其第一电极用作漏电极,而第二电极用作源电极。从而,响应于从电源供应线32提供的电流,驱动晶体管22通过向其提供驱动电流来驱动有机EL元件21发光。更具体地,通过饱和区中的操作,驱动晶体管22向有机EL元件21提供驱动电流,该驱动电流具有与存储电容器24存储的信号电压的电压值相对应的电流值Vsig。驱动电流使有机EL元件21被驱动以进行发光。

当电源电位DS从第一电源电位Vccp切换至第二电源电位Vini时,驱动晶体管22用作开关晶体管,其第一电极用作源电极,其第二电极用作漏电极。通过切换操作,驱动晶体管22停止对有机EL元件21提供驱动电流,从而使有机EL元件21进入非发光状态。即,驱动晶体管22具有用于控制有机EL元件21发光和非发光的晶体管的功能。

驱动晶体管22执行切换操作以提供有机EL元件21非发光的期间(非发光期间),从而使得能够控制有机EL元件21的发光期间和非发光期间的(占空)比率。通过占空控制,能够减少在整个一个显示帧期间像素20的发光中所包括的余像。从而,特别地,运动图像的图像质量进一步提高。

在通过电源供应线32从电源扫描电路50选择性地提供的第一和第二电源供应电压Vccp和Vini中,第一电源电位Vccp是用于将驱动有机EL元件21发光的驱动电流提供至驱动晶体管22的电源电位。第二电源电位Vini是用于反向偏置有机EL元件21的电源电位。第二电源电位Vini被设定为低于参考电压Vofs。例如,第二电源电位Vini被设置为低于Vofs-Vth的电位,优选地,设定为远低于Vofs-Vth的电位,其中Vth表示驱动晶体管22的阈值电压。

[1-2.基本电路操作]

接下来,将参考图3示出的定时波形图和图4A至图5D示出的操作图,说明具有上述构造的有机EL显示装置10的基本电路操作。在图4A至图5D示出的操作图中,写入晶体管23由开关符号表示,以简化说明。

图3的定时波形图示出了扫描线31的电位(写入扫描信号)WS的变化、电源供应线32的电位(电源电位)DS的变化、信号线33的电位(Vsig/Vofs)的变化以及驱动晶体管22的栅电位Vg和源电位Vs的变化。(前一显示帧的发光期间)

在图3的定时波形图中,在时间t11之前的期间是前一显示帧的有机EL元件21的发光期间。在前一显示帧的发光期间中,电源供应线32的电位DS处在第一电源电位(以下称为“高电位”)Vccp,并且写入晶体管23处于非导通状态。

驱动晶体管22被设计为在该点时在饱和区中进行操作。因此,如图4A所示,与驱动晶体管22的栅源电压Vgs相应的驱动电流(漏源电流)Ids通过驱动晶体管22从电源供应线32而提供到有机EL元件21。因此,有机EL元件21的发光亮度与驱动电流Ids的电流值相应。

(阈值校正准备期间)

在时间t11,操作进入了新的显示帧(当前显示帧)以执行线顺序扫描。如图4B所示,电源供应线32的电位DS从高电位Vccp切换到第二电源电位(以下称为“低电位”)Vini,其相对于信号线33的参考电位Vofs远低于Vofs-Vth。

使Vthel为有机EL元件21的阈值电压,并使Vcath为公共电源供应线34的电位(阴极电位)。在这种情况下,在假定低电位Vini满足Vini<Vthel+Vcath时,驱动晶体管22的源电位Vs基本上等于低电位Vini。因此,有机EL元件21被置于反向偏置状态并且停止发光。

接下来,在时间t12,扫描线31的电位WS从低电位侧向高电位侧移动,从而写入晶体管23被置于导通状态,如图4C所示。在该点,因为参考电位Vofs从信号输出电路60提供到信号线33,所以驱动晶体管22的栅电位Vg用作参考电位Vofs。驱动晶体管22的源电位Vs等于远低于参考电位Vofs的电位Vini,即等于低电位Vini。

在该点,驱动晶体管22的栅源电压Vgs等于Vofs-Vini。在这种情况下,除非Vofs-Vini远大于驱动晶体管22的阈值电压Vth,否则难以执行下述的阈值校正处理。因此,执行设置从而满足Vofs-Vini>Vth表达的电位关系。

将驱动晶体管22的栅电位Vg固定(设置)为参考电位Vofs并且将源电位Vs固定为低电位Vini的初始化处理是执行下述的阈值校正处理(阈值校正操作)之前的准备处理(阈值校正准备)。这样,参考电位Vofs和低电位Vini用作驱动晶体管22的栅电位Vg和源电位Vs的初始化电位。

(阈值校正期间)

接下来,在时间t13,电源供应线32的电位DS从低电位Vini切换到高电位Vccp,如图4D所示,并且当驱动晶体管22的栅电位Vg维持在参考电压Vofs时,开始阈值校正处理。即,驱动晶体管22的源电位Vs开始向从栅电位Vg中减去驱动晶体管22的阈值电压Vth获得的电位增加。

在这里,参考驱动晶体管22的栅电位Vg的初始化电位Vofs,将源电位Vs向从初始化电位Vofs中减去驱动晶体管22的阈值电压Vth所获得的电位的处理,为便于说明称为“阈值校正处理”。在阈值校正处理进行时,驱动晶体管22的栅源电压Vgs最后设置成驱动晶体管22的阈值电压Vth。与阈值电压Vth相对应的电压由存储电容器24存储。

在执行阈值校正处理的期间中(即,在阈值校正期间中),公共电源供应线34的电位Vcath被设置为使得有机EL元件21被置于截止状态,从而使电流流入存储电容器24,并防止电流流入有机EL元件21。

接下来,在时间t14,扫描线31的电位WS向低电位侧移动,从而写入晶体管23被置于非导通状态,如图5A所示。在该点,驱动晶体管22的栅电极与信号线33电分离,从而驱动晶体管22的栅电极进入浮置状态。然而,因为栅源电压Vgs等于驱动晶体管22的阈值电压Vth,所以驱动晶体管22处于截止状态。由此,几乎没有漏源电流Ids流入驱动晶体管22。

(信号写入和迁移率校正期间)

接下来,在时间t15,如图5B所示,信号线33的电位从参考电位Vofs切换至视频信号的信号电压Vsig。此后,如图5C所示,在时间t16,扫描线31的电位WS向高电位侧移动,从而写入晶体管23进入导通状态,从而采样视频信号的信号电压Vsig并将信号电压Vsig写入像素20。

在写入晶体管23写入信号电压Vsig时,驱动晶体管22的栅电位Vg变得等于信号电压Vsig。当驱动晶体管22通过视频信号的信号电压Vsig被驱动时,驱动晶体管22的阈值电压Vth被与存储电容器24储存的阈值电压Vth相对应的电压所抵消。阈值抵消的原理的详细情况说明如下。

在该点,有机EL元件21处于截止状态(高阻抗状态)。由此,根据视频信号的信号电压Vsig从电源供应线32流入驱动晶体管22的电流(漏源电流Ids)流入有机EL元件21的等效电容器和辅助电容器25。从而,有机EL元件21的等效电容器和辅助电容器25的充电开始。

作为有机EL元件21的等效电容器以及辅助电容器25充电的结果,随着时间流逝驱动晶体管22的源电位Vs增加。因为像素的驱动晶体管22的阈值电压Vth的变化在该点已经被抵消,所以驱动晶体管22的漏源电流Ids取决于驱动晶体管22的迁移率μ。驱动晶体管22的迁移率μ指的是包括在驱动晶体管22的沟道中的半导体薄膜的迁移率。

现在假定由存储电容器24储存的电压Vgs和视频信号的信号电压Vsig的比率(该比率称为“写入增益G”)是1(理想值)。在这种情况下,驱动晶体管22的源电位Vs增加到由Vofs-Vth+ΔV表达的电位,从而驱动晶体管22的栅源电压Vgs达到由Vsig-Vofs+Vth-ΔV表达的值。

即,驱动晶体管的22源电位Vs的增加ΔV起作用,以使得其从存储电容器24储存的电压(Vsig-Vofs+Vth)中被减去,即使得存储电容器24中的电荷被放电。换句话说,将与源电位Vs的增加ΔV相对应的负反馈施加至存储电容器24。这样,源电位Vs的增加ΔV与负反馈的量相对应。

当具有与流入驱动晶体管22的漏源电流Ids相对应的负反馈的量ΔV的负反馈以上述方式被施加于栅源电压Vgs时,能够消除驱动晶体管22的漏源电流Ids对迁移率μ的依赖。该用于取消对迁移率μ的依赖的处理是用于校正各像素的驱动晶体管22的迁移率μ的变化的迁移率校正处理。

更具体地说,写入驱动晶体管22的栅电极的视频信号的信号幅度Vin(=Vsig-Vofs)越高,漏源电流Ids越大。这样,负反馈的量ΔV的绝对值也增大。因此,根据发光亮度水平执行迁移率校正处理。

当视频信号的信号幅度Vin恒定时,负反馈的量ΔV的绝对值随着驱动晶体管22的迁移率μ增大。因此,各个像素的迁移率μ的变化能减少或消除。即,负反馈的量ΔV也被称为“迁移率校正处理的校正量”。迁移率校正的原理的详细情况说明如下。

(发光期间)

接下来,在时间t17,扫描线31的电位WS向低电位侧移动,从而写入晶体管23被置于非导通状态,如图5D所示。因此,驱动晶体管22的栅电极与信号线33电分离,从而驱动晶体管22的栅电极进入浮置状态。

在这种情况下,在驱动晶体管22的栅电极处于浮置状态时,因为存储电容器24连接在驱动晶体管22的栅极和源极之间,所以栅电位Vg也与驱动晶体管22的源电位Vs的变化联动地变化。

驱动晶体管22的栅电位Vg与源电位Vs的变化联动地变化的该操作,即当维持存储电容器24中存储的栅源电压Vgs时,栅电位Vg和源电位Vs增加的操作在本文中被称为“自举操作”。

在驱动晶体管22的栅电极进入浮置状态的同时,驱动晶体管的漏源电流Ids22开始流入有机EL元件21,从而有机EL元件21的阳极电位响应于漏源电流Ids而增加。

当有机EL元件21的阳极电位超过Vthel+Vcath时,驱动电流开始流入有机EL元件21,从而使有机EL元件21开始发光。有机EL元件21的阳极电位的增加,是因为驱动晶体管22的源电位Vs的增加。当驱动晶体管22的源电位Vs增加时,存储电容器24的自举操作使驱动晶体管22的栅电位Vg与源电位Vs联动地增加。

在自举电路的增益假定为1(理想值)时,栅电位Vg的增加量等于源电位Vs的增加量。因此,在发光期间中,驱动晶体管22的栅源电压Vgs恒定维持在Vsig-Vofs+Vth-ΔV。在时间t18,信号线33的电位从视频信号的信号电压Vsig切换至参考电压Vofs。

在上述的一系列电路操作中,阈值校正准备、阈值校正、信号电压Vsig的写入(信号写入)以及迁移率校正的处理操作在一个水平扫描期间(1H)内执行。信号写入和迁移率校正的处理操作在时间t16到时间t17的期间内并行地执行。

[分割阈值校正]

虽然上面给出了利用仅执行阈值校正处理一次的驱动方法的实例的说明,但是该驱动方法仅仅是一个示例,而且也不限于此。例如也可以采用用于执行所谓“分割阈值校正”的驱动方法。在分割阈值校正中,除与迁移率校正和信号写入处理联动地执行阈值校正处理的1H期间以外,在1H期间之前,多次执行阈值校正处理,即以分割方式在多个水平扫描期间内执行阈值校正处理。

通过分割阈值校正的驱动方法,即使当分配给一个水平扫描期间的时间由于更高分辨率的像素数量增加而减少时,也能够在阈值校正期间的多个扫描期间内确保足够的时间量。因此,由于即使当分配给一个水平扫描期间的时间减少时也能够确保足够的时间量作为阈值校正期间,所以能够可靠地执行阈值校正处理。

[阈值消除的原理]

现在将说明驱动晶体管22的阈值消除(抵消,cancellation)(即阈值校正)的原理。因为驱动晶体管22设计为在饱和区中操作,所以其用作恒定电流源。因此,一定量的漏源电流(驱动电流)Ids从驱动晶体管22流至有机EL元件21,并给出为:

Ids=(1/2)·μ(W/L)Cox(Vgs-Vth)2 (1)

其中,w表示驱动晶体管22的沟道宽度,L表示沟道长度,Cox表示每单位面积的栅电容。

图6A是示出了驱动晶体管22的漏源电流Ids对栅源电压Vgs的特性的示图。如图6A所示,如果不对各个像素的驱动晶体管22的阈值电压Vth的变化执行消除处理(校正处理),则当阈值电压Vth是Vth1时,对应于栅源电压Vgs的漏源电流Ids成为Ids1。

相反,当阈值电压Vth是Vth2(Vth2>Vth1)时,对应于相同的栅源电压Vgs的漏源电流Ids变为Ids2(Ids2<Ids1)。即,在驱动晶体管22的阈值电压Vth变化时,即使当栅源电压Vgs恒定时,漏源电流Ids也变化。

另一方面,在具有上述构造的像素(像素电路)20中,如上所述,在发光期间的驱动晶体管22的栅源电压Vgs表达为Vsig-Vofs+Vth-ΔV。这样,将该表达式代入到上述等式(1)生成如下给出的漏源电流Ids:

Ids=(1/2)·μ(W/L)Cox(Vsig-Vofs-ΔV)2 (2)

即,驱动晶体管22的阈值电压Vth的项被消除,使得从驱动晶体管22提供到有机EL元件21的漏源电流Ids不取决于驱动晶体管22的阈值电压Vth。因此,即使当驱动晶体管22的阈值电压Vth由于驱动晶体管22制造处理的变化、老化等对于各个像素变化时,漏源电流Ids也不变。因此,有机EL元件21的发光亮度能够维持恒定。

[迁移率校正的原理]

接下来将说明驱动晶体管22的迁移率校正的原理。图6B是示出了驱动晶体管22的迁移率μ较大的像素A与驱动晶体管22的迁移率μ较小的像素B之间的比较的特征曲线的示图。当驱动晶体管22通过多晶硅TFT等实现时,发生像素的迁移率μ的变化,如在像素A和B中那样。

现在给出这样的实例的说明,其中,当像素中A和B的迁移率μ变化时,同样水平的信号幅度Vin(=Vsig-Vofs)被写入像素A和B的驱动晶体管22的栅电极。在这种情况下,如果不对迁移率μ执行校正,则在流经具有大的迁移率μ的像素A的漏源电流Ids1′与流经具有小的迁移率μ的像素B的漏源电流Ids2′之间产生大的差异。当由于像素的迁移率μ的变化而在像素的漏源电流Ids之间产生大的差异时,画面的均匀性被损坏。

如上述等式(1)所给出的晶体管特性所表明的,漏源电流Ids随着迁移率μ增大而增大。因此,随着迁移率μ增大,负反馈的量ΔV增大。如图6B所示,具有大的迁移率μ的像素A的负反馈的量ΔV1大于具有小的迁移率μ的像素B的负反馈的量ΔV2。

因此,当执行迁移率校正处理,使得将具有与驱动晶体管22的漏源电流Ids相对应的反馈的量ΔV的负反馈施加至栅源电压Vgs时,随着迁移率μ增大,施加更大的负反馈量。因此,能够抑制像素的迁移率μ的变化。

更具体地,当对具有较大迁移率μ的像素A执行与负反馈的量ΔV1相对应的校正时,漏源电流Ids显著地从Ids1′减小到Ids1。另一方面,因为具有较小迁移率μ的像素B中的反馈的量ΔV2较小,所以漏源电流Ids从Ids2′减小到Ids2,并且该减小量不那么大。因此,像素A的漏源电流Ids1和像素B的漏源电流Ids2变得基本上彼此相等,从而像素的迁移率μ的变化得以校正。

简言之,当存在具有不同的迁移率μ的像素A和B时,具有较大迁移率μ的像素A的反馈量ΔV1大于具有较小迁移率μ的像素B的反馈量ΔV2。即,像素的迁移率μ越大,反馈量ΔV越大,并且漏源电流Ids减小量越大。

因此,由于将具有与驱动晶体管22的漏源电流Ids相对应的反馈量ΔV的负反馈施加至栅源电压Vgs,使具有不同的迁移率μ的像素的漏源电流Ids的电流值变得彼此相等。因此,能够校正像素的迁移率μ的变化。即,迁移率校正处理是这样的处理,其中,向驱动晶体管22的栅源电压Vgs,即向存储电容器24施加具有与流入驱动晶体管22的电流(漏源电流Ids)相对应的反馈量(校正量)ΔV的负反馈。上述阈值校正和迁移率校正是可在本发明中执行或不执行的操作,并且上述的各种校正、发光等不限于这些操作和定时。

[1-3.底栅结构和顶栅结构]

在具有上述构造的有机EL显示装置10中,像素20中的晶体管,具体地说,构成驱动晶体管22和写入晶体管23的TFT,根据结构广泛地划分为底栅结构和顶栅结构。在底栅结构中,栅电极位于相对于半导体层更靠近基板的一侧。在顶栅结构中,栅电极位于相对于半导体层基板的相反侧。

当具有底栅结构TFT用作像素20中的晶体管时,半导体层和薄绝缘膜位于栅电极的金属层与源/漏电极的金属层之间。因此,栅电极的金属层和源/漏电极的金属层配置为彼此相对,使得利用薄绝缘膜作为电介质的电容器在金属层之间形成。在这些金属层之间利用其间介有的绝缘膜形成的电容器可以用作要制入像素20中的电容元件,例如,作为辅助电容器25,以用作有机EL元件21的等效电容器的辅助。

另一方面,当具有顶栅结构的TFT用作像素20中的晶体管时,在包括晶体管等的电路部上形成绝缘平坦化膜,从而平坦化该电路部的上部,并且在绝缘平坦化膜上形成源/漏电极的金属层。像素20中的晶体管是驱动晶体管22的情况将参考图7更详细地说明。

如图7所示,在基板(例如玻璃基板71)上形成驱动晶体管22的半导体层221。半导体层221的中心区用作沟道区222,并且沟道区222的相反两端用作源/漏区223和224。在半导体层221的沟道区222上沉积栅绝缘膜225,并且在栅绝缘膜225上形成栅电极226。

为了平坦化包括如此形成的驱动晶体管22的TFT电路部的上部,在包括驱动晶体管22的TFT电路部上形成绝缘平坦化膜72。接触孔73和74在绝缘平坦化膜72中形成,从而连通半导体层221的相反两端的相应的源/漏区223和224。源/漏电极227和228在绝缘平坦化膜72上形成,并且接触孔73和74填充有配线材料(电极材料),从而源/漏电极227和228分别与源/漏区223和224电连接。

如上所述,在像素20的晶体管由具有顶栅结构的TFT实现时,绝缘平坦化膜72主要设置用于平坦化。因此,绝缘平坦化膜72的厚度明显地大于栅绝缘膜225的厚度。绝缘平坦化膜72的较大厚度使得难以在栅电极226的金属层和源/漏电极227和228的金属层之间形成电容器。

由于这样的原因,如果要制入像素20中的电容元件可以形成在除这些金属层之间的区域以外的区域中,则能够提高像素20的截面结构的自由度。不仅在具有顶栅结构的TFT用作像素20中的晶体管的情况下,而且在具有底栅结构的TFT用作像素20中的晶体管的情况下,同样如此。

<2.实施方式>

为了提高像素20的截面结构的自由度,本发明的实施方式采用这样的构造,其中,要制入像素20中的电容元件形成在与晶体管的栅电极同一层的金属层和形成有晶体管的源/漏区的半导体层之间。金属层与半导体层之间的电容元件的形成涉及对金属层施加电压。现在将参考图8A至图8C,说明为何将电压施加至金属层从而在金属层和半导体层之间形成电容元件的原因。

图8A示出了诸如驱动像素20的操作的高频率操作期间半导体层和金属层的C-V(电容电压)特性。在图8A的C-V特性中,横轴表示金属层相对于半导体层的电位。纵轴表示比率C/C0,其中C0表示栅绝缘膜的电容,C表示金属层与半导体层之间的电容。

在图8A的C-V特性中,特征曲线与纵轴相交的点A处的C/C0如下给出:

A(C/C0)=1/{1+K0LD/(Ktd)}

其中,K0表示栅绝缘膜的相对介电常数,td表示栅绝缘膜的厚度,K表示半导体的相对介电常数,并且LD表示载流子的屏蔽距离。

现在将通过示例讨论像素20中的晶体管是N沟道MOS晶体管的情况。

对于N沟道MOS晶体管,当相对于半导体层的电压足够高的电压施加至金属层时,电子在半导体层的表面积累,即,在半导体层的表面形成沟道,如图8B(对应于图8A所示的状态1)所示。因此,夹置于半导体层和金属层之间的栅绝缘膜被用作电介质以形成电容器。即,能够在半导体层的表面形成足够量的沟道的电压被施加至金属层。

在图8A的C-V特性中,V1表示使栅绝缘膜的电容C0变得可见的电压值,换句话说,表示作为电介质的栅绝缘膜的电容C0变为等于金属层和半导体层之间的电容C的电压值(即C/C0=1)。另一方面,当相对于半导体层的电压的低的电压施加至金属层时,在半导体层的表面电子耗尽区的面积增加,如图8B所示(其对应于图8A所示的状态2)。这减小半导体层和金属层之间形成并且使用栅绝缘膜作为电介质的电容器的电容值。

上述表明,在金属层和半导体层配置为彼此相对并且栅绝缘膜夹置于其间的像素结构中,对金属层施加电压会使半导体层的表面形成沟道。这使得能够使用栅绝缘膜作为电介质而形成电容器。例如,电容器可以进一步用作要制入像素20中的电容元件,例如,如图2中所示的像素电路中的辅助电容器25。通过这种配置,因为要制入像素20中的电容元件能在除金属层之间区域以外的区域中形成,所以能够提高像素20的截面结构的自由度。

图9是示出了根据本发明的实施方式的像素的截面结构的截面图。图9示出了图2中示出的像素电路的驱动晶体管22和辅助电容器25,即示出了形成在金属层和半导体层之间并且将栅绝缘膜用作电介质的电容器用作辅助电容器25的实例。在图9中,与图7中的同样的部分以同样的参考标号标记。

如上所述,参考图7,包括驱动晶体管22的TFT电路部形成在玻璃基板71上。驱动晶体管22包括,形成在玻璃基板71上的半导体层221、与半导体层221的沟道区222相对设置的栅电极226以及置于半导体层221和栅电极226之间的栅绝缘膜225。在半导体层221中,沟道区222的相反两端分别用作源/漏区223和224。

在包括驱动晶体管22的TFT电路部上形成绝缘平坦化膜72,从而平坦化其上部。在绝缘平坦化膜72上形成包括源/漏电极227和228的配线层。在该示例中,在驱动晶体管22的一侧的源/漏电极228也适于用作有机EL元件21的阳极电极。在包括源/漏电极227和228的配线层上形成窗口绝缘膜75。在窗口绝缘膜75中的开口部(凹部)76中形成有机EL元件21的有机层(未示出),并且在窗口绝缘膜75上形成有机EL元件21的阴极电极(未示出,所有像素共用)。

在具有上述构造的像素结构中,半导体层221设置为在有机EL元件21下部中延伸。半导体层221的一端,即源漏电极224,也用作辅助电容器25的第一电极251。辅助电容器25的第二电极252在与驱动晶体管22的栅电极226的层的同一层中形成,从而与第一电极251相对。在第一电极251和第二电极252之间设置栅绝缘膜253。

如上所述,使得在半导体层221的表面即在第一电极251的表面形成足够量的沟道的电压被施加至作为金属层的第二电极252。因此,电子在半导体层221的表面积累,从而使用栅绝缘膜253作为电介质的电容器形成为用作要制入像素20中的电容元件,即用作该实例中的辅助电容器25。

下面将参考将电压施加至第二电极252的具体实施方式来说明辅助电容器25的第一电极251由半导体层221实现并且辅助电容器25的第二电极252由金属层实现的情况。

[2-1.第一实施方式]

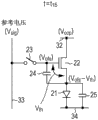

图10是根据第一实施方式的像素电路的电路图。在图10中,与图2中的那些同样的部分以同样的参考标号表示。

根据第一实施方式的像素电路采用如下构造,其中,辅助电容器25的第二电极是开路的而不是连接到接地电平的公共电源供应线34,其不同于图2中所示的像素电路的情况,并且恒定电压Vsub从外部电源(未示出)施加至第二电极。

图11示出了用于将恒定电压Vsub从外部的电源施加至辅助电容器25的第二电极的面板的布局实例。如图11所示,电压供应线L1以行为单位连接到像素电路中辅助电容器25的第二电极。电压供应线L1在像素阵列部30的外围部被捆束到一起,从而形成例如围绕像素阵列部30的环状的公共电源供应线L2。垫片PAD1和PAD2在面板的相反两端(左右端部)形成,并连接到环状的公共电源供应线L2。通过垫片PAD1和PAD2、公共电源供应线L2和电压供应线L1将恒定电压Vsub从面板的外部电源(未示出)提供到辅助电容器25的第二电极。

利用通过在面板的相反两端的垫片PAD1和PAD2将电压施加至环状的公共电源供应线L2的配置,恒定电压Vsub能被稳定地提供到像素中的辅助电容器25的第二电极。该配置能降低像素中的辅助电容器25的电容值Csub的变化,从而像素电路能被辅助电容器25的稳定的电容值Csub所驱动。

在该情况下,优选的是,在高灰度级(high-gradation)视频信号期间,外部提供的恒定电压Vsub相对于驱动晶体管22的源电位具有上述的电压值V1(即,使栅绝缘膜的电容C0变得可见的电压值)或更大的值。如果相对于驱动晶体管22的源电位(即半导体层的电位)的辅助电容器25的第二电极的电位(即金属层的电位)降低,则辅助电容器25的电容值Csub降低,从而像素20的发光亮度降低。

现在将参考图12中示出的定时波形图,说明当相对于半导体层的电位的金属层的电位降低时,亮度降低的机制。

当在信号写入和迁移率校正期间辅助电容器25的电容值Csub小于指定值的情况下,当视频信号的信号电压Vsig写入驱动晶体管22的栅极时源电压Vs的增加变大,如图12的虚线所示。因此,紧接发光之前的驱动晶体管22的栅源电压Vgs降低,从而有机EL元件21的亮度降低。

使Coled为有机EL元件21的等效电容的电容值,并使Cs为存储电容器24的电容值,在信号写入期间的驱动晶体管22的源电压Vs的增加量ΔVs如下给出:

ΔVs=(Vsig-Vofs)/(Cs+Csub+Coled)

如果辅助电容器25的电容值Csub在发光期间从大的电容值到小的电容值大幅变化,这将导致与有机EL元件21的特性向耗尽型特性转变的情况的效果同样的效果(然而,根据第一实施方式的像素电路没有问题,因为其适于将恒定电压Vsub施加至辅助电容器25的第二电极的方式)。因此,各个有机EL元件21的操作点变化。作为像素中的有机EL元件21的操作点变化的结果,发生亮度不均匀。

现在将参考图13和图14说明像素中的有机EL元件21的操作点的变化引起亮度不均匀的机制。

如图13所示,半导体电容的电容特性在阈值电压附近电容值Vth通过电压而大幅变化的点处可变。因此,在辅助电容器25的第二电极的电压Vsub相对于半导体层的电位、即相对于驱动晶体管22的源电位Vs接近阈值电压Vth时,辅助电容器25的电容值Csub大的像素以及电容值Csub小的像素在同一面板中共存。在图13中,辅助电容器25的电容值Csub大的像素的特性用点划线表示,并且辅助电容器25的电容值Csub小的像素的特性用双点划线表示。

对于辅助电容器25的电容值Csub大的像素,因为驱动晶体管22的源电压Vs的增加量小,所以亮度增加,如图14的点划线所示。相反,对于辅助电容器25的电容值Csub小的像素,因为驱动晶体管22的源电压Vs的增加量大,所以亮度降低,如图14的双点划线所示。因此,由于具有高亮度的像素和具有低亮度像素在同一面板中共存,所以亮度的变化被观察为亮度的不均匀。

[2-2.第二实施方式]

接下来将说明根据第二实施方式的像素电路。根据第二实施方式的像素电路采用与图10中所示的根据第一实施方式的像素电路同样的电路构造。即,辅助电容器25的第二电极开路。尽管根据上述第一实施方式的像素电路用于使得将恒定电压Vsub提供至辅助电容器25的第二电极,但是根据第二实施方式的像素电路采用将脉冲电压Vsub施加至辅助电容器25的第二电极的构造。

更具体地,在需要辅助电容器25的电容值Csub保持较大的期间,脉冲电压Vsub增加至高电压VH,如图15中的定时波形所示。上述说明表明,在高灰度级视频信号写入期间,高电压VH相对于驱动晶体管22的源电位具有电压值V1或更大的值。需要辅助电容器25的电容值Csub保持较大的期间是电源供应线32的电位DS是第一电源电位Vccp的期间。在需要辅助电容器25的电容值Csub保持较大的期间以外的期间,脉冲电压Vsub降低为低电压VL。

当电压连续施加至金属层时,在半导体层和金属层之间形成的电容器的特性转变为增强型特性,因而可靠性可能降低。此外,因为特性向增强型特性转变的速度也因像素而异,所以速度的差异引起像素的电容值的变化。

由于这样的原因,将电压Vsub脉冲化,从而使电压不连续地施加至金属层,换句话说,使辅助电容器25两端的电压的施加时间最小化,从而使得能够确保辅助电容器25的可靠性。

特别地,在有机EL元件21不发光的期间,驱动晶体管22的源电位Vs成为电源供应线32的电位DS的第二电源电位Vini,从而脉冲电压Vsub的低电压VL用作第二电源电位Vini。如上所述,在需要辅助电容器25的电容值Csub保持较大的期间以外的期间,辅助电容器25的第二电极的电位降低为第二电源电位Vini,从而使辅助电容器25两端的电压达到0V。因为该配置能进一步确保辅助电容器25的可靠性,所以能够防止电容器的可靠性降低造成的亮度不均匀和亮度降低。

图16是示出了根据第二实施方式的示例性驱动定时的定时波形图。图16示出了相对于两个像素行(线)(即第(i-1)像素行和第i像素行)的扫描线31的电位(扫描信号)WS、电源供应线32的电位DS以及脉冲电压Vsub的波形。

如图16所示,期望脉冲电压Vsub对于各条线(各行)偏移1H(一个水平期间),从而与电源供应线32的相应的电位DS同步。如上所述,脉冲电压Vsub的高电压VH在高灰度级视频信号写入期间被设定为相对于驱动晶体管22的源电位具有电压值V1或者更大值的电压,并且低电压VL用作电源供应线32的电位DS的第二电源电位Vini。

图17示出了用于提供脉冲电压Vsub至辅助电容器25的第二电极以及用于实现根据第二实施方式的示例性驱动定时的面板构造的实例。

如图17所示,除写入扫描电路40和电源扫描电路50以外,例如,在显示面板70上设置用于生成辅助电容器25的电容器生成扫描电路80。电容器生成扫描电路80与电源扫描电路50的操作同步,具体地,与电源供应线32的电位DS同步,从而在顺序地扫描像素行的同时顺序地输出脉冲电压Vsub1至Vsubm,从而通过扫描线351到35m将电压Vsub1至Vsubm提供至像素20中的辅助电容器25的第二电极。

(第二实施方式的修改例)

虽然,第二实施方式采用设置用于生成辅助电容器25的专用的电容器生成扫描电路80以实现提供脉冲电压Vsub给辅助电容器25的第二电极的示例性驱动定时,但是也可以采用以下构造作为修改例。即,从使用脉冲电压Vsub的观点,也可以采用这样的构造,其中,如图18所示,属于前一像素行(即紧接的前一行)的电源供应线32的电位DS作为脉冲电压Vsub提供。该构造可以通过将辅助电容器25的第二电极连接到属于前一像素行的电源供应线32来实现。

这是因为,在高灰度级视频信号写入期间,各电源供应线32的电位DS的高电位相对于驱动晶体管22的源电位具有电压值V1或更大的值,电源供应线32的电位DS的低电位是第二电源电位Vini,从而电源供应线32的电位DS满足上述的电压Vsub的电位的条件。在这种情况下,施加至辅助电容器25的第二电极的电压Vsub的定时相对于在第二实施方式的情况下的定时具有1H的偏离。然而,在该1H的偏离被设置为足够小而可忽略时,可以提供与第二实施方式的情况下基本上相同的优点。

<3.应用例>

虽然已经在上述实施方式中说明了本发明应用于具有两个晶体管(即驱动晶体管22和写入晶体管23)和两个电容元件(即存储电容器24和辅助电容器25)的像素电路的实例,但是本发明的应用不局限于像素电路。即,本发明可适用于有更大量的晶体管的像素电路、具有更大量的电容元件的像素电路等。

虽然已经在上述实施方式中说明了本发明应用于有机EL显示装置的实例,但是本发明的应用并不限于此。更具体地说,本发明适用于使用发光亮度根据流过诸如有机EL元件、LED元件和半导体激光器元件的器件的电流值而变化的电流驱动型电光元件(发光元件)的显示装置。除了这样的使用电流驱动型电光元件的显示装置之外,本发明还适用于采用在像素中设置电容元件的构造的显示装置。这样的显示装置的实例包括液晶显示装置和等离子体显示装置。

<4.电子设备>

上述根据本发明的实施方式的显示装置适用于各个领域的电子设备的显示单元(显示装置),其中,输入到电子设备的视频信号或由其产生的视频信号以图像或视频的形式显示。例如,如图19至图23G中所示,本发明适用于诸如电视机、数码相机、视频摄像机、笔记本个人计算机、以及诸如移动电话的移动终端装置的各种类型的电子设备的显示单元。

以上实施方式的说明表明,根据本发明的实施方式的显示装置能够确保在金属层和半导体层之间的电容元件形成期间要制入像素中的电容元件的可靠性,从而使其能够防止亮度不均匀和亮度降低。从而,根据本发明的实施方式的显示装置用作各个领域的电子设备的显示单元能够提供高质量的显示图像。

根据本发明的实施方式的显示装置还能够通过具有密封结构的模块化形式来实现。例如,模块化形式对应于通过向像素阵列部层压由透明玻璃等制成的对向部所形成的显示模块。例如,显示模块还可以设置有用于向/从像素阵列部外部输入/输出信号等的FPC(柔性印刷电路)或电路部。

下面将说明应用本发明实施方式的电子设备的具体实例。

图19是示出了应用本发明实施方式的电视机的外观的透视图。根据本应用例的电视机包括具有前面板102、滤光玻璃103等的视频显示画面部101。该电视机通过使用根据本发明实施方式的显示装置作为视频显示画面部101来制造。

图20A和图20B分别是示出了应用本发明实施方式的数码相机的外观的前透视图和后透视图。根据本应用例的数码相机包括闪光灯发光部111、显示部112、菜单开关113、快门按钮114等。该数码相机通过使用根据本发明实施方式的显示装置作为显示部112来制造。

图21是示出了应用本发明实施方式的笔记本个人计算机的外观的透视图。根据本应用例的笔记本个人计算机具有如下构造,其中,主单元121包括用于输入字符的操作等的键盘122、用于显示图像的显示部123等。该笔记本个人计算机通过使用根据本发明实施方式的显示装置作为显示部123来制造。

图22是示出了应用本发明实施方式的视频摄像机的外观的透视图。根据本应用例的摄像机包括主单元131、设置在其前侧表面的对象拍摄镜头132、用于拍照的启动/停止开关133、显示部134等。该视频摄像机通过使用根据本发明实施方式的显示装置作为显示部134来制造。

图23A至图23G是示出了应用本发明实施方式的移动终端装置(例如,移动电话)的外部视图。具体地,图23A是移动电话打开时的前视图,图23B其侧视图,图23C是移动电话关闭时的前视图,图23D是左侧视图,图23E是右侧视图,图23F是顶视图,图23G是底视图。根据本应用例的移动电话包括上壳体141、下壳体142、结合部(在该情况中为铰接部)143、显示器144、副显示器145、图片灯146、摄像头147等。根据本应用例的移动电话使用根据本发明实施方式的显示装置作为显示器144和/或子显示器145来制造。

<5.本发明的构造>

(1)一种显示装置,包括:

具有电光元件和晶体管的像素,各个像素具有在与所述晶体管的栅电极同一层的金属层与形成有所述晶体管的源区和漏区的半导体层之间通过向所述金属层施加电压而形成的电容元件。

(2)根据(1)所述的显示装置,其中,施加至所述金属层的所述电压能够在所述半导体层的表面形成沟道。

(3)根据(2)所述的显示装置,其中,施加至所述金属层的电压所具有的电压值大于或等于满足C/C0=1的电压值,其中,C0表示所述金属层与所述半导体层之间的电介质的电容,C表示所述金属层与所述半导体层之间的电容。

(4)根据(1)至(3)中的任一项所述的显示装置,其中,各个电容元件用作相应的电光元件的等效电容的辅助。

(5)根据(4)所述的显示装置,其中,各个晶体管与相应的电光元件串联连接以用作用于驱动所述电光元件的驱动晶体管;并且

各个电容元件具有连接至所述驱动晶体管的源/漏电极的第一电极。

(6)根据(5)所述的显示装置,其中,各个电容元件具有被施加恒定电压的第二电极,所述恒定电压作为要施加至相应的金属层的电压。

(7)根据(6)所述的显示装置,其中,所述像素按矩阵形式配置以构成像素阵列部;并且

所述恒定电压通过以行为单位连接到所述电容元件的所述第二电极的电压供应线,施加到所述电容元件的所述第二电极。

(8)根据(7)所述的显示装置,其中,以行为单位连接到所述电容元件的所述第二电极的电压供应线在所述像素阵列部的外围部被捆束,以围绕所述像素阵列部形成环状公共电压供应线;并且

所述恒定电压通过所述环状公共电压供应线和所述电压供应线而施加至所述电容元件的所述第二电极。

(9)根据(8)所述的显示装置,其中,在设置有所述像素阵列部的面板的相对的两个端部处形成焊盘,所述焊盘连接至所述环状公共电压供应线;并且

所述恒定电压通过所述焊盘、所述环状公共电压供应线和所述电压供应线施加至所述电容元件的第二电极。

(10)根据(5)所述的显示装置,其中,各个电容元件具有被施加脉冲电压的第二电极,所述脉冲电压作为要施加至相应的金属层的电压。

(11)根据(10)所述的显示装置,其中,向所述驱动晶体管提供电力的电源供应线的电位能够在用于供应用以驱动所述电光元件发光的电流的第一电源电位和用于反向偏置所述电光元件的第二电源电位之间切换,并且

当所述电源供应线的电位是所述第一电源电位时,所述脉冲电压达到高电位。

(12)根据(11)所述的显示装置,其中,所述脉冲电压的低电位被设置为所述第二电源电位。

(13)根据(10)至(12)中的任一项所述的显示装置,其中,所述像素按矩阵形式配置以构成像素阵列部;并且

所述脉冲电压被逐行施加至所述电容元件的所述第二电极。

(14)根据(13)所述的显示装置,其中,所述脉冲电压从用于逐行扫描所述像素阵列部的扫描电路输出。

(15)根据(13)所述的显示装置,其中,所述脉冲电压通过属于前一像素行的所述电源供应线来提供。

(16)根据(15)所述的显示装置,其中,所述电容元件的第二电极连接至属于所述前一像素行的所述电源供应线。

(17)一种电子设备,包括:

显示装置,所述显示装置具有包括电光元件和晶体管的像素,各个像素具有在与所述晶体管的栅电极同一层的金属层与形成有所述晶体管的源区和漏区的半导体层之间通过向所述金属层施加电压而形成的电容元件

本发明包括于2011年5月10日向日本专利局提交的日本在先专利申请JP2011-105285所披露的主题,将其全部内容结合于此作为参考。

本领域技术人员应当理解,根据设计要求和其他要素,可以进行各种修改、组合、子组合和变形,只要它们在所附权利要求书及其等同物的范围之内。

Claims (18)

1.一种显示装置,包括:

具有电光元件和晶体管的像素,各个像素具有在与所述晶体管的栅电极同一层的金属层与形成有所述晶体管的源区和漏区的半导体层之间通过向所述金属层施加电压而形成的电容元件。

2.根据权利要求1所述的显示装置,其中,施加至所述金属层的所述电压能够在所述半导体层的表面形成沟道。

3.根据权利要求2所述的显示装置,其中,施加至所述金属层的电压所具有的电压值大于或等于满足C/C0=1的电压值,其中,C0表示所述金属层与所述半导体层之间的电介质的电容,C表示所述金属层与所述半导体层之间的电容。

4.根据权利要求1所述的显示装置,其中,各个电容元件用作相应的电光元件的等效电容的辅助。

5.根据权利要求4所述的显示装置,其中,各个晶体管与相应的电光元件串联连接以用作用于驱动所述电光元件的驱动晶体管;并且

各个电容元件具有连接至所述驱动晶体管的源/漏电极的第一电极。

6.根据权利要求5所述的显示装置,其中,各个电容元件具有被施加恒定电压的第二电极,所述恒定电压作为要施加至相应的金属层的电压。

7.根据权利要求6所述的显示装置,其中,所述像素按矩阵形式配置以构成像素阵列部;并且

所述恒定电压通过以行为单位连接到所述电容元件的所述第二电极的电压供应线,施加到所述电容元件的所述第二电极。

8.根据权利要求7所述的显示装置,其中,以行为单位连接到所述电容元件的所述第二电极的电压供应线在所述像素阵列部的外围部被捆束,以围绕所述像素阵列部形成环状公共电压供应线;并且

所述恒定电压通过所述环状公共电压供应线和所述电压供应线而施加至所述电容元件的所述第二电极。

9.根据权利要求8所述的显示装置,其中,在设置有所述像素阵列部的面板的相对的两个端部处形成焊盘,所述焊盘连接至所述环状公共电压供应线;并且

所述恒定电压通过所述焊盘、所述环状公共电压供应线和所述电压供应线施加至所述电容元件的第二电极。

10.根据权利要求5所述的显示装置,其中,各个电容元件具有被施加脉冲电压的第二电极,所述脉冲电压作为要施加至相应的金属层的电压。

11.根据权利要求10所述的显示装置,其中,向所述驱动晶体管提供电力的电源供应线的电位能够在用于供应用以驱动所述电光元件发光的电流的第一电源电位和用于反向偏置所述电光元件的第二电源电位之间切换,并且

当所述电源供应线的电位是所述第一电源电位时,所述脉冲电压达到高电位。

12.根据权利要求11所述的显示装置,其中,所述脉冲电压的低电位被设置为所述第二电源电位。

13.根据权利要求10所述的显示装置,其中,所述像素按矩阵形式配置以构成像素阵列部;并且

所述脉冲电压被逐行施加至所述电容元件的所述第二电极。

14.根据权利要求13所述的显示装置,其中,所述脉冲电压从用于逐行扫描所述像素阵列部的扫描电路输出。

15.根据权利要求13所述的显示装置,其中,所述脉冲电压通过属于前一像素行的所述电源供应线来提供。

16.根据权利要求15所述的显示装置,其中,所述电容元件的第二电极连接至属于所述前一像素行的所述电源供应线。

17.根据权利要求1所述的显示装置,其中,栅绝缘膜夹置于所述半导体层与所述金属层之间以用作电介质。

18.一种电子设备,包括:

显示装置,所述显示装置具有包括电光元件和晶体管的像素,各个像素具有在与所述晶体管的栅电极同一层的金属层与形成有所述晶体管的源区和漏区的半导体层之间通过向所述金属层施加电压而形成的电容元件。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011105285A JP2012237805A (ja) | 2011-05-10 | 2011-05-10 | 表示装置及び電子機器 |

| JP2011-105285 | 2011-05-10 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN102779829A true CN102779829A (zh) | 2012-11-14 |

Family

ID=47124689

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2012101357055A Pending CN102779829A (zh) | 2011-05-10 | 2012-05-03 | 显示装置和电子设备 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20120286275A1 (zh) |

| JP (1) | JP2012237805A (zh) |

| CN (1) | CN102779829A (zh) |

| TW (1) | TWI490835B (zh) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109064974A (zh) * | 2013-05-30 | 2018-12-21 | 三星显示有限公司 | 有机发光二极管显示器及显示设备的像素电路 |

| CN111344774A (zh) * | 2017-11-21 | 2020-06-26 | 索尼半导体解决方案公司 | 像素电路、显示装置和电子设备 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014163972A (ja) * | 2013-02-21 | 2014-09-08 | Sony Corp | 表示装置およびその駆動方法、並びに電子機器 |

| JP6357663B2 (ja) * | 2013-09-06 | 2018-07-18 | 株式会社Joled | 表示装置 |

| JP2018060743A (ja) * | 2016-10-07 | 2018-04-12 | 株式会社ジャパンディスプレイ | 表示装置 |

| WO2019187047A1 (ja) * | 2018-03-30 | 2019-10-03 | シャープ株式会社 | 表示デバイス |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020039814A1 (en) * | 2000-09-29 | 2002-04-04 | Norio Jada | Flat panel display device and method for manufacturing the same |

| CN101154348A (zh) * | 2006-09-29 | 2008-04-02 | 精工爱普生株式会社 | 电光学装置和电子设备 |

| CN101443699A (zh) * | 2006-05-19 | 2009-05-27 | 夏普株式会社 | 显示装置 |

| CN101520985A (zh) * | 2008-02-28 | 2009-09-02 | 索尼株式会社 | 电致发光显示面板、电子设备和电致发光显示面板驱动方法 |

| CN101404140B (zh) * | 2007-08-15 | 2010-12-15 | 索尼株式会社 | 显示设备和电子装置 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0687503B2 (ja) * | 1987-03-11 | 1994-11-02 | 株式会社日立製作所 | 薄膜半導体装置 |

| JP2845303B2 (ja) * | 1991-08-23 | 1999-01-13 | 株式会社 半導体エネルギー研究所 | 半導体装置とその作製方法 |

| JP2002359252A (ja) * | 2000-09-29 | 2002-12-13 | Toshiba Corp | 平面表示装置及びその製造方法 |

| JP4352937B2 (ja) * | 2004-03-03 | 2009-10-28 | セイコーエプソン株式会社 | 電源回路、電気光学装置および電子機器 |

| TWI284246B (en) * | 2004-08-13 | 2007-07-21 | Au Optronics Corp | Pixel structure of a liquid crystal display and fabricating method thereof and liquid crystal display panel |

| JP4969043B2 (ja) * | 2005-02-10 | 2012-07-04 | シャープ株式会社 | アクティブマトリクス型の表示装置およびその走査側駆動回路 |

| FR2890236B1 (fr) * | 2005-08-30 | 2007-11-30 | Commissariat Energie Atomique | Procede de fabrication de circuits en couches minces en silicium amorphe et polycristallin |

| TWI318716B (en) * | 2005-12-12 | 2009-12-21 | Himax Display Inc | Reflective type liquid crystal panel and pixel structure thereof |

| KR101300683B1 (ko) * | 2006-02-06 | 2013-08-26 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| TW200730978A (en) * | 2006-02-08 | 2007-08-16 | Wintek Corp | Active matrix liquid crystal display and pixel structure thereof |

| CN101356652B (zh) * | 2006-06-02 | 2012-04-18 | 日本财团法人高知县产业振兴中心 | 包括由氧化锌构成的氧化物半导体薄膜层的半导体器件及其制造方法 |

| JP2008107785A (ja) * | 2006-09-29 | 2008-05-08 | Seiko Epson Corp | 電気光学装置および電子機器 |

| TWI376556B (en) * | 2007-05-30 | 2012-11-11 | Au Optronics Corp | Pixel structure and method for forming thereof |

| JP2009026586A (ja) * | 2007-07-19 | 2009-02-05 | Sony Corp | 輝点リペア方法、表示パネル及び電子機器 |

| JP2009047766A (ja) * | 2007-08-15 | 2009-03-05 | Sony Corp | 表示装置および電子機器 |

| GB0721567D0 (en) * | 2007-11-02 | 2007-12-12 | Cambridge Display Tech Ltd | Pixel driver circuits |

| TWI360710B (en) * | 2008-02-22 | 2012-03-21 | Au Optronics Corp | Active device array substrate, electro-optical app |

| JP5491833B2 (ja) * | 2008-12-05 | 2014-05-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2010224417A (ja) * | 2009-03-25 | 2010-10-07 | Sony Corp | 表示装置および電子機器 |

| JP5218269B2 (ja) * | 2009-05-13 | 2013-06-26 | ソニー株式会社 | 表示装置および駆動制御方法 |

| KR101137391B1 (ko) * | 2010-03-24 | 2012-04-20 | 삼성모바일디스플레이주식회사 | 박막 트랜지스터를 갖는 기판, 이를 제조하는 방법, 및 상기 박막 트랜지스터를 갖는 기판을 구비하는 유기 발광 표시 장치 |

-

2011

- 2011-05-10 JP JP2011105285A patent/JP2012237805A/ja active Pending

-

2012

- 2012-03-30 TW TW101111521A patent/TWI490835B/zh active

- 2012-04-09 US US13/442,372 patent/US20120286275A1/en not_active Abandoned

- 2012-05-03 CN CN2012101357055A patent/CN102779829A/zh active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020039814A1 (en) * | 2000-09-29 | 2002-04-04 | Norio Jada | Flat panel display device and method for manufacturing the same |

| CN101443699A (zh) * | 2006-05-19 | 2009-05-27 | 夏普株式会社 | 显示装置 |

| CN101154348A (zh) * | 2006-09-29 | 2008-04-02 | 精工爱普生株式会社 | 电光学装置和电子设备 |

| CN101404140B (zh) * | 2007-08-15 | 2010-12-15 | 索尼株式会社 | 显示设备和电子装置 |

| CN101520985A (zh) * | 2008-02-28 | 2009-09-02 | 索尼株式会社 | 电致发光显示面板、电子设备和电致发光显示面板驱动方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109064974A (zh) * | 2013-05-30 | 2018-12-21 | 三星显示有限公司 | 有机发光二极管显示器及显示设备的像素电路 |

| CN109064974B (zh) * | 2013-05-30 | 2021-10-29 | 三星显示有限公司 | 有机发光二极管显示器及显示设备的像素电路 |

| CN111344774A (zh) * | 2017-11-21 | 2020-06-26 | 索尼半导体解决方案公司 | 像素电路、显示装置和电子设备 |

| US11721281B2 (en) | 2017-11-21 | 2023-08-08 | Sony Semiconductor Solutions Corporation | Pixel circuit, display device, and electronic apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012237805A (ja) | 2012-12-06 |

| US20120286275A1 (en) | 2012-11-15 |

| TW201248592A (en) | 2012-12-01 |

| TWI490835B (zh) | 2015-07-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101286524B (zh) | 显示器、制造显示器的方法以及电子设备 | |

| CN102623485B (zh) | 有机电致发光显示器件和电子装置 | |

| US8736521B2 (en) | Display device and electronic apparatus have the same | |

| CN101770745B (zh) | 显示装置、显示装置驱动方法及电子设备 | |

| CN101794550B (zh) | 显示装置和电子设备 | |

| CN101577085B (zh) | 显示设备、显示设备的驱动方法及电子器械 | |

| CN101751854B (zh) | 显示装置、显示装置的像素布局方法以及电子设备 | |

| CN102810292B (zh) | 电光学装置以及电子设备 | |

| CN101783361B (zh) | 显示装置和电子设备 | |

| CN102629448B (zh) | 有机电致发光显示器及电子设备 | |

| US20210366386A1 (en) | Pixel circuit and method of driving the same, display panel | |

| CN102867840A (zh) | 像素电路、显示器、电子装置和像素电路的驱动方法 | |

| CN101599503B (zh) | 显示设备、在显示设备中布线的方法、以及电子设备 | |

| CN102779475A (zh) | 显示装置和显示方法 | |

| CN102779829A (zh) | 显示装置和电子设备 | |

| KR20190046414A (ko) | 박막트랜지스터 어레이 기판 및 그를 포함하는 유기발광표시장치 | |

| CN103680390B (zh) | 显示装置和电子设备 | |

| CN102208165A (zh) | 显示装置和电子设备 | |

| CN102339848A (zh) | 有机电致发光显示器件及其制造方法和电子设备 | |

| CN102194406B (zh) | 显示装置、显示装置的驱动方法和电子装置 | |

| JP5573686B2 (ja) | 有機el表示装置及び電子機器 | |

| CN103996373A (zh) | 显示单元及其驱动方法和电子装置 | |

| CN102592540B (zh) | 有机el显示装置和电子设备 | |

| US20210225990A1 (en) | Display device and electronic apparatus | |

| US20120293397A1 (en) | Bootstrap circuit, inverter circuit, scanning circuit, display device, and electronic apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| ASS | Succession or assignment of patent right |

Owner name: JANPAN ORGANIC RATE DISPLAY CO., LTD. Free format text: FORMER OWNER: SONY CORP Effective date: 20150715 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TA01 | Transfer of patent application right |

Effective date of registration: 20150715 Address after: Tokyo, Japan Applicant after: The special display of the organic thunder of Japan of Co., Ltd. Address before: Tokyo, Japan Applicant before: Sony Corp |

|

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Application publication date: 20121114 |