CN101436430B - 半导体集成电路装置 - Google Patents

半导体集成电路装置 Download PDFInfo

- Publication number

- CN101436430B CN101436430B CN2008101814389A CN200810181438A CN101436430B CN 101436430 B CN101436430 B CN 101436430B CN 2008101814389 A CN2008101814389 A CN 2008101814389A CN 200810181438 A CN200810181438 A CN 200810181438A CN 101436430 B CN101436430 B CN 101436430B

- Authority

- CN

- China

- Prior art keywords

- mentioned

- cpu

- signal

- address

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1039—Read-write modes for single port memories, i.e. having either a random port or a serial port using pipelining techniques, i.e. using latches between functional memory parts, e.g. row/column decoders, I/O buffers, sense amplifiers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

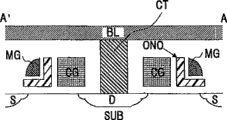

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1075—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for multiport memories each having random access ports and serial ports, e.g. video RAM

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Read Only Memory (AREA)

- Memory System (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007297479 | 2007-11-16 | ||

| JP2007-297479 | 2007-11-16 | ||

| JP2007297479A JP2009123298A (ja) | 2007-11-16 | 2007-11-16 | 半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101436430A CN101436430A (zh) | 2009-05-20 |

| CN101436430B true CN101436430B (zh) | 2012-02-29 |

Family

ID=40303728

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2008101814389A Expired - Fee Related CN101436430B (zh) | 2007-11-16 | 2008-11-13 | 半导体集成电路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7848177B2 (enExample) |

| EP (1) | EP2065893B1 (enExample) |

| JP (1) | JP2009123298A (enExample) |

| CN (1) | CN101436430B (enExample) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101644169B1 (ko) | 2010-04-29 | 2016-08-01 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 이를 포함하는 비휘발성 메모리 시스템 |

| TW201225529A (en) * | 2010-12-03 | 2012-06-16 | Fortune Semiconductor Corp | Test mode controller and electronic apparatus with self-testing thereof |

| US8593878B2 (en) | 2011-11-17 | 2013-11-26 | Macronix International Co., Ltd. | Program method and flash memory using the same |

| CN103514956B (zh) * | 2012-06-15 | 2016-04-13 | 晶豪科技股份有限公司 | 半导体存储器元件及其测试方法 |

| US9190172B2 (en) * | 2013-01-24 | 2015-11-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6359491B2 (ja) * | 2015-06-12 | 2018-07-18 | 東芝メモリ株式会社 | 半導体記憶装置 |

| US11048583B1 (en) * | 2015-09-11 | 2021-06-29 | Green Mountain Semiconductor Inc. | Flexible, low-latency error correction architecture for semiconductor memory products |

| DE102015221064A1 (de) * | 2015-10-28 | 2017-05-04 | Robert Bosch Gmbh | Anordnung aus wenigstens zwei Mikrocontrollern und Verfahren zur Herstellung einer solchen Anordnung |

| KR102557324B1 (ko) * | 2016-02-15 | 2023-07-20 | 에스케이하이닉스 주식회사 | 메모리 장치 |

| KR102682253B1 (ko) * | 2016-11-29 | 2024-07-08 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작방법 |

| US9997212B1 (en) * | 2017-04-24 | 2018-06-12 | Micron Technology, Inc. | Accessing data in memory |

| US10347307B2 (en) * | 2017-06-29 | 2019-07-09 | SK Hynix Inc. | Skew control circuit and interface circuit including the same |

| JP2019040646A (ja) * | 2017-08-22 | 2019-03-14 | 東芝メモリ株式会社 | 半導体記憶装置 |

| US11360704B2 (en) | 2018-12-21 | 2022-06-14 | Micron Technology, Inc. | Multiplexed signal development in a memory device |

| CN111489773B (zh) * | 2019-01-29 | 2023-04-07 | 合肥格易集成电路有限公司 | 一种读取数据的电路、非易失存储器以及读取数据的方法 |

| US11676657B2 (en) * | 2020-04-16 | 2023-06-13 | Mediatek Inc. | Time-interleaving sensing scheme for pseudo dual-port memory |

| US11443823B2 (en) * | 2020-10-29 | 2022-09-13 | SambaNova Systems, Inc. | Method and circuit for scan dump of latch array |

| US12321262B2 (en) * | 2020-12-28 | 2025-06-03 | Kioxia Corporation | Memory system which orders data fetching from a latch circuit during execution of a read operation |

| JP7614966B2 (ja) * | 2021-07-14 | 2025-01-16 | キオクシア株式会社 | 半導体記憶装置 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0562605A2 (en) * | 1992-03-26 | 1993-09-29 | Nec Corporation | Dynamic random access memory device having addressing section and/or data transferring path arranged in pipeline architecture |

| US5375089A (en) * | 1993-10-05 | 1994-12-20 | Advanced Micro Devices, Inc. | Plural port memory system utilizing a memory having a read port and a write port |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2855633B2 (ja) | 1989-02-03 | 1999-02-10 | ミノルタ株式会社 | マルチプロセッサシステムにおけるデュアルポートメモリの故障診断装置 |

| JP2001306307A (ja) | 2000-04-25 | 2001-11-02 | Hitachi Ltd | ファームウェアの処理方法。 |

| JP4704541B2 (ja) * | 2000-04-27 | 2011-06-15 | エルピーダメモリ株式会社 | 半導体集積回路装置 |

| US6246634B1 (en) | 2000-05-01 | 2001-06-12 | Silicon Storage Technology, Inc. | Integrated memory circuit having a flash memory array and at least one SRAM memory array with internal address and data bus for transfer of signals therebetween |

| JP4331966B2 (ja) | 2003-04-14 | 2009-09-16 | 株式会社ルネサステクノロジ | 半導体集積回路 |

| US7349285B2 (en) | 2005-02-02 | 2008-03-25 | Texas Instruments Incorporated | Dual port memory unit using a single port memory core |

| JP2007297479A (ja) | 2006-04-28 | 2007-11-15 | Hitachi Chem Co Ltd | 樹脂組成物及び電気機器絶縁物の製造方法 |

-

2007

- 2007-11-16 JP JP2007297479A patent/JP2009123298A/ja active Pending

-

2008

- 2008-11-12 US US12/269,098 patent/US7848177B2/en not_active Expired - Fee Related

- 2008-11-13 EP EP08253714A patent/EP2065893B1/en not_active Expired - Fee Related

- 2008-11-13 CN CN2008101814389A patent/CN101436430B/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0562605A2 (en) * | 1992-03-26 | 1993-09-29 | Nec Corporation | Dynamic random access memory device having addressing section and/or data transferring path arranged in pipeline architecture |

| US5375089A (en) * | 1993-10-05 | 1994-12-20 | Advanced Micro Devices, Inc. | Plural port memory system utilizing a memory having a read port and a write port |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2065893A1 (en) | 2009-06-03 |

| EP2065893B1 (en) | 2012-06-06 |

| US7848177B2 (en) | 2010-12-07 |

| JP2009123298A (ja) | 2009-06-04 |

| CN101436430A (zh) | 2009-05-20 |

| US20090129173A1 (en) | 2009-05-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101436430B (zh) | 半导体集成电路装置 | |

| US9740431B2 (en) | Memory controller and method for interleaving DRAM and MRAM accesses | |

| CN1134016C (zh) | 动态存储器 | |

| US8837236B2 (en) | Hybrid nonvolatile shadowed DRAM with an overlapping region between a volatile storage die and a nonvolatile storage die | |

| US10068626B2 (en) | Clocked commands timing adjustments in synchronous semiconductor integrated circuits | |

| US8189424B2 (en) | Semiconductor memory device having plurality of types of memories integrated on one chip | |

| TWI441192B (zh) | 快閃記憶體裝置、記憶體裝置以及控制快閃記憶體裝置之方法 | |

| US7369447B2 (en) | Random cache read | |

| TWI376693B (en) | Semiconductor memory device | |

| US8285917B2 (en) | Apparatus for enhancing flash memory access | |

| US10832747B2 (en) | Clocked commands timing adjustments method in synchronous semiconductor integrated circuits | |

| US7240147B2 (en) | Memory decoder and data bus for burst page read | |

| CN107025922A (zh) | 半导体存储器器件 | |

| CN101930798A (zh) | 闪存装置、存储器装置以及控制闪存装置的方法 | |

| JP3334589B2 (ja) | 信号遅延装置及び半導体記憶装置 | |

| CN111386569B (zh) | 波管线 | |

| US11423958B2 (en) | Semiconductor memory device having a first plane and a second plane including respective latch circuits, and first and second FIFO circuits for fetching read data from the latch circuits | |

| CN1647204A (zh) | 存取单端口存储设备的方法,存储器存取设备,集成电路设备和集成电路设备的使用方法 | |

| US6747898B2 (en) | Column decode circuit for high density/high performance memories | |

| JP7618245B2 (ja) | シフト可能メモリ、およびシフト可能メモリを動作させる方法 | |

| JPH0982085A (ja) | 半導体記憶装置 | |

| McIntyre et al. | A 4-MB on-chip L2 cache for a 90-nm 1.6-GHz 64-bit microprocessor | |

| CN112116933B (zh) | 包含同步级的行波流水线 | |

| JP3520259B2 (ja) | 半導体記憶装置およびその動作方法 | |

| US20090285035A1 (en) | Pipelined wordline memory architecture |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| ASS | Succession or assignment of patent right |

Owner name: RENESAS ELECTRONICS CO., LTD. Free format text: FORMER OWNER: RENESAS TECHNOLOGY CORP. Effective date: 20100925 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TA01 | Transfer of patent application right |

Effective date of registration: 20100925 Address after: Kanagawa Applicant after: Renesas Electronics Corporation Address before: Tokyo, Japan, Japan Applicant before: Renesas Technology Corp. |

|

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20120229 Termination date: 20131113 |