CN100447978C - 在铜晶种沉积后的植入方法 - Google Patents

在铜晶种沉积后的植入方法 Download PDFInfo

- Publication number

- CN100447978C CN100447978C CNB028234413A CN02823441A CN100447978C CN 100447978 C CN100447978 C CN 100447978C CN B028234413 A CNB028234413 A CN B028234413A CN 02823441 A CN02823441 A CN 02823441A CN 100447978 C CN100447978 C CN 100447978C

- Authority

- CN

- China

- Prior art keywords

- layer

- barrier

- implant

- forming

- seed

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

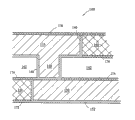

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

- H01L21/76846—Layer combinations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76855—After-treatment introducing at least one additional element into the layer

- H01L21/76859—After-treatment introducing at least one additional element into the layer by ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76867—Barrier, adhesion or liner layers characterized by methods of formation other than PVD, CVD or deposition from a liquids

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76871—Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Other Surface Treatments For Metallic Materials (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/994,358 | 2001-11-26 | ||

| US09/994,358 US6703307B2 (en) | 2001-11-26 | 2001-11-26 | Method of implantation after copper seed deposition |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1592964A CN1592964A (zh) | 2005-03-09 |

| CN100447978C true CN100447978C (zh) | 2008-12-31 |

Family

ID=25540575

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028234413A Expired - Fee Related CN100447978C (zh) | 2001-11-26 | 2002-10-11 | 在铜晶种沉积后的植入方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6703307B2 (enExample) |

| EP (1) | EP1449248A2 (enExample) |

| JP (1) | JP4685352B2 (enExample) |

| KR (1) | KR20040064288A (enExample) |

| CN (1) | CN100447978C (enExample) |

| AU (1) | AU2002340177A1 (enExample) |

| WO (1) | WO2003046978A2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI584441B (zh) * | 2013-02-26 | 2017-05-21 | 旺宏電子股份有限公司 | 內連線結構及其形成方法 |

Families Citing this family (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6776792B1 (en) | 1997-04-24 | 2004-08-17 | Advanced Cardiovascular Systems Inc. | Coated endovascular stent |

| US6783793B1 (en) | 2000-10-26 | 2004-08-31 | Advanced Cardiovascular Systems, Inc. | Selective coating of medical devices |

| US6565659B1 (en) | 2001-06-28 | 2003-05-20 | Advanced Cardiovascular Systems, Inc. | Stent mounting assembly and a method of using the same to coat a stent |

| US7049226B2 (en) * | 2001-09-26 | 2006-05-23 | Applied Materials, Inc. | Integration of ALD tantalum nitride for copper metallization |

| US7115991B1 (en) * | 2001-10-22 | 2006-10-03 | Lsi Logic Corporation | Method for creating barriers for copper diffusion |

| US6835655B1 (en) * | 2001-11-26 | 2004-12-28 | Advanced Micro Devices, Inc. | Method of implanting copper barrier material to improve electrical performance |

| TW571389B (en) * | 2001-12-25 | 2004-01-11 | Nec Electronics Corp | A copper interconnection and the method for fabricating the same |

| US7115498B1 (en) * | 2002-04-16 | 2006-10-03 | Advanced Micro Devices, Inc. | Method of ultra-low energy ion implantation to form alloy layers in copper |

| US6861349B1 (en) * | 2002-05-15 | 2005-03-01 | Advanced Micro Devices, Inc. | Method of forming an adhesion layer with an element reactive with a barrier layer |

| US6992004B1 (en) * | 2002-07-31 | 2006-01-31 | Advanced Micro Devices, Inc. | Implanted barrier layer to improve line reliability and method of forming same |

| US6861758B2 (en) * | 2002-08-30 | 2005-03-01 | Intel Corporation | Structure and manufacturing process of localized shunt to reduce electromigration failure of copper dual damascene process |

| US20040229453A1 (en) * | 2003-05-15 | 2004-11-18 | Jsr Micro, Inc. | Methods of pore sealing and metal encapsulation in porous low k interconnect |

| US7198675B2 (en) | 2003-09-30 | 2007-04-03 | Advanced Cardiovascular Systems | Stent mandrel fixture and method for selectively coating surfaces of a stent |

| US7169706B2 (en) * | 2003-10-16 | 2007-01-30 | Advanced Micro Devices, Inc. | Method of using an adhesion precursor layer for chemical vapor deposition (CVD) copper deposition |

| US6998343B1 (en) * | 2003-11-24 | 2006-02-14 | Lsi Logic Corporation | Method for creating barrier layers for copper diffusion |

| US7563324B1 (en) | 2003-12-29 | 2009-07-21 | Advanced Cardiovascular Systems Inc. | System and method for coating an implantable medical device |

| DE102004003863B4 (de) | 2004-01-26 | 2009-01-29 | Advanced Micro Devices, Inc., Sunnyvale | Technik zur Herstellung eingebetteter Metallleitungen mit einer erhöhten Widerstandsfähigkeit gegen durch Belastung hervorgerufenen Materialtransport |

| US7553377B1 (en) | 2004-04-27 | 2009-06-30 | Advanced Cardiovascular Systems, Inc. | Apparatus and method for electrostatic coating of an abluminal stent surface |

| US7632307B2 (en) | 2004-12-16 | 2009-12-15 | Advanced Cardiovascular Systems, Inc. | Abluminal, multilayer coating constructs for drug-delivery stents |

| US7329599B1 (en) * | 2005-03-16 | 2008-02-12 | Advanced Micro Devices, Inc. | Method for fabricating a semiconductor device |

| US20060267113A1 (en) * | 2005-05-27 | 2006-11-30 | Tobin Philip J | Semiconductor device structure and method therefor |

| US7867547B2 (en) | 2005-12-19 | 2011-01-11 | Advanced Cardiovascular Systems, Inc. | Selectively coating luminal surfaces of stents |

| US8069814B2 (en) | 2006-05-04 | 2011-12-06 | Advanced Cardiovascular Systems, Inc. | Stent support devices |

| US8603530B2 (en) | 2006-06-14 | 2013-12-10 | Abbott Cardiovascular Systems Inc. | Nanoshell therapy |

| US8048448B2 (en) | 2006-06-15 | 2011-11-01 | Abbott Cardiovascular Systems Inc. | Nanoshells for drug delivery |

| US8017237B2 (en) | 2006-06-23 | 2011-09-13 | Abbott Cardiovascular Systems, Inc. | Nanoshells on polymers |

| US20080157375A1 (en) * | 2006-12-27 | 2008-07-03 | Dongbu Hitek Co., Ltd. | Semiconductor device having a metal interconnection and method of fabricating the same |

| US7750852B2 (en) * | 2007-04-13 | 2010-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8048441B2 (en) | 2007-06-25 | 2011-11-01 | Abbott Cardiovascular Systems, Inc. | Nanobead releasing medical devices |

| US20100007022A1 (en) * | 2007-08-03 | 2010-01-14 | Nobuaki Tarumi | Semiconductor device and manufacturing method thereof |

| US7772110B2 (en) * | 2007-09-28 | 2010-08-10 | Tokyo Electron Limited | Electrical contacts for integrated circuits and methods of forming using gas cluster ion beam processing |

| JP2009099585A (ja) * | 2007-10-12 | 2009-05-07 | Panasonic Corp | 埋め込み配線の形成方法 |

| US7737013B2 (en) * | 2007-11-06 | 2010-06-15 | Varian Semiconductor Equipment Associates, Inc. | Implantation of multiple species to address copper reliability |

| KR101433899B1 (ko) * | 2008-04-03 | 2014-08-29 | 삼성전자주식회사 | 기판 식각부의 금속층 형성방법 및 이를 이용하여 형성된금속층을 갖는 기판 및 구조물 |

| CN101661922B (zh) * | 2009-07-30 | 2014-04-09 | 广州市香港科大霍英东研究院 | 一种高深宽比硅通孔铜互连线及其制备方法 |

| EP2761663B1 (en) * | 2011-09-29 | 2016-09-14 | Intel Corporation | Method of depositing electropositive metal containing layers for semiconductor applications |

| US20140273436A1 (en) * | 2013-03-15 | 2014-09-18 | Globalfoundries Inc. | Methods of forming barrier layers for conductive copper structures |

| DE102014205234A1 (de) * | 2014-03-20 | 2015-09-24 | Bayerische Motoren Werke Aktiengesellschaft | Separator für eine galvanische Zelle, galvanische Zelle umfassend den Separator, Batterie enthaltend wenigstens zwei galvanische Zellen, mobile Konsumer-Geräte und Kraftfahrzeug mit der Batterie |

| KR102211741B1 (ko) * | 2014-07-21 | 2021-02-03 | 삼성전기주식회사 | 인쇄회로기판 및 인쇄회로기판의 제조 방법 |

| CN105899003B (zh) | 2015-11-06 | 2019-11-26 | 武汉光谷创元电子有限公司 | 单层电路板、多层电路板以及它们的制造方法 |

| US9520284B1 (en) * | 2015-11-13 | 2016-12-13 | Varian Semiconductor Equipment Associates, Inc. | Ion beam activated directional deposition |

| US9947621B2 (en) | 2016-08-05 | 2018-04-17 | International Business Machines Corporation | Structure and method to reduce copper loss during metal cap formation |

| CN109216261B (zh) * | 2017-07-03 | 2021-07-09 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| US10763168B2 (en) | 2017-11-17 | 2020-09-01 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor structure with doped via plug and method for forming the same |

| US20240222191A1 (en) * | 2022-12-28 | 2024-07-04 | Winbond Electronics Corp. | Semiconductor structure and method of forming the same |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5899740A (en) * | 1997-03-04 | 1999-05-04 | Samsung Electronics Co., Ltd. | Methods of fabricating copper interconnects for integrated circuits |

| US6015749A (en) * | 1998-05-04 | 2000-01-18 | Taiwan Semiconductor Manufacturing Company | Method to improve adhesion between copper and titanium nitride, for copper interconnect structures, via the use of an ion implantation procedure |

| US6169041B1 (en) * | 1999-11-01 | 2001-01-02 | United Microelectronics Corp. | Method for enhancing the reliability of a dielectric layer of a semiconductor wafer |

| WO2001054192A1 (en) * | 2000-01-18 | 2001-07-26 | Micron Technology, Inc. | Process for providing seed layers for aluminium, copper, gold and silver metallurgy |

| US6268291B1 (en) * | 1995-12-29 | 2001-07-31 | International Business Machines Corporation | Method for forming electromigration-resistant structures by doping |

Family Cites Families (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4908275A (en) | 1987-03-04 | 1990-03-13 | Nippon Mining Co., Ltd. | Film carrier and method of manufacturing same |

| JPH01265540A (ja) * | 1988-04-15 | 1989-10-23 | Sony Corp | 半導体装置の製造方法 |

| JPH0750697B2 (ja) | 1989-02-20 | 1995-05-31 | 株式会社東芝 | 半導体装置の製造方法 |

| US5243222A (en) | 1991-04-05 | 1993-09-07 | International Business Machines Corporation | Copper alloy metallurgies for VLSI interconnection structures |

| JP2534434B2 (ja) | 1992-04-30 | 1996-09-18 | インターナショナル・ビジネス・マシーンズ・コーポレイション | 耐酸化性化合物およびその製造方法 |

| KR960010056B1 (ko) | 1992-12-10 | 1996-07-25 | 삼성전자 주식회사 | 반도체장치 및 그 제조 방법 |

| US5654245A (en) | 1993-03-23 | 1997-08-05 | Sharp Microelectronics Technology, Inc. | Implantation of nucleating species for selective metallization and products thereof |

| EP0751567B1 (en) | 1995-06-27 | 2007-11-28 | International Business Machines Corporation | Copper alloys for chip interconnections and method of making |

| US5770517A (en) | 1997-03-21 | 1998-06-23 | Advanced Micro Devices, Inc. | Semiconductor fabrication employing copper plug formation within a contact area |

| US5969422A (en) | 1997-05-15 | 1999-10-19 | Advanced Micro Devices, Inc. | Plated copper interconnect structure |

| US6069068A (en) | 1997-05-30 | 2000-05-30 | International Business Machines Corporation | Sub-quarter-micron copper interconnections with improved electromigration resistance and reduced defect sensitivity |

| US5821168A (en) | 1997-07-16 | 1998-10-13 | Motorola, Inc. | Process for forming a semiconductor device |

| US5882738A (en) | 1997-12-19 | 1999-03-16 | Advanced Micro Devices, Inc. | Apparatus and method to improve electromigration performance by use of amorphous barrier layer |

| US6344413B1 (en) | 1997-12-22 | 2002-02-05 | Motorola Inc. | Method for forming a semiconductor device |

| KR100404649B1 (ko) | 1998-02-23 | 2003-11-10 | 가부시끼가이샤 히다치 세이사꾸쇼 | 반도체장치 및 그 제조방법 |

| JP3955386B2 (ja) | 1998-04-09 | 2007-08-08 | 富士通株式会社 | 半導体装置及びその製造方法 |

| US6156638A (en) | 1998-04-10 | 2000-12-05 | Micron Technology, Inc. | Integrated circuitry and method of restricting diffusion from one material to another |

| US6181012B1 (en) | 1998-04-27 | 2001-01-30 | International Business Machines Corporation | Copper interconnection structure incorporating a metal seed layer |

| JPH11330001A (ja) * | 1998-05-21 | 1999-11-30 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| US6461675B2 (en) | 1998-07-10 | 2002-10-08 | Cvc Products, Inc. | Method for forming a copper film on a substrate |

| JP2000164717A (ja) * | 1998-09-25 | 2000-06-16 | Sanyo Electric Co Ltd | 半導体装置及び半導体装置の製造方法 |

| US6144096A (en) | 1998-10-05 | 2000-11-07 | Advanced Micro Devices, Inc. | Low resistivity semiconductor barrier layers and manufacturing method therefor |

| US6117770A (en) | 1998-10-08 | 2000-09-12 | Advanced Micro Devices, Inc. | Method for implanting semiconductor conductive layers |

| KR100385042B1 (ko) | 1998-12-03 | 2003-06-18 | 인터내셔널 비지네스 머신즈 코포레이션 | 내 일렉트로 마이그레이션의 구조물을 도핑으로 형성하는 방법 |

| US6294836B1 (en) | 1998-12-22 | 2001-09-25 | Cvc Products Inc. | Semiconductor chip interconnect barrier material and fabrication method |

| US6096648A (en) | 1999-01-26 | 2000-08-01 | Amd | Copper/low dielectric interconnect formation with reduced electromigration |

| KR100309642B1 (ko) | 1999-01-29 | 2001-09-26 | 김영환 | 반도체장치의 콘택 형성방법 |

| JP3910752B2 (ja) | 1999-03-23 | 2007-04-25 | 株式会社東芝 | 半導体装置の製造方法 |

| US6521532B1 (en) | 1999-07-22 | 2003-02-18 | James A. Cunningham | Method for making integrated circuit including interconnects with enhanced electromigration resistance |

| US6440849B1 (en) | 1999-10-18 | 2002-08-27 | Agere Systems Guardian Corp. | Microstructure control of copper interconnects |

| WO2001039250A2 (en) | 1999-11-24 | 2001-05-31 | Honeywell International Inc. | Conductive interconnection |

| US6420262B1 (en) | 2000-01-18 | 2002-07-16 | Micron Technology, Inc. | Structures and methods to enhance copper metallization |

| US6225221B1 (en) * | 2000-02-10 | 2001-05-01 | Chartered Semiconductor Manufacturing Ltd. | Method to deposit a copper seed layer for dual damascene interconnects |

| US6627995B2 (en) | 2000-03-03 | 2003-09-30 | Cvc Products, Inc. | Microelectronic interconnect material with adhesion promotion layer and fabrication method |

| US6410383B1 (en) | 2000-03-16 | 2002-06-25 | Sharp Laboratories Of America, Inc. | Method of forming conducting diffusion barriers |

| US6426289B1 (en) | 2000-03-24 | 2002-07-30 | Micron Technology, Inc. | Method of fabricating a barrier layer associated with a conductor layer in damascene structures |

| KR100775159B1 (ko) | 2000-05-15 | 2007-11-12 | 에이에스엠 인터내셔널 엔.붸. | 집적회로의 생산 공정 |

| US6749699B2 (en) | 2000-08-09 | 2004-06-15 | Olin Corporation | Silver containing copper alloy |

| JP2002075994A (ja) | 2000-08-24 | 2002-03-15 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US6977224B2 (en) | 2000-12-28 | 2005-12-20 | Intel Corporation | Method of electroless introduction of interconnect structures |

| US6534865B1 (en) * | 2001-06-12 | 2003-03-18 | Advanced Micro Devices, Inc. | Method of enhanced fill of vias and trenches |

-

2001

- 2001-11-26 US US09/994,358 patent/US6703307B2/en not_active Expired - Fee Related

-

2002

- 2002-10-11 JP JP2003548300A patent/JP4685352B2/ja not_active Expired - Fee Related

- 2002-10-11 EP EP02778522A patent/EP1449248A2/en not_active Withdrawn

- 2002-10-11 WO PCT/US2002/032554 patent/WO2003046978A2/en not_active Ceased

- 2002-10-11 AU AU2002340177A patent/AU2002340177A1/en not_active Abandoned

- 2002-10-11 KR KR10-2004-7007988A patent/KR20040064288A/ko not_active Ceased

- 2002-10-11 CN CNB028234413A patent/CN100447978C/zh not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6268291B1 (en) * | 1995-12-29 | 2001-07-31 | International Business Machines Corporation | Method for forming electromigration-resistant structures by doping |

| US5899740A (en) * | 1997-03-04 | 1999-05-04 | Samsung Electronics Co., Ltd. | Methods of fabricating copper interconnects for integrated circuits |

| US6015749A (en) * | 1998-05-04 | 2000-01-18 | Taiwan Semiconductor Manufacturing Company | Method to improve adhesion between copper and titanium nitride, for copper interconnect structures, via the use of an ion implantation procedure |

| US6169041B1 (en) * | 1999-11-01 | 2001-01-02 | United Microelectronics Corp. | Method for enhancing the reliability of a dielectric layer of a semiconductor wafer |

| WO2001054192A1 (en) * | 2000-01-18 | 2001-07-26 | Micron Technology, Inc. | Process for providing seed layers for aluminium, copper, gold and silver metallurgy |

Non-Patent Citations (2)

| Title |

|---|

| Prepare W-B-N Ternary Barrier to Cu Diffusion byImplantingBF2 Ions into W-N Thin film. Dong Joon Kim, Yong Tae Kim, Jong-Wan Park.J.VAC.SCI.Technol.B,Vol.17 No.(4).1999 * |

| structural and electrical characterization of Si-implanted TiNasa diffusion barrier for Cu metallization.W.F. Mcarthure, K.M.Ring, K.L.Kavanagh.Materials Reliability in Microelectronics V. Symposium San Francisco, CA, USA, 17-21 April 1995,Vol.391. 1995 * |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI584441B (zh) * | 2013-02-26 | 2017-05-21 | 旺宏電子股份有限公司 | 內連線結構及其形成方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1592964A (zh) | 2005-03-09 |

| AU2002340177A1 (en) | 2003-06-10 |

| JP2005510874A (ja) | 2005-04-21 |

| JP4685352B2 (ja) | 2011-05-18 |

| US20040023486A1 (en) | 2004-02-05 |

| KR20040064288A (ko) | 2004-07-16 |

| US6703307B2 (en) | 2004-03-09 |

| WO2003046978A2 (en) | 2003-06-05 |

| EP1449248A2 (en) | 2004-08-25 |

| WO2003046978A3 (en) | 2003-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100447978C (zh) | 在铜晶种沉积后的植入方法 | |

| US20220115505A1 (en) | Copper-filled trench contact for transistor performance improvement | |

| US7989338B2 (en) | Grain boundary blocking for stress migration and electromigration improvement in CU interconnects | |

| US7074709B2 (en) | Localized doping and/or alloying of metallization for increased interconnect performance | |

| US9269615B2 (en) | Multi-layer barrier layer for interconnect structure | |

| US9589836B1 (en) | Methods of forming ruthenium conductive structures in a metallization layer | |

| CN113764336A (zh) | 半导体结构与其形成方法 | |

| US6633085B1 (en) | Method of selectively alloying interconnect regions by ion implantation | |

| CN101278396A (zh) | 用于势垒增强的包含氧/氮过渡区的电镀种子层 | |

| CN107275282A (zh) | 半导体结构及形成半导体结构的方法 | |

| US7115498B1 (en) | Method of ultra-low energy ion implantation to form alloy layers in copper | |

| US7696092B2 (en) | Method of using ternary copper alloy to obtain a low resistance and large grain size interconnect | |

| US8728931B2 (en) | Multi-layer barrier layer for interconnect structure | |

| US6992004B1 (en) | Implanted barrier layer to improve line reliability and method of forming same | |

| US6656834B1 (en) | Method of selectively alloying interconnect regions by deposition process | |

| US6861349B1 (en) | Method of forming an adhesion layer with an element reactive with a barrier layer | |

| US6703308B1 (en) | Method of inserting alloy elements to reduce copper diffusion and bulk diffusion | |

| US6656836B1 (en) | Method of performing a two stage anneal in the formation of an alloy interconnect | |

| US6979642B1 (en) | Method of self-annealing conductive lines that separates grain size effects from alloy mobility | |

| US6835655B1 (en) | Method of implanting copper barrier material to improve electrical performance | |

| US7169706B2 (en) | Method of using an adhesion precursor layer for chemical vapor deposition (CVD) copper deposition | |

| KR20030000828A (ko) | 반도체 소자의 금속 배선 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: ADVANCED MICRO DEVICES INC Free format text: FORMER OWNER: ADVANCED MICRO DEVICES INC. Effective date: 20100709 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| COR | Change of bibliographic data |

Free format text: CORRECT: ADDRESS; FROM: CALIFORNIA, USA TO: GRAND CAYMAN ISLAND RITISH CAYMAN ISLANDS |

|

| TR01 | Transfer of patent right |

Effective date of registration: 20100709 Address after: Grand Cayman, Cayman Islands Patentee after: Globalfoundries Semiconductor Inc. Address before: American California Patentee before: Advanced Micro Devices Inc. |

|

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20081231 Termination date: 20161011 |