CN100405221C - 用于无铬相位光刻技术中将半导体器件图案分解为相位和镀铬区域的方法和装置 - Google Patents

用于无铬相位光刻技术中将半导体器件图案分解为相位和镀铬区域的方法和装置 Download PDFInfo

- Publication number

- CN100405221C CN100405221C CNB031286399A CN03128639A CN100405221C CN 100405221 C CN100405221 C CN 100405221C CN B031286399 A CNB031286399 A CN B031286399A CN 03128639 A CN03128639 A CN 03128639A CN 100405221 C CN100405221 C CN 100405221C

- Authority

- CN

- China

- Prior art keywords

- mask

- features

- pattern

- width

- equal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/26—Phase shift masks [PSM]; PSM blanks; Preparation thereof

- G03F1/34—Phase-edge PSM, e.g. chromeless PSM; Preparation thereof

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/36—Masks having proximity correction features; Preparation thereof, e.g. optical proximity correction [OPC] design processes

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70058—Mask illumination systems

- G03F7/70125—Use of illumination settings tailored to particular mask patterns

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70425—Imaging strategies, e.g. for increasing throughput or resolution, printing product fields larger than the image field or compensating lithography- or non-lithography errors, e.g. proximity correction, mix-and-match, stitching or double patterning

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70425—Imaging strategies, e.g. for increasing throughput or resolution, printing product fields larger than the image field or compensating lithography- or non-lithography errors, e.g. proximity correction, mix-and-match, stitching or double patterning

- G03F7/70466—Multiple exposures, e.g. combination of fine and coarse exposures, double patterning or multiple exposures for printing a single feature

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/708—Construction of apparatus, e.g. environment aspects, hygiene aspects or materials

- G03F7/70908—Hygiene, e.g. preventing apparatus pollution, mitigating effect of pollution or removing pollutants from apparatus

- G03F7/70941—Stray fields and charges, e.g. stray light, scattered light, flare, transmission loss

Landscapes

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Public Health (AREA)

- Health & Medical Sciences (AREA)

- Engineering & Computer Science (AREA)

- Epidemiology (AREA)

- Environmental & Geological Engineering (AREA)

- Atmospheric Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Abstract

一种通过在一衬底上印刷一目标图案以产生一掩模的方法。所述方法包括步骤:(a)通过使用在掩模中形成的相位结构,以确定在衬底上成像的特征的最大宽度;(b)识别具有等于或者小于所述最大宽度的宽度的目标图案中包含的所有特征;(c)从所述目标图案中抽取宽度等于或者小于所述最大宽度的所有特征;(d)在对应于在步骤(b)中识别出的所有特征的掩模中形成相位结构;以及(e)在所述掩模中为执行步骤(c)之后的目标图案中保留的所有特征形成不透明的结构。

Description

技术领域

本发明一般地涉及使用无铬相位光刻技术的掩模图案的生成,具体来讲是用于将一目标设计分解为利用镀铬和相位移技术印刷特征的相应掩模图案。此外,本发明还涉及一种使用一光刻装置的器件制造方法,所述光刻装置包括一个用于提供投影射束的辐射系统;用于承载一个用来使所述投影束形成图案的掩模的掩模平台;一个用于承载一衬底的衬底平台;以及一个用于将已形成图案的投影束投影到所述衬底的目标部分上的投影系统。

背景技术

举例来说在集成电路(IC)的制造中可以使用光刻投影装置(工具)。在这种情况下,掩模包含一个对应于IC的一个单层的电路图案,该图案可以被成像在一个衬底(硅片)上的一个目标部分(例如包括一个或多个芯片)上,所述衬底(硅片)上已经被镀有一层感光材料(防腐蚀涂层)。通常,单一晶圆将包含相邻目标部分的整个线路,经由所述投影系统对其进行一次一个的连续辐射。在一种光刻投影装置中,通过对所述目标部分上的全部掩模图案的一次性曝光来辐射每一目标部分;这样一种装置通常被称为晶圆分档器。在一种可供选择的装置(通常被称为步进和扫描装置)中,通过在所述投影束下沿一给定方向(即“扫描”方向)渐进地扫描所述掩模图案,以辐射每一目标部分,同时与所述方向平行或不平行地同步扫描所述衬底平台;一般来讲,由于所述投影系统具有一放大因数M(通常<1),扫描所述衬底平台的速度V将是扫描掩模平台的速度的M倍。举例来说,关于这里说明的光刻装置的更多信息可以从US 6,046,792中收集,该发明在这里合并作为参考。

在一个使用一光刻投影装置的制造工艺中,一掩模图案被成像在一衬底上,所述衬底至少部分地被一层感光材料(防腐蚀涂层)所覆盖。在成像步骤之前,所述衬底将经过各种工序,例如涂底漆,防腐蚀涂层涂敷以及软烘干。曝光以后,所述衬底可以经受其他工序,例如曝光后烘干(PEB),显像,硬烘干以及对成像图案的测量/检查。该工序系列被用作对一器件,例如一IC,的单层形成图案的基础。然后这样一种图案层可以经历各种的处理,例如蚀刻,离子注入(掺杂),金属喷镀,氧化,镀铬机理抛光等等,上述所有工序后,才能形成一个单层。如果需要若干层,那么需要对每一新层重复所述整个过程或者其相应的变更方案。最后,将在所述衬底(晶圆)上形成一系列器件。然后通过切割或者锯割技术,使这些器件彼此分离。其后,所述独立器件可以被嵌于载体,连接到插脚等等。可以获得关于此类处理的进一步信息,例如,来自由Peter van Zant、McGraw HillPublishing Co.于1997年出版的书“Microchip Fabrication:A Practical Guide toSemiconductor Processing”(第三版,ISBN0-07-067250-4),在这里合并作为参考。

所述光刻工具可以是一种具有两个或更多衬底平台(和/或两个或更多掩模平台)的类型。在这种“多平台设备”中,可以并行使用额外的平台,或者当一个或多个平台被用于曝光的同时,在一个或多个平台上进行准备步骤。例如,二级光刻设备已在US5969441和WO98/40791中做出了描述,在这里合并作为参考。

前面所提到的光刻法掩模包括相当于在硅片上将被集成的电路元件的几何图形。用于产生这种掩模的图案是利用CAD(计算机辅助设计)程序产生的,该处理通常被称为EDA(电子设计自动化)。大多数的CAD程序遵循一组用于产生功能化掩模的预定设计规则。通过处理和设计限制来设定这些规则。例如,设计规则定义了电路器件(例如门,电容器等等)或者互连线之间的间隔容限,以便保证所述电路器件或者线对彼此有不良影响。

当然,集成电路制造中目的之一是在晶圆(经由掩模)上如实地再现原始电路设计。另一目标是尽可能使用所述半导体片的大部分资源。然而当一集成电路的尺寸减少而其密度增加时,其相应掩模图案的CD(临界尺寸)趋近所述光学曝光工具的分辨极限。所述曝光工具可以重复地在晶圆上曝光的最小特征称为一个曝光工具的分辨率。当前曝光设备的分辨率值通常限制了许多先进IC电路设计的CD。

此外,微处理器速度、存储器存储密度和微电子器件的低电耗方面的不断改善,与用于在一半导体器件的各层上转移和形成图案的光刻技术的能力直接地相关。所述技术的当前状态要求其CD最好在自然光源波长以下的图案形成。例如,248纳米的当前生产波长正被推近为CD小于100纳米的图案形成。如在国际半导体技术标准(ITRs 2000)中说明的,该工业趋势将在接下来的5-10年继续并且可能普遍加快速度。

一项在当今照相光刻界受到额外注意的技术被称为无铬相位光刻″CPL″用于进一步的改善照相光刻设备的分辨/印刷能力。现在已知,当使用CPL技术时,结果产生的掩模图案一般包括不要求使用镀铬(即由相位移技术印刷的特征)的结构(将要印刷在晶圆上的图案)以及使用镀铬的结构。因此,需要掩模设计者验证使用各种技术的掩模结构以一种可接受的方式相互作用,以使所需图案被印刷在晶圆上。然而,由于掩模的复杂性,这可能是一项冗长、沉闷而困难的过程。

因此,就存在对一种方法的需要,该方法提供一种使用CPL技术定义掩模图案的简单和系统化的方法,并允许精确的印刷所需图案。

发明内容

为了解决上述需要,本发明的目的之一是提供一种方法,用于使用CPL技术根据所需的目标图案或者设计产生一掩模图案。重要的是,一个目的是提供一简单和系统化的处理,用于将所需目标图案转换为一掩模图案,以减少掩模设计需要的时间,同时提高在晶圆上印刷所述设计的精确度。

更具体地说,在一个示范性的实施例中,本发明涉及一种产生通过用于在一衬底上印刷目标图案以产生一的掩模的方法,所述方法包括步骤:(a)通过使用在所述掩模中形成的相位结构,确定在所述衬底上成像的特征的最大宽度;(b)识别所述目标图案中包含的具有等于或者小于所述最大宽度的宽度的所有特征;(c)从所述目标图案中抽取宽度等于或者小于所述最大宽度的所有特征;(d)在所述掩模中对应于在步骤(b)中识别出的所有特征的,所述掩模中形成相位结构;以及(e)在所述掩模中为执行步骤(c)之后目标图案中保留的所有特征形成不透明的结构。

本发明还涉及一种用于产生用于在一衬底上印刷一目标图案的掩模的设备,所述设备包括:通过使用在所述掩模中形成的相位结构来确定在所述衬底上成像的特征的最大宽度的装置;用于识别所述目标图案中包含的具有等于或者小于所述最大宽度的宽度的所有特征的装置;用于从所述目标图案中抽取宽度等于或者小于所述最大宽度的所有特征的装置;用于在所述掩模中对应于宽度等于或小于所述最大宽度的所有特征而形成相位结构的装置;以及用于在所述掩模中为宽度等于或小于所述最大宽度的所有特征形成不透明的结构的装置。

尽管在该文本中,本发明使用了IC制造中的具体参考依据,但应该明确理解的是,本发明还具有许多其他可能的应用。例如它可以被应用于制造集成光学系统、用于磁畴存储器的导槽和检测图案、液晶显示面板、薄膜磁头等等。本领域普通技术人员可以理解的是,此类可供选择的应用的范围内,文本中的术语“光刻掩遮模(reticle)”、“晶圆(wafer)”或者“芯片(die)”应该被认为是分别用更一般的术语“掩模(mask)”、“衬底(substrate)”和“目标部分(target portion)”做了替换。

在本文件中,术语“辐射”和“束”用来包含所有类型的电磁辐射,包括紫外线(例如波长为365.248,193,157或者126纳米)和极紫外辐射EUV(极端的紫外辐射,例如波长在5-20纳米范围内)。

本文本中采用的术语掩模可以被广义的解释为,可以对应于一个在衬底的一目标部分上生成的图案、向一个具有已形成图案的横截面施加一入射辐射射束的一般的图案形成装置;术语“光阀”也可以被用于本文。除典型的掩模(能透射的或者反射的;二元的,相位移,混和积体,等等)之外,此类其他形成图案的装置的实例包括:

a)可编程镜像阵列。此类设备的一个实例是一个具有一个粘弹性控制层和一个反射面的可寻址矩阵表面。这样一种装置背后的基本原理是(举例来说)所述反射面的寻址面积将入射光作为衍射光反射,而非寻址面积将入射光作为非衍射光反射。通过使用一种适当的滤光器,可以从所述反射束中将所述非衍射光线滤除,仅仅保留衍射光;用这样的方式,所述光束被根据可寻址矩阵表面的地址图案形成图案。所要求的矩阵寻址可以使用适当的电子装置来执行。有关此类镜像阵列的更多信息可以从例如美国专利US 5,296,891和US 5,523,193中收集,在这里合并作为参考。

b)可编程LCD阵列。该结构的一种实例在美国专利US5,229,872中给定,在这里合并作为参考。

本发明的方法相对于现有技术,提供了极其重要的有益效果。例如,上述为了定义/产生印刷目标图案所使用的掩模而将一目标图案分解为相位结构和不透明的结构的方法,提供一种将所需目标图案转换为掩模图案的简单的和系统化的过程,从而减少掩模设计需要的时间,同时提高在晶圆上印刷所述设计的精确度。

本发明的其他有益效果将通过对以下本发明的示例性实施例的详细说明,而变得对于本领域中普通技术人员十分清楚明显。

可以参考以下详细说明和附图来更好理解本发明本身以及进一步的目的和有益效果。

附图说明

图1是示出本发明的一个实施例的示例性的流程图。

图2a-2c示出三个示例性的图案以及在之后从所述图案中抽取的垂直特征的识别。

图3a-3c分别相应于在图2a-2c中示出的图案,并示出从所述图案中提取的水平特征,

图4a-4c分别示出在图2a-2c和图3a-3c中抽取的垂直和水平图案之间交叉的区域。

图5a-5c分别表示图2a、3a和4a;2b、3b和4b;以及2c、3c和4c中阐明的相应图案所对应的最终掩模设计;

图6a-6c示出能够减少闪光的各种亚分辨能力图案。

图7示出一个镀铬亚分辨能力图案和包括180°相位结构的同一图案的透射百分比之间的关系。

图8示意地描述了一种适于使用借助于当前发明设计的掩模的光刻投影装置。

具体实施方式

如下面的更详细说明,本发明的最佳实施例涉及一个用于分解一个所需目标图案(将被印刷在一晶圆上)以便产生一个掩模图案(例如,光刻掩遮模)的过程,该掩膜图案被用来在晶圆/衬底形成图像并在其上产生所述目标图案。根据本发明,要被产生的所述掩模图案使用了CPL技术。因而,所述掩模图案将包括大约100%透射和零相位移的区域;大约100%透射和180°相位移的区域;以及大约0%透射的区域。由于在使用CPL技术时具有这些用于印刷特征的不同类型区域再加上典型掩模的复杂性,掩模设计可能是一项困难并且需要大量时间的工作。如下面的详细说明,本发明通过提供一项可以被用于直接地从目标图案产生一掩模图案的简单分解处理,减少了生成掩模需要的时间。此外应注意的是,可以使用一种标准CAD系统(例如上面提到的那些)来执行本发明的所述方法,这是通过根据以下的说明来编程运行的。

图1是一般地示出本发明的掩模生成处理的流程图。如上所述,当使用CPL技术时,结果的掩模能够使用例如在所述掩模的光刻掩遮模中形成的相位边缘或相位移印刷特征(即,无铬),并能够使用所述掩模中包含的至少部分镀铬结构印刷特征。参照图1,在所述处理中的第一步骤(即步骤11)是确定可以使用相位结构(即,无铬)印刷的特征的最大宽度。换句话说,需要定义特征宽度,且需要以这个宽度结合镀铬的使用在晶圆上精确地再现所述特征。该最大宽度可以基于成像系统参数,例如但不限于波长、镜口率、照明和晶圆分档器条件确定,所述最大宽度是由巳知的方法例如使用一种空间像模拟器来确定。具体来讲,通过使用一种空间像模拟器可以确定所述图像在相位结构的什么宽度开始降低。最大宽度将被设置为小于该降低点,所述最大宽度还可以基于所需图案内的临界特征的定义来确定,例如最小特征尺寸、最小间距和最大作业周期。为了基于临界特征确定所述最大宽度,最大相位尺寸被设定以使所有临界最小特征属于所述相位区域。然后,利用该宽度,提供该相位尺寸宽度的可接受成像结果的照明设置被确定。这还可以使用一空间像模拟器来执行。换句话说,固定照明并确定最大宽度,或者根据所述临界几何尺寸固定最大宽度,然后确定需要的照明。因此,在步骤11中,可以使用相位移技术印刷的特征的最大宽度被确定。任何超过该宽度的特征必须使用镀铬来进行所述晶圆上的适当成像。

接下来在步骤12中,检验所述目标图案,识别并从原始设计中抽取出所有等于或者小于所述最大宽度的垂直分量/特征。图2a-2c示出三个示例性的图案以及在之后从所述图案中抽取的垂直特征的识别。如图2a-2c的每一个中所示,垂直特征21相应于等于或小于步骤11中确定的最大宽度的垂直特征,并因此从原始设计(即目标图案)中抽取出成为一个单独的图案,被称为图案A。如图2b中所示,超过最大宽度的垂直特征(例如参见,垂直特征23)没有被抽取出。应注意的是抽取出并被放入图案A中的特征能够使用相位结构印刷。应进一步注意的是,一旦被识别出,可以使用通常已知的布尔操作从所述目标图案中抽取出所述垂直特征21。

类似地,在步骤13中,所有等于或者小于最大宽度的水平分量特征被识别出并从所述目标图案中抽取出。图3a-3c分别相应于图2a-2c中示出的图案。如图3b-3c中的每一个中所示,水平特征31相应于等于或小于步骤11中确定的最大宽度的水平特征,并因此从原始设计中抽取出成为一个单独的图案,被指示为图案B。如图3a-3c中所示,超过最大宽度的水平特征(例如参见,水平特征33)没有被抽取出。应注意的是抽取出并被放入图案B中的特征能够使用相位结构印刷。应进一步注意的是,一旦被识别出,可以使用通常巳知的布尔操作从所述原始图案中抽取出所述水平特征31。

处理的下一步骤,即步骤14,要求识别将要使用相位结构印刷的垂直特征21和水平特征31之间的交叉部分。如下面进一步的解释,有时需要识别这样的交叉部分,以便控制应用在交叉部分的镀铬的尺寸,使其独立于对其他图案的镀铬应用。在该处理中是一个可选步骤的步骤14,有时候会被要求,以便保证交叉部分被正确地印刷在所述衬底上(即线没有中断)。交叉部分的识别执行如下。首先,图案A中包含的垂直特征,在每一特征的两头沿垂直方向长度增加。其次,图案B中包含的水平特征,在每一特征的两头沿水平方向长度增加。图案A和B中包含的垂直与水平特征的尺寸增大对于确保正确地识别交叉部分是十分必要的。例如,假定一个“L”形特征,当抽取该特征的垂直部分(或者水平部分)时,还成为交叉部分的一部分的垂直特征部分被丢失(即没有抽取出)。通过将垂直特征的长度延长某一预定量,属于交叉部分的垂直特征部分被重新捕获。以上所述对水平特征是一样的。应注意的是垂直与水平特征最好都延长相同的量。需进一步注意的是,关于增加量的一般规则是最大相位宽度的两倍。

接下来,一旦延长了图案A中的垂直特征和图案B中的水平特征,使用图案A和图案B执行布尔“AND”操作,其结果(被称为图案C)识别出要使用相位结构印刷的垂直特征和水平特征之间的交叉部分。分别在图4a-4c中示出对图2a-2c和图3a-3c中示出的示例性图案进行该操作的结果。更具体地说,参照图4a,没有识别出交叉部分,因为图3a中示出的相应水平图案不具有任何要使用相位结构印刷的水平特征。图4b和4c中的附图标记41示出分别在图2b和3b以及图2c和3c中识别出的垂直与水平特征之间的交叉部分。应注意的是,在将交叉部分与目标图案的其余部分分离之后,可以对镀铬交叉部分图案应用附加处理,例如调整大小。

接下来,一旦执行上述处理,下一步,即步骤15要求将图案分解为相位区域(例如100%透射和180°相位移)和不透明区(例如零透射)。应注意的是上述关于相位区域的要求仅仅是示例性的,也可以使用其他适于印刷所述相位结构的条件。例如,所述方法可以使用25%透射,或者50%透射,或者在所述光掩模上提供多次透射。对于分解,首先,通过对图案A和图案B执行布尔操作“OR”,以定义相位图案。操作“OR″的结果(称为图案D)是一个包含仅仅使用相位结构印刷(即没有镀铬)的垂直与水平特征的图案。其次,通过从原始图案减去图案D和图案C,识别出不使用相位结构印刷以及垂直与水平相位结构之间没有交叉部分的原始图案的部分。被称为图案E的结果图案,可以通过执行以下布尔运算获得:图案E=“原始图案”-(图案C“OR”图案D)。这样,图案E指出将使用掩模上的零透射特征(即镀铬特征)印刷的图案的那些部分。

因此,一旦上述步骤完成,就定义了所述掩模的以下三个不同部分:(1)图案D-使用相位结构印刷的垂直与水平特征,(2)图案C-使用不透明的结构(即零透射结构)印刷的垂直与水平特征的之间的交叉部分以及(3)图案E-原始设计中包含的而没有包含在图案C或者D中的所有其他特征。应注意的是图案C和图案E可以被合并成单一图案,这样每一图案中包含的所有特征都使用一个不透明的特征印刷(即零透射)。图案C和E的组合图称为图案F。

在最后的步骤中,上述图案被用于产生被用来在衬底上形成所需图案的图像的掩模。更具体地说,图案D和图案F通过使用布尔操作“AND”,合并以形成单一掩模。参照表示分别与图2a、3a和4a;2b、3b和4b;以及2c、3c和4c中示出的相应图案的对应最终掩模设计的图5a-5c,最终掩模包含用于印刷具有适于使用相位结构印刷的宽度的垂直与水平分量的相位结构51,和用于不适于使用相位结构印刷的印刷分量的不透明的结构53,以及使用不透明的结构印刷的垂直与水平分量之间的交叉部分。在所述示例性的实施例中,图5c中的掩模中包含的本底(background)区域55被定义为100%透射和0°相位移,所述相特征51被定义为100%透射和180°相位移,而所述不透明的结构53被定义为0%透射。应注意的是所述掩模的背景部分结合相位结构51操作,以便印刷图案D中示出的垂直与水平分量。应进一步注意的是,本发明的上述方法不限于上面阐述的具体透射和相位移特征。很明显,对上述发生变动也是可以的。

还可以结合本发明的所述方法使用光学接近校正技术或者边缘偏置。例如,可以将散射栅的使用结合到结果掩模设计里。此外,可以在处理中的各步骤将所述散射栅引入所述掩模设计中。按现状,散射栅可以被设置为不透明的散射栅或者相位边缘散射栅。重要必要条件之一是所述散射栅保持亚分辩率。图5a-5c示出结合进最终掩模设计中的示例性的散射栅57。

如上所述,上述为了定义/产生印刷目标图案所使用的掩模而将一目标图案分解为相位结构相特征和不透明结构的方法,提供了一种简单的和系统化的处理,用于将所需目标图案转换为一掩模图案,减少掩模设计要求的时间,同时提高在晶圆上印刷所述设计的精确度。

本发明的另一方面涉及为减少成像衬底中的“闪光”效应,而对所述掩模图案进行的进一步改进。按现状,“闪光”对应于降低图像平面(即一般是晶圆的表面)上的空间像的有害背景光。然而,闪光效应是大范围的(即一给定点的闪光量取决于已知点周围的一大片范围),因此无法使用传统的OPC方法校正。与闪光的原因有关的某些当前理论是:光学系统内的光线散射;空间像的对比度以及未消除的零级光线。应注意的是,影响一具体几何形状的背景光或者闪光是来自所述几何形状周围的一大片区域,而不是所述几何形状本身。因此,将图案大范围明亮区域内的能量强度减少30%,对减少有害的闪光分量具有非常积极的效果。

下面阐述用于从空间像中减少闪光分量的各种方法。在讨论这些方法之前,应注意的是,以下技术将在不包含要被印刷的特征或分量的掩模的大部分上实施。例如,参照图6a-6c,将这些图中示出部分之外的掩模的部分实施下列改进。

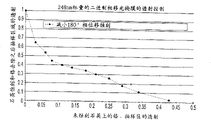

根据参照图6a的第一个方法,将亚分辩率不透明的图案添加到对应于设计中的开放区域(例如,远离任何图案几何形状200纳米以上的区域)部分的掩模图案。如这些图中所示,填充了开放空间25%的镀铬特征61的棋盘状图案起了作用,将这些区域面积中的强度减少至大约为入射光强度的82%。在第二种方法中,如图6b中所示,将一种具有180°相位移特征的棋盘状图案63添加到开孔区域,所述180°相位移特征63填充了开放空间的25%。该图案起作用,可以将该区域面积中的强度减少到大约是入射光强度的35%。在第三种方法中,如图6c中所示,将一种具有120°相位移特征的棋盘状图案65添加到开放区域,所述120°相位移特征65填充了开放空间的25%。该图案可以将该区域面积中的强度减少到大约是入射光强度的75%。应注意的是,大区域面积上的能量强度直接地取决于填充在所述闪光减少图案中的百分比。

图7示出镀铬亚分辩率图案以及180°相位结构的同一图案的透射百分比之间的关系。如所示的那样,当镀铬图案透射50%的入射光时,180°相位移的同一图案,100%传输特征将具有零强度。

应进一步注意的是,上述棋盘状图案和相位移量或者镀铬的使用仅仅是示例性的。可以执行对上文的变动,直到获得所要求的闪光减少量。例如,可允许的图案可以包括,但是不局限于:线条/空间图案,矩形棋盘,交替的水平和垂直线条,确认线条/空间图案等等。重要特征是闪光减少图案中包含的特征保持亚分辩率。

图8示意地描述了一种适于使用借助于当前发明设计的掩模的光刻投影装置。所述装置包括:

一辐射系统Ex,IL,用于提供一辐射投影束PB。在此具体实例中,所述辐射系统还包括一辐射源LA;

一个第一对象平台(掩模平台)MT,装备有一个用于承载一掩模MA(例如一光刻掩遮模)的掩模承载器,并连接到根据PL项精确放置所述掩模的第一定位装置;

一个第二对象平台(衬底平台)WT,装备有一个用于承载一衬底W(例如一个镀有防腐蚀涂层的硅片)的衬底承载器,并连接到根据项PL精确放置所述衬底的第二定位装置;

一投影系统(“透镜″)PL(例如折射的、反射的或者反折射的光学系统),用于在所述衬底W的一目标部分C(例如包括一个或多个芯片)上形成掩模MA的辐射部分的图像。

如此处描述的,所述装置是透射类型的(即具有一透射的掩模)。然而举例来说,通常它还可以是反射类型的(用一反射的掩模)。替换地,所述装置还可以采用另一种类的图案形成装置,作为掩模使用的替换物;实例包括可编程镜像阵列或者LCD矩阵。

所述光源LA(例如一汞灯、准分子激光器或者等离子体放电源)产生一射束。举例来说,该束被直接地或者在横截限定装置,例如一射束扩展器Ex,之后输入一个照明系统(照明设备)IL。所述照明设备IL可以包括调节装置AM,用于设定所述束中强度分布的外部和/或内部的半径范围(通常地被分别称为为σ-外部的和σ-内部的)。此外,它一般将包括各种其他组件,例如一个积分器IN和一个聚光镜CO。以这种方式,射在所述掩模MA上的所述束PB在其横截面具有期望的均匀性和强度分布。

对于图8应当指出的是,光源LA可以在所述光刻投影装置的外壳之内(例如当所述源LA是汞灯时,通常就是这样),但是它也可以远离所述光刻投影装置,它产生的辐射束被引导到所述装置(例如借助于适当的导引镜);后一方案经常是在所述光源LA是一个准分子激光器(例如基于KrF,ArF或者F2发射激光)的情况。当前发明包含这两个方案。

随后所述射束PB截断所述掩模MA,所述掩模MA置于掩模平台MT。横向穿过掩模MA之后,所述射束PB透过透镜PL,所述透镜PL将所述射束PB聚焦在所述衬底W的一目标部分C上。借助于所述算二定位装置(和干涉量度测量装置IF),所述衬底平台WT可以精确地移动,以便确定射束PB的路线中定位不同的目标部分C的位置。类似地所述第一定位装置可用于根据束PB的路线精确地定位掩模MA,例如在从一掩模库中机器检索所述掩模MA之后,或者在一次扫描期间。一般来讲,所述对象平台MT、WT的移动将借助于长行程模块(粗调定位)以及短行程模块(精调定位)来实现,这在图8中没有明确地描述。然而,就一晶圆分档器(与步进和扫描工具相反)来说,所述掩模平台MT可以仅仅与一短行程动臂机构连接,或可被固定。

所述工具可以两种不同的模式使用:

在步进模式中,所述掩模平台MT实质上是保持静止的,并且全部的掩模图像是在一目标部分C上一次投射的(即单一“闪光”)。然后所述衬底平台WT被沿X和/或Y轴方向移动,以通过光束PB辐射不同的目标部分C;

在扫描模式中,实质上应用了相同的方案,只是没有以单一“闪光”曝光给定目标部分C。作为代替的是,所述掩模平台MT是可以沿一给定方向(所谓的“扫描方向”,例如Y轴方向)以一速度v移动的,以使得投影束PB在一掩模图像上方扫描;同时,所述衬底平台WT同时沿相同的或者相反的方向以一速度V=Mv移动,其中M是透镜PL的放大倍率(一般为1/4或者1/5)。用这样的方式,可以曝光相对大的目标部分C,而不会损害分辩率。

尽管已经公开了本发明的某些具体实施例,但应注意的是,本发明可以以其他形式实施而不会脱离其精神上或者本质的特征。因此从各方面来说都应将当前实施例认为是例证性的而非限制性的,本发明的范围由所附加的权利要求书表明,因此所有属于该权利要求书的等效范围和意义内的改变都应包括在其中。

Claims (12)

1.一种产生用于在一衬底上印刷目标图案的掩模的方法,所述方法包括步骤:

(a)通过使用在所述掩模中形成的相位结构,确定在所述衬底上成像的特征的最大宽度;

(b)识别所述目标图案中包含的具有等于或者小于所述最大宽度的宽度的所有特征;

(c)从所述目标图案中抽取宽度等于或者小于所述最大宽度的所有特征;

(d)在所述掩模中对应于在步骤(b)中识别出的所有特征形成相位结构;以及

(e)在所述掩模中为执行步骤(c)之后目标图案中保留的所有特征形成不透明的结构。

2.如权利要求1所述的方法,其中步骤(b)包括以下步骤:

(f)识别所有宽度等于或者小于所述最大宽度的垂直特征;

(g)抽取步骤(f)中识别出的所有垂直特征;

(h)识别所有宽度等于或者小于所述最大宽度的水平特征;以及

(i)抽取步骤(h)中识别出的所有水平特征。

3.如权利要求2所述的方法,进一步包括以下步骤:识别步骤(f)中识别出的所述垂直特征与步骤(h)中识别出的所述水平特征之间的所有交叉部分,并在所述掩模中对应于所有所述交叉部分,形成不透明结构。

4.如权利要求3所述的方法,其中,通过在步骤(g)中抽取的垂直特征与步骤(h)中抽取的水平特征之间执行布尔操作“AND”,识别所述交叉部分。

5.如权利要求1所述的方法,其中,在所述掩模中由实质表现为100%透射和180°相位移的区域形成所述相位结构,而在所述掩模中由表现为0%透射的区域形成所述不透明的结构。

6.如权利要求1所述的方法,进一步包括以下步骤:在所述掩模中包括光学邻近校正特征或者边缘偏置。

7.一种用于产生用于在一衬底上印刷一目标图案的掩模的设备,所述设备包括:

通过使用在所述掩模中形成的相位结构来确定在所述衬底上成像的特征的最大宽度的装置;

用于识别所述目标图案中包含的具有等于或者小于所述最大宽度的宽度的所有特征的装置;

用于从所述目标图案中抽取宽度等于或者小于所述最大宽度的所有特征的装置;

用于在所述掩模中对应于宽度等于或小于所述最大宽度的所有特征而形成相位结构的装置;以及

用于在所述掩模中为宽度等于或小于所述最大宽度的所有特征形成不透明的结构的装置。

8.如权利要求7所述的设备,其中,所述用于识别包含在所述目标图案中具有等于或者小于所述最大宽度的宽度的所有特征的装置包括:

用于识别所有宽度等于或者小于所述最大宽度的所有垂直特征的装置;

用于抽取所有宽度等于或者小于所述最大宽度的所有垂直特征的装置;

用于识别所有宽度等于或者小于所述最大宽度的所有水平特征的装置;以及

用于抽取所有宽度等于或者小于所述最大宽度的所有水平特征的装置。

9.如权利要求8所述的设备,其中,识别宽度等于或者小于所述最大宽度的所述垂直特征与宽度等于或者小于所述最大宽度的所述水平特征之间的所有交叉部分,并且在所述掩模中对应于所有所述交叉部分形成不透明的结构。

10.如权利要求9所述的设备,其中,通过在抽取的垂直特征与抽取的水平特征之间执行布尔操作“AND”,识别出所述交叉部分。

11.如权利要求7所述的设备,其中,在所述掩模中由实质表现为100%透射和180°相位移的区域形成所述相位结构,而在所述掩模中由表现为0%透射的区域形成所述不透明的结构。

12.如权利要求7所述的设备,进一步包括:在所述掩模中包括光学校正特征或者边缘偏置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US36654502P | 2002-03-25 | 2002-03-25 | |

| US60/366545 | 2002-03-25 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1450403A CN1450403A (zh) | 2003-10-22 |

| CN100405221C true CN100405221C (zh) | 2008-07-23 |

Family

ID=27805318

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB031286399A Expired - Lifetime CN100405221C (zh) | 2002-03-25 | 2003-03-25 | 用于无铬相位光刻技术中将半导体器件图案分解为相位和镀铬区域的方法和装置 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US6851103B2 (zh) |

| EP (1) | EP1349002B1 (zh) |

| JP (2) | JP4102701B2 (zh) |

| KR (1) | KR100566151B1 (zh) |

| CN (1) | CN100405221C (zh) |

| DE (1) | DE60306438T2 (zh) |

| SG (2) | SG125911A1 (zh) |

| TW (1) | TWI301229B (zh) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06335801A (ja) * | 1993-05-24 | 1994-12-06 | Okuma Mach Works Ltd | バランス修正機能付数値制御旋盤 |

| JP3025369U (ja) * | 1995-11-30 | 1996-06-11 | 大宮工業株式会社 | 不釣合い修正機能付旋盤 |

| KR100566151B1 (ko) * | 2002-03-25 | 2006-03-31 | 에이에스엠엘 마스크툴즈 비.브이. | 무크롬 상 리소그래피를 이용하여 상 및 크롬영역으로반도체디바이스패턴을 분해하는 방법 및 장치 |

| KR100570196B1 (ko) * | 2002-07-26 | 2006-04-11 | 에이에스엠엘 마스크툴즈 비.브이. | 마스크 생성방법 및 장치, 패턴프린팅 방법, 및 컴퓨터프로그램물 |

| SG137657A1 (en) * | 2002-11-12 | 2007-12-28 | Asml Masktools Bv | Method and apparatus for performing model-based layout conversion for use with dipole illumination |

| US7234128B2 (en) * | 2003-10-03 | 2007-06-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for improving the critical dimension uniformity of patterned features on wafers |

| US6968532B2 (en) * | 2003-10-08 | 2005-11-22 | Intel Corporation | Multiple exposure technique to pattern tight contact geometries |

| US7234130B2 (en) * | 2004-02-25 | 2007-06-19 | James Word | Long range corrections in integrated circuit layout designs |

| US7861207B2 (en) | 2004-02-25 | 2010-12-28 | Mentor Graphics Corporation | Fragmentation point and simulation site adjustment for resolution enhancement techniques |

| US8037429B2 (en) * | 2005-03-02 | 2011-10-11 | Mentor Graphics Corporation | Model-based SRAF insertion |

| US7493587B2 (en) * | 2005-03-02 | 2009-02-17 | James Word | Chromeless phase shifting mask for integrated circuits using interior region |

| DE102005009805A1 (de) * | 2005-03-03 | 2006-09-14 | Infineon Technologies Ag | Lithographiemaske und Verfahren zum Erzeugen einer Lithographiemaske |

| JP4617272B2 (ja) * | 2005-04-12 | 2011-01-19 | エーエスエムエル マスクツールズ ビー.ブイ. | 二重露光リソグラフィを実行するための方法、プログラム製品及びデバイス製造方法 |

| US7712064B2 (en) * | 2005-05-20 | 2010-05-04 | Cadence Design Systems, Inc. | Manufacturing aware design of integrated circuit layouts |

| US7395516B2 (en) | 2005-05-20 | 2008-07-01 | Cadence Design Systems, Inc. | Manufacturing aware design and design aware manufacturing |

| US7732102B2 (en) * | 2005-07-14 | 2010-06-08 | Freescale Semiconductor, Inc. | Cr-capped chromeless phase lithography |

| EP1843202B1 (en) * | 2006-04-06 | 2015-02-18 | ASML Netherlands B.V. | Method for performing dark field double dipole lithography |

| JP4922112B2 (ja) * | 2006-09-13 | 2012-04-25 | エーエスエムエル マスクツールズ ビー.ブイ. | パターン分解フィーチャのためのモデルベースopcを行うための方法および装置 |

| US7934177B2 (en) * | 2007-02-06 | 2011-04-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and system for a pattern layout split |

| US7799487B2 (en) * | 2007-02-09 | 2010-09-21 | Ayman Yehia Hamouda | Dual metric OPC |

| US7945869B2 (en) * | 2007-08-20 | 2011-05-17 | Infineon Technologies Ag | Mask and method for patterning a semiconductor wafer |

| US7846643B1 (en) | 2007-11-02 | 2010-12-07 | Western Digital (Fremont), Llc | Method and system for providing a structure in a microelectronic device using a chromeless alternating phase shift mask |

| JP5355112B2 (ja) * | 2009-01-28 | 2013-11-27 | 株式会社東芝 | パターンレイアウト作成方法 |

| JP5407623B2 (ja) * | 2009-07-16 | 2014-02-05 | 富士通セミコンダクター株式会社 | マスクパターン評価方法、マスクパターン補正方法及びマスクパターン発生装置 |

| CN104040428B (zh) * | 2012-02-15 | 2018-11-13 | 大日本印刷株式会社 | 相移掩模及使用该相移掩模的抗蚀图案形成方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1237781A (zh) * | 1998-05-29 | 1999-12-08 | 日本电气株式会社 | 掩模的制造方法 |

| US20020015899A1 (en) * | 2000-05-01 | 2002-02-07 | Chen Jang Fung | Hybrid phase-shift mask |

Family Cites Families (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5362591A (en) * | 1989-10-09 | 1994-11-08 | Hitachi Ltd. Et Al. | Mask having a phase shifter and method of manufacturing same |

| US5281500A (en) * | 1991-09-04 | 1994-01-25 | Micron Technology, Inc. | Method of preventing null formation in phase shifted photomasks |

| JPH05341498A (ja) | 1992-04-10 | 1993-12-24 | Toshiba Corp | フォトマスク設計装置および設計方法 |

| US5881125A (en) * | 1992-09-25 | 1999-03-09 | Intel Corporation | Attenuated phase-shifted reticle using sub-resolution pattern |

| US5446521A (en) * | 1993-06-30 | 1995-08-29 | Intel Corporation | Phase-shifted opaquing ring |

| JP2661529B2 (ja) | 1993-11-30 | 1997-10-08 | 日本電気株式会社 | 位相シフトマスク |

| JP2917879B2 (ja) | 1995-10-31 | 1999-07-12 | 日本電気株式会社 | フォトマスク及びその製造方法 |

| US6228539B1 (en) * | 1996-09-18 | 2001-05-08 | Numerical Technologies, Inc. | Phase shifting circuit manufacture method and apparatus |

| US5923562A (en) * | 1996-10-18 | 1999-07-13 | International Business Machines Corporation | Method for automatically eliminating three way intersection design conflicts in phase edge, phase shift designs |

| JPH10198018A (ja) * | 1997-01-13 | 1998-07-31 | Mitsubishi Electric Corp | 減衰型位相シフトマスクおよびその製造方法 |

| US6114071A (en) | 1997-11-24 | 2000-09-05 | Asml Masktools Netherlands B.V. | Method of fine feature edge tuning with optically-halftoned mask |

| US6106979A (en) * | 1997-12-30 | 2000-08-22 | Micron Technology, Inc. | Use of attenuating phase-shifting mask for improved printability of clear-field patterns |

| US6077630A (en) * | 1998-01-08 | 2000-06-20 | Micron Technology, Inc. | Subresolution grating for attenuated phase shifting mask fabrication |

| AU3063799A (en) | 1998-03-17 | 1999-10-11 | Asml Masktools Netherlands B.V. | Method of patterning sub-0.25 lambda line features with high transmission, "attenuated" phase shift masks |

| KR100400294B1 (ko) * | 1998-12-30 | 2003-12-24 | 주식회사 하이닉스반도체 | 노광마스크 |

| JP4442962B2 (ja) * | 1999-10-19 | 2010-03-31 | 株式会社ルネサステクノロジ | フォトマスクの製造方法 |

| JP2001183806A (ja) | 1999-12-24 | 2001-07-06 | Nec Corp | 露光方法および位相シフトマスク |

| DE10001119A1 (de) * | 2000-01-13 | 2001-07-26 | Infineon Technologies Ag | Phasenmaske |

| JP2001222097A (ja) * | 2000-02-09 | 2001-08-17 | Fujitsu Ltd | 位相シフトマスク及びその製造方法 |

| JP2001319871A (ja) * | 2000-02-29 | 2001-11-16 | Nikon Corp | 露光方法、濃度フィルタの製造方法、及び露光装置 |

| US6544694B2 (en) * | 2000-03-03 | 2003-04-08 | Koninklijke Philips Electronics N.V. | Method of manufacturing a device by means of a mask phase-shifting mask for use in said method |

| JP2001296646A (ja) * | 2000-04-17 | 2001-10-26 | Fujitsu Ltd | フォトマスク、フォトマスクの製造方法、露光方法及び露光装置 |

| JP3749083B2 (ja) * | 2000-04-25 | 2006-02-22 | 株式会社ルネサステクノロジ | 電子装置の製造方法 |

| US6335130B1 (en) | 2000-05-01 | 2002-01-01 | Asml Masktools Netherlands B.V. | System and method of providing optical proximity correction for features using phase-shifted halftone transparent/semi-transparent features |

| US6338922B1 (en) * | 2000-05-08 | 2002-01-15 | International Business Machines Corporation | Optimized alternating phase shifted mask design |

| US6787271B2 (en) * | 2000-07-05 | 2004-09-07 | Numerical Technologies, Inc. | Design and layout of phase shifting photolithographic masks |

| US6815129B1 (en) * | 2000-09-26 | 2004-11-09 | Euv Llc | Compensation of flare-induced CD changes EUVL |

| US6901575B2 (en) * | 2000-10-25 | 2005-05-31 | Numerical Technologies, Inc. | Resolving phase-shift conflicts in layouts using weighted links between phase shifters |

| US6500587B1 (en) * | 2001-02-02 | 2002-12-31 | Advanced Micro Devices, Inc. | Binary and attenuating phase-shifting masks for multiple wavelengths |

| US6553562B2 (en) | 2001-05-04 | 2003-04-22 | Asml Masktools B.V. | Method and apparatus for generating masks utilized in conjunction with dipole illumination techniques |

| US6571380B2 (en) * | 2001-07-12 | 2003-05-27 | Micron Technology, Inc. | Integrated circuit with layout matched high speed lines |

| US6605396B2 (en) * | 2001-08-06 | 2003-08-12 | Infineon Technologies, Ag | Resolution enhancement for alternating phase shift masks |

| US6548417B2 (en) * | 2001-09-19 | 2003-04-15 | Intel Corporation | In-situ balancing for phase-shifting mask |

| US6757886B2 (en) * | 2001-11-13 | 2004-06-29 | International Business Machines Corporation | Alternating phase shift mask design with optimized phase shapes |

| CN100373258C (zh) * | 2001-12-26 | 2008-03-05 | 松下电器产业株式会社 | 光掩模、光掩模的制成方法以及使用该光掩模的图案形成方法 |

| US6625802B2 (en) | 2002-02-01 | 2003-09-23 | Intel Corporation | Method for modifying a chip layout to minimize within-die CD variations caused by flare variations in EUV lithography |

| KR100566151B1 (ko) * | 2002-03-25 | 2006-03-31 | 에이에스엠엘 마스크툴즈 비.브이. | 무크롬 상 리소그래피를 이용하여 상 및 크롬영역으로반도체디바이스패턴을 분해하는 방법 및 장치 |

| US6894864B2 (en) | 2002-07-26 | 2005-05-17 | Wistron Corp. | Portable information storage device |

-

2003

- 2003-03-25 KR KR1020030018563A patent/KR100566151B1/ko active IP Right Grant

- 2003-03-25 SG SG200301491A patent/SG125911A1/en unknown

- 2003-03-25 CN CNB031286399A patent/CN100405221C/zh not_active Expired - Lifetime

- 2003-03-25 DE DE60306438T patent/DE60306438T2/de not_active Expired - Fee Related

- 2003-03-25 SG SG200608891-8A patent/SG144749A1/en unknown

- 2003-03-25 TW TW092106620A patent/TWI301229B/zh not_active IP Right Cessation

- 2003-03-25 EP EP03251875A patent/EP1349002B1/en not_active Expired - Lifetime

- 2003-03-25 US US10/395,903 patent/US6851103B2/en not_active Expired - Lifetime

- 2003-03-25 JP JP2003124535A patent/JP4102701B2/ja not_active Expired - Fee Related

-

2005

- 2005-01-18 US US11/035,737 patent/US7549140B2/en not_active Expired - Lifetime

-

2007

- 2007-08-17 JP JP2007212820A patent/JP4558770B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1237781A (zh) * | 1998-05-29 | 1999-12-08 | 日本电气株式会社 | 掩模的制造方法 |

| US20020015899A1 (en) * | 2000-05-01 | 2002-02-07 | Chen Jang Fung | Hybrid phase-shift mask |

Non-Patent Citations (4)

| Title |

|---|

| 微光刻相移掩模技术研究. 冯伯儒,孙国良,沈锋,阙珑,陈宝钦,崔铮.光电工程,第23卷增刊卷. 1996 |

| 微光刻相移掩模技术研究. 冯伯儒,孙国良,沈锋,阙珑,陈宝钦,崔铮.光电工程,第23卷增刊卷. 1996 * |

| 相移掩模的制作. 冯伯儒,陈宝钦.微细加工技术,第1997年第1期. 1997 |

| 相移掩模的制作. 冯伯儒,陈宝钦.微细加工技术,第1997年第1期. 1997 * |

Also Published As

| Publication number | Publication date |

|---|---|

| US20040010770A1 (en) | 2004-01-15 |

| JP4102701B2 (ja) | 2008-06-18 |

| EP1349002B1 (en) | 2006-06-28 |

| KR100566151B1 (ko) | 2006-03-31 |

| US6851103B2 (en) | 2005-02-01 |

| JP4558770B2 (ja) | 2010-10-06 |

| SG125911A1 (en) | 2006-10-30 |

| US20050125765A1 (en) | 2005-06-09 |

| TWI301229B (en) | 2008-09-21 |

| TW200307190A (en) | 2003-12-01 |

| EP1349002A3 (en) | 2004-03-17 |

| DE60306438T2 (de) | 2007-01-04 |

| KR20030077447A (ko) | 2003-10-01 |

| DE60306438D1 (de) | 2006-08-10 |

| JP2003295413A (ja) | 2003-10-15 |

| EP1349002A2 (en) | 2003-10-01 |

| US7549140B2 (en) | 2009-06-16 |

| CN1450403A (zh) | 2003-10-22 |

| SG144749A1 (en) | 2008-08-28 |

| JP2007323091A (ja) | 2007-12-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100405221C (zh) | 用于无铬相位光刻技术中将半导体器件图案分解为相位和镀铬区域的方法和装置 | |

| JP3645242B2 (ja) | ダイポール式照明技術に関連して使用されるマスクの生成方法と生成装置 | |

| KR100592580B1 (ko) | 쌍극조명에 사용하기 위한 모델-기반 레이아웃 변환을수행하는 방법 및 장치 | |

| KR100668192B1 (ko) | 고수율의 레티클 형성 방법 | |

| JP4267245B2 (ja) | 解像度以下の補助フィーチャとして罫線ラダー・バーを利用した光近接補正方法 | |

| KR100570196B1 (ko) | 마스크 생성방법 및 장치, 패턴프린팅 방법, 및 컴퓨터프로그램물 | |

| CN100338528C (zh) | 利用双极照明进行基于规则的栅极缩小的方法和装置 | |

| US6951701B2 (en) | Method for improved lithographic patterning utilizing multiple coherency optimized exposures and high transmission attenuated PSM | |

| JP5001235B2 (ja) | リソグラフィ処理方法 | |

| KR20060050603A (ko) | 4분의 1 파장의 리소그래피에서 초점심도를 향상시키는모델 기반 스캐터링 바아 배치를 위한 방법, 프로그램물 및장치 | |

| KR20050025095A (ko) | 서브-파장 광학 리소그래피용 위상-평형 스캐터링바아들의 모델 기반 배치를 수행하는 방법 및 장치 | |

| TW200525178A (en) | A method, program product and apparatus of simultaneous optimization for NA-sigma exposure settings and scattering bars OPC using a device layout | |

| KR20040065188A (ko) | 딥 서브-파장 광학 리소그래피용 레티클 패턴에 광근접성피처들을 제공하는 방법 및 장치 | |

| US7316870B2 (en) | Device manufacturing method, mask set for use in the method, data set for controlling a programmable patterning device, method of generating a mask pattern and a computer program | |

| KR20050002615A (ko) | 이미지 필드 맵을 이용하여 어시스트 피처를 생성하는방법, 프로그램물 및 장치 | |

| JP5191464B2 (ja) | リソグラフィパターンの分割方法、当該分割方法を含むリソグラフィ処理方法及びデバイス製造方法、並びに前記分割方法で製造されるマスク | |

| EP1467256A1 (en) | Device manufacturing method and mask set for use in the method | |

| TWI279648B (en) | Method and apparatus for generating complementary mask patterns for use in a multiple-exposure lithographic imaging process, computer program product for controlling a computer, and integrated circuit device manufacturing method | |

| Roeth et al. | In-die registration metrology on future-generation reticles | |

| Zibold et al. | Application results at 193nm: lithography emulation by aerial imaging and supplementary high resolution measurements | |

| KR20120065886A (ko) | 반도체 소자의 마스크 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: ASML HOLLAND CO., LTD. Free format text: FORMER OWNER: ASML FRISKET TOOLS B.V. Effective date: 20140211 |

|

| TR01 | Transfer of patent right |

Effective date of registration: 20140211 Address after: Holland Weide Eindhoven Patentee after: ASML Holding N.V Address before: Holland Weierde Eindhoven Patentee before: ASML Masktools B.V. |

|

| TR01 | Transfer of patent right | ||

| CX01 | Expiry of patent term |

Granted publication date: 20080723 |

|

| CX01 | Expiry of patent term |