WO2024084366A1 - 半導体装置、及び、記憶装置 - Google Patents

半導体装置、及び、記憶装置 Download PDFInfo

- Publication number

- WO2024084366A1 WO2024084366A1 PCT/IB2023/060395 IB2023060395W WO2024084366A1 WO 2024084366 A1 WO2024084366 A1 WO 2024084366A1 IB 2023060395 W IB2023060395 W IB 2023060395W WO 2024084366 A1 WO2024084366 A1 WO 2024084366A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- conductor

- insulator

- oxide semiconductor

- oxide

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/69—IGFETs having charge trapping gate insulators, e.g. MNOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/875—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being semiconductor metal oxide, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

-

- H10P14/29—

-

- H10P14/3434—

-

- H10P34/42—

Definitions

- One embodiment of the present invention relates to a method for forming a metal oxide film. Another embodiment of the present invention relates to a transistor including the metal oxide and a method for manufacturing the transistor. Another embodiment of the present invention relates to a semiconductor device using the metal oxide and a method for manufacturing the semiconductor device. Another embodiment of the present invention relates to a memory device using the metal oxide and a method for manufacturing the memory device.

- one embodiment of the present invention is not limited to the above technical field.

- Examples of the technical field of one embodiment of the present invention include semiconductor devices, display devices, light-emitting devices, power storage devices, memory devices, electronic devices, lighting devices, input devices (e.g., touch sensors), input/output devices (e.g., touch panels), driving methods thereof, or manufacturing methods thereof.

- a semiconductor device is a device that utilizes semiconductor characteristics, and refers to a circuit including a semiconductor element (transistor, diode, photodiode, etc.), a device having such a circuit, etc. Also, it refers to any device that can function by utilizing semiconductor characteristics. For example, an integrated circuit, a chip including an integrated circuit, and an electronic component that houses a chip in a package are examples of semiconductor devices. Also, memory devices, display devices, light-emitting devices, lighting devices, and electronic devices may themselves be semiconductor devices and each may have a semiconductor device.

- a CPU is a collection of semiconductor elements that have semiconductor integrated circuits (at least transistors and memories) that are chipped by processing a semiconductor wafer and have electrodes that serve as connection terminals.

- IC chips Semiconductor circuits (IC chips) such as LSIs, CPUs, and memories are mounted on circuit boards, such as printed wiring boards, and are used as components in a variety of electronic devices.

- transistors are widely used in electronic devices such as integrated circuits (ICs) and display devices.

- ICs integrated circuits

- Silicon-based semiconductor materials are widely known as semiconductor materials that can be used in transistors, but oxide semiconductors are also attracting attention as other materials.

- Patent Document 1 discloses a low-power consumption CPU that utilizes the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 2 discloses a memory device that can retain stored contents for a long period of time by utilizing the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 3 and Non-Patent Document 1 disclose a technique for increasing the density of integrated circuits by stacking a first transistor using an oxide semiconductor film and a second transistor using an oxide semiconductor film to provide multiple overlapping memory cells.

- Patent Document 4 discloses a vertical transistor in which the side surface of the oxide semiconductor is covered by a gate electrode via a gate insulator.

- Non-Patent Documents 2 and 3 disclose techniques for fabricating transistors using oxide semiconductors having a CAAC structure.

- An object of one embodiment of the present invention is to provide a novel metal oxide and a method for forming the same.

- an object of one embodiment of the present invention is to provide a transistor, semiconductor device, or memory device that can be miniaturized or highly integrated.

- an object of one embodiment of the present invention is to provide a highly reliable transistor, semiconductor device, or memory device.

- an object of one embodiment of the present invention is to provide a transistor with a large on-state current.

- an object of one embodiment of the present invention is to provide a transistor with favorable electrical characteristics.

- an object of one embodiment of the present invention is to provide a semiconductor device or memory device with low power consumption.

- an object of one embodiment of the present invention is to provide a memory device with high operation speed.

- an object of one embodiment of the present invention is to provide a method for manufacturing the transistor, semiconductor device, or memory device.

- One aspect of the present invention is a semiconductor device that includes an oxide semiconductor, a first conductor, a second conductor, a third conductor, and a first insulator, the first conductor and the second conductor each have a portion in contact with the oxide semiconductor, the third conductor overlaps the oxide semiconductor via the first insulator, the oxide semiconductor has a first portion provided along the first surface and a second portion provided along a second surface that is inclined with respect to the first surface, the ratio of the thickness of the second portion to the thickness of the first portion is 0.8 to 1.2, the oxide semiconductor includes indium and one or more selected from gallium, tin, and zinc, and the aluminum concentration of the oxide semiconductor is 0.01 atomic% to 10 atomic%.

- Another aspect of the present invention is a semiconductor device that includes an oxide semiconductor, a first conductor, a second conductor, a third conductor, a first insulator, and a second insulator, the first insulator is in contact with the top surface of the first conductor, the second conductor is located on the first insulator, the oxide semiconductor has a first portion in contact with the top surface of the first conductor, a second portion in contact with a side surface of the first insulator, and a third portion in contact with the second conductor, the second insulator is located on the oxide semiconductor, the third conductor is located on the second insulator, and overlaps with the oxide semiconductor via the second insulator, the ratio of the thickness of the second portion to the thickness of the first portion is 0.8 to 1.2, the oxide semiconductor includes indium and one or more selected from gallium, tin, and zinc, and the aluminum concentration of the oxide semiconductor is 0.01 atomic% to 10 atomic%.

- one aspect of the present invention includes an oxide semiconductor, a first conductor, a second conductor, a third conductor, a first insulator, and a second insulator, the first insulator being in contact with an upper surface of the first conductor, the second conductor being located on the first insulator, the first insulator and the second conductor having a first opening that reaches the first conductor, and the oxide semiconductor having, inside the first opening, a first portion that is in contact with an upper surface of the first conductor and a second portion that is in contact with a side surface of the first insulator, and a third portion that is in contact with the second conductor.

- the second insulator is located on the oxide semiconductor

- the third conductor is located on the second insulator and overlaps with the oxide semiconductor via the second insulator at a position overlapping with the first opening

- the ratio of the thickness of the second portion to the thickness of the first portion is 0.8 or more and 1.2 or less

- the oxide semiconductor contains indium and one or more selected from gallium, tin, and zinc

- the aluminum concentration of the oxide semiconductor is 0.01 atomic% or more and 10 atomic% or less.

- the aluminum concentration of the oxide semiconductor is preferably 0.01 atomic% or more and 5 atomic% or less.

- the carbon concentration of the oxide semiconductor is preferably greater than or equal to 1 ⁇ 10 17 atoms/cm 3 and less than or equal to 5 ⁇ 10 19 atoms/cm 3 .

- one aspect of the present invention is a memory device having the above-mentioned semiconductor device, a fourth conductor, a third insulator, and a capacitor, the capacitor having a fifth conductor, a fourth insulator on the fifth conductor, and a first conductor on the fourth insulator, the third insulator having a second opening reaching the fourth conductor, and at least a portion of the fifth conductor, at least a portion of the fourth insulator, and at least a portion of the first conductor are disposed in the second opening.

- Another aspect of the present invention is a method for forming a metal oxide film, comprising a first step of supplying a first compound containing indium into a chamber and then supplying an oxidizing agent into the chamber, and a second step of supplying a second compound into the chamber and then supplying an oxidizing agent into the chamber, wherein the aluminum content of the first compound is 0.01 ppm or more and 500 ppm or less, the aluminum content of the second compound is less than the aluminum content of the first compound, and the second compound contains gallium, tin, or zinc.

- Another aspect of the present invention is a method for forming a metal oxide film, comprising a first step of supplying a first compound containing indium into a chamber and then supplying an oxidizing agent into the chamber, and a second step of supplying a second compound into the chamber and then supplying the oxidizing agent into the chamber, wherein the aluminum content of the first compound is 0.01 ppm or more and 500 ppm or less, the aluminum content of the second compound is less than the aluminum content of the first compound, and the sum of the time for supplying the oxidizing agent in the first step and the time for supplying the oxidizing agent in the second step is 90 seconds or more.

- the second compound preferably contains gallium or zinc.

- each of the first step and the second step at least once, and then to carry out microwave treatment in an oxygen-containing atmosphere.

- each of the first step and the second step at least once, and then perform microwave treatment in an oxygen-containing atmosphere to form a first cycle, and to repeat the first cycle multiple times.

- Another embodiment of the present invention includes a first insulator, an oxide semiconductor covering the first insulator, a first conductor and a second conductor on the oxide semiconductor, a second insulator disposed on the first conductor and the second conductor and having an opening overlapping with a region between the first conductor and the second conductor, a third insulator disposed in the opening and on the oxide semiconductor, and a third conductor disposed in the opening and on the third insulator, wherein the height of the first insulator in a cross-sectional view in a channel width direction is

- the semiconductor device has a first portion that is longer than the width of the edge, the oxide semiconductor has a first portion that is provided along the first surface, and a second portion that is provided along the second surface that is inclined with respect to the first surface, the ratio of the thickness of the second portion to the thickness of the first portion is 0.8 to 1.2, the oxide semiconductor has indium and one or more selected from gallium, tin, and zinc, and the aluminum concentration of the oxide semiconductor is 0.01

- the side of the opening of the second insulator coincides or roughly coincides with the side of the first conductor and the side of the second conductor.

- the first conductor preferably functions as one of the source electrode and drain electrode of the transistor.

- the second conductor preferably functions as the other of the source electrode and drain electrode of the transistor.

- the third conductor preferably functions as the gate electrode of the transistor.

- the oxide semiconductor and the third conductor face each other with the third insulator in between, and on the other side of the first insulator, the oxide semiconductor and the third conductor face each other with the third insulator in between.

- the first conductor contacts the oxide semiconductor on one side and the other side of the first insulator, and the second conductor contacts the oxide semiconductor on one side and the other side of the first insulator.

- the height of the first insulator is greater than or equal to 2 times and less than or equal to 20 times the width of the first insulator.

- Another embodiment of the present invention is a memory device including the above-described semiconductor device and a capacitor, in which one electrode of the capacitor is electrically connected to a first conductor of the semiconductor device.

- the capacitor is preferably disposed over a third conductor. At least a part of the capacitor is preferably overlapped with the oxide semiconductor and the third conductor.

- a novel metal oxide and a method for forming the same can be provided.

- a transistor, a semiconductor device, or a memory device that can be miniaturized or highly integrated can be provided.

- a highly reliable transistor, a semiconductor device, or a memory device can be provided.

- a transistor with a large on-state current can be provided.

- a transistor with good electrical characteristics can be provided.

- a semiconductor device or a memory device with low power consumption can be provided.

- a memory device with a high operating speed can be provided.

- a method for manufacturing the above-mentioned transistor, semiconductor device, or memory device can be provided.

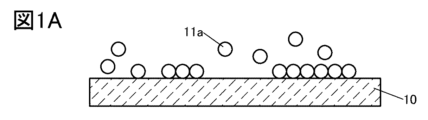

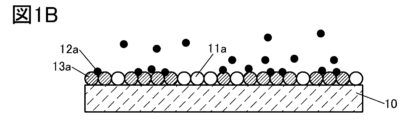

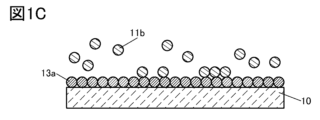

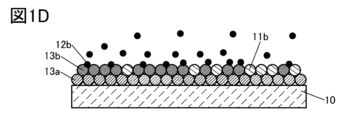

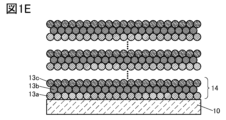

- 1A to 1E are cross-sectional views showing an example of a method for forming a metal oxide film.

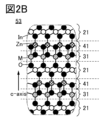

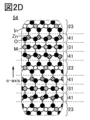

- 2A to 2D are cross-sectional views showing an example of a metal oxide.

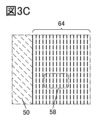

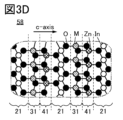

- 3A to 3D are cross-sectional views showing an example of a metal oxide.

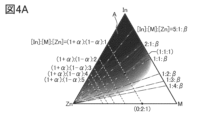

- 4A to 4C are diagrams showing examples of ranges of atomic ratios of metal oxides.

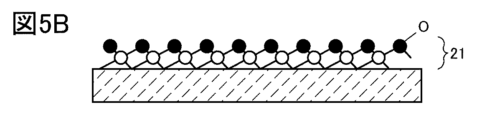

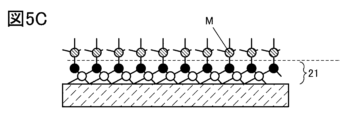

- 5A to 5D are cross-sectional views showing an example of a method for forming a metal oxide film.

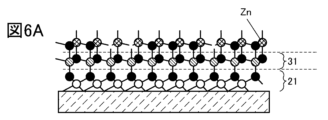

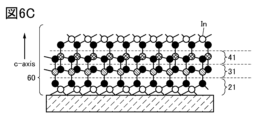

- 6A to 6C are cross-sectional views showing an example of a method for forming a metal oxide film.

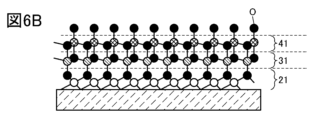

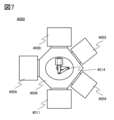

- FIG. 7 is a plan view and a cross-sectional view showing an example of a film forming apparatus.

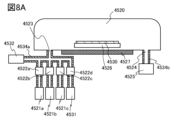

- FIG. 8A and 8B are cross-sectional views showing an example of a film forming apparatus.

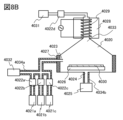

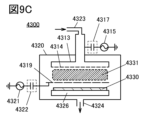

- 9A to 9C are cross-sectional views showing an example of a film forming apparatus.

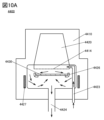

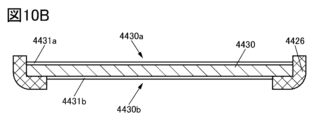

- 10A and 10B are cross-sectional views showing an example of a film forming apparatus.

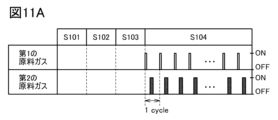

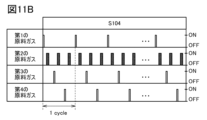

- 11A and 11B are diagrams showing an example of a method for forming a metal oxide film.

- 12A and 12B are diagrams showing an example of a method for forming a metal oxide film.

- FIG. 13 is a diagram showing an example of a method for forming a metal oxide film.

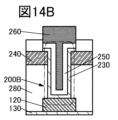

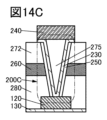

- 14A to 14D are cross-sectional views showing an example of a memory device.

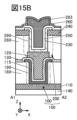

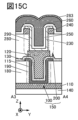

- Fig. 15A is a plan view showing an example of a memory device

- FIG. 15C are cross-sectional views showing an example of a memory device

- Fig. 15D is a circuit diagram showing an example of a memory device

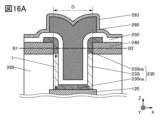

- 16A and 16B are cross-sectional views showing an example of a memory device.

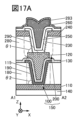

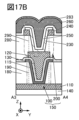

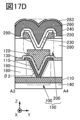

- 17A to 17D are cross-sectional views showing an example of a memory device.

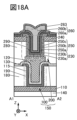

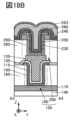

- 18A and 18B are cross-sectional views showing an example of a memory device.

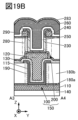

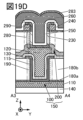

- 19A to 19D are cross-sectional views showing an example of a memory device.

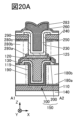

- 20A and 20B are cross-sectional views showing an example of a memory device.

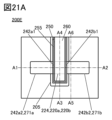

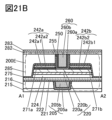

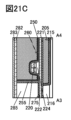

- Fig. 21A is a plan view showing an example of a semiconductor device

- Fig. 21B to Fig. 21D are cross-sectional views showing an example of the semiconductor device.

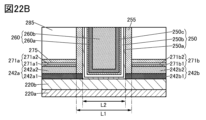

- FIG. 22A and 22B are cross-sectional views showing an example of a semiconductor device.

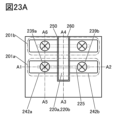

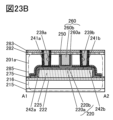

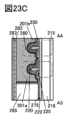

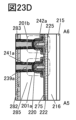

- Fig. 23A is a plan view showing an example of a semiconductor device

- Fig. 23B to Fig. 23D are cross-sectional views showing an example of the semiconductor device.

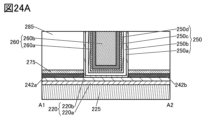

- 24A and 24B are cross-sectional views showing an example of a semiconductor device.

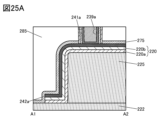

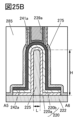

- 25A to 25C are cross-sectional views showing an example of a semiconductor device.

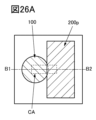

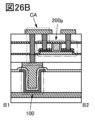

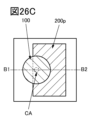

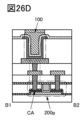

- 26A and 26C are plan views and sectional views of an example of a storage device, respectively.

- 27A and 27B are plan and cross-sectional views illustrating an example of a storage device.

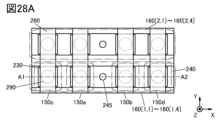

- 28A is a plan view of an example of a storage device

- FIG 28B is a cross-sectional view of the example of the storage device.

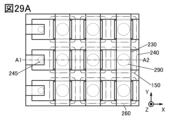

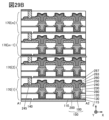

- 29A is a plan view of an example of a storage device

- FIG 29B is a cross-sectional view of the example of the storage device.

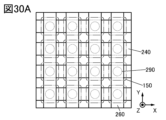

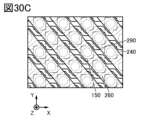

- 30A to 30C are plan layouts showing an example of a storage device.

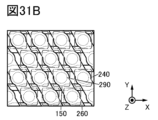

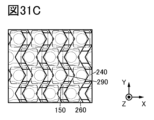

- 31A to 31C are plan layouts showing an example of a storage device.

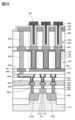

- FIG. 32 is a cross-sectional view showing an example of a storage device.

- FIG. 33 is a block diagram illustrating an example of a storage device.

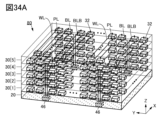

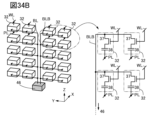

- 34A and 34B are schematic diagrams showing an example of a storage device.

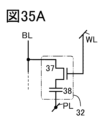

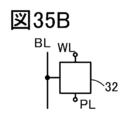

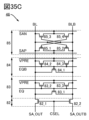

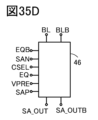

- 35A to 35D are circuit diagrams showing an example of a memory device.

- FIG. 36 is a circuit diagram showing an example of a memory device.

- 37A and 37B are diagrams illustrating an example of an electronic component.

- FIG. 38A and 38B are diagrams showing an example of an electronic device

- Fig. 38C to Fig. 38E are diagrams showing an example of a mainframe computer.

- FIG. 39 is a diagram showing an example of space equipment.

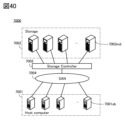

- FIG. 40 is a diagram illustrating an example of a storage system that can be applied to a data center.

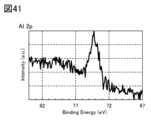

- FIG. 41 is a diagram showing the results of XPS analysis of Example 1.

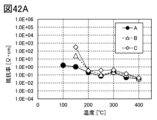

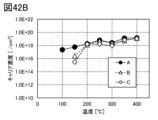

- 42A and 42B are diagrams showing the results of Hall effect measurement in Example 1.

- FIG. 43 is a diagram showing the results of SIMS analysis of Example 1.

- FIG. 44 is a diagram showing the results of SIMS analysis of Example 1.

- FIG. 45 is a diagram showing the results of SIMS analysis of Example 1.

- 46A and 46B are diagrams showing the results of SIMS analysis of Example 1.

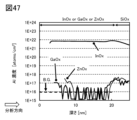

- FIG. 47 is a diagram showing the results of SIMS analysis of Example 1.

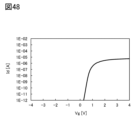

- FIG. 48 is a diagram showing the Id-Vg characteristics of the transistor of Example 1.

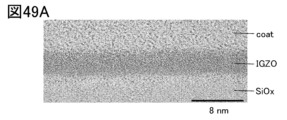

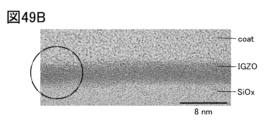

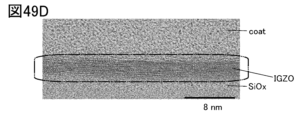

- 49A to 49D are cross-sectional observation images of the IGZO film of Example 1.

- 50A to 50D are diagrams showing the results of SIMS analysis of Example 2.

- ordinal numbers “first” and “second” are used for convenience and do not limit the number of components or the order of the components (e.g., the order of processes or the order of stacking).

- an ordinal number attached to a component in one place in this specification may not match an ordinal number attached to the same component in another place in this specification or in the claims.

- a transistor is a type of semiconductor element that can perform functions such as amplifying current or voltage and switching operations that control conduction or non-conduction.

- transistor includes IGFETs (Insulated Gate Field Effect Transistors) and thin film transistors (TFTs).

- a transistor is an element having at least three terminals including a gate, a drain, and a source.

- a transistor has a region (also called a channel formation region) in which a channel is formed between the drain (drain terminal, drain region, or drain electrode) and the source (source terminal, source region, or source electrode), and a current can flow between the source and drain through the channel formation region.

- a channel formation region refers to a region through which a current mainly flows.

- source and drain may be interchanged when transistors of different polarity are used, or when the direction of current changes during circuit operation. For this reason, in this specification, the terms “source” and “drain” can be used interchangeably.

- the impurity of a semiconductor refers to, for example, anything other than the main component constituting the semiconductor.

- an element with a concentration of less than 0.1 atomic % can be said to be an impurity.

- the defect level density of the semiconductor may increase or the crystallinity may decrease.

- the semiconductor is an oxide semiconductor

- examples of the impurity that changes the characteristics of the semiconductor include, for example, a Group 1 element, a Group 2 element, a Group 13 element, a Group 14 element, a Group 15 element, and a transition metal other than the main component of the oxide semiconductor.

- Specific examples of the impurity include, for example, hydrogen, lithium, sodium, silicon, boron, phosphorus, carbon, and nitrogen.

- water may also function as an impurity.

- oxygen vacancies also referred to as V O

- V O oxygen vacancies

- an oxynitride refers to a material whose composition contains more oxygen than nitrogen.

- An oxynitride refers to a material whose composition contains more nitrogen than oxygen.

- SIMS secondary ion mass spectrometry

- XPS X-ray photoelectron spectroscopy

- SIMS is suitable when the content of the target element is high (e.g., 0.5 atomic% or more, or 1 atomic% or more).

- SIMS is suitable when the content of the target element is low (e.g., 0.5 atomic% or less, or 1 atomic% or less).

- the term “insulator” can be replaced with “insulating film” or “insulating layer.”

- the term “conductor” can be replaced with “conductive film” or “conductive layer.”

- the term “semiconductor” can be replaced with “semiconductor film” or “semiconductor layer.”

- parallel refers to a state in which two straight lines are arranged at an angle of -10 degrees or more and 10 degrees or less. Therefore, it also includes cases in which the angle is -5 degrees or more and 5 degrees or less.

- approximately parallel refers to a state in which two straight lines are arranged at an angle of -30 degrees or more and 30 degrees or less.

- Perfect refers to a state in which two straight lines are arranged at an angle of 80 degrees or more and 100 degrees or less. Therefore, it also includes cases in which the angle is 85 degrees or more and 95 degrees or less.

- approximately perpendicular refers to a state in which two straight lines are arranged at an angle of 60 degrees or more and 120 degrees or less.

- electrically connected includes a connection via "something that has some kind of electrical action.”

- something that has some kind of electrical action is not particularly limited as long as it allows electrical signals to be sent and received between the connected objects.

- something that has some kind of electrical action includes electrodes or wiring, as well as switching elements such as transistors, resistive elements, coils, capacitive elements, and other elements with various functions.

- the off-state current refers to a leakage current between the source and drain when a transistor is in an off state (also referred to as a non-conducting state or a cut-off state).

- the off-state refers to a state in which the voltage Vgs between the gate and source of an n-channel transistor is lower than the threshold voltage Vth (higher than Vth for a p-channel transistor).

- the top surface shape of a certain component refers to the contour shape of the component in a planar view.

- a planar view refers to a view from the normal direction of the surface on which the component is formed or the surface of the support (e.g., substrate) on which the component is formed.

- a tapered shape refers to a shape in which at least a part of the side of the structure is inclined with respect to the substrate surface or the surface to be formed.

- the side of the structure, the substrate surface, and the surface to be formed do not necessarily need to be completely flat, and may be approximately planar with a slight curvature, or approximately planar with fine irregularities.

- A covers B

- at least a part of A covers B. Therefore, for example, it can be rephrased as saying that A has an area that covers B.

- the metal oxide of one embodiment of the present invention can be used as a semiconductor material, an insulating material, or a conductive material, depending on the type, combination, composition, and the like of the elements constituting the metal oxide.

- the metal oxide of one embodiment of the present invention can be used, for example, in the semiconductor layer of a transistor.

- the metal oxide may also be called an oxide semiconductor or an oxide.

- the metal oxide film formation method of one embodiment of the present invention uses the ALD (Atomic Layer Deposition) method, which allows extremely thin and uniform films to be formed. This makes it suitable for forming metal oxide films that form fine transistors.

- ALD Atomic Layer Deposition

- an inorganic precursor is a precursor that contains carbon as a constituent element

- an inorganic precursor is a precursor that does not contain carbon as a constituent element.

- a metal oxide film formed using an inorganic precursor can have a lower impurity concentration (e.g., at least one of hydrogen concentration, carbon concentration, and nitrogen concentration) in the film compared to a metal oxide film formed using an organic precursor.

- a lower impurity concentration e.g., at least one of hydrogen concentration, carbon concentration, and nitrogen concentration

- the metal oxide film formation temperature can be lowered compared to when an inorganic precursor is used.

- the impurities may get into the metal oxide, adversely affecting the physical properties of the metal oxide and even the characteristics of a semiconductor device that uses the metal oxide.

- metal oxide that does not contain aluminum as a main component may affect the physical properties of the metal oxide.

- metal oxides that do not contain aluminum as a main component include indium zinc oxide (In-Zn oxide) and indium gallium zinc oxide (In-Ga-Zn oxide, also referred to as IGZO).

- the IGZO film when aluminum is present in an IGZO film in an oxidized state (such as Al 2 O 3 ), the IGZO film becomes highly resistive. If the highly resistive IGZO film is used in a semiconductor layer, the on-current of a transistor becomes low.

- aluminum has a high bond dissociation energy with oxygen and functions as a carrier suppressing element. Specifically, the bond dissociation energy between aluminum and oxygen is higher than the bond dissociation energy between Ga and oxygen. For this reason, the presence of aluminum in the IGZO film can make it difficult for oxygen vacancies (Vo) to be generated. If an IGZO film in which Vo is difficult to generate is used as the semiconductor layer, it is possible to suppress the negative bias light deterioration of the transistor. For this reason, it is not necessary to completely remove aluminum from the metal oxide, and in some cases aluminum may be included in the metal oxide to an extent that does not have a detrimental effect.

- a precursor with a low aluminum content is used to produce a metal oxide that does not contain aluminum as a main component. This makes it possible to prevent the aluminum concentration in the formed metal oxide film from becoming too high.

- metal oxide when metal oxide is formed using the ALD method, it may be difficult to sufficiently remove impurities in the film even if the metal oxide is subjected to a heat treatment after film formation.

- a high-temperature process e.g., a process exceeding 700°C

- productivity decreases.

- the carbon concentration in the film is reduced by supplying a sufficient amount of oxidizing agent, for example, by making the total time of the step of supplying the oxidizing agent in the entire process of forming the metal oxide film sufficiently long, or by increasing the proportion of ozone (O 3 ) contained in the oxidizing agent.

- a microwave treatment in an oxygen-containing atmosphere as an impurity removal treatment.

- impurities in the film can be removed. This makes it possible to suppress impurities contained in raw materials such as precursors from remaining in the metal oxide. Therefore, the impurity concentration in the metal oxide can be reduced. Also, the crystallinity of the metal oxide can be increased.

- an impurity removal process intermittently in an oxygen-containing atmosphere during film formation.

- the impurity removal process may be performed both during and after film formation.

- a metal oxide with a low impurity content can be formed for use in the semiconductor layer of a fine transistor.

- a metal oxide with high crystallinity can be formed for use in the semiconductor layer of a fine transistor. This makes it possible to realize a transistor that is fine and has good electrical characteristics. In addition, it makes it possible to realize a transistor that is fine and has good reliability. In particular, it is preferable to form a metal oxide with a CAAC structure.

- one aspect of the present invention is a method for forming a metal oxide film, comprising a first step of supplying a first compound containing indium into a chamber, and then supplying an oxidizing agent into the chamber, and a second step of supplying a second compound into the chamber, and then supplying an oxidizing agent into the chamber.

- the method may further comprise a third step of supplying a third compound into the chamber, and then supplying an oxidizing agent into the chamber.

- the aluminum content of the first compound is preferably 0.001 ppm or more, 0.01 ppm or more, or 0.1 ppm or more, and is preferably 1000 ppm or less, more preferably 500 ppm or less, more preferably 100 ppm or less, more preferably 50 ppm or less, more preferably 10 ppm or less, and even more preferably 1 ppm or less.

- the second compound and the third compound each preferably contain at least one of gallium, tin, and zinc.

- the preferred range of the aluminum content of the second compound and the aluminum content of the third compound is the same as the preferred range of the aluminum content of the first compound.

- the total time for supplying the oxidizing agent in one cycle is preferably 10 seconds or more, more preferably 30 seconds or more, more preferably 60 seconds or more, more preferably 90 seconds or more, even more preferably 120 seconds or more, and preferably 150 seconds or less, 200 seconds or less, 250 seconds or less, or 300 seconds or less.

- one cycle is performed by carrying out the above-mentioned first step and second step once each.

- the total time for supplying the oxidizing agent in one cycle corresponds to the sum of the time for supplying the oxidizing agent in the first step and the time for supplying the oxidizing agent in the second step.

- one cycle is performed by carrying out the above-mentioned first step, second step, and third step once each.

- the total time for supplying the oxidizing agent in one cycle corresponds to the sum of the time for supplying the oxidizing agent in the first to third steps.

- the proportion of ozone in the gas is preferably 10% or more, more preferably 20% or more, more preferably 30% or more, more preferably 40% or more, more preferably 50% or more, more preferably 60% or more, more preferably 70% or more, more preferably 80% or more, more preferably 90% or more, and particularly preferably 100%.

- a higher proportion of ozone is preferable because it promotes the oxidation of the metal and reduces the carbon concentration in the metal oxide.

- the substrate temperature When supplying the oxidizing agent, it is preferable to set the substrate temperature to 150°C or higher, 200°C or higher, or 250°C or higher.

- the upper limit of the substrate temperature can be the lower of the decomposition temperature of the precursor such as the first compound and the decomposition temperature of ozone (e.g., 300°C). Increasing the substrate temperature is preferable because it reduces the impurity concentration in the metal oxide.

- an impurity removal treatment is preferably performed under an atmosphere containing oxygen.

- the impurity removal treatment is a treatment for releasing impurities contained in the metal oxide from the film.

- impurity removal treatments include plasma treatment, microwave treatment, and heat treatment.

- the substrate temperature is at least room temperature (e.g., 25°C), at least 100°C, at least 200°C, at least 300°C, or at least 400°C, and at most 500°C, or at most 450°C. It is also preferable that the heat treatment temperature is at least 100°C, at least 200°C, at least 300°C, or at least 400°C, and at most 500°C, or at most 450°C.

- the temperature during the impurity removal process is preferably set to a temperature equal to or lower than the maximum temperature in the manufacturing process of a transistor or semiconductor device, in particular, so that the content of impurities in the metal oxide can be reduced without reducing productivity.

- the productivity of a transistor or semiconductor device can be increased by setting the maximum temperature in the manufacturing process of a transistor or semiconductor device using the metal oxide of one embodiment of the present invention to 500° C. or lower, preferably 450° C. or lower.

- the impurity removal process is preferably performed at a temperature lower than the decomposition temperature of both the first compound and the second compound. Furthermore, when a third compound is used, it is preferable to perform the process at a temperature lower than the decomposition temperature of the third compound. Furthermore, the impurity removal process may be performed at a temperature higher than 500°C (for example, higher than 500°C and equal to or lower than 700°C).

- the impurity removal process may be performed while irradiating light (e.g., ultraviolet light). This can promote the desorption of impurities.

- light sources include lasers and mercury lamps.

- oxygen radicals can be generated by photoexcitation and reacted with hydrogen, carbon, nitrogen, etc., to reduce impurities in the film and promote crystallization. By irradiating light, it may be easier to remove impurities even at a lower heating temperature than when light irradiation is not performed.

- light may be irradiated during film formation.

- first step light may be irradiated onto the surface on which the metal oxide is to be formed while the first compound is being supplied into the chamber and/or while the oxidizing agent is being supplied into the chamber.

- second and third steps may be irradiated onto the surface on which the metal oxide is to be formed while the first compound is being supplied into the chamber and/or while the oxidizing agent is being supplied into the chamber.

- first and second steps it is preferable to perform the first and second steps at least once each and then perform an impurity removal process in an oxygen-containing atmosphere as a first cycle, and to perform the first and second steps at least once each in an order different from that of the first cycle and then perform an impurity removal process in an oxygen-containing atmosphere as a second cycle, and to alternately repeat the first and second cycles multiple times.

- the impurity removal treatment for example, every time the first step or the second step is carried out fewer times, or every time both steps are carried out in a range of 5 to 10 times.

- impurities may not be sufficiently removed by simply performing an impurity removal process after forming a metal oxide film.

- an impurity removal process By introducing an impurity removal process intermittently (at intervals) during film formation, it is possible to sufficiently remove impurities from the metal oxide.

- Another aspect of the present invention is a method for forming a film of an indium compound using an ALD method, in which a precursor containing indium (e.g., triethylindium precursor) is supplied into a chamber, and then an oxidizing agent is supplied into the chamber.

- the aluminum content of the precursor is preferably 0.001 ppm or more, 0.01 ppm or more, or 0.1 ppm or more, and is preferably 1000 ppm or less, more preferably 500 ppm or less, more preferably 100 ppm or less, more preferably 50 ppm or less, more preferably 10 ppm or less, and even more preferably 1 ppm or less.

- Metal oxides may have lattice defects.

- Lattice defects include point defects such as atomic vacancies and heteroatoms, line defects such as dislocations, surface defects such as grain boundaries, and volume defects such as voids.

- Factors that cause the generation of lattice defects include a deviation in the ratio of the number of atoms of the constituent elements (an excess or deficiency of constituent atoms) and impurities.

- the metal oxide used in the semiconductor layer of a transistor When a metal oxide is used in the semiconductor layer of a transistor, lattice defects in the metal oxide can cause carrier generation or capture. Therefore, if a metal oxide with many lattice defects is used in the semiconductor layer of a transistor, the electrical characteristics of the transistor may become unstable. Therefore, it is preferable that the metal oxide used in the semiconductor layer of a transistor has few lattice defects.

- V O H oxygen vacancies

- the transistor is likely to have normally-on characteristics (characteristics in which a channel exists and a current flows through the transistor even when no voltage is applied to the gate electrode). Therefore, it is preferable that oxygen vacancies and impurities are reduced as much as possible in the channel formation region in the metal oxide. In other words, it is preferable that the carrier concentration of the channel formation region in the metal oxide is reduced and the channel formation region in the metal oxide is made i-type (intrinsic) or substantially i-type.

- the types of lattice defects likely to exist in metal oxides and the amount of lattice defects present vary depending on the structure of the metal oxide or the method of forming the metal oxide film.

- Non-single crystal structures include, for example, CAAC structures, polycrystalline structures, nc structures, pseudo-amorphous (a-like) structures, and amorphous structures.

- A-like structures have a structure between the nc structure and the amorphous structure.

- the crystallinity of the metal oxide of one embodiment of the present invention is not particularly important.

- metal oxides having an a-like structure and metal oxides having an amorphous structure have voids or low-density regions. That is, metal oxides having an a-like structure and metal oxides having an amorphous structure have lower crystallinity than metal oxides having an nc structure and metal oxides having a CAAC structure. In addition, metal oxides having an a-like structure have a higher hydrogen concentration in the metal oxide than metal oxides having an nc structure and metal oxides having a CAAC structure. Therefore, lattice defects are easily generated in metal oxides having an a-like structure and metal oxides having an amorphous structure.

- a metal oxide having a crystal part for the semiconductor layer of the transistor it is preferable to use a metal oxide having high crystallinity.

- a metal oxide having a CAAC structure or a metal oxide having a single crystal structure By using such a metal oxide for the transistor, it is possible to realize a transistor having good electrical characteristics. In addition, it is possible to realize a highly reliable transistor.

- a metal oxide for the channel formation region of the transistor, which increases the on-current of the transistor.

- the crystal has a crystal structure in which multiple layers (for example, a first layer, a second layer, and a third layer) are stacked. That is, the crystal has a layered crystal structure (also called a layered crystal or layered structure). In this case, the c-axis of the crystal is oriented in the direction in which the multiple layers are stacked.

- metal oxides having the crystal include single crystal oxide semiconductors and CAAC-OS (c-axis aligned crystalline oxide semiconductors).

- the c-axis of the crystal in the normal direction to the surface on which the metal oxide is formed or the film surface. This allows the multiple layers to be arranged parallel or approximately parallel to the surface on which the metal oxide is formed or the film surface. In other words, the multiple layers extend in the channel length direction.

- the above three-layered crystal structure has the following structure.

- the first layer has an atomic coordination structure of an oxygen octahedron with the metal of the first layer at the center.

- the second layer has an atomic coordination structure of an oxygen trigonal bipyramid or tetrahedron with the metal of the second layer at the center.

- the third layer has an atomic coordination structure of an oxygen trigonal bipyramid or tetrahedron with the metal of the third layer at the center.

- the crystal structure of the above crystals includes, for example, a YbFe 2 O 4 type structure, a Yb 2 Fe 3 O 7 type structure, and modified structures thereof.

- each of the first layer to the third layer is preferably composed of one metal element or multiple metal elements having the same valence, and oxygen.

- the valence of the one or multiple metal elements constituting the first layer is preferably the same as the valence of the one or multiple metal elements constituting the second layer.

- the first layer and the second layer may have the same metal element.

- the valence of the one or multiple metal elements constituting the first layer is different from the valence of the one or multiple metal elements constituting the third layer.

- the above structure improves the crystallinity of the metal oxide and increases the mobility of the metal oxide. Therefore, by using the metal oxide in the channel formation region of a transistor, the on-state current of the transistor increases, and the electrical characteristics of the transistor can be improved.

- the metal oxide of one embodiment of the present invention preferably contains at least indium or zinc.

- metal elements include gallium and tin.

- the metal oxide is an In-M-Zn oxide having indium (In), element M, and zinc (Zn).

- the element M is gallium or tin.

- Other elements that can be used for element M include yttrium, boron, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium, calcium, cobalt, and aluminum.

- a combination of multiple elements mentioned above can be used as element M.

- metal oxides examples include indium zinc oxide (In-Zn oxide), indium tin oxide (In-Sn oxide), indium titanium oxide (In-Ti oxide), indium gallium oxide (In-Ga oxide), indium gallium tin oxide (In-Ga-Sn oxide), gallium zinc oxide (Ga-Zn oxide, also referred to as GZO), indium tin zinc oxide (In-Sn-Zn oxide, also referred to as ITZO (registered trademark)), indium titanium zinc oxide (In-Ti-Zn oxide), indium gallium zinc oxide (In-Ga-Zn oxide, also referred to as IGZO), and indium gallium tin zinc oxide (In-Ga-Sn-Zn oxide, also referred to as IGZTO).

- ITZO indium tin zinc oxide

- ITZO registered trademark

- the field effect mobility of the transistor can be increased.

- the metal oxide may have one or more metal elements with a higher period number in the periodic table instead of indium.

- the metal oxide may have one or more metal elements with a higher period number in addition to indium.

- Examples of metal elements with a higher period number include metal elements belonging to the fifth period and metal elements belonging to the sixth period.

- the metal elements include yttrium, zirconium, silver, cadmium, tin, antimony, barium, lead, bismuth, lanthanum, cerium, praseodymium, neodymium, promethium, samarium, and europium. Note that lanthanum, cerium, praseodymium, neodymium, promethium, samarium, and europium are called light rare earth elements.

- the metal oxide may also contain one or more nonmetallic elements.

- the field effect mobility of the transistor may be increased.

- nonmetallic elements include carbon, nitrogen, phosphorus, sulfur, selenium, fluorine, chlorine, bromine, and hydrogen.

- the metal oxide becomes highly crystalline, and the diffusion of impurities in the metal oxide can be suppressed. Therefore, fluctuations in the electrical characteristics of the transistor can be suppressed, and reliability can be improved.

- the formation of oxygen vacancies in the metal oxide can be suppressed. Therefore, carrier generation due to oxygen vacancies can be suppressed, and a transistor with a small off-current can be obtained. Furthermore, fluctuations in the electrical characteristics of the transistor can be suppressed, and reliability can be improved.

- the transistor can obtain a large on-current and high frequency characteristics.

- In-Ga-Zn oxide may be used as an example of a metal oxide.

- the metal oxide film formation method of the present invention it is preferable to deposit atoms one layer at a time.

- the ALD method is used, so that it is easy to form a metal oxide having the above-mentioned layered crystal structure.

- Examples of the ALD method include the Thermal ALD method, in which the reaction between the precursor and reactant is carried out using only thermal energy, and the Plasma Enhanced ALD (PEALD) method, in which a plasma-excited reactant is used.

- Thermal ALD method in which the reaction between the precursor and reactant is carried out using only thermal energy

- PEALD Plasma Enhanced ALD

- the ALD method can deposit atoms one layer at a time, and therefore has the following advantages: extremely thin films can be formed; films can be formed on structures with high aspect ratios; films can be formed with fewer defects such as pinholes; films can be formed with excellent coverage; and films can be formed at low temperatures.

- the PEALD method may be preferable because it can form films at lower temperatures by using plasma.

- some precursors used in the ALD method contain elements such as carbon or chlorine.

- films formed by the ALD method may contain more elements such as carbon or chlorine than films formed by other film formation methods. Note that the quantification of these elements can be performed using XPS or SIMS.

- the metal oxide film formation method of one embodiment of the present invention uses the ALD method, but adopts one or both of the conditions of a high substrate temperature during film formation and the implementation of an impurity removal process, and therefore the amount of carbon and chlorine contained in the film may be smaller than when the ALD method is used without applying these.

- the ALD method is a film formation method in which a film is formed by a reaction on the surface of a workpiece, unlike a film formation method in which particles released from a target are deposited. Therefore, it is a film formation method that is not easily affected by the shape of the workpiece and has good step coverage.

- the ALD method has excellent step coverage and excellent thickness uniformity, making it suitable for coating the surface of an opening with a high aspect ratio.

- the ALD method since the ALD method has a relatively slow film formation speed, it may be preferable to use it in combination with other film formation methods such as a sputtering method or a CVD method, which have a fast film formation speed.

- a method of forming a first metal oxide film using a sputtering method and forming a second metal oxide film on the first metal oxide using an ALD method can be mentioned.

- the second metal oxide may grow as a crystal with the crystal part as a nucleus.

- the ALD method can control the composition of the resulting film by the amount of raw material gas introduced.

- the ALD method can form a film of any composition by adjusting the amount of raw material gas introduced, the number of introductions (also called the number of pulses), the time required for one pulse (also called the pulse time), and the like.

- the ALD method can form a film whose composition changes continuously by changing the raw material gas while forming the film.

- the time required for film formation can be shortened compared to forming a film using multiple film formation chambers because no time is required for transportation and pressure adjustment. Therefore, the productivity of semiconductor devices can be increased in some cases.

- a transistor with high field effect mobility can be realized.

- a highly reliable transistor can be realized.

- a miniaturized or highly integrated transistor can be realized. For example, a transistor with a channel length of 2 nm to 30 nm can be manufactured.

- the carrier concentration of the channel formation region of the oxide semiconductor is preferably 1 ⁇ 10 18 cm ⁇ 3 or less, 1 ⁇ 10 17 cm ⁇ 3 or less, 1 ⁇ 10 16 cm ⁇ 3 or less, 1 ⁇ 10 15 cm ⁇ 3 or less, 1 ⁇ 10 14 cm ⁇ 3 or less, 1 ⁇ 10 13 cm ⁇ 3 or less, 1 ⁇ 10 12 cm ⁇ 3 or less, 1 ⁇ 10 11 cm ⁇ 3 or less, or 1 ⁇ 10 10 cm ⁇ 3 or less.

- the lower limit of the carrier concentration of the channel formation region is not particularly limited, but can be, for example, 1 ⁇ 10 ⁇ 9 cm ⁇ 3 .

- the impurity concentration in the oxide semiconductor film is reduced to reduce the density of defect states.

- a low impurity concentration and a low density of defect states are referred to as high-purity intrinsic or substantially high-purity intrinsic.

- an oxide semiconductor with a low carrier concentration may be referred to as a high-purity intrinsic or substantially high-purity intrinsic oxide semiconductor.

- a highly pure intrinsic or substantially highly pure intrinsic oxide semiconductor film may have a low density of trap states because of its low density of defect states.

- the charge trapped in the trap states of the oxide semiconductor takes a long time to disappear and may behave as if it were a fixed charge. Therefore, a transistor in which a channel formation region is formed in an oxide semiconductor with a high density of trap states may have unstable electrical characteristics.

- an impurity in an oxide semiconductor refers to, for example, anything other than the main component that constitutes the oxide semiconductor.

- an element with a concentration of less than 0.1 atomic % can be considered an impurity.

- the band gap of the oxide semiconductor is preferably larger than that of silicon (typically 1.1 eV), and is preferably 2 eV or more, more preferably 2.5 eV or more, and further preferably 3.0 eV or more.

- the off-state current (also referred to as Ioff) of the transistor can be reduced.

- OS transistors use oxide semiconductors, which are semiconductor materials with a wide band gap, and therefore the short channel effect can be suppressed. In other words, OS transistors are transistors that do not have the short channel effect or have an extremely small short channel effect.

- the short channel effect is a degradation of electrical characteristics that becomes evident as transistors are miniaturized (channel length is reduced).

- Specific examples of short channel effects include a decrease in threshold voltage, an increase in subthreshold swing value (sometimes referred to as S value), and an increase in leakage current.

- S value refers to the amount of change in gate voltage in the subthreshold region that changes the drain current by one order of magnitude at a constant drain voltage.

- characteristic length is widely used as an index of resistance to short channel effects.

- Characteristic length is an index of how easily the potential of the channel formation region bends. The smaller the characteristic length, the steeper the potential rises, and therefore the more resistant it is to short channel effects.

- OS transistors are accumulation-type transistors, while Si transistors are inversion-type transistors. Therefore, compared to Si transistors, OS transistors have smaller characteristic lengths between the source region and the channel-forming region, and between the drain region and the channel-forming region. Therefore, OS transistors are more resistant to the short-channel effect than Si transistors. In other words, when it is desired to manufacture a transistor with a short channel length, OS transistors are more suitable than Si transistors.

- the OS transistor can also be regarded as having an n + / n ⁇ /n + accumulation-type junction-less transistor structure or an n + /n ⁇ /n + accumulation-type non-junction transistor structure in which the channel formation region is an n ⁇ type region and the source and drain regions are n + type regions.

- the OS transistor can have good electrical characteristics even when the semiconductor device is miniaturized or highly integrated. For example, good electrical characteristics can be obtained even when the channel length or gate length of the OS transistor is 20 nm or less, 15 nm or less, 10 nm or less, 7 nm or less, or 6 nm or less, and 1 nm or more, 3 nm or more, or 5 nm or more.

- the gate length is the length of the gate electrode in the direction in which carriers move inside the channel formation region when the transistor is operating.

- the cutoff frequency of the transistor can be improved.

- the cutoff frequency of the transistor can be set to, for example, 50 GHz or more, preferably 100 GHz or more, and more preferably 150 GHz or more in a room temperature environment.

- an oxide semiconductor contains a large amount of aluminum unintentionally, the physical properties of the oxide semiconductor may be affected. For example, if aluminum is present in an oxidized state (such as Al 2 O 3 ), the resistance of the oxide semiconductor increases. If an oxide semiconductor with a high resistance is used in a channel formation region of a transistor, the on-state current of the transistor decreases.

- aluminum has a high bond dissociation energy with oxygen and functions as a carrier suppressing element.

- the presence of aluminum in an oxide semiconductor can make it difficult for oxygen vacancies (Vo) to be generated. If an oxide semiconductor in which Vo is unlikely to be generated is used in the channel formation region of a transistor, negative bias light photodegradation of the transistor can be suppressed.

- the aluminum concentration in the oxide semiconductor so that the reliability and electrical characteristics of the transistor are both good.

- the aluminum concentration in the channel formation region of the oxide semiconductor obtained by STEM-EDX is preferably 0.01 atomic% or more, and preferably 10 atomic% or less, more preferably 5 atomic% or less, more preferably 3 atomic% or less, more preferably 1 atomic% or less, and even more preferably 0.1 atomic% or less. Or it may be 0.01 atomic% or less.

- the aluminum concentration in the channel formation region of the oxide semiconductor measured by SIMS is preferably 1 ⁇ 10 22 atoms/cm 3 or less, more preferably 1 ⁇ 10 21 atoms/cm 3 or less, still more preferably 1 ⁇ 10 20 atoms/cm 3 or less, still more preferably 5 ⁇ 10 19 atoms/cm 3 or less, still more preferably 1 ⁇ 10 19 atoms/cm 3 or less, still more preferably 5 ⁇ 10 18 atoms/cm 3 or less, and still more preferably 1 ⁇ 10 18 atoms/cm 3 or less.

- the presence of aluminum and the state of the aluminum present can be confirmed by the Al2p spectrum obtained by XPS analysis of an oxide semiconductor. For example, if the peak position is in the range of 74.2 eV to 74.8 eV, it can be said that aluminum is present in an oxidized state.

- the carbon concentration in a channel formation region of the oxide semiconductor measured by SIMS is 1 ⁇ 10 20 atoms/cm 3 or less, preferably 5 ⁇ 10 19 atoms/cm 3 or less, more preferably 3 ⁇ 10 19 atoms/cm 3 or less, more preferably 1 ⁇ 10 19 atoms/cm 3 or less, more preferably 3 ⁇ 10 18 atoms/cm 3 or less, and further preferably 1 ⁇ 10 18 atoms/cm 3 or less.

- the silicon concentration in the channel formation region of the oxide semiconductor measured by SIMS is 1 ⁇ 10 20 atoms/cm 3 or less, preferably 5 ⁇ 10 19 atoms/cm 3 or less, more preferably 3 ⁇ 10 19 atoms/cm 3 or less, more preferably 1 ⁇ 10 19 atoms/cm 3 or less, more preferably 3 ⁇ 10 18 atoms/cm 3 or less, and still more preferably 1 ⁇ 10 18 atoms/cm 3 or less.

- the nitrogen concentration in a channel formation region of an oxide semiconductor obtained by SIMS is set to 1 ⁇ 10 20 atoms/cm 3 or less, preferably 5 ⁇ 10 19 atoms/cm 3 or less, more preferably 1 ⁇ 10 19 atoms/cm 3 or less, more preferably 5 ⁇ 10 18 atoms/cm 3 or less, more preferably 1 ⁇ 10 18 atoms/cm 3 or less, and further preferably 5 ⁇ 10 17 atoms/cm 3 or less.

- Hydrogen contained in the oxide semiconductor reacts with oxygen bonded to a metal atom to form water, which may form an oxygen vacancy.

- an electron serving as a carrier may be generated.

- some of the hydrogen may bond to oxygen bonded to a metal atom to generate an electron serving as a carrier. Therefore, a transistor using an oxide semiconductor containing hydrogen is likely to have normally-on characteristics. For this reason, it is preferable that hydrogen in a channel formation region of the oxide semiconductor is reduced as much as possible.

- the hydrogen concentration in the channel formation region of the oxide semiconductor obtained by SIMS is 1 ⁇ 10 20 atoms/cm 3 or less, preferably 5 ⁇ 10 19 atoms/cm 3 or less, more preferably 1 ⁇ 10 19 atoms/cm 3 or less, more preferably 5 ⁇ 10 18 atoms/cm 3 or less, and further preferably 1 ⁇ 10 18 atoms/cm 3 or less.

- the concentration of the alkali metal or the alkaline earth metal in a channel formation region of the oxide semiconductor obtained by SIMS is set to 1 ⁇ 10 18 atoms/cm 3 or less, preferably 2 ⁇ 10 16 atoms/cm 3 or less.

- a first source gas (sometimes called a precursor, precursor, or metal precursor) for the reaction and a second source gas (sometimes called a reactant, reactant, oxidizer, or nonmetal precursor) are alternately introduced into the chamber, and the introduction of these source gases is repeated to form a film.

- the introduction of the source gas can be switched, for example, by switching the respective switching valves (sometimes called high-speed valves).

- an inert gas such as nitrogen (N 2 ), argon (Ar), or helium (He) may be introduced into the chamber together with the source gas as a carrier gas.

- the uniformity of the film formed is also improved, which is preferable.

- precursor 11a is introduced into a chamber and the precursor 11a is adsorbed onto the surface of substrate 10.

- ALD window is determined by the temperature characteristics, vapor pressure, decomposition temperature, etc. of the precursor.

- an inert gas e.g., argon, helium, or nitrogen

- the second step is also called purging.

- vacuum exhaust refers to exhausting at a pressure at least lower than atmospheric pressure (reduced pressure state).

- a reactant 12a e.g., an oxidizing agent

- a reactant 12a is introduced into the chamber and reacted with the precursor 11a adsorbed on the surface of the substrate 10, so that some of the components contained in the precursor 11a are desorbed while the metal elements constituting the precursor 11a are still adsorbed on the substrate 10.

- a layer of oxide 13a formed by oxidizing part of the precursor 11a is formed on the surface of the substrate 10.

- the oxidizing agent may be ozone (O 3 ), oxygen (O 2 ), water (H 2 O), nitrogen dioxide (N 2 O), hydrogen peroxide (H 2 O 2 ), and plasma, radicals, ions, and the like of these.

- oxygen may be constantly supplied as an oxidizing agent and plasma may be generated in the third step.

- oxygen plasma is formed in the third step and functions as reactant 12a.

- a precursor 11a that does not react with oxygen heated to the above temperature may be used in any step other than the third step.

- precursor 11b having a metal element different from precursor 11a is introduced, and a process similar to the first step is carried out to adsorb precursor 11b onto the surface of the oxide layer 13a.

- the precursor 11b is adsorbed to the layer of oxide 13a, and a self-terminating mechanism of the surface chemical reaction is activated, so that the precursor 11b is not further adsorbed onto the layer of precursor 11b on the substrate 10.

- reactant 12b is introduced into the chamber, and a process similar to the third step is carried out. As a result, a layer of oxide 13b, which is formed by oxidizing a portion of precursor 11b, is formed on the layer of oxide 13a.

- Reactant 12b may be made of the same material as reactant 12a, or it may be made of a different material.

- steps 1 to 4 are performed to form a layer of oxide 13c on the layer of oxide 13b.

- a compound having a metal element different from that of precursors 11a and 11b is used as the precursor.

- the reactant may be the same material as one or both of reactants 12a and 12b, or may be a material different from either of them.

- an oxide layer can be formed by performing steps 1 to 4 as one set (also referred to as one cycle), and by repeating this set, a layered crystal structure in which multiple oxide layers are stacked can be formed.

- the thickness of the metal oxide with a layered crystal structure is preferably 1 nm or more and less than 100 nm, and more preferably 3 nm or more and less than 20 nm.

- the process shown in FIG. 1 is preferably performed while heating the substrate.

- the substrate temperature is preferably set to 200° C. or higher and 600° C. or lower, and more preferably 300° C. or higher and 450° C. or lower.

- the substrate temperature is preferably set to a temperature lower than the decomposition temperature of any of the precursors used. This allows the multiple types of precursors used to be adsorbed onto the target (e.g., substrate) during film formation by the ALD method without being decomposed.

- impurities such as hydrogen or carbon contained in the precursor or reactant can be removed from the metal oxide in each of the first to fourth steps.

- carbon in the metal oxide can be released as CO 2 or CO.

- hydrogen in the metal oxide can be released as H 2 O.

- rearrangement of metal atoms and oxygen atoms can be performed, and each oxide layer can be arranged with high order. Therefore, a metal oxide with a highly crystalline layered crystal structure, particularly a metal oxide with a CAAC structure, can be formed.

- FIG. 1A illustrates an example of a configuration in which precursor 11a is adsorbed onto substrate 10, but is not limited to this.

- an insulating film insulating film having one or more of oxygen, nitrogen, silicon, aluminum, hafnium, etc.

- a conductive film conductive film having one or more of tungsten, tantalum, molybdenum, zirconium, aluminum, titanium, etc.

- precursor 11a may be adsorbed onto a structure formed of an insulating film, a conductive film, etc. on substrate 10.

- the decomposition temperature of the precursor used in the film formation is not too low.

- the decomposition temperature of the precursor is preferably 200°C or higher and 700°C or lower, more preferably 300°C or higher and 650°C or lower, and even more preferably 400°C or higher and 600°C or lower.

- Inorganic precursors contain less impurities such as hydrogen and carbon, and can prevent an increase in the impurity concentration in the metal oxide film being formed. On the other hand, inorganic precursors tend to have a higher decomposition temperature than organic precursors.

- a method for forming a metal oxide film uses an organic precursor, forms the film while heating the substrate, and performs an impurity removal process, thereby suppressing an increase in the impurity concentration in the metal oxide film being formed.

- the frequency of the impurity removal treatment is not particularly limited. A higher frequency is preferable because it is easier to remove impurities, but there is a risk of lower productivity. A lower frequency is preferable because it is possible to shorten the time of the metal oxide film formation process, but there is a risk of impurities not being sufficiently removed.

- the impurity removal treatment can be performed each time one of oxides 13a to 13c is formed, but it is preferable to perform the impurity removal treatment each time multiple oxide layers are formed or multiple stacked structures 14 are formed, because this simplifies the process.

- the impurity removal treatment may be performed once after the metal oxide film formation is completed.

- the impurity removal treatment may be performed every time n oxide layers (n is an integer of 1 to 100, preferably an integer of 2 to 50, more preferably an integer of 5 to 30) are formed.

- a metal oxide can be formed by repeatedly forming oxides 13a, 13b, 13c, 13a, and 13b in this order, performing the impurity removal treatment, forming oxides 13c, 13a, 13b, 13c, and 13a in this order, performing the impurity removal treatment, forming oxides 13b, 13c, 13a, 13b, and 13c in this order, and performing the impurity removal treatment.

- an impurity removal process may be performed every time m layers (m is an integer between 1 and 50, preferably between 2 and 30, more preferably between 5 and 10) of the laminate structure 14 are formed.

- examples of impurity removal treatments include plasma treatment, microwave treatment, and heat treatment.

- the impurity removal treatment may also be performed while irradiating light.

- the chamber in which the impurity removal process is performed may be the same as the chamber in which the first to fourth steps are performed, or it may be a different chamber.

- the chamber for film formation and the chamber for impurity removal process may be the same or different.

- the substrate temperature is preferably set to room temperature (e.g., 25°C) or higher, 100°C or higher, 200°C or higher, 300°C or higher, or 400°C or higher, and 500°C or lower, or 450°C or lower.

- the temperature of the heat treatment is preferably set to 100°C or higher, 200°C or higher, 300°C or higher, or 400°C or higher, and 500°C or lower, or 450°C or lower.

- the temperature during the impurity removal treatment is preferably set to a temperature equal to or lower than the maximum temperature in the manufacturing process of the transistor or semiconductor device, in particular, so that the content of impurities in the metal oxide can be reduced without reducing productivity.

- the processing time of the third step can be extended to allow the plasma treatment to also function as an impurity removal treatment.

- the third step can be performed once out of multiple times for a longer processing time than the other times, making it a process that also serves as an impurity removal treatment.

- microwave processing refers to processing using, for example, a device having a power source that generates high-density plasma using microwaves.

- microwaves refer to electromagnetic waves having a frequency of 300 MHz or more and 300 GHz or less.

- Microwave processing can also be called microwave-excited high-density plasma processing.

- the microwave treatment it is preferable to use a microwave treatment device having a power source that generates high-density plasma using microwaves.

- the frequency of the microwave treatment device is preferably 300 MHz or more and 300 GHz or less, more preferably 2.4 GHz or more and 2.5 GHz or less, and can be set to, for example, 2.45 GHz.

- the power of the power source that applies microwaves in the microwave treatment device is preferably 1000 W or more and 10000 W or less, more preferably 2000 W or more and 5000 W or less.

- the microwave treatment device may have a power source that applies RF to the substrate side. In addition, by applying RF to the substrate side, oxygen ions generated by high-density plasma can be efficiently guided into the film.

- the microwave treatment is preferably carried out under reduced pressure, with the pressure being preferably from 10 Pa to 1000 Pa, and more preferably from 300 Pa to 700 Pa.

- the treatment temperature is preferably from room temperature (25°C) to 750°C, more preferably from 300°C to 500°C, and can be from 400°C to 450°C.

- a heat treatment may be performed continuously without exposure to the outside air.

- the temperature of the heat treatment is, for example, preferably 100°C or higher and 750°C or lower, more preferably 300°C or higher and 500°C or lower, and even more preferably 400°C or higher and 450°C or lower.

- the microwave treatment can be performed using, for example, oxygen gas and argon gas.

- the oxygen flow ratio ( O2 /( O2 +Ar)) is greater than 0% and less than 100%.

- the oxygen flow ratio ( O2 /( O2 +Ar)) is greater than 0% and less than 50%. More preferably, the oxygen flow ratio ( O2 /( O2 +Ar)) is greater than 10% and less than 40%. Even more preferably, the oxygen flow ratio ( O2 /( O2 +Ar)) is greater than 10% and less than 30%.

- the heat treatment is performed in a nitrogen gas or inert gas atmosphere, or in an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas.

- a nitrogen gas or inert gas atmosphere or in an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas.

- the heat treatment may be performed under reduced pressure.

- the heat treatment may be performed in an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas to compensate for the oxygen that has been desorbed.

- the heat treatment may be performed in an atmosphere of ultra-dry air (air with a water content of 20 ppm or less, preferably 1 ppm or less, preferably 10 ppb or less).

- the gas used in the heat treatment is highly purified.