WO2020225641A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- WO2020225641A1 WO2020225641A1 PCT/IB2020/053916 IB2020053916W WO2020225641A1 WO 2020225641 A1 WO2020225641 A1 WO 2020225641A1 IB 2020053916 W IB2020053916 W IB 2020053916W WO 2020225641 A1 WO2020225641 A1 WO 2020225641A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- oxide

- insulator

- transistor

- conductor

- oxygen

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 280

- 229910052738 indium Inorganic materials 0.000 claims description 19

- 229910052725 zinc Inorganic materials 0.000 claims description 10

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 claims 1

- 239000012212 insulator Substances 0.000 description 701

- 239000004020 conductor Substances 0.000 description 414

- 239000010408 film Substances 0.000 description 275

- 229910052760 oxygen Inorganic materials 0.000 description 195

- 239000001301 oxygen Substances 0.000 description 194

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 190

- 238000000034 method Methods 0.000 description 157

- 230000006870 function Effects 0.000 description 156

- 239000010410 layer Substances 0.000 description 151

- 229910052739 hydrogen Inorganic materials 0.000 description 121

- 239000001257 hydrogen Substances 0.000 description 121

- 229910044991 metal oxide Inorganic materials 0.000 description 118

- 150000004706 metal oxides Chemical class 0.000 description 116

- 239000012535 impurity Substances 0.000 description 110

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 108

- 230000015654 memory Effects 0.000 description 84

- 230000015572 biosynthetic process Effects 0.000 description 75

- 239000000758 substrate Substances 0.000 description 74

- 239000000463 material Substances 0.000 description 68

- 229910052814 silicon oxide Inorganic materials 0.000 description 67

- 238000010438 heat treatment Methods 0.000 description 66

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 60

- 229910001868 water Inorganic materials 0.000 description 60

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 59

- 229910052581 Si3N4 Inorganic materials 0.000 description 57

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 56

- 238000004544 sputter deposition Methods 0.000 description 56

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 52

- 239000011701 zinc Substances 0.000 description 51

- 238000000231 atomic layer deposition Methods 0.000 description 43

- 229910052782 aluminium Inorganic materials 0.000 description 40

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical group [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 40

- 238000005229 chemical vapour deposition Methods 0.000 description 40

- 238000009792 diffusion process Methods 0.000 description 39

- 229910052751 metal Inorganic materials 0.000 description 39

- 238000003860 storage Methods 0.000 description 38

- 239000002184 metal Substances 0.000 description 34

- 229910052735 hafnium Inorganic materials 0.000 description 33

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 29

- 150000004767 nitrides Chemical class 0.000 description 29

- 230000007547 defect Effects 0.000 description 28

- 239000012298 atmosphere Substances 0.000 description 27

- -1 silicon oxide nitride Chemical class 0.000 description 26

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 25

- 239000007789 gas Substances 0.000 description 24

- 229910052757 nitrogen Inorganic materials 0.000 description 24

- 206010021143 Hypoxia Diseases 0.000 description 23

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical group [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 22

- 238000004549 pulsed laser deposition Methods 0.000 description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 21

- 238000004519 manufacturing process Methods 0.000 description 21

- 238000001451 molecular beam epitaxy Methods 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- 230000003071 parasitic effect Effects 0.000 description 20

- 229910052715 tantalum Inorganic materials 0.000 description 20

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 20

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 19

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical group [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 19

- 238000010586 diagram Methods 0.000 description 19

- 239000013078 crystal Substances 0.000 description 18

- 150000002431 hydrogen Chemical class 0.000 description 18

- 238000007789 sealing Methods 0.000 description 18

- 229910052721 tungsten Inorganic materials 0.000 description 18

- 239000010937 tungsten Substances 0.000 description 18

- 229910052799 carbon Inorganic materials 0.000 description 17

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 17

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 17

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical group [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 16

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical group [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 16

- 229910052802 copper Inorganic materials 0.000 description 16

- 239000010949 copper Chemical group 0.000 description 16

- 229910052733 gallium Inorganic materials 0.000 description 16

- 239000002356 single layer Substances 0.000 description 16

- 229910052719 titanium Inorganic materials 0.000 description 16

- 239000010936 titanium Chemical group 0.000 description 16

- 238000013473 artificial intelligence Methods 0.000 description 15

- 230000005684 electric field Effects 0.000 description 14

- 230000008569 process Effects 0.000 description 14

- 238000004364 calculation method Methods 0.000 description 13

- 125000004429 atom Chemical group 0.000 description 12

- 230000004888 barrier function Effects 0.000 description 12

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 12

- 238000001312 dry etching Methods 0.000 description 12

- 238000005530 etching Methods 0.000 description 12

- 229910001195 gallium oxide Inorganic materials 0.000 description 12

- 238000012545 processing Methods 0.000 description 12

- 229910052707 ruthenium Inorganic materials 0.000 description 12

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 11

- 229910000449 hafnium oxide Inorganic materials 0.000 description 11

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 11

- 229910052759 nickel Inorganic materials 0.000 description 11

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 11

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical group [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 10

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 10

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 10

- 238000005259 measurement Methods 0.000 description 10

- 229910052750 molybdenum Inorganic materials 0.000 description 10

- 239000011733 molybdenum Substances 0.000 description 10

- 230000003647 oxidation Effects 0.000 description 10

- 238000007254 oxidation reaction Methods 0.000 description 10

- 230000002093 peripheral effect Effects 0.000 description 10

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 9

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 9

- 229910052731 fluorine Inorganic materials 0.000 description 9

- 239000011737 fluorine Substances 0.000 description 9

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 8

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 8

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 8

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 8

- 238000004140 cleaning Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 229910052746 lanthanum Inorganic materials 0.000 description 8

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 8

- 229910052749 magnesium Inorganic materials 0.000 description 8

- 239000011777 magnesium Substances 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 239000011347 resin Substances 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- 229910052726 zirconium Inorganic materials 0.000 description 8

- 229910052732 germanium Inorganic materials 0.000 description 7

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical group [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 7

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 7

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 7

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- 229910052727 yttrium Inorganic materials 0.000 description 7

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical group [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 7

- 229910001928 zirconium oxide Inorganic materials 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- 230000000903 blocking effect Effects 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 239000000470 constituent Substances 0.000 description 6

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 6

- 239000011261 inert gas Substances 0.000 description 6

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 6

- 239000002159 nanocrystal Substances 0.000 description 6

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 6

- 125000004430 oxygen atom Chemical group O* 0.000 description 6

- 239000012466 permeate Substances 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 239000011148 porous material Substances 0.000 description 6

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 6

- 238000001039 wet etching Methods 0.000 description 6

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 229910001873 dinitrogen Inorganic materials 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- 230000010354 integration Effects 0.000 description 5

- 229910052742 iron Inorganic materials 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 230000001590 oxidative effect Effects 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 239000002994 raw material Substances 0.000 description 5

- 229910052712 strontium Inorganic materials 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical group [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 150000004770 chalcogenides Chemical class 0.000 description 4

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 4

- 230000020169 heat generation Effects 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 4

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 4

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 4

- 229910001936 tantalum oxide Inorganic materials 0.000 description 4

- 229910052718 tin Inorganic materials 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052723 transition metal Inorganic materials 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 3

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 229910052790 beryllium Inorganic materials 0.000 description 3

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical group [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 230000002950 deficient Effects 0.000 description 3

- 238000006356 dehydrogenation reaction Methods 0.000 description 3

- 230000014509 gene expression Effects 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 3

- 239000000395 magnesium oxide Substances 0.000 description 3

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 3

- 238000002156 mixing Methods 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 239000013589 supplement Substances 0.000 description 3

- 229910052714 tellurium Inorganic materials 0.000 description 3

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- 229910052720 vanadium Inorganic materials 0.000 description 3

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical group [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 239000007864 aqueous solution Substances 0.000 description 2

- 238000013528 artificial neural network Methods 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 229910052798 chalcogen Inorganic materials 0.000 description 2

- 150000001787 chalcogens Chemical class 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000018044 dehydration Effects 0.000 description 2

- 238000006297 dehydration reaction Methods 0.000 description 2

- 238000003795 desorption Methods 0.000 description 2

- 238000010894 electron beam technology Methods 0.000 description 2

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 238000010606 normalization Methods 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- ITRNXVSDJBHYNJ-UHFFFAOYSA-N tungsten disulfide Chemical compound S=[W]=S ITRNXVSDJBHYNJ-UHFFFAOYSA-N 0.000 description 2

- 238000005406 washing Methods 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- FIPWRIJSWJWJAI-UHFFFAOYSA-N Butyl carbitol 6-propylpiperonyl ether Chemical compound C1=C(CCC)C(COCCOCCOCCCC)=CC2=C1OCO2 FIPWRIJSWJWJAI-UHFFFAOYSA-N 0.000 description 1

- 235000015842 Hesperis Nutrition 0.000 description 1

- 235000012633 Iberis amara Nutrition 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910016001 MoSe Inorganic materials 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 240000007594 Oryza sativa Species 0.000 description 1

- 235000007164 Oryza sativa Nutrition 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- 239000004783 Serene Substances 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- QIBVQUQUTLXVOH-UHFFFAOYSA-J [Se](=O)(=O)([O-])[O-].[Mo+4].[Se](=O)(=O)([O-])[O-] Chemical compound [Se](=O)(=O)([O-])[O-].[Mo+4].[Se](=O)(=O)([O-])[O-] QIBVQUQUTLXVOH-UHFFFAOYSA-J 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- WVMYSOZCZHQCSG-UHFFFAOYSA-N bis(sulfanylidene)zirconium Chemical compound S=[Zr]=S WVMYSOZCZHQCSG-UHFFFAOYSA-N 0.000 description 1

- 229910000416 bismuth oxide Inorganic materials 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000000921 elemental analysis Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 235000013305 food Nutrition 0.000 description 1

- 239000000446 fuel Substances 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910021389 graphene Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- NRJVMVHUISHHQB-UHFFFAOYSA-N hafnium(4+);disulfide Chemical compound [S-2].[S-2].[Hf+4] NRJVMVHUISHHQB-UHFFFAOYSA-N 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 239000002648 laminated material Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 235000011007 phosphoric acid Nutrition 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052699 polonium Inorganic materials 0.000 description 1

- HZEBHPIOVYHPMT-UHFFFAOYSA-N polonium atom Chemical compound [Po] HZEBHPIOVYHPMT-UHFFFAOYSA-N 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 239000011819 refractory material Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 235000009566 rice Nutrition 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- JLLMPOYODONDTH-UHFFFAOYSA-N selanylidenezirconium Chemical compound [Se].[Zr] JLLMPOYODONDTH-UHFFFAOYSA-N 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 239000011669 selenium Substances 0.000 description 1

- MTCFGRXMJLQNBG-UHFFFAOYSA-N serine Chemical compound OCC(N)C(O)=O MTCFGRXMJLQNBG-UHFFFAOYSA-N 0.000 description 1

- 229910021428 silicene Inorganic materials 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 235000013599 spices Nutrition 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000004506 ultrasonic cleaning Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 230000003313 weakening effect Effects 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

- H01L27/1207—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI combined with devices in contact with the semiconductor body, i.e. bulk/SOI hybrid circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1233—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with different thicknesses of the active layer in different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/03—Astable circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

Definitions

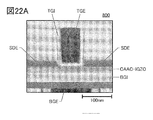

- Non-Patent Document 1 In oxide semiconductors, CAAC (c-axis aligned crystalline) structures and nc (nanocrystalline) structures that are neither single crystal nor amorphous have been found (see Non-Patent Document 1 and Non-Patent Document 2).

- the gate of the second transistor is electrically connected to the input terminal in, one of the source or drain of the second transistor is electrically connected to the output terminal out, and the other of the source or drain of the second transistor has a low power potential. Be supplied.

- the first transistor and the second transistor include an oxide semiconductor in the semiconductor layer. The first transistor and the second transistor each have a back gate.

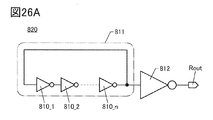

- Another aspect of the present invention is a semiconductor device including an n-stage (n is an odd number of 3 or more) inverter circuits, and the output of the i-stage (i is a natural number of 2 or more and n-1 or less) inverter circuit. Is electrically connected to the input of the i + 1th stage inverter circuit, and the output of the i-1st stage inverter circuit is electrically connected to the input of the ith stage inverter circuit.

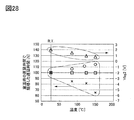

- the semiconductor device described above preferably has a function of adjusting the voltage supplied to the second back gate according to the operating temperature.

- the present invention it is possible to provide a semiconductor device having little variation in transistor characteristics. Further, according to one aspect of the present invention, it is possible to provide a semiconductor device having a large on-current. Further, according to one aspect of the present invention, it is possible to provide a semiconductor device having good electrical characteristics. Further, according to one aspect of the present invention, it is possible to provide a semiconductor device capable of miniaturization or high integration. Further, according to one aspect of the present invention, it is possible to provide a semiconductor device having good reliability. Further, according to one aspect of the present invention, a semiconductor device having low power consumption can be provided. Further, according to one aspect of the present invention, it is possible to provide a semiconductor device that operates stably even if the operating temperature changes.

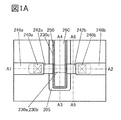

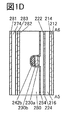

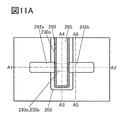

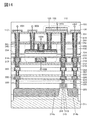

- FIG. 1A is a top view of the semiconductor device.

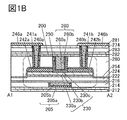

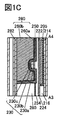

- 1B to 1D are cross-sectional views of a semiconductor device.

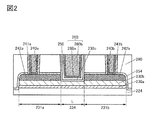

- FIG. 2 is a cross-sectional view of the semiconductor device.

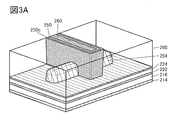

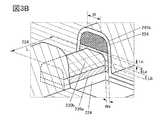

- 3A and 3B are perspective views of the semiconductor device.

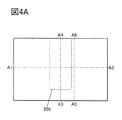

- 4A to 4D are views showing a method of manufacturing a semiconductor device.

- 5A to 5D are diagrams showing a method of manufacturing a semiconductor device.

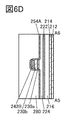

- 6A to 6D are diagrams showing a method of manufacturing a semiconductor device.

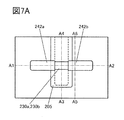

- 7A to 7D are diagrams showing a method of manufacturing a semiconductor device.

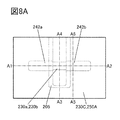

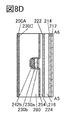

- 8A to 8D are diagrams showing a method of manufacturing a semiconductor device.

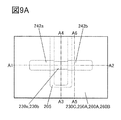

- 9A to 9D are diagrams showing a method of manufacturing a semiconductor device.

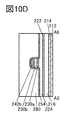

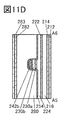

- 10A to 10D are diagrams showing a method for manufacturing a semiconductor device.

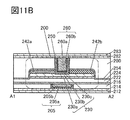

- FIG. 11A to 11D are diagrams showing a method of manufacturing a semiconductor device.

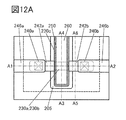

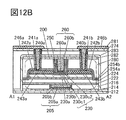

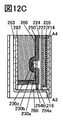

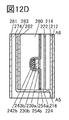

- FIG. 12A is a top view of the semiconductor device.

- 12B to 12D are cross-sectional views of the semiconductor device.

- 13A and 13B are cross-sectional views of the semiconductor device.

- FIG. 14 is a cross-sectional view of the semiconductor device.

- FIG. 15 is a cross-sectional view of the semiconductor device.

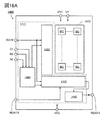

- FIG. 16A is a block diagram showing a configuration example of the storage device.

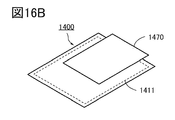

- FIG. 16B is a perspective view of the storage device.

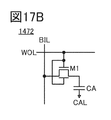

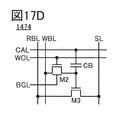

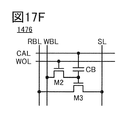

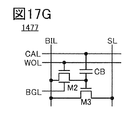

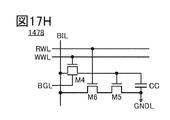

- 17A to 17H are circuit diagrams showing a configuration example of a memory cell.

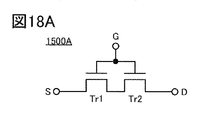

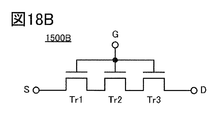

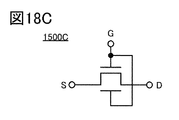

- 18A to 18D are diagrams showing circuit symbols of transistors.

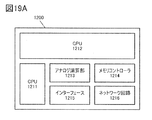

- 19A and 19B are schematic views of a semiconductor device.

- first and second ordinal numbers are used for convenience and do not indicate the process order or the stacking order. Therefore, for example, the "first” can be appropriately replaced with the “second” or “third” for explanation.

- the ordinal numbers described in the present specification and the like may not match the ordinal numbers used to specify one aspect of the present invention.

- a transistor is an element having at least three terminals including a gate, a drain, and a source. It also has a region (hereinafter, also referred to as a channel forming region) in which a channel is formed between the drain (drain terminal, drain region or drain electrode) and the source (source terminal, source region or source electrode). A current can flow between the source and the drain through the channel formation region.

- the channel formation region means a region in which a current mainly flows.

- the channel length is, for example, the source in the top view of the transistor, the region where the semiconductor (or the portion where the current flows in the semiconductor when the transistor is on) and the gate electrode overlap each other, or the channel formation region.

- the channel length does not always take the same value in all regions. That is, the channel length of one transistor may not be fixed to one value. Therefore, in the present specification, the channel length is set to any one value, the maximum value, the minimum value, or the average value in the channel formation region.

- the channel width is, for example, the channel length direction in the region where the semiconductor (or the portion where the current flows in the semiconductor when the transistor is on) and the gate electrode overlap each other in the top view of the transistor, or the channel formation region. Refers to the length of the channel formation region in the vertical direction with reference to. In one transistor, the channel width does not always take the same value in all regions. That is, the channel width of one transistor may not be fixed to one value. Therefore, in the present specification, the channel width is set to any one value, the maximum value, the minimum value, or the average value in the channel formation region.

- the channel width in the region where the channel is actually formed (hereinafter, also referred to as “effective channel width”) and the channel width shown in the top view of the transistor. (Hereinafter, also referred to as “apparent channel width”) and may be different.

- the effective channel width may be larger than the apparent channel width, and the influence thereof may not be negligible.

- the proportion of the channel forming region formed on the side surface of the semiconductor may be large. In that case, the effective channel width is larger than the apparent channel width.

- channel width may refer to an apparent channel width.

- channel width may refer to an effective channel width.

- the channel length, channel width, effective channel width, apparent channel width, and the like can be determined by analyzing a cross-sectional TEM image or the like.

- the semiconductor impurities are, for example, other than the main components constituting the semiconductor.

- an element having a concentration of less than 0.1 atomic% can be said to be an impurity. Due to the inclusion of impurities, for example, the defect level density of the semiconductor may increase or the crystallinity may decrease.

- the impurities that change the characteristics of the semiconductor include, for example, Group 1 elements, Group 2 elements, Group 13 elements, Group 14 elements, Group 15 elements, and oxide semiconductors.

- transition metals other than the main component such as hydrogen, lithium, sodium, silicon, boron, phosphorus, carbon, and nitrogen. Water may also function as an impurity.

- the oxide semiconductor to an oxygen vacancy V O: also referred to as oxygen vacancy

- normally off means that when a potential is not applied to the gate or a ground potential is applied to the gate, the drain current per 1 ⁇ m of the channel width flowing through the transistor is 1 ⁇ 10 ⁇ at room temperature. It means that it is 20 A or less, 1 ⁇ 10 -18 A or less at 85 ° C, or 1 ⁇ 10 -16 A or less at 125 ° C.

- the high power potential Vdd (hereinafter, also simply referred to as “Vdd”, “H potential”, or “H”) refers to the low power potential Vss (hereinafter, simply “Vss”, “L potential”). , Or also referred to as “L”), indicating a power supply potential with a higher potential. Further, Vss indicates a power supply potential having a potential lower than Vdd.

- the ground potential can also be used as Vdd or Vss. For example, when Vdd is the ground potential, Vss is a potential lower than the ground potential, and when V stability is the ground potential, Vdd is a potential higher than the ground potential.

- conductor 240 (conductor 240a and conductor 240b) that is electrically connected to the transistor 200 and functions as a plug.

- An insulator 241 (insulator 241a and insulator 241b) is provided in contact with the side surface of the conductor 240 that functions as a plug.

- a conductor 246 (conductor 246a and a conductor 246b) that is electrically connected to the conductor 240 and functions as wiring is provided.

- a first conductor of 240b is provided, and a second conductor of the conductor 240b is further provided inside.

- the height of the upper surface of the conductor 240 and the height of the upper surface of the insulator 281 can be made about the same.

- the transistor 200 shows a configuration in which the first conductor of the conductor 240 and the second conductor of the conductor 240 are laminated, but the present invention is not limited to this.

- the conductor 240 may be provided as a single layer or a laminated structure having three or more layers. When the structure has a laminated structure, an ordinal number may be given in the order of formation to distinguish them.

- the oxide 230c has a region in contact with the oxide 230b, a region overlapping with the side surface of the conductor 260 via the insulator 250, and a bottom surface of the conductor 260 via the insulator 250. Has a region that overlaps with.

- an In-M-Zn oxide having indium, element M and zinc (element M is aluminum, gallium, yttrium, tin, copper, vanadium, beryllium, boron, titanium, iron, nickel, germanium). , Zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium, etc. (one or more) and the like may be used. Further, as the oxide 230, an In—Ga oxide or an In—Zn oxide may be used.

- the oxide 230a and the oxide 230b and the oxide 230b and the oxide 230c have a common element other than oxygen as a main component.

- the defect level density at the interface between the oxide 230a and the oxide 230b and the interface between the oxide 230b and the oxide 230c can be lowered. Therefore, the influence of interfacial scattering on carrier conduction is reduced, and the transistor 200 can obtain a large on-current and high frequency characteristics.

- the conductor 260 has a conductor 260a and a conductor 260b, and the conductor 260a is arranged so as to wrap the bottom surface and the side surface of the conductor 260b.

- the conductor 260 functions as a first gate (also referred to as a top gate) electrode of the transistor 200.

- the resistance of the oxide semiconductor may be lowered.

- the electrical characteristics are liable to fluctuate, and reliability may deteriorate.

- the impurities include aluminum (Al) and silicon (Si).

- Aluminum and silicon have higher binding energies with oxygen than indium and zinc.

- In-M-Zn oxide when aluminum is mixed in the oxide semiconductor, oxygen contained in the oxide semiconductor is deprived by aluminum, so that oxygen is absorbed in the vicinity of indium or zinc. Defects may form.

- the oxide 230b has a region 231a (not shown in FIG. 3B) in contact with at least a part of the conductor 242a, a region 231b (not shown in FIG. 3B) in contact with at least a part of the conductor 242b, and a region. Between the 231a and the region 231b, there is a region 234 that functions as a channel forming region of the transistor 200.

- the region 234 has a region in which the oxide 230b and the conductor 260 overlap with each other in the oxide 230b.

- the region where the oxide 230b and the conductor 242a overlap can be rephrased as the region 231a, and the region where the oxide 230b and the conductor 242b overlap can be rephrased as the region 231b. ..

- the end portion of the side surface and the end portion of the upper surface are curved (hereinafter, also referred to as a round shape).

- the radius of curvature on the curved surface is La.

- La is the height of the upper surface of the oxide 230b in the region where the oxide 230b and the conductor 260 overlap when the lower surface of the insulator 224 is used as a reference in the cross-sectional view of the transistor 200 in the channel width direction.

- the side surface of the oxide 230b it may be regarded as the difference from the height of the lower end portion of the region having the curved surface.

- the transistor when impurities are mixed in the oxide semiconductor, a defect level or an oxygen defect may be formed. Therefore, when impurities are mixed in the channel formation region of the oxide semiconductor, the electrical characteristics of the transistor using the oxide semiconductor are liable to fluctuate, and the reliability may be deteriorated. Further, when the channel formation region contains oxygen deficiency, the transistor tends to have a normal-on characteristic (a characteristic that a channel exists even if a voltage is not applied to the gate electrode and a current flows through the transistor).

- the upper surface of the oxide 230b in the region 234 is lower than the upper surface of the oxide 230b in the region overlapping the conductor 242.

- Lc is preferably larger than 0 nm and smaller than the film thickness of the oxide 230b in the region overlapping the conductor 242.

- Lc is larger than 0 nm and 15 nm or less, preferably 0.5 nm or more and 10 nm or less, and more preferably 1 nm or more and 5 nm or less.

- the effective channel length on the upper surface of the region 234 is L + 2 ⁇ Lc. Therefore, by reducing Lc, it is possible to suppress a decrease in the on-current of the transistor.

- the amount of film loss on the side surface of the oxide 230b in the region where the oxide 230b and the conductor 260 overlap is defined as We.

- We is calculated as, for example, the difference between the side surface of the oxide 230b in the region overlapping the conductor 242 and the side surface of the oxide 230b in the region having no curved surface in the cross-sectional view of the transistor 200 in the channel width direction. can do.

- the difference between the length of the lower surface of the oxide 230b in the region overlapping the conductor 242 and the length of the lower surface of the oxide 230b in the region not overlapping the conductor 242. Can be calculated as half of.

- x i is the value of Vsh of the i-th transistor (i is an integer of 1 or more and n or less), and ⁇ is the average value of Vsh of n transistors.

- the standard deviation ⁇ of Vsh is specifically 60 mV or less, preferably 40 mV or less, and more preferably 20 mV or less.

- the impurity concentration in the channel forming region of the oxide semiconductor and its vicinity can be reduced.

- the concentration of impurities obtained by secondary ion mass spectrometry (SIMS) in the channel formation region of the oxide semiconductor and its vicinity is preferably 1 ⁇ 10 18 atoms / cm 3 or less. Is 2 ⁇ 10 16 atoms / cm 3 or less.

- the concentration of impurities obtained by elemental analysis using energy dispersive X-ray spectroscopy (EDX) in the channel formation region of the oxide semiconductor and its vicinity is reduced to 1.0 atomic% or less. To do.

- the concentration ratio of impurities to the element M is set to less than 0.10, preferably less than 0.05 in the channel formation region of the oxide semiconductor and its vicinity. ..

- the concentration of the element M used when calculating the concentration ratio may be the concentration in the same region as the region in which the concentration of impurities is calculated, or may be the concentration in the oxide semiconductor.

- the insulator 212, the insulator 214, the insulator 254, the insulator 282, the insulator 283 and the insulator 281 a hydrogen atom, a hydrogen molecule, a water molecule, a nitrogen atom, a nitrogen molecule, nitric oxide molecule (N 2 O)

- an insulating material having a function of suppressing the diffusion of impurities such as NO, NO 2

- copper atoms the above impurities are difficult to permeate

- it is preferable to use an insulating material having a function of suppressing the diffusion of oxygen for example, at least one oxygen atom, oxygen molecule, etc.) (the oxygen is difficult to permeate).

- the transistor 200 is surrounded by an insulator 212, an insulator 214, an insulator 254, an insulator 282, and an insulator 283 having a function of suppressing the diffusion of impurities such as water and hydrogen, and oxygen. Is preferable.

- the conductor 260 may function as a first gate (also referred to as a top gate) electrode. Further, the conductor 205 may function as a second gate electrode. In that case, the threshold voltage (Vth) of the transistor 200 can be controlled by changing the potential applied to the conductor 205 independently of the potential applied to the conductor 260 without interlocking with it. In particular, by applying a negative potential to the conductor 205, it is possible to increase the Vth of the transistor 200 and reduce the off-current. Therefore, when a negative potential is applied to the conductor 205, the drain current when the potential applied to the conductor 260 is 0 V can be made smaller than when it is not applied.

- Vth threshold voltage

- the conductor 205 may be provided larger than the size of the region that does not overlap with the conductor 242a and the conductor 242b of the oxide 230.

- the conductor 205 is also stretched in a region outside the end portion intersecting the channel width direction of the oxide 230. That is, it is preferable that the conductor 205 and the conductor 260 are superimposed via an insulator on the outside of the side surface of the oxide 230 in the channel width direction.

- the channel forming region of the oxide 230 is electrically surrounded by the electric field of the conductor 260 that functions as the first gate electrode and the electric field of the conductor 205 that functions as the second gate electrode. Can be done.

- the structure of the transistor that electrically surrounds the channel forming region by the electric fields of the first gate and the second gate is referred to as a surroundd channel (S-channel) structure.

- the transistor having the S-channel structure represents the structure of the transistor that electrically surrounds the channel forming region by the electric fields of one and the other of the pair of gate electrodes.

- the side surface and the periphery of the oxide 230 in contact with the conductor 242a and the conductor 242b functioning as the source electrode and the drain electrode are said to be type I as in the channel forming region. It has characteristics. Further, since the side surface and the periphery of the oxide 230 in contact with the conductor 242a and the conductor 242b are in contact with the insulator 280, they can be type I as in the channel formation region.

- type I can be treated as the same as high-purity authenticity described later.

- the S-channel structure disclosed in the present specification and the like is different from the Fin type structure and the planar type structure. By adopting the S-channel structure, it is possible to increase the resistance to the short-channel effect, in other words, to make a transistor in which the short-channel effect is unlikely to occur.

- the conductor 205 is stretched to function as wiring.

- the present invention is not limited to this, and a conductor that functions as wiring may be provided under the conductor 205. Further, it is not always necessary to provide one conductor 205 for each transistor. For example, the conductor 205 may be shared by a plurality of transistors.

- the conductor 205 shows a configuration in which the conductor 205a and the conductor 205b are laminated, but the present invention is not limited to this.

- the conductor 205 may be provided as a single layer or a laminated structure having three or more layers. When the structure has a laminated structure, an ordinal number may be given in the order of formation to distinguish them.

- the conductor 205a By using a conductive material having a function of suppressing the diffusion of oxygen for the conductor 205a, it is possible to prevent the conductor 205b from being oxidized and the conductivity from being lowered.

- the conductive material having a function of suppressing the diffusion of oxygen for example, tantalum, tantalum nitride, ruthenium, ruthenium oxide and the like are preferably used. Therefore, as the conductor 205a, the conductive material may be a single layer or a laminated material.

- the conductor 205a may be a laminate of tantalum, tantalum nitride, ruthenium, or ruthenium oxide and titanium or titanium nitride.

- the conductor 205b it is preferable to use a conductive material containing tungsten, copper, or aluminum as a main component.

- a conductive material containing tungsten, copper, or aluminum as a main component.

- the conductor 205b is shown as a single layer, it may have a laminated structure, for example, titanium or titanium nitride may be laminated with the conductive material.

- the insulator 222 it is preferable to use an insulator containing oxides of one or both of aluminum and hafnium, which are insulating materials.

- the insulator it is preferable to use aluminum oxide, hafnium oxide, an oxide containing aluminum and hafnium (hafnium aluminate) and the like.

- the insulator 222 releases oxygen from the oxide 230 to the substrate side and diffuses impurities such as hydrogen from the peripheral portion of the transistor 200 to the oxide 230. Functions as a layer that suppresses.

- the insulator 222 it is possible to suppress the diffusion of impurities such as hydrogen into the inside of the transistor 200 and suppress the generation of oxygen deficiency in the oxide 230. Further, it is possible to suppress the conductor 205 from reacting with the oxygen contained in the insulator 224 and the oxide 230.