WO2020196271A1 - 画像表示装置の製造方法および画像表示装置 - Google Patents

画像表示装置の製造方法および画像表示装置 Download PDFInfo

- Publication number

- WO2020196271A1 WO2020196271A1 PCT/JP2020/012313 JP2020012313W WO2020196271A1 WO 2020196271 A1 WO2020196271 A1 WO 2020196271A1 JP 2020012313 W JP2020012313 W JP 2020012313W WO 2020196271 A1 WO2020196271 A1 WO 2020196271A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- light emitting

- wiring

- image display

- layer

- semiconductor layer

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 61

- 238000000034 method Methods 0.000 title claims abstract description 34

- 239000004065 semiconductor Substances 0.000 claims abstract description 240

- 239000000758 substrate Substances 0.000 claims abstract description 78

- 238000005530 etching Methods 0.000 claims abstract description 16

- 238000006243 chemical reaction Methods 0.000 claims description 29

- 150000004767 nitrides Chemical class 0.000 claims description 4

- 230000000149 penetrating effect Effects 0.000 claims description 3

- 229910052594 sapphire Inorganic materials 0.000 claims description 2

- 239000010980 sapphire Substances 0.000 claims description 2

- 229910052710 silicon Inorganic materials 0.000 claims 3

- 239000010703 silicon Substances 0.000 claims 3

- 229910002601 GaN Inorganic materials 0.000 claims 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 claims 2

- 150000001875 compounds Chemical class 0.000 claims 2

- 238000010030 laminating Methods 0.000 abstract description 3

- 239000010410 layer Substances 0.000 description 381

- 239000010408 film Substances 0.000 description 144

- 239000011229 interlayer Substances 0.000 description 93

- 238000012986 modification Methods 0.000 description 31

- 230000004048 modification Effects 0.000 description 31

- 239000013078 crystal Substances 0.000 description 20

- 239000011347 resin Substances 0.000 description 17

- 229920005989 resin Polymers 0.000 description 17

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 10

- 238000010586 diagram Methods 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 238000012545 processing Methods 0.000 description 6

- 230000006798 recombination Effects 0.000 description 6

- 238000005215 recombination Methods 0.000 description 6

- 238000012546 transfer Methods 0.000 description 6

- 239000011248 coating agent Substances 0.000 description 5

- 238000000576 coating method Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 4

- 238000002844 melting Methods 0.000 description 4

- 230000008018 melting Effects 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 239000012790 adhesive layer Substances 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 239000003973 paint Substances 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 239000002096 quantum dot Substances 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- HIVGXUNKSAJJDN-UHFFFAOYSA-N [Si].[P] Chemical compound [Si].[P] HIVGXUNKSAJJDN-UHFFFAOYSA-N 0.000 description 1

- MXSJNBRAMXILSE-UHFFFAOYSA-N [Si].[P].[B] Chemical compound [Si].[P].[B] MXSJNBRAMXILSE-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- 230000000740 bleeding effect Effects 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000002788 crimping Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000004020 luminiscence type Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by at least one potential-jump barrier or surface barrier, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/102—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier

- H01L31/107—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier the potential barrier working in avalanche mode, e.g. avalanche photodiode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0075—Processes for devices with an active region comprising only III-V compounds comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0093—Wafer bonding; Removal of the growth substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/38—Devices specially adapted for multicolour light emission comprising colour filters or colour changing media [CCM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0066—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound

- H01L33/007—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

- H01L33/22—Roughened surfaces, e.g. at the interface between epitaxial layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/42—Transparent materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

Definitions

- An embodiment of the present invention relates to a method for manufacturing an image display device and an image display device.

- a self-luminous element As a self-luminous element, the appearance of a display device using a micro LED, which is a fine light emitting element, is expected.

- a method of manufacturing a display device using micro LEDs a method of sequentially transferring individually formed micro LEDs to a drive circuit has been introduced.

- the number of micro LED elements increases as the image quality becomes higher, such as full high-definition, 4K, 8K, etc.

- a large number of micro LEDs may be individually formed and sequentially transferred to a substrate on which a drive circuit or the like is formed.

- the transfer process requires a huge amount of time. Further, a poor connection between the micro LED and the drive circuit or the like may occur, resulting in a decrease in yield.

- a technique is known in which a semiconductor layer including a light emitting layer is grown on a Si substrate, electrodes are formed on the semiconductor layer, and then the electrodes are attached to a circuit board on which a drive circuit is formed (for example, Patent Document 1).

- the embodiment provides a method for manufacturing an image display device and an image display device in which the transfer process of the light emitting element is shortened and the yield is improved.

- the method for manufacturing an image display device includes a step of preparing a substrate in which a semiconductor layer including a light emitting layer is formed on a first substrate, and a second substrate in which a circuit including a circuit element is formed. , A step of laminating the semiconductor layer, a step of etching the semiconductor layer to form a light emitting element, a step of forming an insulating film covering the light emitting element, and a via penetrating the insulating film to reach the circuit. And the step of forming the light emitting element, the light emitting element and the circuit element on the side of the surface of the light emitting element facing the surface of the second substrate, and the light emitting element and the circuit element are electrically connected via the via. It is provided with a process of connecting the devices. The via connects the light emitting element and the circuit element provided in different layers to each other.

- the image display device includes a circuit element, a first wiring layer electrically connected to the circuit element, a first insulating film covering the circuit element and the first wiring layer, and the first insulating film.

- a light emitting element disposed on the insulating film, a second insulating film covering at least a part of the light emitting element, and a second insulating film electrically connected to the light emitting element and arranged on the second insulating film. It includes a wiring layer and a first via that penetrates the first insulating film and the second insulating film and electrically connects the first wiring layer and the second wiring layer.

- the image display device includes a plurality of transistors, a first wiring layer electrically connected to the plurality of conductors, the plurality of transistors, and a first insulating film covering the first wiring layer.

- a first conductive type first semiconductor layer disposed on the first insulating film, a light emitting layer disposed on the first semiconductor layer, and the first conductive layer disposed on the light emitting layer.

- a second semiconductor layer having a second conductive shape different from the shape, a second insulating film covering the first insulating film, the first semiconductor layer and the light emitting layer, and a second insulating film covering at least a part of the second semiconductor layer.

- a second wiring layer connected to transparent electrodes arranged on a plurality of exposed surfaces of the second semiconductor layer, which are each exposed from the second insulating film according to the plurality of transistors, and the first insulation. It includes a first via that penetrates the film and the second insulating film and electrically connects the wiring of the first wiring layer and the wiring of the second wiring layer.

- a manufacturing method of an image display device and an image display device in which the transfer process of the light emitting element is shortened and the yield is improved are realized.

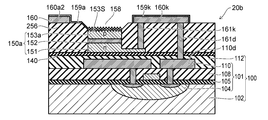

- FIG. 1 is a schematic cross-sectional view illustrating a part of the image display device according to the embodiment.

- FIG. 1 schematically shows the configuration of the sub-pixel 20 of the image display device of the present embodiment.

- the pixel 10 constituting the image displayed on the image display device is composed of a plurality of subpixels 20. In the following, it may be described using the three-dimensional coordinate system of XYZ.

- the subpixels 20 are arranged on a two-dimensional plane. Let the two-dimensional plane in which the subpixels 20 are arranged be the XY plane.

- the subpixels 20 are arranged along the X-axis direction and the Y-axis direction.

- the subpixel 20 has a light emitting surface 153S substantially parallel to the XY plane.

- the light emitting surface 153S mainly outputs light in the positive direction of the Z axis orthogonal to the XY plane.

- FIG. 1 schematically shows a cross section when the subpixel 20 is cut along a plane parallel to the XZ plane.

- This cross-sectional view is a cross-sectional view taken along the line AA'in FIG. 4, which will be described later.

- the subpixel 20 of the image display device includes a transistor 103, a first wiring layer 110, a first insulating film (interlayer insulating film) 112, a light emitting element 150, and a second insulation.

- a film (interlayer insulating film) 156, a second wiring layer 160, and a via 161d are provided.

- the subpixel 20 further includes a color filter 180.

- the color filter (wavelength conversion member) 180 is provided on the surface resin layer 170 via a transparent thin film adhesive layer 188.

- the surface resin layer 170 is provided on the light emitting element 150, the interlayer insulating film 156, and the wiring layer 160.

- the transistor 103 is formed on the substrate 102. As shown in FIGS. 3 and 12 described later, in addition to the transistor 103, circuit elements such as other transistors, resistors, and capacitors are formed on the substrate 102, and the circuit 101 is formed by wiring or the like. In the following, it is assumed that the circuit 101 includes an element forming region 104 in which a circuit element is formed, an insulating layer 105, a wiring layer 110, a via connecting the wiring layer 110 and the circuit element, and an insulating film 108 that insulates between the circuit elements. ..

- the circuit board 100 may include other components such as the substrate 102, the circuit 101, and the interlayer insulating film 112.

- the transistor 103 includes a p-type semiconductor region 104b, an n-type semiconductor region 104s and 104d, and a gate 107.

- the gate 107 is provided on the p-type semiconductor region 104b via the insulating layer 105.

- the insulating layer 105 is provided to insulate the element forming region 104 and the gate 107 and to sufficiently insulate the other adjacent circuit elements. When a voltage is applied to the gate 107, a channel can be formed in the p-type semiconductor region 104b.

- the transistor 103 is an n-channel MOSFET.

- the element forming region 104 is provided on the substrate 102.

- the substrate 102 is, for example, a Si substrate.

- the element forming region 104 includes a p-type semiconductor region 104b and an n-type semiconductor region 104s and 104d.

- the p-type semiconductor region 104b is provided near the surface of the substrate 102.

- the n-type semiconductor regions 104s and 104d are provided in the p-type semiconductor region 104b in the vicinity of the surface of the p-type semiconductor region 104b so as to be separated from each other.

- An insulating layer 105 is provided on the surface of the substrate 102.

- the insulating layer 105 also covers the element forming region 104, and also covers the surfaces of the p-type semiconductor region 104b and the n-type semiconductor regions 104s and 104d.

- the insulating layer 105 is, for example, SiO 2 .

- the insulating layer 105 may be a multi-layered insulating layer containing SiO 2 or Si 3 N 4 depending on the covering region.

- the insulating layer 105 may include a layer of an insulating material having a high dielectric constant.

- a gate 107 is provided on the p-type semiconductor region 104b via the insulating layer 105.

- the gate 107 is provided between the n-type semiconductor regions 104s and 104d.

- the gate 107 is, for example, polycrystalline Si.

- the gate 107 may contain silicide or the like having a resistance lower than that of polycrystalline Si.

- the gate 107 and the insulating layer 105 are covered with the insulating film 108.

- the insulating film 108 is, for example, SiO 2 or Si 3 N 4 or the like.

- an organic insulating film such as PSG (Phosphorus Silicon Glass) or BPSG (Boron Phosphorus Silicon Glass) may be further provided.

- a first wiring layer (first wiring layer) 110 is formed on the insulating film 108.

- the first wiring layer 110 includes a plurality of wirings having different potentials, and includes wirings 110s and 110d. As described above, in the cross-sectional views after FIG. 1, the code of the wiring layer is assumed to be displayed at a position next to one wiring included in the wiring layer.

- Vias 111s and 111d are provided between the wirings 110s and 110d of the wiring layer 110 and the n-type semiconductor regions 104s and 104d, respectively, and are electrically connected to each other.

- the wiring layer 110 and the vias 111s and 111d are formed of, for example, a metal such as Al or Cu.

- the wiring layer 110 and the vias 111s and 111d may contain a refractory metal or the like.

- a first interlayer insulating film 112 is further provided as a flattening film on the insulating film 108 and the wiring layer 110.

- the interlayer insulating film (first insulating film) 112 is, for example, an organic insulating film such as PSG or BPSG.

- the first interlayer insulating film 112 also functions as a protective film that protects the surface of the circuit board 100.

- a buffer layer 140 is provided over the interlayer insulating film 112.

- the buffer layer (buffer layer) 140 includes a nitride such as AlN. By providing the buffer layer 140, it can be expected to reduce crystal defects generated when the light emitting element 150 is epitaxially grown. As described above, the light emitting element 150 is directly provided on the first interlayer insulating film 112, not only when the buffer layer 140 is provided between the light emitting element 150 and the first interlayer insulating film 112. It may be.

- the wiring 110s in the circuit board 100 is provided so as to extend in the X-axis direction to the position where the light emitting element 150 is placed. As shown in FIG. 4, which will be described later, the wiring 110s extends in the Y-axis direction as long as or longer than the length of the light emitting element in the Y-axis direction.

- the outer circumference of the wiring 110s includes the outer circumference when the light emitting element 150 is projected from above the Z axis in the XY plan view.

- the wiring 110s can block the scattering of light downward from the light emitting element 150 so that it does not reach the transistor 103.

- the downward scattering of the light emitting element 150 can be reflected on the light emitting surface 153S side to improve the luminous efficiency.

- the wiring 110s blocks the scattered light below the light emitting element 150, the arrival of the light to the transistor 103 is suppressed, and the malfunction of the transistor 103 can be prevented.

- the light emitting element 150 includes an n-type semiconductor layer (first semiconductor layer) 151, a light emitting layer 152, and a p-type semiconductor layer (second semiconductor layer) 153.

- the n-type semiconductor layer 151, the light emitting layer 152, and the p-type semiconductor layer 153 are laminated in this order from the interlayer insulating film 112 of the circuit board 100 toward the positive direction of the Z axis, that is, toward the light emitting surface 153S.

- the light emitting element 150 has, for example, a substantially square or rectangular shape in XY plan view, but the corners may be rounded.

- the light emitting element 150 may have, for example, an elliptical shape or a circular shape in an XY plan view.

- the degree of freedom in layout is improved by appropriately selecting the shape and arrangement of the light emitting elements in a plan view.

- the n-type semiconductor layer 151 has a stepped portion 151a extending on the buffer layer 140 in the X-axis direction.

- the light emitting element 150 for example, a nitride semiconductor such as In X Al Y Ga 1-XY N (0 ⁇ X, 0 ⁇ Y, X + Y ⁇ 1) is preferably used.

- the light emitting element 150 is a so-called blue light emitting diode, and the wavelength of the light emitted by the light emitting element 150 is, for example, about 467 nm ⁇ 20 nm.

- the wavelength of the light emitted by the light emitting element 150 may be bluish purple emission of about 410 nm ⁇ 20 nm.

- the wavelength of the light emitted by the light emitting element 150 is not limited to the above-mentioned value, and may be appropriate.

- the second interlayer insulating film (second insulating film) 156 covers the buffer layer 140 and the light emitting element 150.

- the second interlayer insulating film 156 is formed of a transparent resin.

- the interlayer insulating film 156 also has a function of protecting the light emitting element 150 and flattening the surface due to the wiring layer 160 formed on the second interlayer insulating film 156.

- a via (second via) 161k is provided so as to penetrate the second interlayer insulating film 156.

- One end of the via 161k is connected to the step portion 151a.

- the via (first via) 161d is provided so as to penetrate the interlayer insulating films 112 and 156. One end of the via 161d is connected to the wiring 110d.

- the wiring layer 160 is provided on the flattened interlayer insulating film 156.

- the wiring layer 160 includes wirings 160a and 160k.

- the wiring 160a is connected to the p-type semiconductor layer 153 via a contact hole opened in the interlayer insulating film 156. Although not shown in this figure, the wiring 160a is connected to a power line that supplies power to the subpixel 20.

- the wiring 160k is connected to the other ends of the vias 161k and 161d. Therefore, the n-type semiconductor layer 151 of the light emitting element 150 is electrically connected to the main electrode of the transistor 103 via the vias 161k and 161d and the wirings 160k and 110d.

- the surface resin layer 170 covers the second interlayer insulating film 156 and the second wiring layer 160.

- the surface resin layer 170 is a transparent resin, protects the interlayer insulating film 156 and the wiring layer 160, and provides a flattening surface for adhering the color filter 180.

- the color filter 180 includes a light-shielding unit 181 and a color conversion unit 182.

- the color conversion unit 182 is provided directly above the light emitting surface 153S of the light emitting element 150 according to the shape of the light emitting surface 153S.

- the portion other than the color conversion unit 182 is a light-shielding unit 181.

- the light-shielding unit 181 is a so-called black matrix, which reduces bleeding due to color mixing of light emitted from the adjacent color conversion unit 182 and makes it possible to display a sharp image.

- the color conversion unit 182 has one layer or two layers.

- FIG. 1 shows a two-layer portion. Whether it is one layer or two layers is determined by the color of the light emitted by the subpixel 20, that is, the wavelength.

- the color conversion unit 182 preferably has two layers.

- the emission color of the subpixel 20 is blue, it is preferably one layer.

- the first layer closer to the light emitting element 150 is the color conversion layer 183

- the second layer is the filter layer 184. That is, the filter layer 184 is laminated on the color conversion layer 183.

- the color conversion layer 183 is a layer that converts the wavelength of the light emitted by the light emitting element 150 into a desired wavelength.

- the light having a wavelength of 467 nm ⁇ 20 nm of the light emitting element 150 is converted into light having a wavelength of, for example, about 630 nm ⁇ 20 nm.

- the light having a wavelength of 467 nm ⁇ 20 nm of the light emitting element 150 is converted into light having a wavelength of, for example, about 532 nm ⁇ 20 nm.

- the filter layer 184 blocks the wavelength component of blue light emission remaining without color conversion in the color conversion layer 183.

- the subpixel 20 may output the light through the color conversion layer 183, or outputs the light as it is without passing through the color conversion layer 183. You may do so.

- the wavelength of the light emitted by the light emitting element 150 is about 467 nm ⁇ 20 nm

- the subpixel 20 may output the light without passing through the color conversion layer 183.

- the wavelength of the light emitted by the light emitting element 150 is 410 nm ⁇ 20 nm, it is preferable to provide one color conversion layer 183 in order to convert the wavelength of the output light to about 467 nm ⁇ 20 nm.

- the subpixel 20 may have the filter layer 184.

- the filter layer 184 By providing the filter layer 184 on the blue subpixel 20, minute external light reflection generated on the surface of the light emitting element 150 is suppressed.

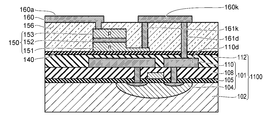

- FIGS. 2A and later are schematic cross-sectional views illustrating each modification of the image display device of the present embodiment.

- the display of the surface resin layer 170 and the color filter 180 is omitted in order to avoid complication.

- a surface resin layer and a color filter are provided on the second interlayer insulating film and the second wiring layer. The same applies to the cases of other embodiments and modifications thereof described later.

- the subpixels 20a and 20b have a configuration of the light emitting element 150a different from that of the first embodiment described above.

- the other components are the same as those in the first embodiment described above, and detailed description thereof will be omitted as appropriate.

- the subpixel 20a includes a light emitting element 150a.

- the light emitting element 150a is covered with a second interlayer insulating film (second insulating film) 256.

- the second interlayer insulating film 256 is preferably a white resin.

- the interlayer insulating film 256 as a white resin, the light emitting element 150a can reflect the light emitted in the lateral direction or the downward direction, and the brightness of the light emitting element 150a can be substantially improved.

- the second interlayer insulating film 256 may be a black resin.

- the interlayer insulating film 256 as a black resin, scattering of light in the subpixels is suppressed, and stray light is suppressed more effectively.

- An image display device in which stray light is suppressed can display a sharper image.

- the second interlayer insulating film 256 has an opening 158.

- the opening 158 is formed by removing a part of the interlayer insulating film 256 above the light emitting element 150a.

- the wiring 160a1 is connected to the p-type semiconductor layer 153a exposed by the opening 158.

- the p-type semiconductor layer 153a has a light emitting surface 153S exposed by the opening 158.

- the light emitting surface 153S is a surface of the p-type semiconductor layer 153a facing the surface in contact with the light emitting layer 152.

- the light emitting surface 153S is preferably roughened. When the light emitting surface 153S is a rough surface, the light emitting element 150a can improve the light extraction efficiency.

- transparent electrodes 159a and 159k are provided on the wirings 160a and 160k, respectively.

- the transparent electrode 159a is provided on the light emitting surface 153S of the opened p-type semiconductor layer 153a, and electrically connects the wiring 160a2 and the p-type semiconductor layer 153a.

- the connection area with the p-type semiconductor layer 153a can be increased, and the luminous efficiency can be improved.

- the connection area between the light emitting surface 153S and the transparent electrode 159a can be increased, and the contact resistance can be reduced.

- FIG. 2C shows a case where the circuit element such as the transistor 103 and the light emitting element 150 are arranged so as to be offset from each other on the XY plane.

- the light emitting element 150 and the transistor 130 may be arranged so as not to overlap each other in a plan view.

- a depletion layer region is generated between the p-type semiconductor region 104b and the n-type substrate 102, and this depletion layer region may function as a parasitic photodiode. It is preferable that the parasitic photodiode does not overlap with the light-irradiated region generated immediately below the light emitting element 150.

- the distance between the end portion when the light emitting layer 152 is projected onto the surface of the substrate 102 in XY plan view and the boundary of the p-type semiconductor region 104b is at least about 1 ⁇ m or more.

- the wiring 110s3 is not extended to the position where the light emitting element 150 is placed. That is, the wiring 110s3 does not necessarily include the outer peripheral portion of the light emitting element 150 when projected from above the Z axis in the XY plane view.

- the wiring 160k3 is extended longer in the X-axis direction than in the case of the above-described embodiment and other modifications.

- the light emitting element 150 when the light emitting element 150 is arranged sufficiently away from the circuit element, the scattered light in the negative direction of the Z axis is reduced, so that the circuit element such as the transistor 103 is less likely to malfunction due to the light. Become.

- the wiring in the circuit board 100 the wiring is not used for shading, so that the degree of freedom in circuit arrangement is improved and the integration density can be improved.

- any of the configurations of the subpixels 20 to 20c shown above can be included.

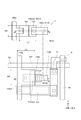

- FIG. 3 is a schematic block diagram illustrating an image display device according to the present embodiment.

- the image display device 1 of the present embodiment includes a display area 2.

- Subpixels 20 are arranged in the display area 2.

- the subpixels 20 are arranged in a grid pattern, for example. For example, n subpixels 20 are arranged along the X axis, and m subpixels 20 are arranged along the Y axis.

- Pixel 10 includes a plurality of subpixels 20 that emit light of different colors.

- the subpixel 20R emits red light.

- the subpixel 20G emits green light.

- the subpixel 20B emits blue light.

- the emission color and brightness of one pixel 10 are determined by the three types of sub-pixels 20R, 20G, and 20B emitting light with desired brightness.

- One pixel 10 includes three sub-pixels 20R, 20G, 20B, and the sub-pixels 20R, 20G, 20B are linearly arranged on the X-axis, for example, as in this example.

- subpixels of the same color may be arranged in the same column, or subpixels of different colors may be arranged for each column as in this example.

- the image display device 1 further includes a power supply line 3 and a ground line 4.

- the power line 3 and the ground line 4 are arranged in a grid pattern along the array of subpixels 20.

- the power supply line 3 and the ground line 4 are electrically connected to each subpixel 20, and power is supplied to each subpixel 20 from a DC power source connected between the power terminal 3a and the GND terminal 4a.

- the power supply terminal 3a and the GND terminal 4a are provided at the ends of the power supply line 3 and the ground line 4, respectively, and are connected to a DC power supply circuit provided outside the display area 2. A positive voltage is supplied to the power supply terminal 3a with reference to the GND terminal 4a.

- the image display device 1 further has a scanning line 6 and a signal line 8.

- the scanning line 6 is laid out in a direction parallel to the X axis. That is, the scanning lines 6 are laid out along the array in the row direction of the subpixels 20.

- the signal line 8 is laid out in a direction parallel to the Y axis. That is, the signal line 8 is laid out along the array of the subpixels 20 in the column direction.

- the image display device 1 further includes a row selection circuit 5 and a signal voltage output circuit 7.

- the row selection circuit 5 and the signal voltage output circuit 7 are provided along the outer edge of the display area 2.

- the row selection circuit 5 is provided along the Y-axis direction of the outer edge of the display area 2.

- the row selection circuit 5 is electrically connected to the subpixels 20 of each column via the scanning line 6 to supply a selection signal to each subpixel 20.

- the signal voltage output circuit 7 is provided along the outer edge of the display area 2.

- the signal voltage output circuit 7 is provided along the X-axis direction of the outer edge of the display area 2.

- the signal voltage output circuit 7 is electrically connected to the subpixel 20 of each line via the signal line 8 to supply a signal voltage to each subpixel 20.

- the subpixel 20 includes a light emitting element 22, a selection transistor 24, a drive transistor 26, and a capacitor 28.

- the selection transistor 24 may be displayed as T1

- the drive transistor 26 may be displayed as T2

- the capacitor 28 may be displayed as Cm.

- the light emitting element 22 is connected in series with the drive transistor 26.

- the drive transistor 26 is an n-channel MOSFET, and the cathode electrode, which is the n electrode of the light emitting element 22, is connected to the drain electrode, which is the main electrode of the drive transistor 26.

- the series circuit of the light emitting element 22 and the drive transistor 26 is connected between the power supply line 3 and the ground line 4.

- the drive transistor 26 corresponds to the transistor 103 in FIG. 1 and the like

- the light emitting element 22 corresponds to the light emitting element 150 in FIG. 1 and the like.

- the voltage applied between the gate and the source of the drive transistor 26 determines the current flowing through the light emitting element 22, and the light emitting element 22 emits light with a brightness corresponding to the current flowing through the light emitting element 22.

- the selection transistor 24 is connected between the gate electrode of the drive transistor 26 and the signal line 8 via a main electrode.

- the gate electrode of the selection transistor 24 is connected to the scanning line 6.

- a capacitor 28 is connected between the gate electrode of the drive transistor 26 and the ground wire 4.

- the row selection circuit 5 selects one row from the array of subpixels 20 in the m row and supplies the selection signal to the scanning line 6.

- the signal voltage output circuit 7 supplies a signal voltage having the required analog voltage value for each subpixel 20 in the selected row.

- a signal voltage is applied between the gate and source of the drive transistor 26 of the subpixel 20 in the selected row.

- the signal voltage is held by the capacitor 28.

- the drive transistor 26 causes a current corresponding to the signal voltage to flow through the light emitting element 22.

- the light emitting element 22 emits light with a brightness corresponding to the flowing current.

- the row selection circuit 5 sequentially switches the rows to be selected and supplies the selection signal. That is, the row selection circuit 5 scans the row in which the subpixels 20 are arranged. A current corresponding to the signal voltage flows through the light emitting element 22 of the subpixel 20 that is sequentially scanned to emit light. Each pixel 10 emits light with an emission color and brightness determined by the emission color and brightness of each of the RGB color subpixels 20, and an image is displayed in the display area 2.

- FIG. 4 is a schematic plan view illustrating a part of the image display device of the present embodiment.

- the light emitting element 22 (150) and the drive transistor 26 (103) are laminated in the Z-axis direction, and the cathode electrode of the light emitting element 22 (150) is formed by the via 161d. Is electrically connected to the drain electrode of the drive transistor 26 (103).

- the plan view of the I layer is schematically displayed in the upper part of FIG. 4, and the plan view of the II layer is schematically displayed in the lower part.

- the first layer is referred to as “I” and the second layer is referred to as “II”.

- the I-th layer is a layer on which the light emitting element 22 (150) is formed. That is, in FIG. 1, the first layer includes layers from the buffer layer 140 to the second wiring layer 160 in the positive direction of the Z axis. In FIG. 4, the buffer layer 140 and the second interlayer insulating film 156 are not shown.

- the second layer includes the layers from the substrate 102 to the first interlayer insulating film 112 in the positive direction of the Z axis in FIG. In FIG. 4, the substrate 102, the insulating layer 105, the insulating film 108, and the first interlayer insulating film 112 are not shown. In this figure, the channel region 104c is shown as the element forming region 104.

- FIG. 1 is an arrow cross section of the AA'line at the location indicated by the alternate long and short dash line in each of the I layer and the II layer.

- a wiring 160k is connected to the n-type semiconductor layer 151 which is a cathode electrode of the light emitting element 150 via a via 161k (FIG. 1) and a contact hole 161k1 thereof.

- the wiring 160k is connected to one end of the via 161d via a contact hole 161d1 provided in the second interlayer insulating film 156.

- the via 161d is schematically shown by a chain double-dashed line in the figure.

- the other end of the via 161d is connected to the wiring 110d via the contact hole 161d2 provided in the first interlayer insulating film 112.

- the wiring 110d is connected to the via 111d (FIG. 1) via the contact hole 111c1 opened in the insulating film 108, and is connected to the drain electrode of the transistor 103.

- the light emitting element 150 and the transistor 103 formed in the first layer and the second layer, which are different layers, can be electrically connected by the via 161d penetrating the interlayer insulating films 156 and 112.

- the wiring 110s has a light-shielding portion 110s1.

- the light-shielding portion (part) 110s1 is a rectangular portion having a length L2 in the X-axis direction and a length W2 in the Y-axis direction.

- the light-shielding portion 110s1 is provided directly below the light-emitting element 150.

- the light emitting element 150 has a rectangular bottom surface having a length L1 in the X-axis direction and a length W1 in the Y-axis direction.

- the length of each part is set so that L2> L1 and W2> W1. Since the light-shielding portion 110s1 is provided directly below the light-emitting element 150, the outer circumference of the light-shielding portion 110s1 includes the outer circumference of the light-emitting element 150. The outer circumference of the light-shielding portion 110s1 may include the outer circumference of the light emitting element 150, and the shape of the light-shielding portion 110s1 is not limited to a square shape and can be any suitable shape.

- the light emitting element 150 emits light upward, and also emits light downward, and includes reflected light, scattered light, and the like at the interface between the interlayer insulating film 112 and the surface resin layer 170. Therefore, preferably, the outer circumference of the light-shielding portion 110s1 is set to include the outer circumference of the light emitting element 150 projected on the light-shielding portion 110s1 in the XY plan view. By setting the light-shielding portion 110s1 in this way, it is possible to suppress the arrival of light below the light emitting element 150 and reduce the influence of light on the circuit element.

- the manufacturing method of the image display device 1 of this embodiment will be described.

- 5A to 6C are schematic cross-sectional views illustrating the method of manufacturing the image display device of the present embodiment.

- the semiconductor growth substrate 1194 is prepared.

- the semiconductor growth substrate 1194 has a semiconductor layer 1150 grown on the crystal growth substrate (first substrate) 1001.

- the crystal growth substrate 1001 is, for example, a Si substrate, a sapphire substrate, or the like.

- a Si substrate is used.

- the buffer layer 1140 is formed on one surface of the crystal growth substrate 1001.

- nitride such as AlN is preferably used as the buffer layer (buffer layer) 1140.

- the buffer layer 1140 is used to alleviate the mismatch at the interface between the GaN crystal and the crystal growth substrate 1001 when epitaxially growing GaN.

- the n-type semiconductor layer 1151, the light emitting layer 1152, and the p-type semiconductor layer 1153 are laminated on the buffer layer 1140 in this order from the buffer layer 1140 side.

- a vapor phase growth method (Chemical Vapor Deposition, CVD method) is used, and an organic metal vapor deposition method (Metal Organic Chemical Vapor Deposition, MOCVD method) is preferably used.

- the semiconductor layer 1150 is, for example, In X Al Y Ga 1-XY N (0 ⁇ X, 0 ⁇ Y, X + Y ⁇ 1) or the like.

- the support substrate 1190 is adhered to the open surface of the p-type semiconductor layer 1153 on the side facing the side on which the crystal growth substrate 1001 is provided.

- the support substrate 1190 is made of, for example, Si or quartz.

- the crystal growth substrate 1001 is removed. For example, a laser is used to remove the crystal growth substrate 1001.

- the circuit board 1100 is prepared.

- the circuit board (second board) 1100 has a circuit 101 described with reference to FIG. 1 and the like for the configuration of the subpixel 20.

- one surface of the circuit board 1100 and the surface of the buffer layer 1140 of the semiconductor layer 1150 are aligned, and both are bonded together.

- the bonded surface of the circuit board 1100 is an exposed surface of the interlayer insulating film 112 formed on the wiring layer 160.

- a low melting point metal or a low melting point alloy may be used for heat crimping.

- the low melting point metal is, for example, Sn, In, or the like, and the low melting point alloy can be, for example, an alloy containing Zn, In, Ga, Sn, Bi, or the like as a main component.

- the bonded surfaces of each substrate are flattened using chemical mechanical polishing (CMP), etc., and then the bonded surfaces are cleaned and adhered in vacuum by plasma treatment. You may let it.

- CMP chemical mechanical polishing

- the semiconductor layer 1150 may be attached to the support substrate 1190, the crystal growth substrate 1001 may be removed, and then the buffer layer 1140 may also be removed.

- the surface of the n-type semiconductor layer 1151 opened by removing the buffer layer 1140 is bonded to the circuit board 1100.

- a semiconductor growth substrate in which the semiconductor layer 1150 is crystal-grown may be used without providing the buffer layer 1140.

- the circuit board 1100 is bonded to the semiconductor layer 1150 via the buffer layer 1140 by wafer bonding.

- the semiconductor layer 1150 is formed in the shape of the light emitting element 150.

- a dry etching process is used, and preferably anisotropic plasma etching (Reactive Ion Etching, RIE) is used.

- an interlayer insulating film is formed so as to cover the light emitting element 150.

- Via holes are formed in the interlayer insulating film. After that, the via hole is filled with a conductive metal material. Either wet etching or dry etching can be used to form the via holes.

- a conductive layer is formed in the via hole by sputtering or the like, and a wiring layer 160 is formed by photolithography. After forming the via hole, the via and the wiring layer may be formed at the same time.

- a part of the circuit other than the subpixel 20 is formed in the circuit board 100.

- the row selection circuit 5 (FIG. 3) can be formed in the circuit board 100 together with the drive transistor, the selection transistor, and the like. That is, the row selection circuit 5 may be incorporated at the same time by the manufacturing process described above.

- the signal voltage output circuit 7 is mounted on another board together with the CPU and other circuit elements, and is mutually connected with the wiring of the circuit board 100, for example, before incorporating the color filter described later or after incorporating the color filter. Connected to.

- the circuit board 1100 is a wafer containing the circuit 101.

- the circuit board 1100 is formed with circuits 101 for one or more image display devices.

- the circuit 101 for forming one image display device is divided into a plurality of circuit boards 1100 and formed, and all of the divided circuits are combined to form 1 One image display device may be configured.

- the crystal growth substrate 1001 is a wafer having the same size as the wafer-shaped circuit board 1100.

- the semiconductor layers 1150 formed on the plurality of crystal growth substrates 1001 may be bonded to one circuit board 1100.

- FIGS. 7A and 7B are schematic cross-sectional views illustrating a manufacturing method of a modified example of the image display device of the present embodiment.

- 7A and 7B show the manufacturing process for forming the subpixel 20a of FIG. 2A.

- the same steps as in the case of the first embodiment are performed until the second interlayer insulating film 256 (156) is formed.

- FIGS. 7A and 7B are executed after the step of FIG. 6B or FIG. 6C.

- the second interlayer insulating film 256 is etched to form an opening 158 to expose the surface of the p-type semiconductor layer 153.

- the etching may be wet etching or dry etching.

- the light emitting surface 153S of the exposed p-type semiconductor layer 153 is roughened in order to improve the luminous efficiency.

- each wiring 160a1,160k is formed by photolithography.

- the wiring 160a1 is formed so as to be connected to the light emitting surface 153S of the exposed p-type semiconductor layer 153.

- the subpixel 20a of the modified example is formed.

- 8A and 8B are schematic cross-sectional views illustrating a manufacturing method of one modification of the image display device of the present embodiment.

- 8A and 8B show the manufacturing process for forming the subpixel 20b of FIG. 2B.

- the same steps as in the case of the above-mentioned modified example are obtained until the opening 158 is formed. Therefore, in the following description, it is assumed that the steps of FIGS. 8A and 8B are executed after FIG. 7A.

- each wiring 160a2, 160k is formed.

- the wiring 160a2 is not connected to the light emitting surface 153S of the p-type semiconductor layer 153.

- a transparent conductive film covering the wiring layer 160, the second interlayer insulating film 256 (156), and the light emitting surface 153S of the p-type semiconductor layer 153 is formed.

- the transparent conductive film an ITO film, a ZnO film, or the like is preferably used.

- the required transparent electrodes 159a, 159k are formed by photolithography.

- the transparent electrode 159a is formed on the wiring 160a2 and also on the light emitting surface 153S of the p-type semiconductor layer 153. Therefore, the wiring 160a2 and the p-type semiconductor layer 153 are electrically connected.

- the transparent electrode 159a is provided so as to cover the entire surface of the exposed light emitting surface 153S and is connected to the light emitting surface 153S.

- FIG. 9 is a schematic cross-sectional view illustrating the method for manufacturing the image display device of the present embodiment.

- the wiring and the like in the circuit board 100 and the interlayer insulating films 112 and 156 are not shown. Further, in FIG. 9, a part of the color conversion member such as the color filter 180 is displayed.

- a structure including a buffer layer 140, a light emitting element 150, vias 161k, 161d, a wiring layer 160, an interlayer insulating film 156, and a surface resin layer 170 is referred to as a light emitting circuit unit 172.

- a structure in which the light emitting circuit unit 172 is provided on the circuit board 100 is referred to as a structure 1192.

- the color filter 180 is adhered to the structure 1192 on one side.

- the other surface of the color filter 180 is adhered to the glass substrate 186.

- a transparent thin film adhesive layer 188 is provided on one surface of the color filter 180, and is adhered to the surface of the structure 1192 on the light emitting circuit portion 172 side via the transparent thin film adhesive layer 188.

- the color filter 180 has color conversion units arranged in the positive direction of the X-axis in the order of red, green, and blue.

- a red color conversion layer 183R and a green color conversion layer 183G are provided on the first layer, and a filter layer 184 is provided on the second layer, respectively.

- a single-layer color conversion layer 183B is provided for blue.

- a light-shielding unit 181 is provided between the color conversion units.

- the color filter 180 is attached to the structure 1192 by aligning the positions of the color conversion layers 183R, 183G, and 183B of each color with the positions of the light emitting element 150.

- 10A to 10D are schematic cross-sectional views showing a manufacturing method of a modified example of the image display device of the present embodiment.

- 10A-10D show a method of forming a color filter by an inkjet.

- a structure 1192 having a light emitting circuit unit 172 attached to the circuit board 100 is prepared.

- a light-shielding portion 181a is formed on the structure 1192.

- the light-shielding portion 181a is formed by using, for example, screen printing, photolithography technology, or the like.

- the phosphor 183a corresponding to the emission color is ejected from the inkjet nozzle.

- the phosphor 183a colors the region where the light-shielding portion 181a is not formed.

- a fluorescent paint using a general phosphor material or a quantum dot phosphor material is used as the phosphor 183a.

- a quantum dot phosphor material it is preferable because each emission color can be realized, monochromaticity is high, and color reproducibility can be high.

- the drying process is performed at an appropriate temperature and time. The thickness of the coating film at the time of coloring is set to be thinner than the thickness of the light-shielding portion 181a.

- the blue light emitting subpixel may not form a color conversion part, so that the phosphor is not ejected.

- the color conversion unit may be one layer, so that the thickness of the coating film of the blue phosphor is preferably set to that of the light shielding portion 181a. It is about the same as the thickness.

- the paint 184a for the filter layer is ejected from the inkjet nozzle.

- the paint 184a is applied over the coating film of the phosphor 183a.

- the total thickness of the coating film of the phosphor 183a and the coating film 184a is about the same as the thickness of the light-shielding portion 181a.

- the image display device 1 can be manufactured.

- the semiconductor layer 1150 including the light emitting layer 1152 for the light emitting element 150 is mounted on the circuit board 1100 (100) including the circuit elements such as the transistor 103 for driving the light emitting element 150. to paste together. Then, the semiconductor layer 1150 is etched to form the light emitting element 150. Therefore, the step of transferring the light emitting element can be remarkably shortened as compared with the case of individually transferring the light emitting element separated into the circuit board 1100 (100).

- the number of subpixels exceeds 24 million, and in the case of an 8K image quality image display device, the number of subpixels exceeds 99 million. It would take an enormous amount of time to mount such a large number of light emitting elements individually on a circuit board, and it is difficult to realize an image display device using micro LEDs at a realistic cost. Further, if a large number of light emitting elements are individually mounted, the yield is reduced due to poor connection at the time of mounting, and further cost increase is unavoidable.

- the entire semiconductor layer 1150 is attached to the circuit board 1100 (100) before the semiconductor layer 1150 is fragmented, so that the transfer step is performed once. Complete with.

- the light emitting element is directly formed on the circuit board by etching or the like, the light emitting element and the circuit element in the circuit board 1100 (100) are electrically connected by via formation, so that a uniform connection structure is realized. It is possible to suppress a decrease in yield.

- the semiconductor layer 1150 is attached to the circuit board 1100 (100) at the wafer level without being fragmented in advance or forming an electrode at a position corresponding to the circuit element, it is not necessary to perform alignment. Therefore, the pasting process can be easily performed in a short time. Since it is not necessary to align the light emitting element 150 at the time of pasting, the light emitting element 150 can be easily miniaturized, which is suitable for a high-definition display.

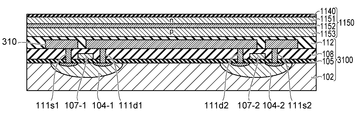

- FIG. 11 is a schematic cross-sectional view illustrating a part of the image display device according to the present embodiment.

- the configuration of the light emitting element 250 and the configuration of the transistor 203 for driving the light emitting element 250 are different from those of the other embodiments described above.

- the same components as in the case of the other embodiments described above are designated by the same reference numerals, and detailed description thereof will be omitted as appropriate.

- the subpixel 220 of the image display device of the present embodiment includes the transistor 203 and the light emitting element 250.

- the transistor 203 is formed in the element forming region 204 formed on the substrate 102.

- the element forming region 204 includes an n-type semiconductor region 204b and a p-type semiconductor region 204s and 204d.

- the n-type semiconductor region 204b is provided near the surface of the substrate 102.

- the p-type semiconductor regions 204s and 204d are provided in the n-type semiconductor region 204b in the vicinity of the surface of the n-type semiconductor region 204b so as to be separated from each other.

- a gate 107 is provided on the n-type semiconductor region 204b via the insulating layer 105.

- the gate 107 is provided between the p-type semiconductor regions 204s and 204d.

- the transistor 203 is a p-channel MOSFET.

- the light emitting element 250 includes a p-type semiconductor layer (first semiconductor layer) 253, a light emitting layer 252, and an n-type semiconductor layer (second semiconductor layer) 251.

- the p-type semiconductor layer 253, the light emitting layer 252, and the n-type semiconductor layer 251 are laminated in this order from the first interlayer insulating film 112 of the circuit board 100 toward the light emitting surface 251S.

- the light emitting element 250 has, for example, a substantially square or rectangular shape in XY plan view, but the corners may be rounded.

- the light emitting element 250 may have, for example, an elliptical shape or a circular shape in an XY plan view.

- the degree of freedom in layout is improved by appropriately selecting the shape and arrangement of the light emitting elements in a plan view.

- the p-type semiconductor layer 253 has a stepped portion 253a extending in the X-axis direction on the first interlayer insulating film 112.

- the light emitting element 250 may be made of the same material as in the other embodiments described above.

- the light emitting element 250 emits, for example, blue light having a wavelength of about 467 nm ⁇ 20 nm or blue-purple light having a wavelength of 410 nm ⁇ 20 nm.

- the light emitting element 250 is provided on the interlayer insulating film (first insulating film) 112 without interposing the buffer layer.

- the second interlayer insulating film (second insulating film) 256 covers the first interlayer insulating film 112 and the light emitting element 250.

- the second interlayer insulating film 256 has an opening 258.

- the opening 258 is formed on the light emitting element 250, and the interlayer insulating film 256 is not provided on the light emitting surface 251S of the light emitting element 250.

- a white resin is preferably used so that the light emitting element 250 reflects the light emitted and is effectively output from the opening 258.

- the light emitting surface 251S is a surface of the n-type semiconductor layer 251 facing the surface in contact with the light emitting layer 252.

- the light emitting surface 251S is roughened.

- a via (second via) 261a is provided so as to penetrate the interlayer insulating film 256.

- One end of the via 261a is connected to the step portion 253a.

- the via (first via) 161d is provided so as to penetrate the interlayer insulating films 112 and 256. One end of the via 161d is connected to the wiring 110d.

- the wiring layer 260 is provided on the interlayer insulating film 256.

- the wiring layer 260 includes wirings 260k and 260a.

- the wiring 260a is connected to the other ends of the vias 261a and 161d. Therefore, the p-type semiconductor layer 253 of the light emitting element 250 is electrically connected to the main electrode of the transistor 203 via the vias 261a and 161d.

- Wiring 260k is not shown, but is connected to the ground wire.

- a transparent electrode 259k is provided on the wiring 260k.

- the transparent electrode 259k extends to the light emitting surface 251S and is provided over the entire surface of the light emitting surface 251S. Therefore, the n-type semiconductor layer 251 is connected to the ground wire via the transparent electrode 259k and the wiring 260k.

- a transparent electrode 259a is also arranged on the wiring 260a.

- a surface resin layer 170 is provided on the interlayer insulating film 256 and the transparent electrodes 259k and 259a.

- FIG. 12 is a schematic block diagram illustrating an image display device according to the present embodiment.

- the image display device 201 of the present embodiment includes a display area 2, a row selection circuit 205, and a signal voltage output circuit 207.

- the sub-pixels 220 are arranged in a grid pattern as in the case of the other embodiments described above.

- the light emitting element 222 is provided on the ground wire 4, and the drive transistor 226 connected in series with the light emitting element 222 is provided on the power supply line 3. That is, the drive transistor 226 is connected to the higher potential side than the light emitting element 222.

- the drive transistor 226 is a p-channel MOSFET.

- a selection transistor 224 is connected between the gate electrode of the drive transistor 226 and the signal line 208.

- the capacitor 228 is connected between the gate electrode of the drive transistor 226 and the power supply line 3.

- the row selection circuit 205 and the signal voltage output circuit 207 perform selection signals and signal voltages having different polarities from those of the other embodiments described above in order to drive the drive transistor 226, which is a p-channel MOSFET, in scanning lines 206 and signal lines 208. Supply to.

- the row selection circuit 205 supplies a selection signal to the scanning line 206 so as to sequentially select one row from the array of m rows of subpixels 220.

- the signal voltage output circuit 207 supplies a signal voltage having the required analog voltage value to each subpixel 220 in the selected row.

- the drive transistor 226 of the subpixel 220 in the selected row causes a current corresponding to the signal voltage to flow through the light emitting element 222.

- the light emitting element 222 emits light with a brightness corresponding to the flowing current.

- FIG. 13A to 14B are schematic cross-sectional views illustrating the method of manufacturing the image display device of the present embodiment.

- the semiconductor growth substrate 1194 already described in FIG. 5A is used.

- the subsequent steps of preparing the semiconductor growth substrate 1194 having the semiconductor layer 1150 epitaxially grown via the buffer layer 1140 on the crystal growth substrate 1001 will be described.

- the semiconductor growth substrate 1194 is turned upside down and attached to the circuit board 1100 without removing the crystal growth substrate 1001 from the semiconductor growth substrate 1194. That is, the exposed surface of the p-type semiconductor layer 1153 on the opposite side of the crystal growth substrate 1001 is attached to the flattened surface of the interlayer insulating film 112 of the circuit board 1100 by wafer bonding as shown by the arrows in the figure. wear. Wafer bonding can be performed in the same manner as in the other embodiments described above.

- the crystal growth substrate 1001 is removed by laser irradiation or the like.

- the semiconductor layer 1150 is etched together with the buffer layer 1140 to form the light emitting element 250. Since the buffer layer 240 remains on the light emitting element 250, the buffer layer 240 is removed by further etching. The buffer layer 240 may be removed before forming the light emitting element 250.

- the first interlayer insulating film 112 and the second interlayer insulating film 256 covering the light emitting element 250 are formed. After that, a via hole is formed so as to penetrate the second interlayer insulating film 256. The via hole is filled with a conductive metal material.