RU2461966C2 - Система, способ и устройство для передачи данных - Google Patents

Система, способ и устройство для передачи данных Download PDFInfo

- Publication number

- RU2461966C2 RU2461966C2 RU2010128565/07A RU2010128565A RU2461966C2 RU 2461966 C2 RU2461966 C2 RU 2461966C2 RU 2010128565/07 A RU2010128565/07 A RU 2010128565/07A RU 2010128565 A RU2010128565 A RU 2010128565A RU 2461966 C2 RU2461966 C2 RU 2461966C2

- Authority

- RU

- Russia

- Prior art keywords

- data

- mode

- transition

- processor

- state

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 36

- 238000012545 processing Methods 0.000 claims abstract description 128

- 230000005540 biological transmission Effects 0.000 claims abstract description 58

- 230000008569 process Effects 0.000 claims abstract description 21

- 230000007704 transition Effects 0.000 claims description 76

- 230000004044 response Effects 0.000 claims description 42

- 238000001514 detection method Methods 0.000 claims description 23

- 230000008859 change Effects 0.000 claims description 15

- 238000005516 engineering process Methods 0.000 abstract description 9

- 239000000126 substance Substances 0.000 abstract 1

- 238000004891 communication Methods 0.000 description 89

- 238000012546 transfer Methods 0.000 description 20

- 230000004913 activation Effects 0.000 description 15

- 101000772194 Homo sapiens Transthyretin Proteins 0.000 description 14

- 102100029290 Transthyretin Human genes 0.000 description 14

- 238000010586 diagram Methods 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 5

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 2

- 230000006870 function Effects 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/18—Multiprotocol handlers, e.g. single devices capable of handling multiple protocols

Landscapes

- Engineering & Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Communication Control (AREA)

Abstract

Изобретение относится к системе бесконтактной беспроводной связи в ближней зоне для передачи и приема данных с использованием электромагнитных волн между устройством чтения/записи картой с интегральной схемой. Изобретение раскрывает способ, систему и устройство для передачи данных, включающие в себя передатчик и первый процессор для передачи данных, по меньшей мере, в двух рабочих режимах, приемник, запоминающее устройство и второй процессор с двумя рабочими режимами для обработки данных. В режиме готовности принимаемые данные готовы для обработки после приема. В активном режиме принимаемые данные преобразуют в другой формат перед обработкой. Передатчик осуществляет передачу первых данных, относящихся к режиму готовности, первой команды перехода, относящейся к переходу из режима готовности в активный режим, вторых данных, относящихся к активному режиму, и второй команды перехода, относящейся к переходу из активного режима в режим готовности. Второй процессор обрабатывает первые данные в режиме готовности, переходит в активный режим, обрабатывает вторые данные в активном режиме и переходит в режим готовности. 5 н. и 19 з.п. ф-лы, 13 ил.

Description

Уровень техники

Настоящее описание относится к системе, способу и устройству для передачи данных (для связи) и, в частности, например, при осуществлении бесконтактной беспроводной связи в ближней зоне, к приемному устройству, способу приема, программе, передающему устройству и способу передачи, позволяющим передавать и принимать данные, сконфигурированные в соответствии со структурой или форматом данных, отличных от заданных структуры или формата данных, с использованием схемы связи для передачи и приема данных, сконфигурированных в соответствии с заданной структурой или форматом данных.

Известна технология бесконтактной беспроводной связи в ближней зоне для передачи и приема данных с использованием электромагнитных волн между устройством чтения/записи и микропроцессорной картой (картой с интегральной схемой) и т.п.

В технологии бесконтактной беспроводной связи в ближней зоне применяются несколько стандартов, отличающихся один от другого системой команд, схемой связи, структурой или форматом данных и т.п. Поэтому, например, если устройство чтения/записи и микропроцессорная карта соответствуют разным стандартам, передача и прием данных между такими устройством чтения/записи и микропроцессорной картой могут оказаться невозможными.

Соответственно разработана технология «сквозных команд», согласно которой между микропроцессорной картой и устройством чтения/записи помещают «сквозной считыватель», включающий команды от микропроцессорных карт, передающих команды, соответствующие различным стандартам, в сквозные команды, которые может распознать устройство чтения/записи, и передающий эти сквозные команды устройству чтения/записи (см., например, JP-A-2004-264921).

Согласно технологии сквозных команд устройство чтения/записи может принимать команды от микропроцессорных карт, работающих в различных стандартах, через сквозной считыватель в виде сквозных команд.

Далее, разработана технология передачи и приема данных, согласно которой в случае, когда, например, структуры данных в первом сообщении, подлежащем передаче и приему между устройством чтения/записи и микропроцессорной картой, отличны от структур данных во втором сообщении, подлежащем обработке в устройстве чтения/записи и микропроцессорной карте, второе сообщение включают в первое сообщение и затем выполняют передачу и прием (см., например, JP-A-2005-242445).

Согласно этой технологии передачи и приема второе сообщение, включенное в состав первого сообщения, может быть обработано в устройстве чтения/записи и в микропроцессорной карте, тогда как передача и прием первого сообщения осуществляется между устройством чтения/записи и микропроцессорной картой.

Согласно японскому промышленному стандарту JIS X 6319-4, являющемуся стандартом бесконтактной беспроводной связи в ближней зоне, для бесконтактной беспроводной связи в ближней зоне предписывается использовать схему связи для передачи и приема кадров в виде данных, сконфигурированных в соответствии со структурой данных (форматом), определенной в стандарте JIS X 6319-4 (далее именуется «схема передачи кадров»).

Однако схема передачи кадров при передаче и приеме данных посредством бесконтактной беспроводной связи в ближней зоне согласно стандарту JIS X 6319-4 не предусматривает передачу блоков данных, сконфигурированных в соответствии со структурой данных, определенной в стандарте ISO/IEC 14443-4 (международная организация по стандартизации/международная электротехническая комиссия (ИСО/МЭК)), команд согласно ISO/IEC 7816-4, откликов на эти команды и тому подобного.

Соответственно было невозможно передавать и принимать блоки данных со структурой данных согласно ISO/IEC 14443-4, команд согласно ISO/IEC 7816-4, откликов на эти команды и т.п.с использованием только указанной схемы передачи кадров. Примерно тоже относится и к описанному выше случаю применения технологии сквозных команд и технологии передачи и приема.

Таким образом, желательно получить возможность передавать и принимать данные, сконфигурированные в соответствии со структурой или форматом данных, отличных от заданных структуры или формата данных, с использованием схемы связи для передачи и приема данных, сконфигурированных в соответствии с заданными структурой или форматом данных.

Раскрытие изобретения

В варианте осуществления система передачи данных включает в себя первое устройство, включающее в себя передатчик для передачи данных и функционально связанный с передатчиком первый процессор, причем первый процессор выполнен с возможностью подготовки данных к передаче, по меньшей мере, в двух рабочих режимах, включая режим готовности и активный режим, и второе устройство, включающее в себя приемник для приема данных, запоминающее устройство и функционально связанный с приемником и запоминающим устройством второй процессор, причем второй процессор выполнен с возможностью обеспечивать указанные, по меньшей мере, два рабочих режима, включая режим готовности и активный режим, для обработки принятых данных после приема данных, при этом в режиме готовности принятые данные готовы к обработке сразу по приеме данных, а в активном режиме принятые данные преобразуются в другой формат перед обработкой после приема данных, причем первый процессор выполнен с возможностью предоставлять передатчику, а передатчик выполнен с возможностью передавать (i) первые данные, связанные с режимом готовности, которые готовы к обработке по приеме, (ii) первую команду перехода, связанную с переходом из режима готовности в активный режим, (iii) вторые данные, связанные с активным режимом, которые преобразуются в другой формат при приеме, и (iv) вторую команду перехода, связанную с переходом из активного режима в режим готовности, при этом приемник выполнен с возможностью приема и передачи второму процессору первых данных, первой команды перехода, вторых данных и второй команды перехода, а второй процессор выполнен с возможностью обеспечивать сохранение данных, представляющих, по меньшей мере, одну из указанных команд перехода, в запоминающем устройстве, и при этом второй процессор выполнен с возможностью (i) обработки первых данных в режиме готовности, (ii) перехода в активный режим по первой команде перехода, (iii) обработки вторых данных в активном режиме и (iv) перехода в режим готовности по второй команде перехода.

В варианте осуществления в режиме готовности данные обрабатываются с использованием протокола JIS X 6319-4.

В варианте осуществления при приеме данных в режиме готовности принятые данные форматируются в соответствии с протоколом JIS X 6319-4.

В варианте осуществления режим готовности включает в себя подрежим запрошенной готовности и подрежим объявленной готовности, причем в подрежиме запрошенной готовности для перехода в подрежим объявленной готовности предоставляется ответ, включающий в себя идентификатор, а в подрежиме объявленной готовности выполняется обработка данных, когда поступает команда обработки, включающая в себя указанный идентификатор.

В варианте осуществления в подрежиме объявленной готовности команда обработки, включающая идентификатор, вызывает переход из подрежима объявленной готовности в JIS-активный режим, в котором выполняется обработка.

В варианте осуществления подрежим объявленной готовности вызывает выполнение команд и формирование ответов с использованием протокола JIS X 6319-4.

В варианте осуществления в активном режиме обработка данных осуществляется с использованием, по меньшей мере, одного из протокола ISO/IEC 7816-4 и протокола ISO/IEC 14443-4.

В варианте осуществления в активном режиме при приеме данных принятые данные форматируются с использованием протокола, отличного от указанного, по меньшей мере, одного из протоколов ISO/IEC 7816-4 и ISO/IEC 14443-4.

В варианте осуществления, по меньшей мере, одна команда перехода вызывает переход в режим остановки, запрещающий прямой переход из режима остановки в режим готовности и из режима остановки в активный режим.

В варианте осуществления указанная, по меньшей мере, одна команда перехода включает третью команду перехода и четвертую команду перехода, так что третья команда перехода вызывает переход из режима готовности в режим остановки, а четвертая команда перехода вызывает переход из активного режима в режим остановки.

В варианте осуществления третья команда перехода вызывает переход из режима остановки в холостой режим, допускающий прямой переход из холостого режима в режим готовности в ответ на четвертую команду перехода.

В варианте осуществления первое устройство представляет собой устройство чтения/записи, а второе устройство представляет собой микропроцессорную карту ("IC card").

В варианте осуществления устройство для передачи данных содержит передатчик для передачи данных и, по меньшей мере, один функционально соединенный с этим передатчиком процессор, причем указанный, по меньшей мере, один процессор осуществляет подготовку данных к передаче, по меньшей мере, в двух режимах работы, включающих в себя режим готовности и активный режим, при этом в режиме готовности данные, подготовленные к передаче, готовы для обработки сразу же по приеме этих данных, а в активном режиме данные, подготовленные к передаче, преобразуют в другой формат перед обработкой после приема этих данных, причем указанный, по меньшей мере, один процессор предоставляет передатчику (i) первые данные, относящиеся к режиму готовности, так что эти данные готовы к обработке сразу же по приеме, (ii) первую команду перехода, относящиеся к переходу из режима готовности в активный режим, (iii) вторые данные, относящиеся к активному режиму и преобразуемые в другой формат при приеме, и (iv) вторую команду перехода, относящиеся к переходу из активного режима в режим готовности.

В варианте осуществления это устройство представляет собой микропроцессорную карту.

В варианте осуществления устройство представляет собой устройство чтения/записи.

В варианте осуществления устройство для передачи данных включает в себя приемник данных, запоминающее устройство и, по меньшей мере, один процессор, функционально связанный с приемником и с запоминающим устройством, при этом указанный процессор имеет, по меньшей мере, два рабочих режима, включающих в себя режим готовности и активный режим, причем в режиме готовности принятые данные готовы к обработке, по меньшей мере, одним процессором, а в активном режиме принятые данные преобразуют в другой формат перед обработкой, по меньшей мере, одним процессором, при этом, по меньшей мере, один процессор принимает, по меньшей мере, одну команду перехода от приемника, вызывает сохранение данных, характеризующих эту, по меньшей мере, одну команду перехода, в запоминающем устройстве, переходит из режима готовности в активный режим на основе первой команды перехода и переходит из активного режима в режим готовности на основе второй команды перехода.

В варианте осуществления это устройство представляет собой микропроцессорную карту.

В варианте осуществления это устройство представляет собой устройство чтения/записи.

В варианте осуществления способ передачи данных включает в себя прием кадра данных, включающего в себя первый код обнаружения ошибок, определение, содержит ли принятый кадр данных неповрежденные данные, с использованием первого кода обнаружения ошибок, определение текущего состояния, причем текущее состояние является первым состоянием и/или вторым состоянием, при этом первое состояние указывает, что данные в кадре данных готовы к обработке сразу по приеме, а второе состояние означает, что данные в кадре данных подлежат преобразованию в другой формат перед обработкой, определение в ответ на определение, что принятый кадр данных содержит неповрежденные данные, содержит ли принимаемый кадр данных команду изменения состояния для перехода, по меньшей мере, к одному из первого состояния и второго состояния, переход ко второму состояния на основе команды изменения состоянию, удаление, по меньшей мере, одного фрагмента данных из принятого кадра данных, если текущее состояние является вторым состоянием, вычисление второго кода обнаружения ошибок на основе данных, оставшихся в кадре данных, замену первого кода обнаружения ошибок вторым кодом обнаружения ошибок, формирование блока данных из оставшихся данных и второго кода обнаружения ошибок и обработку данных в этом блоке данных.

В варианте осуществления принятый кадр данных представляет собой кадр данных JIS-протокола, а блок данных представляет собой блок данных ISO/IEC-протокола.

В варианте осуществления указанный, по меньшей мере, один фрагмент данных включает, по меньшей мере, одно из данных преамбулы, данных кода синхронизации и данных длины.

В варианте осуществления способ передачи данных включает обработку данных для формирования данных передачи, вычисление первого кода обнаружения ошибок на основе данных передачи, формирование блока данных на основе результата обработки и первого кода обнаружения ошибок, проверку с целью подтверждения, что данные передачи в блоке данных являются неповрежденными, добавление, по меньшей мере, одного фрагмента данных к блоку данных для формирования кадра данных, вычисление второго кода обнаружения ошибок, на основе добавленного, по меньшей мере, одного фрагмента данных и данных передачи, замену первого кода обнаружения ошибок вторым кодом обнаружения ошибок и передачу кадра данных, причем при приеме переданного кадра данных данные в кадре данных перед обработкой преобразуют в другой формат.

В варианте осуществления указанный блок данных представляет собой блок данных ISO/IEC-протокола, а кадр данных представляет собой кадр данных JIS-протокола.

В варианте осуществления передаваемые данные помещают в информационное поле блока данных ISO/IEC-протокола.

Согласно рассмотренным здесь примерам вариантов осуществления настоящего изобретения данные, сконфигурированные в виде структуры или формата данных, отличных от заданной структуры или формата данных, можно передавать и принимать с использованием схемы связи для передачи и приема данных, сконфигурированных в соответствии с заданными структурой или форматом данных.

Здесь описаны также дополнительные признаки и преимущества, которые будут ясны из следующего подробного описания и прилагаемых чертежей.

Краткое описание чертежей

Фиг.1 представляет блок-схему, показывающую пример конфигурации системы передачи данных.

Фиг.2 представляет блок-схему, показывающую пример конфигурации устройства чтения/записи.

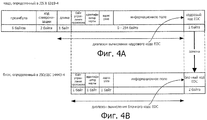

Фиг.3А и 3В представляют схемы для пояснения процесса преобразования блока данных в кадр.

Фиг.4А и 4В представляют схемы для пояснения процесса преобразования кадра данных в блок.

Фиг.5 представляет блок-схему, показывающую пример конфигурации микропроцессорной карты.

Фиг.6 показывает изменения состояния микропроцессорной карты.

Фиг.7 представляет блок-схему последовательности операций для пояснения обработки данных при приеме.

Фиг.8 представляет блок-схему последовательности для пояснения обработки команд.

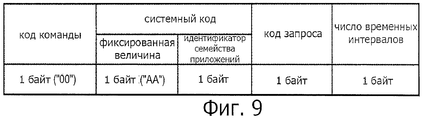

Фиг.9 показывает пример формата команды REQ запроса.

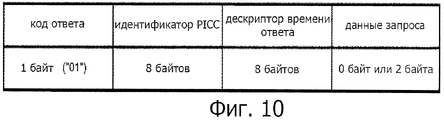

Фиг.10 показывает пример формата ответа на команду REQ запроса.

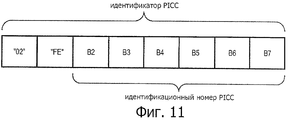

Фиг.11 показывает пример идентификатора PICC.

Фиг.12 показывает пример дескриптора времени ответа.

Фиг.13 представляет блок-схему, показывающую пример конфигурации компьютера.

Подробное описание изобретения

На фиг.1 показан пример конфигурации системы 1 связи в качестве примера осуществления изобретения.

Система 1 связи содержит устройство 21 чтения/записи и микропроцессорную карту 22. Между устройством 21 чтения/записи и микропроцессорной картой 22 передают и принимают (обмениваются) блоки данных, конфигурированные в соответствии со структурой данных, определенной в ISO/IEC 14443-4, посредством, например, бесконтактной беспроводной связи в ближней зоне с использованием схемы передачи кадров для передачи и приема кадров данных, сконфигурированных в соответствии со структурой данных, определяемой протоколом JIS X 6319-4.

Устройство 21 чтения/записи принимает кадр данных от микропроцессорной карты 22 с использованием схемы передачи кадров и преобразует принятый кадр в блок. Затем устройство 21 чтения/записи выполняет соответствующую обработку блока в качестве объекта обработки.

Далее, устройство 21 чтения/записи генерирует блок и преобразует блок в кадр. После этого устройство 21 чтения/записи передает преобразованный кадр с использованием схемы передачи кадров.

Микропроцессорная карта 22 принимает кадр, переданный с применением схемы передачи кадров от, например, устройства 21 чтения/записи или аналогичного устройства. Затем, если в принятый кадр включена команда изменения состояния микропроцессорной карты 22, микропроцессорная карта 22 переходит в одно из состояний - «холостое» (IDLE) состояние, состояние «готовности» (READY), «активное» (ACTIVE) состояние или состояние «остановки» (HALT) в ответ на команду изменения состояния. Подробнее команда изменения состояния и сам процесс изменения состояния микропроцессорной картой 22 будут рассмотрены далее со ссылками на фиг.6.

Когда микропроцессорная карта 22 находится в состоянии READY готовности, она служит микропроцессорной картой, выполняющей соответствующую обработку кадра в качестве объекта обработки, а в активном ACTIVE состоянии карта служит микропроцессорной картой, выполняющей соответствующую обработку блока в качестве объекта обработки.

Таким образом, например, когда микропроцессорная карта осуществляет бесконтактную беспроводную связь в ближней зоне с использованием схемы передачи кадров с устройством чтения/записи, выполняющим соответствующую обработку кадра в качестве объекта, устройство чтения/записи переводит микропроцессорную карту 22 в состояние READY готовности. Затем передачу и прием кадров между микропроцессорной картой 22 и устройством чтения/записи осуществляют с использованием схемы передачи кадров.

Далее, например, когда микропроцессорная карта осуществляет бесконтактную беспроводную связь в ближней зоне с использованием схемы передачи кадров с устройством чтения/записи, выполняющим соответствующую обработку блока в качестве объекта, устройство 21 чтения/записи переводит микропроцессорную карту 22 в активное состояние ACTIVE. Тогда между микропроцессорной картой 22 и устройством 21 чтения/записи осуществляют передачу и прием блоков, преобразованных в кадры, с использованием схемы передачи кадров.

Ниже будет рассмотрена бесконтактная беспроводная связь в ближней зоне для передачи и приема блоков, преобразованных в кадры, с использованием схемы передачи кадров между устройством чтения/записи 21 и микропроцессорной картой 22.

Далее, на фиг.2 представлен пример конфигурации устройства чтения/записи 21.

Устройство 21 чтения/записи включает ISO-процессор 41, преобразователь 42 и ВЧ приемопередатчик 43 (RF (высокочастотный)).

ISO-процессор 41 выполняет соответствующую обработку блока со структурой данных, определенной в стандарте ISO/IEC 14443-4, в качестве обрабатываемого объекта.

Иными словами, например, ISO-процессор 41 выполняет обработку, соответствующую команде, присутствующей в блоке, поступившем от преобразователя 42. Затем ISO-процессор 41 генерирует блок, содержащий результаты обработки, и передает его преобразователю 42.

Преобразователь 42 превращает блок от ISO-процессора 41 в кадр и передает его RF приемопередатчику 43. Далее, преобразователь 42 преобразует кадр от RF приемопередатчика 43 в блок, готовый для обработки, и передает блок в ISO-процессор 41. Подробнее процессы обработки, выполняемые преобразователем 42, будут рассмотрены далее со ссылками на фиг.3А и 3В и фиг.4А и 4В.

RF приемопередатчик 43 принимает кадр от микропроцессорной карты 22, например, с использованием схемы передачи кадров и передает его преобразователю 42. Далее, этот RF приемопередатчик 43 передает кадр, полученный от преобразователя, с использованием схемы передачи кадров.

Далее, подробности примерной обработки данных в преобразователе 42 будут объяснены со ссылками на фиг.3А и 3В и фиг.4А и 4 В.

Фиг.3А и 3В показывают, что преобразователь 42 превращает блок от ISO-процессора 41 в кадр.

Блок данных, показанный на фиг.3А, включает 1 байт РСВ (байт управления протокола), 1 байт CID (идентификатор карты), 1 байт NAD (адрес узла), от 1 до 251 байтов INF (информационное поле) и 2 байта EDC (код обнаружения ошибок).

Кадр, показанный на фиг.3В, включает 6 байтов преамбулы, 2 байта кода синхронизации, 1 байт LEN (длина), представляющий длину данных в поле INF, 1 байт управления РСВ, 1 байт идентификатора CID, 1 байт адреса NAD, от 1 до 251 байтов поля INF и 2 байта кода EDC.

Код EDC в блоке, показанном на фиг.3А, вычисляют на основе данных, образующих РСВ, CID, NAD и поле INF в этом блоке. Код EDC в блоке, показанном на фиг.3А, служит для определения (обнаружения), появилась ли или не появилась ошибка в данных, образующих РСВ, CID, NAD и поле INF в этом блоке, путем вычисления, например, CRC (циклически избыточный контрольный (ЦИК) код) или аналогичным способом.

Кроме того, код EDC в кадре, показанном на фиг.3В, вычисляют на основе данных, образующих LEN, РСВ, CID, NAD и поле INF в этом кадре. Код EDC в кадре, показанном на фиг.3В, служит для определения, повреждены или нет данные, или появилась ли или не появилась ошибка в данных, образующих LEN, РСВ, CID, NAD и поле INF, в этом кадре, с использованием, например, кода CRC или аналогичным способом.

Здесь, в дальнейшем объяснении код EDC в блоке, показанном на фиг.3А, именуется «блочный код EDC», в код EDC в кадре, показанном на фиг.3В, именуется «кадровый код EDC».

Преобразователь 42 определяет, появилась ли ошибка в данных, включающих РСВ, CID, NAD и поле FNF, или нет, на основе показанного на фиг.3А блочного кода EDC, поступающего от ISO процессора 41.

Затем, если преобразователь 42 определяет на основе блочного кода EDC, что в данных, включающих РСВ, CID, NAD и поле INF, ошибок нет, этот преобразователь добавляет преамбулу, код синхронизации и длину LEN к головной части блока, поступившего от ISO процессора 41. Кроме того, преобразователь 42 вычисляет кадровый код EDC, соответствующий данным, включающим LEN, РСВ, CID, NAD и поле INF, и заменяет им блочный код EDC.

Таким образом, преобразователь 42 превращает блок, показанный на фиг.3А, в кадр, показанный на фиг.3В, и передает его ВЧ приемопередатчику 43.

Далее, на фиг.4А и 4В показано, как преобразователь 42 превращает кадр, полученный им от приемопередатчика 43, в блок.

Кадр, показанный на фиг.4А, представляет такой же кадр, как показано на фиг.3В. Блок, показанный на фиг.4В, представляет такой же блок, как показано на фиг.3А.

Преобразователь 42 определяет, появилась ли ошибка в данных, образующих LEN, РСВ, CID, NAD и поле INF, или нет, на основе показанного на фиг.4А кадрового кода EDC, поступающего от RF приемопередатчика 43.

Затем, если преобразователь 42 определит на основе кадрового кода EDC, что в данных, включающих LEN, РСВ, CID, NAD и поле FNF, ошибок нет, этот преобразователь стирает преамбулу, код синхронизации и длину LEN, добавленные к заголовку или к головной части блока, поступившего от RF приемопередатчика 43. Кроме того, преобразователь 42 вычисляет блочный код EDC, соответствующий данным, включающим оставшиеся РСВ, CID, NAD и поле INF, и заменяет им кадровый код EDC.

Таким образом, преобразователь 42 превращает кадр, показанный на фиг.4А, в блок, показанный на фиг.4В, и передает его ISO процессору 41.

Далее, на фиг.5 показан пример конфигурации микропроцессорной карты 22.

Микропроцессорная карта 22 включает RF приемопередатчик 61, JIS процессор 62 связи, запоминающее устройство 63 состояния, JIS процессор 64, преобразователь 65 и ISO процессор 66.

RF приемопередатчик 61 принимает готовый к обработке кадр от устройства 21 чтения/записи, например, с использованием схемы передачи кадров и передает этот кадр JIS процессору 62 связи. Кроме того, RF приемопередатчик 61 передает кадр от JIS процессора 62 связи с использованием схемы передачи кадров.

Когда в кадре от RF приемопередатчика 61 содержится команда изменения состояния (например, REQ, WUP, ATTR, HLT или подобная, что будет описано позже) для изменения состояния микропроцессорной карты 22, JIS процессор 62 связи обновляет информацию состояния, сохраняемую в запоминающем устройстве 63 состояния, в соответствии с этой командой изменения состояния.

JIS процессор 62 связи выполняет обработку данных в соответствии с командами, определенными в протоколе JIS X 6319-4, однако команды WUP, ATTR и HLT, которые будут описаны ниже, не были изначально определены в этом протоколе JIS X 6319-4.

Поэтому в JIS процессоре 62 связи, выполняющем обработку данных в соответствии с командами, определенными в протоколе JIS X 6319-4, обычно может оказаться невозможным осуществить обработку в соответствии с командами WUP, ATTR и HLT.

Однако согласно настоящему описанию протокол JIS X 6319-4 расширен настолько, чтобы можно было выполнять обработку в соответствии с командами WUP, ATTR и HLT даже в JIS процессоре 62 связи, осуществляющем обработку данных в соответствии с командами, определенными в протоколе JIS X 6319-4.

Далее, согласно настоящему описанию для поддержания обратной совместимости с протоколом JIS X 6319-4:2005, протокол JIS X 6319-4 расширяет команду REQ. Такое расширение команды REQ посредством протокола JIS X 6319-4 будет описано позднее со ссылками на фиг.9-12.

Кроме того, в качестве команды изменения состояния (перехода) применяется команда отмены выбора DESELECT для перевода микропроцессорной карты 22 из активного состояния ACTIVE в состояние HALT остановки помимо команд REQ, WUP, ATTR и HLT, причем эта команда DESELECT определена в стандарте ISO/IEC 14443-4. Поэтому команду DESELECT обрабатывает не JIS процессор 62 связи, a ISO процессор 66, который будет описан ниже.

Когда информация состояния, записанная в запоминающем устройстве 63 состояния, указывает состояние READY готовности, JIS процессор 62 определяет, является ли команда обработки данных, содержащаяся в кадре от RF приемопередатчика, (команда, разрешающая микропроцессорной карте 22 выполнить заданную обработку) командой, согласующейся с идентификатором PICC (Proximity Integrated Circuit Card - бесконтактная микропроцессорная карта), содержащей идентификатор PICC для однозначной идентификации микропроцессорной карты 22.

Затем, если JIS процессор 62 связи определит, что команда обработки данных, содержащаяся в кадре от RF приемопередатчика, является командой, согласующейся с идентификатором PICC, процессор связи передаст кадр от RP приемопередатчика 61 JIS процессору 64.

Далее, если информация состояния, записанная в запоминающем устройстве 63 состояния, указывает активное состояние ACTIVE, JIS процессор связи 62 передает кадр от RF приемопередатчика 61 преобразователю 65.

Кроме того, JIS процессор 62 связи передает кадр от JIS процессора 64 или преобразователя 65 RP приемопередатчику 61.

Запоминающее устройство 63 состояния сохраняет информацию состояния, указывающую состояние микропроцессорной карты 22. Запоминающее устройство 63 состояния записывает информацию состояния, указывающую состояние выключенного питания (POWER OFF) заранее.

JIS процессор 64 выполняет обработку, соответствующую командам обработки, определенным в протоколе JIS X 6319-4, над кадром в качестве объекта обработки. Иными словами, JIS процессор 64, например, выполняет обработку, соответствующую командам, определенным в протоколе JIS X 6319-4 и содержащимся в кадре от JIS процессора связи 62. Кроме того, JIS процессор 64 генерирует кадр, содержащий результат обработки, полученный в результате обработки, и передает этот кадр JIS процессору связи 62.

Преобразователь 65 преобразует кадр от JIS процессора 62 связи в блок подобно преобразователю 42 на фиг.2 и передает этот блок в ISO процессор 66. Кроме того, преобразователь 65 преобразует блок от ISO процессора в кадр и передает этот кадр JIS процессору 62 связи.

ISO процессор 66 выполняет обработку в соответствии с командами обработки, определенными в протоколе ISO/IEC 14443-4, над блоком в качестве обрабатываемого объекта. Иными словами, например, ISO процессор 66 выполняет обработку в соответствии с командами обработки, определенными в протоколе ISO/IEC 14443-4 и содержащимися в блоке от преобразователя 65. Далее, ISO процессор 66 генерирует блок, содержащий результаты обработки, и передает этот блок преобразователю 65.

Кроме того, ISO процессор 66 обновляет информацию состояния, указывающую активное состояние ACTIVE, в запоминающем устройстве 63 состояния информацией состояния, указывающей состояние HALT остановки, на основе команды DESELECT отмены выбора в качестве команды изменения состояния, определенной в протоколе ISO/IEC 14443-4 и содержащейся в блоке от преобразователя 65.

Далее, изменение состояния микропроцессорной карты 22 будет объяснено со ссылками на фиг.6, иллюстрирующую примеры рабочих режимов и переходы между режимами или состояниями.

Когда микропроцессорная карта 22 не находится в RE поле (магнитном поле), генерируемом, например, устройством 21 чтения/записи или подобным устройством, микропроцессорная карта 22 переходит в состояние POWER OFF выключенного питания.

Далее, если микропроцессорную карту 22, находящуюся в состоянии POWER OFF выключенного питания, поместить над устройством 21 чтения/записи в области RF поля, генерируемого этим устройством 21 чтения/записи, микропроцессорная карта 22 переходит из состояния POWER OFF выключенного питания в холостое состояние IDLE.

В холостом состоянии IDLE, когда микропроцессорная карта 22 выходит из области RF поля, генерируемого устройством 21 чтения/записи или подобным устройством, микропроцессорная карта 22 переходит из холостого состояния IDLE в состояние POWER OFF выключенного питания. Не только в холостом состоянии IDLE, но и в любом другом - состоянии READY готовности, активном состоянии ACTIVE, состоянии HALT остановки или активном состоянии JIS-ACTIVE, которое будет описано ниже, когда микропроцессорная карта 22 выходит из области RF поля, генерируемого устройством 21 чтения/записи или подобным ему устройством, эта микропроцессорная карта 22 переходит из текущего состояния в состояние POWER OFF выключенного питания.

Далее, при приеме в холостом состоянии IDLE команды REQ (команда запроса) или WUP (команда активизации) микропроцессорная карта 22 переходит из холостого состояния IDLE в состояние READY-REQUESTED запрошенной готовности состояния READY готовности.

В состоянии READY-REQUESTED запрошенной готовности состояния READY готовности, когда микропроцессорная карта 22 передает ответ на принятую команду REQ запроса или WUP активизации (содержащую идентификатор PICC для этой микропроцессорной карты 22), микропроцессорная карта 22 переходит из состояния READY-REQUESTED запрошенной готовности в состояние READY-DECLARED объявленной готовности или из подрежима READY-REQUESTED в подрежим READY-DECLARED.

Когда микропроцессорная карта 22 передает ответ на команду, например, REQ запроса или WUP активизации, устройство 21 чтения/записи принимает идентификатор PICC микропроцессорной карты 22, содержащийся в ответе на команду REQ запроса или WUP активизации. Таким образом, устройство 21 чтения/записи становится способным передать команды обработки или другую подобную информацию для этой микропроцессорной карты 22 с использованием полученного идентификатора PICC.

В состоянии READY-DECLARED объявленной готовности состояния READY готовности, когда команда обработки, содержащаяся в кадре, принятом микропроцессорной картой 22, является командой, согласующейся с идентификатором PICC, микропроцессорная карта переходит из состояния READY-DECLARED объявленной готовности в активное состояние US-ACTIVE. Затем, будучи в активном состоянии JIS-ACTIVE, при обработке в соответствии с командой обработки и передаче ответа на команду обработки микропроцессорная карта 22 переходит (возвращается) из активного состояния JIS-ACTIVE в состояние READY-DECLARED объявленной готовности.

Кроме того, если в состоянии READY-DECLARED объявленной готовности команда обработки, содержащаяся в кадре, принятом микропроцессорной картой 22, не является командой, согласующейся с идентификатором PICC, микропроцессорная карта 22 остается в состоянии READY-DECLARED объявленной готовности.

Если в состоянии READY-DECLARED объявленной готовности микропроцессорная карта 22 принимает команду REQ запроса или WUP активизации от устройства 21 чтения/записи, микропроцессорная карта переходит из состояния READY-DECLARED объявленной готовности в состояние READY-REQUESTED запрошенной готовности. Затем, в состоянии READY-REQUESTED запрошенной готовности выполняется такая же обработка, как и в случае приема команды REQ запроса или WUP активизации в холостом состоянии IDLE, а карта 22 переходит из холостого состояния IDLE в состояние READY-REQUESTED запрошенной готовности.

В состоянии готовности READY или в режиме готовности READY (в состоянии READY-REQUESTED запрошенной готовности или состоянии READY-DECLARED объявленной готовности) при приеме команды HLT (команда остановки) передают ответ на команду HLT, после чего микропроцессорная карта 22 переходит из состояния или режима READY готовности в состояние или режим HALT остановки.

Далее, в состоянии READY готовности при приеме команды ATTR (команда атрибута) передают ответ на команду ATTR, после чего микропроцессорная карта 22 переходит из состояния или режима READY готовности в активное состояние или режим ACTIVE.

Если в активном состоянии ACTIVE команда, содержащаяся в кадре, принятом микропроцессорной картой 22, является командой обработки, содержащей идентификатор PICC микропроцессорной карты 22, микропроцессорная карта 22 осуществляет обработку в соответствии с этой командой обработки. В этом случае микропроцессорная карта 22 остается в активном состоянии ACTIVE.

В активном состоянии или режиме ACTIVE при приеме команды DESELECT отмены выбора передают ответ на команду DESELECT, после чего микропроцессорная карта 22 переходит из активного состояния ACTIVE в состояние HALT остановки.

В состоянии или режиме HALT остановки при приеме команды WUP активизации передают ответ на команду WUP, после чего микропроцессорная карта 22 переходит из состояния HALT остановки в холостое состояние или режим IDLE.

Далее будет дано объяснение процессов обработки при приеме кадра микропроцессорной картой 22 от устройства 21 чтения/записи или подобного устройства.

На фиг.7 и 8 представлены блок-схемы последовательности операций для пояснения примера обработки данных при приеме. Обработка при приеме начинается в момент передачи кадра, например, устройством 21 чтения/записи или аналогичным устройством.

Объяснение обработки данных при приеме будет дано в предположении, что микропроцессорная карта 22 находится в рассматриваемое время в активном состоянии ACTIVE, состоянии READY готовности, состоянии HALT остановки или холостом состоянии IDLE.

На этапе S1 RF приемопередатчик 61 принимает кадр (содержащий кадровый код EDC) от устройства 21 чтения/записи и передает этот кадр в JIS процессор 62 связи. JIS процессор 62 связи определяет, появилась ли ошибка в кадре или нет, на основе кадрового кода, полученного от RF приемопередатчика 61.

На этапе S2, если JIS процессор 62 связи определяет, что в кадре появилась ошибка, на основе кадрового кода EDC, полученного от RF приемопередатчика 61, процессор отбрасывает (игнорирует) рассматриваемый кадр от RF приемопередатчика 61 и заканчивает обработку.

Далее, на этапе S2, если JIS процессор 62 связи определяет, что в принятом кадре нет ошибок, на основе кадрового кода EDC от RF приемопередатчика 61, процессор 62 переходит к этапу S3.

На этапе S3 JIS процессор 62 связи считывает информацию состояния, записанную в запоминающем устройстве 63 состояния. Затем JIS процессор 62 связи на основе считанной информации состояния определяет, что микропроцессорная карта 22 находится в активном состоянии ACTIVE, состоянии READY готовности, состоянии HALT остановки или холостом состоянии IDLE, и переходит к этапу S4.

На этапе S4 JIS процессор 62 связи определяет, является ли команда, содержащаяся в кадре от RF приемопередатчика 61, командой изменения состояния.

На этапе S4, если JIS процессор 62 связи определяет, что команда, содержащаяся в кадре от RF приемопередатчика 61, не является командой изменения состояния, он переходит к этапу S5.

На этапе S5, если микропроцессорная карта 22 находится в активном состоянии ACTIVE, выполняется обработка ISO процессором 66, а если микропроцессорная карта 22 находится в состоянии READY готовности, выполняется обработка команды для выполнения обработки JIS процессором 64. Подробнее обработка команд будет описана ниже со ссылкой на фиг.8.

На этапе S4, если процессор 62 связи определяет, что команда, содержащаяся в кадре от RF приемопередатчика 61, является командой изменения состояния, процессор переходит к выполнению одного из этапов S6-S9 в зависимости от состояния микропроцессорной карты 22, определенного на этапе S3.

А именно, если на этапе S3 определено, что микропроцессорная карта 22 находится в активном состоянии ACTIVE, JIS процессор 62 связи переходит к выполнению этапа S6, если в состоянии READY готовности, переходит к выполнению этапа S7, если в состоянии HALT остановки, переходит к выполнению этапа S8, и если в холостом состоянии IDLE, переходит к выполнению этапа S9.

На этапе S6 микропроцессорная карта 22 находится в активном состоянии ACTIVE. Соответственно JIS процессор 62 связи передает кадр от RF приемопередатчика 61 преобразователю 65. Преобразователь 65 преобразует кадр от JIS процессора 62 связи в блок и передает этот блок ISO процессору 66.

Если команда в блоке от преобразователя 65 является командой DESELECT отмены выбора, ISO процессор 66 передает ответ на эту команду DESELECT через преобразователь 65, JIS процессор 62 связи и RF приемопередатчик 61. Тогда ISO процессор 66 генерирует информацию состояния, указывающую состояние HALT остановки, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от активного состояния ACTIVE к состоянию HALT остановки.

На этапе S7, если команда, содержащаяся в кадре от RF приемопередатчика 61, представляет собой команду ATTR атрибута, JIS процессор 62 связи передает ответ на эту команду ATTR через RF приемопередатчик 61. Тогда JIS процессор 62 связи генерирует информацию состояния, указывающую активное состояние ACTIVE, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от состояния READY готовности к активному состоянию ACTIVE.

Далее, если команда, содержащаяся в кадре от RF приемопередатчика 61, представляет собой команду HLT остановки, JIS процессор 62 связи передает ответ на эту команду HLT через RF приемопередатчик 61. Тогда JIS процессор 62 связи генерирует информацию состояния, указывающую состояние HALT остановки, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от состояния READY готовности к состоянию HALT остановки.

В состоянии READY-DECLARED объявленной готовности состояния READY готовности, если команда, содержащаяся в кадре от RF приемопередатчика 61, представляет собой команду REQ запроса или WUP активизации, JIS процессор 62 связи передает ответ на команду REQ или WUP через RF приемопередатчик 61. Тогда JIS процессор 62 связи генерирует информацию состояния, указывающую состояние READY-REQUESTED запрошенной готовности состояния READY готовности, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от состояния READY-DECLARED объявленной готовности к состоянию READY-REQUESTED запрошенной готовности состояния READY готовности.

На этапе S8, если команда, содержащаяся в кадре от RF приемопередатчика 61, представляет собой команду WUP активизации, указанный JIS процессор 62 связи передает ответ на команду WUP через RF приемопередатчик 61. Тогда JIS процессор 62 связи генерирует информацию состояния, указывающую холостое состояние IDLE, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от состояния HALT остановки к холостому состоянию IDLE.

На этапе S9, если команда, содержащаяся в кадре от RF приемопередатчика 61, представляет собой команду REQ запроса или WUP активизации, JIS процессор 62 связи передает ответ на команду REQ или WUP через RF приемопередатчик 61. Тогда JIS процессор 62 связи генерирует информацию состояния, указывающую состояние READY-REQUESTED запрошенной готовности состояния READY готовности, и передает ее в запоминающее устройство 63 состояния для перезаписи. Тем самым состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от холостого состояния IDLE к состоянию READY-REQUESTED запрошенной готовности состояния READY готовности. Это является окончанием обработки данных при приеме.

Далее будет подробно рассмотрена обработка команд на этапе S5 на фиг.7. Фиг.8 представляет блок-схему последовательности операций, поясняющих обработку команд.

На этапе S31 JIS процессор 62 связи переводит обработку на этап, соответствующий состоянию микропроцессорной карты 22, найденному на этапе S3 на фиг.7.

На этапе S31, если на этапе S3 на фиг.7 было определено, что микропроцессорная карта 22 находится в активном состоянии ACTIVE, JIS процессор 62 связи передает кадр от RF приемопередатчика 61 преобразователю 65 и переходит к выполнению этапа S32.

На этапе S32 преобразователь 65 преобразует кадр от JIS процессора 62 связи в блок и передает этот блок ISO процессору 66.

А именно, например, что преобразователь 65 удаляет преамбулу, код синхронизации и длину LEN в кадре, полученном от JIS процессора 62 связи, и вычисляет блочный код EDC, соответствующий данным, включающим остальные данные РСВ, CID, NAD и поле INF.

Затем преобразователь 65 заменяет кадровый код EDC, полученный от JIS процессора 62 связи, вычисленным блочным кодом EDC, генерирует блок и передает блок ISO процессору 66.

На этапе S33 ISO процессор 66 определяет, не появилась ли ошибка в блоке от преобразователя 65, на основе блочного кода EDC, содержащегося в блоке от преобразователя 65. Если на основе результатов такого определения ISO процессор 66 подтвердит, что в блоке от преобразователя 65 ошибок нет, процессор переходит к выполнению этапа S34.

Заметим, что если на этапе S33 оказалось невозможным подтвердить отсутствие ошибок в блоке от преобразователя 65, снова генерируют блок на этапе S32 до тех пор, пока не будет подтверждено отсутствие ошибок в блоке от преобразователя 65.

На этапе S34 ISO процессор 66 выполняет соответствующую обработку данных на основе определенных в протоколе ISO/IEC 14443-4 команд, содержащихся в блоке от преобразователя 65. Более того, принятые данные, содержащиеся в блоке от преобразователя 65, обрабатывают после их преобразования в другой формат (например, из кадра данных протокола JIS в блок данных протокола ISO).

На этапе S35 указанный ISO процессор 66 генерирует блок, содержащий результат обработки, полученный на этапе S34. А именно, например, ISO процессор 66 добавляет соответствующие параметры РСВ, CID и NAD к полю INF, содержащему результаты обработки, полученные на этапе S34.

Затем ISO процессор 66 вычисляет соответствующий блочный код EDC на основе INF, РСВ, CID и NAD, добавляет вычисленный блочный код EDC к полю INF, к которому уже были добавлены параметры РСВ, CID и NAD, и передает полученный в результате блок преобразователю 65.

На этапе S36 преобразователь 65 определяет, не появилась ли ошибка в блоке, на основе блочного кода EDC от ISO процессора 66. Если по результатам такого определения преобразователь 65 подтверждает отсутствие ошибок в блоке от ISO процессора 66, преобразователь переходит к этапу S37.

Заметим, что если на этапе S36 оказалось невозможным подтвердить отсутствие ошибок в блоке от ISO процессора 66, снова генерируют блок на этапе S35 до тех пор, пока не будет подтверждено отсутствие ошибок в блоке от ISO процессора 66.

На этапе S37 преобразователь 65 превращает блок от ISO процессора 66 в кадр и передает его JIS процессору 62 связи.

А именно, например, преобразователь 65 добавляет преамбулу, код синхронизации и длину LEN к блоку, поступившему от ISO процессора 66, и вычисляет кадровый код EDC, соответствующий данным, включающим в себя РСВ, CID, NAD, LNF и добавленную длину LEN.

Затем преобразователь 65 заменяет вычисленным кадровым кодом EDC блочный код EDC, поступивший от ISO процессора 66, и передает полученный в результате кадр JIS процессору 62 связи.

На этапе S38 JIS процессор 62 связи передает кадр, полученный им от преобразователя 65, RF приемопередатчику 61. После этого RF приемопередатчик 61 передает кадр, полученный от JIS процессора 62 связи, с использованием схемы передачи кадров и возвращается к этапу S5 на фиг.7.

Далее, на этапе S31, если на этапе S3 на фиг.7 оказалось, что микропроцессорная карта 22 находится в состоянии READY готовности, JIS процессор 62 связи передает кадр от RF приемопередатчика 61 указанному JIS процессору 64 и переходит к этапу S39.

На этапе S39 указанный JIS процессор 64 определяет, является ли соответствующая протоколу JIS X 6319-4 команда, присутствующая в кадре, полученном от JIS процессора 62 связи, командой, согласующейся с идентификатором PICC, или нет.

На этапе S39, если JIS процессор 64 определяет, что соответствующая протоколу JIS X 6319-4 команда, присутствующая в кадре, полученном от JIS процессора 62 связи, не является командой, согласующейся с идентификатором PICC, процессор 64 возвращается к этапу S5 на фиг.7.

Далее, на этапе S39, если JIS процессор 64 определяет, что соответствующая протоколу JIS X 6319-4 команда, присутствующая в кадре, полученном от JIS процессора 62 связи, является командой, согласующейся с идентификатором PICC, процессор 64 переходит к этапу S40.

На этапе S40 JIS процессор 64 генерирует информацию состояния, указывающую активное состояние JIS-ACTIVE, и передает эту информацию в запоминающее устройство 63 состояний для перезаписи. Таким образом, состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояний, переходит от состояния READY (READY-DECLARED) готовности к активному состоянию JIS-ACTIVE.

На этапе S41 JIS процессор 64 выполняет соответствующую обработку данных на основе соответствующей протоколу JIS X 6319-4 команды, содержащейся в кадре, полученном от JIS процессора 62 связи. Более того, принятые данные в этом кадре данных готовы к обработке сразу по приеме без преобразования в другой формат данных.

На этапе S42 JIS процессор 64 генерирует кадр, содержащий результат обработки на этапе S41. А именно, например, что JIS процессор 64 добавляет соответствующие преамбулу, код синхронизации и параметры LEN, РСВ, CID и NAD к полю INF, содержащему результаты обработки, полученные на этапе S41.

Затем JIS процессор 64 вычисляет соответствующий кадровый код EDC на основе INF, LEN, РСВ, CID и NAD, добавляет вычисленный кадровый код EDC к полю LNF, к которому были добавлены преамбула, код синхронизации и параметры LEN, РСВ, CID и NAD, и передает полученный в результате кадр JIS процессору 62 связи.

На этапе S43 JIS процессор 62 связи подает кадр, полученный от JIS процессора 64, RF приемопередатчику 61. Затем RF приемопередатчик 61 передает кадр, полученный от JIS процессора 64, с использованием схемы передачи кадров.

На этапе S44 JIS процессор 64 генерирует информацию состояния, указывающую состояние READY готовности (состояние READY-DECLARED объявленной готовности), и подает эту информацию запоминающему устройству 63 состояний для перезаписи. Таким образом, состояние микропроцессорной карты 22, обозначенное информацией состояния, записанной в запоминающем устройстве 63 состояния, переходит от активного состояния JIS-ACTIVE к состоянию READY готовности. После завершения обработки на этапе S44 JIS процессор 64 возвращается к этапу S5 на фиг.7.

На этапе S31, если на этапе S3 на фиг.7 было определено, что микропроцессорная карта 22 находится в состоянии HALT остановки или в холостом состоянии IDLE, указанный JIS процессор 62 связи возвращается к этапу S5 на фиг.7.

Как объяснено выше в примере обработки данных при приеме, состояние микропроцессорной карты 22 изменяется в ответ на команду изменения состояния. Кроме того, при выполнении команд в ходе обработки принимаемых данных микропроцессорная карта 22 ведет себя как микропроцессорная карта с кадром в качестве объекта обработки в состоянии READY готовности и ведет себя как микропроцессорная карта с блоком в качестве объекта обработки в активном состоянии ACTIVE.

Поэтому, например, микропроцессорная карта 22 может выполнять соответствующую обработку к кадру и к блоку, имеющим различные структуры или форматы данных.

Далее, например, когда микропроцессорная карта 22 находится в активном состоянии ACTIVE, преобразователь 65 преобразует кадр, поступивший от устройства 21 чтения/записи, в блок, который может быть обработан в ISO процессоре 66, и преобразует блок от ISO процессора 66 в кадр, который может быть передан с использованием схемы передачи кадров.

Таким образом, можно передавать и принимать (обмениваться) блоки между устройством 21 чтения/записи и микропроцессорной картой 22 с использованием схемы передачи кадров, предназначенной для передачи и приема кадров.

Далее, в приведенном примере обработки команд принятый кадр преобразуют в блок на этапе S32 и выполняют проверку для получения подтверждения, что в блоке после преобразования не появились ошибки, на этапе S33.

Поэтому на этапе S34 можно обрабатывать после преобразования блок, в котором отсутствуют ошибки.

Кроме того, в приведенном примере обработки команд генерируют блок на этапе S35, а на этапе S36 выполняют проверку для получения подтверждения, что в блоке после генерации нет ошибок.

Поэтому на этапе S37 блок, в котором отсутствуют ошибки, можно преобразовать в кадр.

В варианте осуществления стандарт JIS X 6319-4 может быть расширен таким образом, чтобы устройства чтения/записи обоих типов - и устройства чтения/записи, передающие команды, определенные в стандарте JIS X 6319-4, и устройства 21 чтения/записи, передающие команды, определенные в стандарте ISO/IEC 14443-4, смогли осуществлять бесконтактную беспроводную связь в ближней зоне с использованием схемы передачи кадров в микропроцессорной карте 22.

А именно, например, в данном варианте осуществления стандарт JIS X 6319-4 расширен, чтобы включить описанные выше команды ATTR атрибута, WUP активизации и HLT остановки в качестве команд, определенных в стандарте JIS X 6319-4, и что JIS процессор 62 связи выполняет обработку, соответствующую командам, определенным в расширенном стандарте JIS X 6319-4. В результате JIS процессор 62 связи может обновлять состояние микропроцессорной карты 22 в соответствии с описанными выше командами ATTR атрибута, WUP активизации и HLT остановки.

В дополнение к этому в рассматриваемом примере команды REQ запроса и т.п., определенные в стандарте JIS X 6319-4, расширены для сохранения обратной совместимости со стандартом JIS X 6319-4:2005.

Далее, на фиг.9 показан пример формата команды REQ запроса, расширенной в стандарте JIS X 6319-4.

Команда REQ запроса на фиг.9 включает в себя по 1 байту кода команды, системного кода, кода запроса и кода временных интервалов.

Например, код команды установлен "00". Величина, заключенная в кавычки "", представляет шестнадцатеричное число.

Пример системного кода включает фиксированную величину и AFI (идентификатор семейства приложений). Фиксированную величину устанавливают равной "АА". В системном коде идентификатор AFI устанавливают равным "FF", если поле не определено.

Идентификатор AFI представляет собой величину, соответствующую определению в стандарте ISO/IEC 14443-3 (JIS X 6322-3). В идентификаторе AFI не используют "00" и величины, четыре младших бита которых равны нулю.

Далее, для сохранения обратной совместимости со стандартом JIS X 6319-4:2005 применяют также "FFFF" в качестве величины системного кода, не определяющей поле, в дополнение к системному коду "AAFF".

Код запроса, равный "00", указывает, что команда REQ запроса совместима с командой REQ запроса, определенной в стандарте JIS X 6319-4:2005. Далее, код запроса, равный "01", означает, что к ответу на команду REQ запроса добавлено информационное поле системного кода.

Кроме того, код запроса, равный "02", означает, что к ответу на команду REQ запроса добавлены возможности протокола передачи.

Коды запроса с "03" по "FF" являются RFU (зарезервированы для использования в будущем).

Код временных интервалов указывает максимальное число временных интервалов, которые должна использовать микропроцессорная карта 22. В качестве кода временных интервалов можно использовать любой из следующих кодов: "00" - обозначает один временной интервал, "01" - обозначает два временных интервала, "03" - обозначает четыре временных интервала, "07" - обозначает восемь временных интервалов, или "0F" обозначает 16 временных интервалов.

Далее, фиг.10 представляет пример ответа на команду REQ запроса.

Пример ответа на команду REQ запроса, показанный на фиг.10, включает 1 байт кода ответа, 8 байтов идентификатора PICC, 8 байтов дескриптора времени ответа и 0 байтов или 2 байта данных запроса.

Код запроса установлен равным "01". Идентификатор PICC представляет собой идентификатор (ID) микропроцессорной карты 22.

Дескриптор времени ответа содержит 8 байтов информации, используемой для вычисления времени ответа микропроцессорной карты 22, так что старшие (самые первые) 2 байта устанавливают равными "FF", а самый младший 1 байт тоже устанавливают равным "FF".

Когда код запроса, содержащийся в команде REQ запроса, равен, например, "01", данные запроса представляют собой информационное поле системного кода.

Далее, когда код запроса, содержащийся в команде REQ запроса, равен, например, "02", данные запроса представляют собой возможности протокола передачи.

Далее, на фиг.11 представлен пример идентификатора PICC, содержащегося в ответе на команду REQ запроса.

Пример идентификатора PICC представляет собой числовую величину из 8 байтов, так что первые два байта равны "02FE", а остальные 6 байтов представляют собой идентификационный номер PICC для идентификации микропроцессорной карты по ее идентификатору PICC.

В идентификаторе PICC может оказаться возможным, что в системе связи, отличной от системы связи 1, к которой применим рассматриваемый вариант настоящего изобретения, будут использованы величины, в которых первые 2 байта не равны "02FE", вследствие чего величины, отличные от "02FE", первым 2 байтам не назначают.

Далее, на фиг.12 представлен пример дескриптора времени ответа, содержащегося в ответе на команду REQ запроса.

Пример дескриптора времени ответа представляет собой величину из 8 байтов, используемую для вычисления времени ответа микропроцессорной карты 22 на принятую команду.

В дескрипторе времени ответа первые 2 байта устанавливают равными "FFFF". Кроме того, самый младший байт В7 зарезервирован для использования в будущем и должен быть установлен равным "FF".

В одном из примеров микропроцессорная карта 22 может работать в качестве микропроцессорной карты, обрабатывающей кадры, или в качестве микропроцессорной карты, обрабатывающей блоки, в зависимости от состояния этой микропроцессорной карты 22. Однако вместо микропроцессорной карты 22 можно адаптировать устройство 21 чтения/записи для работы либо в качестве устройства чтения/записи, обрабатывающего кадры, либо в качестве устройства чтения/записи, обрабатывающего блоки, в зависимости от состояния этого устройства 21 чтения/записи.

В этом случае устройство 21 чтения/записи может осуществлять бесконтактную беспроводную связь в ближней зоне с микропроцессорной картой, обрабатывающей кадры, либо с микропроцессорной картой, обрабатывающей блоки, с использованием схемы передачи кадров.

Далее, в данном варианте осуществления, поскольку блоки передают и принимают с использованием схемы передачи кадров, команды, определенные, например, в стандарте ISO/IEC 7816-4 или аналогичном стандарте, могут быть включены в эти блоки и переданы с использованием схемы передачи кадров.

Кроме того, в данном варианте осуществления были рассмотрены устройство 21 чтения/записи и микропроцессорная карта 22, передающие и принимающие блоки данных с использованием схемы передачи кадров, однако различные варианты настоящего изобретения могут быть применены к любому устройству связи, передающему и принимающему блоки данных с использованием схемы передачи кадров.

Далее, в варианте осуществления стандарт JIS X 6319-4 расширен таким образом, чтобы обработку, соответствующую командам WUP активизации, ATTR атрибута и HLT остановки, можно было осуществлять в JIS процессоре 62 связи, выполняющем обработку в соответствии с командами, определенными в стандарте JIS X 6319-4, однако, не ограничиваясь этим.

А именно, например, стандарт JIS X 6319-4 может быть расширен таким образом, чтобы в JIS процессоре 62 связи можно было осуществлять обработку в соответствии не только с командами WUP активизации, ATTR атрибута и HLT остановки, но и с командой DESELECT отмены выбора.

В этом случае JIS процессор 62 связи может обновлять поле информации состояния в запоминающем устройстве 63 состояния в соответствии не только с командами WUP активизации, ATTR атрибута и HLT остановки, но и с командой DESELECT отмены выбора. Соответственно, если команда изменения состояния представляет собой команду DESELECT отмены выбора, информацию состояния можно обновлять быстрее по сравнению с вариантом, в котором команду DESELECT отмены выбора передают от JIS процессора 62 связи ISO процессору 66 через преобразователь 65.

Далее, в данном варианте осуществления в кадр преобразуют блок данных, соответствующим предписаниям стандарта ISO/IEC 14443-4, однако типы блоков, преобразуемых в кадры, этим не ограничиваются. А именно, например, можно использовать блоки с произвольной структурой данных, если только эти блоки могут быть преобразованы в кадры с применением способа преобразования, рассмотренного на фиг.ЗА-4 В. В этом случае структуру данных такого блока расширяют (изменяют) в соответствии с предписаниями стандарта ISO/IEC 14443-4.

Кроме того, в данном варианте осуществления между устройством 21 чтения/записи и микропроцессорной картой 22 передают кадры данных, соответствующие предписаниям стандарта JIS X 6319-4, однако возможные типы передаваемых кадров этим не ограничиваются. А именно, например, можно использовать кадры с любой структурой данных, если только эти кадры можно передавать между устройством 21 чтения/записи и микропроцессорной картой 22. В этом случае структуру данных кадра расширяют в соответствии с предписаниями стандарта JIS X 6319-4.

Далее, описанный выше ряд примеров обработки может быть реализован посредством специализированных аппаратурных средств или выполнен с применением соответствующего программного обеспечения. Когда последовательность обработки исполняется посредством программного обеспечения, программы, составляющие пакет программного обеспечения, инсталлируют с носителя записи в так называемом встроенном компьютере или, например, в компьютере общего назначения, который может исполнять различные функции при инсталляции в нем различных программ.

На фиг.13 представлен пример конфигурации компьютера, выполняющего описанную выше последовательность обработки данных.

CPU (центральный процессор) 201 выполняет различные виды обработки в соответствии с программами, записанными в ПЗУ (постоянном запоминающем устройстве (ROM)) 202 или в запоминающем устройстве 208. В ОЗУ (оперативное запоминающее устройство (RAM)) 203 также соответствующим образом записывают программы и данные, выполняемые и обрабатываемые посредством CPU 201. Эти CPU 201, ROM 202 и RAM 203 могут быть соединены одни с другими посредством шины 204.

Далее, с процессором CPU 201 через шину 204 соединен интерфейс 205 ввода/вывода. С этим интерфейсом 205 ввода/вывода соединены устройство 206 ввода, включающее клавиатуру, мышь, микрофон и т.п., и устройство 207 вывода, включающее дисплей, громкоговоритель и т.п. Процессор CPU 201 осуществляет различные виды обработки в ответ на команды, вводимые от устройства 206 ввода. Результаты обработки процессор CPU 201 передает устройству 207 вывода.

Запоминающее устройство 208, соединенное с интерфейсом 205 ввода/вывода, включает, например, накопитель на жестком диске и сохраняет программы, выполняемые центральным процессором CPU 201, и разного рода данные. Устройство 209 связи может поддерживать связь с внешними устройствами через сеть, например через Интернет или локальную сеть связи.

Кроме того, система может получать программы через устройство 209 связи и сохранять их в запоминающем устройстве 208.

Когда в системе установлен съемный носитель 211 записи, такой как магнитный диск, оптический диск, магнитооптический диск или полупроводниковое запоминающее устройство, привод 210, соединенный с интерфейсом 205 ввода/вывода, обращается к этому носителю и считывает записанные на нем программы и данные. Считываемые программы и данные передают в запоминающее устройство 208 и сохраняют в нем до момента, когда они потребуются.

Носитель записи программ, которые могут быть инсталлированы в компьютере и выполнены компьютером, включает съемные носители 211, такие как магнитные диски (включая дискеты), оптические диски (включая CD-ROM (ПЗУ на основе компакт-дисков) и DVD (цифровые универсальные диски)), магнитооптические диски (включая MD (минидиски)), ROM 202, где временно или постоянно записывают программы, накопитель на жестком диске, образующий запоминающее устройство 208, и т.п. Запись программ на носителе записи может быть произведена с использованием проводных или беспроводных систем связи, таких как локальная сеть связи, Интернет или система цифрового спутникового вещания, через устройство 209 связи в качестве интерфейса, такое как маршрутизатор или модем, по мере необходимости, как показано на фиг.13.

В настоящем описании этапы примеров, рассмотренных с применением блок-схем последовательности операций, содержат различные виды обработки, выполняемые последовательно во времени, однако такую обработку необязательно производить последовательно - ее можно осуществлять параллельно или индивидуально.

Кроме того, в настоящем описании термин «система» относится ко всему оборудованию, включающему несколько устройств.

Следует понимать, что специалисту в данной области могут быть очевидны различные изменения и модификации предпочтительных в настоящее время вариантов, рассмотренных здесь. Такие изменения и модификации могут быть произведены, не выходя за рамки сущности и объема настоящего изобретения и без ущерба для предполагаемых преимуществ. Поэтому предполагается, что подобные изменения и модификации подпадают под действие прилагаемой формулы изобретения.

Claims (24)

1. Система передачи данных, содержащая:

первое устройство, включающее в себя:

передатчик для передачи данных; и

первый процессор, функционально связанный с передатчиком, причем первый процессор выполнен с возможностью подготовки данных для передачи, по меньшей мере, в двух рабочих режимах, включающих в себя режим готовности и активный режим; и

второе устройство, включающее в себя:

приемник для приема данных;

запоминающее устройство; и

второй процессор, функционально связанный с приемником и запоминающим устройством, причем второй процессор обеспечивает, по меньшей мере, два рабочих режима, включающих в себя режим готовности и активный режим, для обработки принятых данных после приема данных;

при этом в режиме готовности принятые данные готовы к обработке после приема данных;

в активном режиме принятые данные после приема данных преобразуются в другой формат перед обработкой;

причем первый процессор выполнен с возможностью предоставления передатчику передаваемых передатчиком (i) первых данных, относящихся к режиму готовности и готовых к обработке после приема, (ii) первой команды перехода, относящейся к переходу из режима готовности в активный режим, (iii) вторых данных, относящихся к активному режиму и преобразуемых в другой формат после приема, и (iv) второй команды перехода, относящейся к переходу из активного режима в режим готовности;

при этом приемник выполнен с возможностью приема и передачи второму процессору первых данных, первой команды перехода, вторых данных и второй команды перехода, а второй процессор обеспечивает сохранение данных, указывающих, по меньшей мере, одну команду перехода, в запоминающем устройстве; а

второй процессор выполнен с возможностью (i) обработки первых данных в режиме готовности, (ii) перехода в активный режим на основе первой команды перехода, (iii) обработки вторых данных в активном режиме и (iv) перехода в режим готовности на основе второй команды перехода.

первое устройство, включающее в себя:

передатчик для передачи данных; и

первый процессор, функционально связанный с передатчиком, причем первый процессор выполнен с возможностью подготовки данных для передачи, по меньшей мере, в двух рабочих режимах, включающих в себя режим готовности и активный режим; и

второе устройство, включающее в себя:

приемник для приема данных;

запоминающее устройство; и

второй процессор, функционально связанный с приемником и запоминающим устройством, причем второй процессор обеспечивает, по меньшей мере, два рабочих режима, включающих в себя режим готовности и активный режим, для обработки принятых данных после приема данных;

при этом в режиме готовности принятые данные готовы к обработке после приема данных;

в активном режиме принятые данные после приема данных преобразуются в другой формат перед обработкой;

причем первый процессор выполнен с возможностью предоставления передатчику передаваемых передатчиком (i) первых данных, относящихся к режиму готовности и готовых к обработке после приема, (ii) первой команды перехода, относящейся к переходу из режима готовности в активный режим, (iii) вторых данных, относящихся к активному режиму и преобразуемых в другой формат после приема, и (iv) второй команды перехода, относящейся к переходу из активного режима в режим готовности;

при этом приемник выполнен с возможностью приема и передачи второму процессору первых данных, первой команды перехода, вторых данных и второй команды перехода, а второй процессор обеспечивает сохранение данных, указывающих, по меньшей мере, одну команду перехода, в запоминающем устройстве; а

второй процессор выполнен с возможностью (i) обработки первых данных в режиме готовности, (ii) перехода в активный режим на основе первой команды перехода, (iii) обработки вторых данных в активном режиме и (iv) перехода в режим готовности на основе второй команды перехода.

2. Система по п.1, в которой в режиме готовности обработка данных выполняется с использованием протокола JIS X 6319-4.

3. Система по п.2, в которой в режиме готовности после приема данных принятые данные форматируются в соответствии с протоколом JIS X 6319-4.

4. Система по п.1, в которой:

режим готовности включает в себя подрежим запрошенной готовности и подрежим объявленной готовности;

при этом в подрежиме запрошенной готовности для перехода в подрежим объявленной готовности обеспечивается ответ, содержащий идентификатор; а

в подрежиме объявленной готовности обработка выполняется, когда принята команда обработки, содержащая идентификатор.

режим готовности включает в себя подрежим запрошенной готовности и подрежим объявленной готовности;

при этом в подрежиме запрошенной готовности для перехода в подрежим объявленной готовности обеспечивается ответ, содержащий идентификатор; а

в подрежиме объявленной готовности обработка выполняется, когда принята команда обработки, содержащая идентификатор.

5. Система по п.4, в которой в подрежиме объявленной готовности команда обработки, содержащая идентификатор, вызывает переход из подрежима объявленной готовности в JIS-активный режим, в котором выполняется обработка.

6. Система по п.4, в которой в подрежиме объявленной готовности обработка команд и формирование ответов осуществляются с использованием протокола JIS X 6319-4.

7. Система по п.1, в которой в активном режиме обработка данных производится с использованием протокола ISO/IEC 7816-4 и/или протокола ISO/IEC 14443-4.

8. Система по п.7, в которой в активном режиме после приема данных принятые данные форматируются согласно протоколу, отличному от указанных протокола ISO/IEC 7816-4 и/или протокола ISO/IEC 14443-4.

9. Система по п.1, в которой, по меньшей мере, одна команда перехода вызывает переход в режим остановки, запрещающий прямой переход из режима остановки в режим готовности и из режима остановки в активный режим.

10. Система по п.9, в которой указанная, по меньшей мере, одна команда перехода включает в себя третью команду перехода и четвертую команду перехода, причем третья команда перехода вызывает переход из режима готовности в режим остановки, а четвертая команда перехода вызывает переход из активного режима в режим остановки.

11. Система по п.10, в которой третья команда перехода вызывает переход из режима остановки в холостой режим, что позволяет осуществлять прямой переход из холостого режима в режим готовности на основе четвертой команды перехода.

12. Система по п.1, в которой первое устройство является устройством чтения/записи, а второе устройство является микропроцессорной картой ("IС card").

13. Устройство передачи данных, содержащее:

передатчик для передачи данных; и

по меньшей мере, один процессор, функционально связанный с передатчиком, причем указанный, по меньшей мере, один процессор выполнен с возможностью подготовки данных для передачи, по меньшей мере, в двух рабочих режимах, включающих в себя режим готовности и активный режим;

при этом в режиме готовности данные, подготовленные к передаче, готовы к обработке после приема данных;

в активном режиме данные, подготовленные к передаче, преобразуются после приема данных в другой формат перед обработкой;

причем указанный, по меньшей мере, один процессор выполнен с возможностью предоставления передатчику (i) первых данных, относящихся к режиму готовности и готовых к обработке после приема, (ii) первой команды перехода, относящейся к переходу из режима готовности в активный режим, (iii) вторых данных, относящихся к активному режиму и преобразуемых в другой формат после приема, и (iv) второй команды перехода, относящейся к переходу из активного режима в режим готовности.

передатчик для передачи данных; и

по меньшей мере, один процессор, функционально связанный с передатчиком, причем указанный, по меньшей мере, один процессор выполнен с возможностью подготовки данных для передачи, по меньшей мере, в двух рабочих режимах, включающих в себя режим готовности и активный режим;

при этом в режиме готовности данные, подготовленные к передаче, готовы к обработке после приема данных;

в активном режиме данные, подготовленные к передаче, преобразуются после приема данных в другой формат перед обработкой;

причем указанный, по меньшей мере, один процессор выполнен с возможностью предоставления передатчику (i) первых данных, относящихся к режиму готовности и готовых к обработке после приема, (ii) первой команды перехода, относящейся к переходу из режима готовности в активный режим, (iii) вторых данных, относящихся к активному режиму и преобразуемых в другой формат после приема, и (iv) второй команды перехода, относящейся к переходу из активного режима в режим готовности.

14. Устройство по п.13, характеризующееся тем, что является микропроцессорной картой.

15. Устройство по п.13, характеризующееся тем, что является устройством чтения/записи.

16. Устройство передачи данных, содержащее:

приемник для приема данных;

запоминающее устройство; и

по меньшей мере, один процессор, функционально связанный с приемником и запоминающим устройством, причем указанный, по меньшей мере, один процессор обеспечивает, по меньшей мере, два рабочих режима, включающих в себя режим готовности и активный режим;

при этом в режиме готовности принятые данные готовы к обработке в указанном, по меньшей мере, одном процессоре;

в активном режиме принятые данные преобразуются в другой формат перед обработкой в указанном, по меньшей мере, одном процессоре;

причем указанный, по меньшей мере, один процессор выполнен с возможностью приема, по меньшей мере, одной команды перехода от приемника, обеспечения сохранения данных, указывающих, по меньшей мере, одну команду перехода, в запоминающем устройстве, перехода из режима готовности в активный режим на основе первой команды перехода и перехода из активного режима в режим готовности на основе второй команды перехода.

приемник для приема данных;

запоминающее устройство; и

по меньшей мере, один процессор, функционально связанный с приемником и запоминающим устройством, причем указанный, по меньшей мере, один процессор обеспечивает, по меньшей мере, два рабочих режима, включающих в себя режим готовности и активный режим;

при этом в режиме готовности принятые данные готовы к обработке в указанном, по меньшей мере, одном процессоре;

в активном режиме принятые данные преобразуются в другой формат перед обработкой в указанном, по меньшей мере, одном процессоре;

причем указанный, по меньшей мере, один процессор выполнен с возможностью приема, по меньшей мере, одной команды перехода от приемника, обеспечения сохранения данных, указывающих, по меньшей мере, одну команду перехода, в запоминающем устройстве, перехода из режима готовности в активный режим на основе первой команды перехода и перехода из активного режима в режим готовности на основе второй команды перехода.

17. Устройство по п.16, характеризующееся тем, что является микропроцессорной картой.

18. Устройство по п.16, характеризующееся тем, что является устройством чтения/записи.

19. Способ передачи данных, содержащий этапы, на которых:

принимают кадр данных, включающий в себя первый код обнаружения ошибок;

определяют, содержит ли принимаемый кадр данных неповрежденные данные, с использованием первого кода обнаружения ошибок;