KR900005152B1 - 반도체 집적회로장치 - Google Patents

반도체 집적회로장치 Download PDFInfo

- Publication number

- KR900005152B1 KR900005152B1 KR1019850009110A KR850009110A KR900005152B1 KR 900005152 B1 KR900005152 B1 KR 900005152B1 KR 1019850009110 A KR1019850009110 A KR 1019850009110A KR 850009110 A KR850009110 A KR 850009110A KR 900005152 B1 KR900005152 B1 KR 900005152B1

- Authority

- KR

- South Korea

- Prior art keywords

- transistor

- signal

- address

- semiconductor integrated

- integrated circuit

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims description 19

- 230000002040 relaxant effect Effects 0.000 claims description 3

- 230000004044 response Effects 0.000 claims 2

- 238000010586 diagram Methods 0.000 description 6

- 230000000116 mitigating effect Effects 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000006378 damage Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000002023 wood Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

- G11C11/4087—Address decoders, e.g. bit - or word line decoders; Multiple line decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- Static Random-Access Memory (AREA)

- Read Only Memory (AREA)

Abstract

내용 없음.

Description

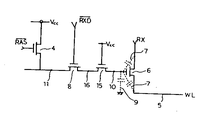

제1도는 본 발명의 일실시예인 반도체 장치의 구성을 나타낸 회로도.

제2도는 종래의 반도체 집적회로장치의 회로구성을 나타낸 회로도.

제3도는 종래의 반도체 집적회로장치의 동작을 설명하기 위한 파형도.

* 도면의 주요부분에 대한 부호의 설명

3 : 행디코더 4 : 프라챠아지용 트랜지스터

6 : 워드드라이버 트랜지스터 8 : 디커플 트랜지스터

15 : 전압완화용 트랜지스터

(도면중 동일부호는 동일 또는 그 상당부분을 표시함)

본 발명은 반도체 집적회로장치, 특히 행어드레스신호와 열어드레스신호를 같은 신호선을 사용하여 전달하고 절환스위치에 따라 행디코더 및 열디코더에 전달하도록 하는 구성의 MOS 다이나믹 RAM에 있어서 디코더의 출력부에 설치하는 디커플 트랜지스터(decouple transistor)에 인가되는 고전압을 완화하기 위한 반도체 집적회로장치에 관한 것이다. 제2도는 행어드레스신호와 열어드레스신호를 같은 신호선을 사용하여 전달하고 행선택시 및 열선택시에는 절환스위치에 따라 각각 행디코더 및 열디코더에 보내는 구성의 MOS 다이나믹 RAM에 있어서 디코더부의 종래의 회로구성을 나타낸 도면이다. 이하 제2도를 참조하고 행디코더 회로출력부의 구성 및 동작에 대하여 설명한다.

우선 행디코더계에 대하여 설명한다.

어드레스신호선 1-1∼1-n을 통하여 주어지는 어드레스 신호 A1∼An,을 받아서 코드하는 행디코더(3)와 로우어드레스 스트로브신호()와 같은 시기에 온·오프하고 행디코더(3)의 출력신호선을 프리챠아지하기 위한 프리챠아지 트랜지스터(4)와 행디코더(3)의 출력신호선에 설치되며 행디코더(3)와 워드선(5)을 분리하기 위한 신호()를 그 게이트에 받아서 온·오프하는 디커플 트랜지스터(8)와 워드선 구동신호(RX)를 워드라인(5)에 전달하기 위한 워드드라이버 트랜지스터(6)로 구성된다.

행디코더(3)는 그 게이트 각각이 어드레스신호선(1-1∼1-n)에 접속되고 그 드레인(drain)이 출력신호선에 공통으로 접속되며 또한 그 소스가 각각 접속되는 전계효과형 트랜지스터(2-1∼2-n)로 구성된다.

디커플 트랜지스터(8)는 그 게이트에 신호()를 받아서 그 소스가 프리챠아지 트랜지스터(4)의 드레인과 노우드(11)를 통해서 접속되며 그 드레인은 노우드(10)를 통하여 워드드라이버 트랜지스터(6)의 게이트에 접속된다.

워드드라이버 트랜지스터(6)는 그 한쪽 도통단자에 워드선구동신호(RX)를 받으며 그 다른쪽 도통단자는 워드선(5)에 접속된다.

여기에서 파선으로 표시된 용량(7)은 트랜지스터(6)의 게이트용량이며 파선으로 표시된 용량(9)은 디커플 트랜지스터(8)의 드레인과 워드드라이버 트랜지스터(6)의 게이트를 접속하는 배선의 부유용량이다.

열디코더계는 어드레스신호선(1-1∼1-n)에 각각 접속되며 열어드레스신호를 열디코더(12)에 전달하기 위한 신호선(13-1∼13-n)과 어드레스신호선(13-1∼13n)과의 각각에 대하여 설치되며 그 게이트에 어드레스 스위치신호(ADSW)를 받아서 온·오프하며 열선택시에 열어드레인신호를 열디코더(12)로 전달하기 위한 스위치 트랜지스터(14-1∼14-n)와 부여된 열어드레스신호를 디코드하기 위한 열디코더(12)로 구성된다.

제3도는 제2도에 표시된 회로에 있어서 각 신호의 타이밍을 표시한 파형도이다.

이하 제2도 및 제3도를 참조하여 종래의 디코더회로의 동작에 대하여 설명한다.

먼저 행선택을 구동하는 기본신호인신호가 올라가서 "H"가 됨에 따라 프리챠아지 트랜지스터(4)가 온상태가 되어서 전원(전압 Vcc=5V)에 행디코더(3)의 출력신호선이 접속되며 동시에 신호()가 "H"로 되어서 디커플 트랜지스터(8)이 온상태가 되고 노우드(10)(11)가 트랜지스터(4)를 통하여 충전된다.

프리챠아지 트랜지스터(4), 디커플 트랜지스터(8)의 정격치전압을 동시에 1V로 하면 노우드(10)(11)의 전위는 4V가 된다.

이렇게 주어진 행어드레스신호중 하나라도 "H"인 것이 있으면 행어드레스디코더(3)에 포함되는 트랜지스터(2-1∼2-n) 가운데 "H"가 입력된 신호선에 연결하는 트랜지스터가 온되고 노우드(10)(11)의 전위는 그 트랜지스터를 사이에 두고 방전되어 0V가 된다.

입력된 행어드레스신호가 모두 "L"의 행디코더(3)에 있어서만 노우드(10)(11)의 전위가 4V 그대로 유지되며 행디코더(3)의 세트가 완료된다.

이때 노우드(10)의 전위는 4V이므로 워드드라이버 트랜지스터(6)는 온상태로 있고 계속해서 입력되는 "H"의 워드선 구동신호(RX)(전압 5V)가 워드선(5)에 전달되어 워드선(5)의 전위도 5V가 된다.

워드선 구동신호(RX)가 입력되면 워드드라이버 트랜지스터(6)의 게이트용량(7)에 의한 용량결합 때문에 노우드(10)의 전위가 상승하고 노우드(10)에 존재하는 배선부유용량(9)을 고려하면 실제로는 8V정도에 달한다.

이후 어드레스절환신호(ADSW)가 올라가서 스위치 트랜지스터(14-1∼14-n)가 온상태로 되면 열디코더(12)와 신호선(13-1∼13-n)이 접속되고 계속하여 입력되는 열어드레스신호는 열디코더(12)에 전달된다. 이 열어드레스신호는 신호선(1-1∼1-n)에 따라 전달되므로 트랜지스터(2-1∼2-n)의 게이트에도 입력되게 된다.

일반적으로는 이 열어드레스신호는 바로 그 앞에 입력된 행어드레스신호와는 다르므로 워드선 선택시에 선택된 행디코더(3)의 트랜지스터(2-1∼2-n)의 몇 개정도가 온상태가 되고 그 온상태의 트랜지스터를 통해서 노우드(11)의 전압은 방전되어 0V가 된다.

따라서 최종적으로는 선택된 행디코더에 있어서 디커플 트랜지스터(8)의 소스, 게이트 및 드레인의 전위는 각각 0V, 0V 및 8V가 되고 소스, 드레인사이, 게이트, 드레인사이에는 동시에 8V정도의 고전압이 인가되고 있다.

최근에는 워드선을 승압하는 경우가 많아졌으나 이 경우에 워드선 구동신호(RX)는 7V정도가 되므로 그에 대응하고 열선택시의 디커플 트랜지스터(8)의 소스, 게이트 및 드레인의 전위는 각각 0V, 0V 및 1V가 되고 소스, 드레인사이, 게이트, 드레인사이에는 동시에 10V에 달하도록 고전압이 인가되게 된다. 종래의 회로구성에서는 상술한 바와같이 디커플 트랜지스터(8)에 고전압이 인가되므로 디커플 트랜지스터(8) 열화, 파괴 혹은 오동작 때문에 신뢰성의 심한 저하를 초래한다고하는 결점이 있었다.

그러므로 본 발명의 목적은 상술한 바와같은 결점을 제거하고 디커플 트랜지스터에 인가되는 고전압을 완화하며 그에 따라 신뢰성이 높은 반도체 집적회로장치를 제공하는 것이다.

본 발명에 관계되는 반도체 집적회로장치는 디커플 트랜지스터에 인가되는 고전압을 완화하기 위한 전압 완화수단을 새로 설치한 것이다. 전압완화수단은 디커플 트랜지스터의 드레인과 드라이버 트랜지스터의 게이트와의 사이에 배치되어 그 게이트에 전원전압을 받은 1개의 트랜지스터이다.

전압완화수단은 1개의 추가된 트랜지스터에 따르며 종래 디커플 트랜지스터에 인가되어 있던 전압이 전압완화용의 트랜지스터와 디커플 트랜지스터로 나누어지기 때문에 디커플 트랜지스터에 인가되는 전압을 완화할 수 있고 신뢰성이 높은 안정된 동작을 하는 반도체 집적회로장치를 얻을 수 있다.

이하 본 발명의 일실시예를 도면에 따라서 설명한다.

제1도는 본 발명의 일실시예인 반도체 집적회로장치의 구성을 나타낸 회로도이다.

제1도에 있어서 본 발명의 특징으로서 종래의 반도체 집척회로장치와는 달리 디커플 트랜지스터(8)의 드레인과 그 한쪽 도통단자가 노우드(16)를 통해 접속되며 그 다른쪽 도통단자가 노우드(10)를 통해 워드드라이버 트랜지스터(6)의 게이트에 접속되고 또한 그 게이트에 전원전압(Vcc)을 받는 전압완화용의 트랜지스터(15)가 설치된다. 다음에 제1도에 표시된 구성을 가진 반도체 집적회로장치의 트랜지스터(15)에 따르는 전압의 완화동작을 설명한다.

일예로서 워드선을 승압한 경우, 즉 신호(RX)의 전위가 7V인 경우에 대하여 설명한다.

신호(RX)가 입력되었을 때(신호(RX)가 "H"인때), 워드드라이버 트랜지스터(6)의 게이트용량(7)에 의한 용량결합으로 노우드(10)의 전위가 10V가 될 때까지는 제2도에 나타낸 종래의 회로구성에 의한 동작과 동일하다.

그러나 새롭게 추가된 트랜지스터(15)의 게이트가 전원전위(Vcc=5V)에 접속되어 있으므로 노우드(16)의 전위는 4V로 억제된다.

여기에서 트랜지스터(15)의 정격치전압을 1V로 가정하였다.

따라서 선택된 행디코더에 있어서 최종적으로는 노우드(10)(16)(11)의 전위는 10V, 4V 및 0V로, 또 트랜지스터(15)(8)의 게이트의 전위는 각각 5V, 0V로 된다.

이 결과 디커플 트랜지스터(8)의 소스(11), 드레인(16)사이 및 소스, 드레인사이의 전압은 동시에 4V정도로 억제되며 또한 트랜지스터(15)에 인가되는 전압도 최대로 소스, 드레인사이(노우드(10)와 노우드(16)사이)의 6V정도이며 트랜지스터(8)(15)에 인가되는 전압은 충분히 완화되게 된다.

또한 상기 실시예에 있어서는 행디코더회로의 출력부에 대하여 설명하였으나 열디코더회로의 출력부에 있어서 똑같은 논리가 성립된다.

이상과 같이 본 발명에 따르면 디커플 트랜지스터에 인가되는 전압을 완화하기 위한 완화수단, 바람직하게 1개의 트랜지스터를 설치하였으므로 예를들면 워드선을 승압한 경우에도 디커플 트랜지스터에 인가되는 고전압을 완화하고 신뢰성이 높은 반도체 집적회로장치를 얻을 수 있다.

Claims (5)

- 어드레스디코더회로와 메모리셀 선택과의 사이에 설치되고 제1의 동작타이밍신호에 응답하여, 온·오프하고 상기 어드레스디코더회로의 출력신호선을 프리챠아지하기 위한 제1의 트랜지스터(4)와 상기 출력신호선에 설치되며 제2의 동작타이밍신호에 응답하여 온·오프하여 상기 출력신호선상의 신호를 전달하기 위한 제2의 트랜지스터(6)와 상기 제2의 트랜지스터(6)로부터 전달되는 신호를 그 게이트에 받아서 온·오프하고 제3의동작타이밍신호를 상기 메모리셀 선택선상에 전달하기 위한 제3의트랜지스터(8)를 갖춘 반도체 집적회로장치에 있어서 상기 제2의 트랜지스터(6)의 오프시에 상기 제2의 트랜지스터(6)에 인가되는 전압을 완화하기 위한 전압완화수단을 설치한 것을 특징으로하는 반도체 집적회로장치.

- 제1항에 있어서 상기 전압완화수단은 상기 제2트랜지스터(6)의 출력측의 도통단자와 상기 제3트랜지스터(8)의 게이트와의 사이에 설치되고 그 게이트에 전원전압을 받는 MOS 트랜지스터로 되어 있는 반도체 집적회로장치.

- 제2항에 있어서 상기 트랜지스터의 수는 1개로 되어 있는 반도체 집적회로장치.

- 제1항에, 제2항 또는 제3항에 있어서 상기 어드레스디코더회로는 행어드레스디코더회로(3)이고 상기 메모리셀 선택선은 워드선(5)으로 되어 있는 반도체 집적회로장치.

- 제1항 또는 제2항에 있어서 상기 어드레스디코더회로는 열어드레스디코더회로(12)이고 상기 메모리셀 선택선은 비트선으로 되어 있는 반도체 집적회로장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP135334 | 1985-06-20 | ||

| JP60-135334 | 1985-06-20 | ||

| JP60135334A JPS61294695A (ja) | 1985-06-20 | 1985-06-20 | 半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR870000762A KR870000762A (ko) | 1987-02-20 |

| KR900005152B1 true KR900005152B1 (ko) | 1990-07-20 |

Family

ID=15149336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019850009110A KR900005152B1 (ko) | 1985-06-20 | 1985-12-04 | 반도체 집적회로장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US4811304A (ko) |

| JP (1) | JPS61294695A (ko) |

| KR (1) | KR900005152B1 (ko) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4963765A (en) * | 1989-07-03 | 1990-10-16 | Texas Instruments Incorporated | High speed CMOS transition detector circuit |

| JP2612618B2 (ja) * | 1989-10-13 | 1997-05-21 | 富士通株式会社 | 半導体集積回路装置 |

| GB9007790D0 (en) * | 1990-04-06 | 1990-06-06 | Lines Valerie L | Dynamic memory wordline driver scheme |

| GB9007791D0 (en) * | 1990-04-06 | 1990-06-06 | Foss Richard C | High voltage boosted wordline supply charge pump and regulator for dram |

| JPH0812754B2 (ja) * | 1990-08-20 | 1996-02-07 | 富士通株式会社 | 昇圧回路 |

| US5160860A (en) * | 1991-09-16 | 1992-11-03 | Advanced Micro Devices, Inc. | Input transition responsive CMOS self-boost circuit |

| JPH05307891A (ja) * | 1992-05-01 | 1993-11-19 | Nec Corp | 行デコーダ |

| US5293342A (en) * | 1992-12-17 | 1994-03-08 | Casper Stephen L | Wordline driver circuit having an automatic precharge circuit |

| US5311481A (en) * | 1992-12-17 | 1994-05-10 | Micron Technology, Inc. | Wordline driver circuit having a directly gated pull-down device |

| KR100518399B1 (ko) | 2000-07-25 | 2005-09-29 | 엔이씨 일렉트로닉스 가부시키가이샤 | 내부 전압 레벨 제어 회로 및 반도체 기억 장치 및 그들의제어 방법 |

| TWI621337B (zh) * | 2013-05-14 | 2018-04-11 | 半導體能源研究所股份有限公司 | 信號處理裝置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5528138B2 (ko) * | 1974-09-09 | 1980-07-25 | ||

| US3969706A (en) * | 1974-10-08 | 1976-07-13 | Mostek Corporation | Dynamic random access memory misfet integrated circuit |

| JPS53101236A (en) * | 1977-02-16 | 1978-09-04 | Toshiba Corp | Address selection circuit for mos dynamic memory |

| US4289982A (en) * | 1979-06-28 | 1981-09-15 | Motorola, Inc. | Apparatus for programming a dynamic EPROM |

| JPS5694661A (en) * | 1979-12-27 | 1981-07-31 | Fujitsu Ltd | Semiconductor device |

| JPS56156987A (en) * | 1980-05-06 | 1981-12-03 | Nec Corp | Semiconductor storage circuit |

| JPS5730192A (en) * | 1980-07-29 | 1982-02-18 | Fujitsu Ltd | Sense amplifying circuit |

| JPS5774886A (en) * | 1980-10-29 | 1982-05-11 | Toshiba Corp | Semiconductor integrated circuit device |

| JPS58212226A (ja) * | 1982-06-02 | 1983-12-09 | Mitsubishi Electric Corp | ブ−トストラツプ回路 |

| JPS599990A (ja) * | 1982-07-07 | 1984-01-19 | Mitsubishi Electric Corp | 半導体レ−ザの製造方法 |

-

1985

- 1985-06-20 JP JP60135334A patent/JPS61294695A/ja active Granted

- 1985-12-04 KR KR1019850009110A patent/KR900005152B1/ko not_active IP Right Cessation

-

1986

- 1986-03-10 US US06/838,303 patent/US4811304A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH0470716B2 (ko) | 1992-11-11 |

| US4811304A (en) | 1989-03-07 |

| JPS61294695A (ja) | 1986-12-25 |

| KR870000762A (ko) | 1987-02-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4697106A (en) | Programmable memory circuit | |

| US4692638A (en) | CMOS/NMOS decoder and high-level driver circuit | |

| US4811292A (en) | Semiconductor memory in which data readout operation is carried out over wide power voltage range | |

| EP0326878A2 (en) | Decoder driver circuit for programming high-capacitance lines | |

| EP0186907A2 (en) | Non-volatile semiconductor memory device having an improved write circuit | |

| KR900005152B1 (ko) | 반도체 집적회로장치 | |

| JPH0115957B2 (ko) | ||

| JP2007323808A (ja) | 半導体記憶装置用xデコーダ | |

| US20020004267A1 (en) | Sense amplifier circuit and semiconductor storage device | |

| KR930001654B1 (ko) | 반도체 메모리 집적회로 | |

| EP0191544A2 (en) | CMOS decoder/driver circuit for a memory | |

| US4259731A (en) | Quiet row selection circuitry | |

| US4063118A (en) | MIS decoder providing non-floating outputs with short access time | |

| US4542306A (en) | Buffer circuits for use with semiconductor memory devices | |

| KR930000963B1 (ko) | 불휘발성 메모리 회로장치 | |

| US6137733A (en) | Boosting circuit using 2-step boosting operation | |

| US7282956B2 (en) | High voltage switching circuit of nonvolatile memory device | |

| KR950000029B1 (ko) | 기생용량에 의해 야기된 오동작을 방지하기 위한 eprom의 디코더 회로 | |

| KR100207971B1 (ko) | 전위 전송회로 및 이를 이용한 반도체 장치 | |

| US5566115A (en) | Semiconductor memory device | |

| JPH0766675B2 (ja) | プログラマブルrom | |

| US5239207A (en) | Semiconductor integrated circuit | |

| US4042833A (en) | In-between phase clamping circuit to reduce the effects of positive noise | |

| US6430093B1 (en) | CMOS boosting circuit utilizing ferroelectric capacitors | |

| EP0251734A2 (en) | Static random-access memory devices |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20010711 Year of fee payment: 12 |

|

| LAPS | Lapse due to unpaid annual fee |