KR20180118137A - 가변 주파수 rc 발진기 - Google Patents

가변 주파수 rc 발진기 Download PDFInfo

- Publication number

- KR20180118137A KR20180118137A KR1020187025097A KR20187025097A KR20180118137A KR 20180118137 A KR20180118137 A KR 20180118137A KR 1020187025097 A KR1020187025097 A KR 1020187025097A KR 20187025097 A KR20187025097 A KR 20187025097A KR 20180118137 A KR20180118137 A KR 20180118137A

- Authority

- KR

- South Korea

- Prior art keywords

- delay

- stage

- oscillator circuit

- output

- variable

- Prior art date

Links

- 230000001419 dependent effect Effects 0.000 claims abstract description 4

- 239000003990 capacitor Substances 0.000 claims description 124

- 238000000034 method Methods 0.000 claims description 27

- 230000008878 coupling Effects 0.000 claims 1

- 238000010168 coupling process Methods 0.000 claims 1

- 238000005859 coupling reaction Methods 0.000 claims 1

- 238000005516 engineering process Methods 0.000 description 10

- 208000037516 chromosome inversion disease Diseases 0.000 description 7

- 230000010355 oscillation Effects 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 230000008901 benefit Effects 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000001934 delay Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/03—Astable circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/03—Astable circuits

- H03K3/0315—Ring oscillators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/20—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising resistance and either capacitance or inductance, e.g. phase-shift oscillator

- H03B5/24—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising resistance and either capacitance or inductance, e.g. phase-shift oscillator active element in amplifier being semiconductor device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/20—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising resistance and either capacitance or inductance, e.g. phase-shift oscillator

- H03B5/26—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising resistance and either capacitance or inductance, e.g. phase-shift oscillator frequency-determining element being part of bridge circuit in closed ring around which signal is transmitted; frequency-determining element being connected via a bridge circuit to such a closed ring, e.g. Wien-Bridge oscillator, parallel-T oscillator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/01—Shaping pulses

- H03K5/04—Shaping pulses by increasing duration; by decreasing duration

- H03K5/06—Shaping pulses by increasing duration; by decreasing duration by the use of delay lines or other analogue delay elements

- H03K5/065—Shaping pulses by increasing duration; by decreasing duration by the use of delay lines or other analogue delay elements using dispersive delay lines

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/125—Discriminating pulses

- H03K5/1252—Suppression or limitation of noise or interference

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/099—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

- Pulse Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로는, 제1 지연 섹션에 제공되는 제어 신호에 의해 설정되는 가변 지연 및 음의 게인을 갖는 제1 지연 섹션을 포함할 수 있다. 음의 게인 및 고정 지연을 갖는 제2 지연 섹션은 제1 지연 섹션과 직렬로 연결될 수 있다. 발진기 회로는, 제1 지연 섹션의 지연 및 제2 지연 섹션의 지연에 의존하는 주파수를 갖는 제2 지연 섹션의 출력을 포함하는 출력을 포함할 수 있다.

Description

[0001]

35 U.S.C.§119(e)에 의거하여, 본 출원은 2016년 3월 2일자로 출원된 미국 가출원 제62/302,735 호의 출원일의 이익을 받을 권한을 갖고, 이를 주장하고, 상기 출원의 전체 내용은 모든 목적으로 본원에 인용에 의해 통합된다.

[0002]

본 개시내용은 일반적으로 발진기들에 관한 것이며, 더 상세하게는, 가변 주파수를 갖는 RC 발진기에 관한 것이다.

[0003]

디지털 로직 회로들의 설계에서, 대규모 집적 기술들은 많은 수의 컴포넌트들이 단일 실리콘 칩 상에서 제조되는 구조를 가져왔다. 디지털 회로는 통상적으로 자신들의 동작을 위한 시간 축(time base)을 제공하기 위한 다양한 클록 신호들을 요구한다. 이러한 클록 신호들은 다양한 설계들에 도입되는 발진기 회로들에 의해 생성된다. 하나의 그러한 설계는 RC(resistor/capacitor) 발진기로 지칭되는 RC 네트워크에 기반한다.

[0004]

종래의 RC 발진기들은 저가의 타이밍 소스를 제공할 수 있다. 또한, 종래의 RC 발진기들은, 집적 회로들 상에서 제조하기에 어려울 수 있는 인덕터들(예컨대, 도 5 참조)의 사용을 피한다. RC 발진기들은 자신들의 유용성을 증가시키기 위해 저항(R) 또는 커패시턴스(C)를 변경함으로써 가변 주파수들의 생성을 허용할 수 있다.

[0005]

본 개시내용의 양상들에 따라, 프로그래밍 가능한 출력 주파수를 갖는 발진기 회로는 입력단 및 출력단을 갖는 제1 지연 섹션을 포함할 수 있다. 제1 지연 섹션은 입력단과 출력단 간의 음의 게인(negative gain), 및 제1 지연 섹션에 제공되는 제어 신호에 의해 설정되는 가변 지연을 가질 수 있다. 발진기는 제1 지연 섹션과 직렬로 전기적으로 연결된 제2 지연 섹션을 더 포함할 수 있다. 제2 지연 섹션은 입력단과 출력단 및 입력단과 출력단 사이의 음의 게인을 가질 수 있다. 제2 지연 섹션은 고정 지연을 가질 수 있다. 발진기는 제1 지연 섹션으로 인한 지연 및 제2 지연 섹션으로 인한 지연의 함수인 주파수를 갖는 출력 신호를 위한 회로 출력을 더 포함할 수 있다. 회로 출력은 제2 지연 섹션의 출력단을 포함할 수 있다.

[0006]

일부 실시예들에서, 제1 지연 섹션은 저항기 및 가변 커패시터를 포함하는 제1 RC 네트워크, 및 제1 RC 네트워크와 직렬로 연결되고 또한 저항기 및 가변 커패시터를 포함하는 제2 RC 네트워크를 포함할 수 있다. 제1 지연 섹션의 지연은 제1 및 제2 RC 네트워크들의 가변 커패시터들의 커패시턴스들에 기반하여 결정될 수 있다. 제어 신호는 제1 RC 네트워크의 가변 커패시터의 커패시턴스를 설정할 수 있고, 추가 제어 신호는 제2 RC 네트워크의 가변 커패시터의 커패시턴스를 설정할 수 있다.

[0007]

일부 실시예들에서, 제1 지연 섹션은 저항기 및 가변 커패시터를 포함하는 RC 네트워크를 포함할 수 있다. 제1 지연 섹션에 제공되는 제어 신호는 제1 RC 네트워크의 가변 커패시터의 커패시턴스를 설정할 수 있다. 제1 지연 섹션의 지연은 가변 커패시터의 커패시턴스에 기반할 수 있다.

[0008]

일부 실시예들에서, 제1 지연 섹션은 복수의 스위칭형 커패시터들을 포함할 수 있고, 제어 신호는 선택적으로 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 설정한다. 일부 실시예들에서, 스위칭형 커패시터가 ON 상태에 있을 때, 스위칭형 커패시터는 DC 전압에 전기적으로 연결된 노드를 갖는다. 다른 실시예들에서, 스위칭형 커패시터가 ON 상태에 있을 때, 스위칭형 커패시터는 접지 전위에 전기적으로 연결된 노드를 갖는다. 제어 신호는 n-비트 워드일 수 있다.

[0009]

일부 실시예들에서, 제2 지연 섹션은, 고정 값 저항성 컴포넌트 및 고정 값 용량성 컴포넌트를 포함하는 RC 네트워크를 포함할 수 있다. 고정 값 용량성 컴포넌트의 적어도 하나의 노드는 발진기 회로의 공급 전압 위로 스윙(swing)할 수 있다. 일부 실시예들에서, 고정 값 용량성 컴포넌트의 적어도 하나의 노드는 접지 전위 아래로 스윙할 수 있다.

[0010]

일부 실시예들에서, 제1 지연 섹션은 피드백 루프의 제2 지연 섹션을 통해 회로 출력에 전기적으로 연결될 수 있다.

[0011]

본 개시내용의 양상들에 따라, 발진기 회로는 입력단 및 출력단을 갖는 제1 지연 섹션을 포함할 수 있다. 제1 지연 섹션은 입력단과 출력단 간의 음의 게인을 가질 수 있다. 제1 지연 섹션은 저항기 및 가변 커패시터를 포함하는 제1 RC 네트워크, 및 제1 RC 네트워크와 직렬로 연결되고 저항기 및 가변 커패시터를 포함하는 제2 RC 네트워크를 포함할 수 있다. 발진기 회로는 제1 지연 섹션의 지연을 설정하기 위해 제1 RC 네트워크의 적어도 가변 커패시터에 제공되는 적어도 하나의 제어 신호를 포함할 수 있다. 발진기 회로는 제1 지연 섹션과 직렬로 전기적으로 연결된 제2 지연 섹션을 포함할 수 있다. 제2 지연 섹션은 입력단과 출력단 및 입력단과 출력단 사이의 음의 게인을 가질 수 있다. 제2 지연 섹션은 고정 지연을 가질 수 있다. 발진기 회로는 제1 지연 섹션으로 인한 지연 및 제2 지연 섹션으로 인한 지연의 함수인 주파수를 갖는 출력 신호를 위한 회로 출력을 포함할 수 있다. 회로 출력은 제2 지연 섹션의 출력단을 포함할 수 있다.

[0012]

일부 실시예들에서, 제1 지연 섹션 내의 제1 RC 네트워크 및 제2 RC 네트워크 내의 가변 커패시터들 각각은 복수의 스위칭형 커패시터들을 포함할 수 있고, 프로그래밍 가능한 지연 스테이지에 제공되는 제어 신호는 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 선택적으로 설정한다. 일부 실시예들에서, 스위칭형 커패시터가 ON 상태에 있을 때, 스위칭형 커패시터의 노드는 DC 전압에 전기적으로 연결된다. 다른 실시예들에서, 스위칭형 커패시터가 ON 상태에 있을 때, 스위칭형 커패시터의 노드는 접지 전위에 전기적으로 연결된다.

[0013]

일부 실시예들에서, 제어 신호는 제1 RC 네트워크의 가변 커패시터에 제공될 수 있다. 발진기 회로는 제2 RC 네트워크의 가변 커패시터에 제공되는 추가 제어 신호를 더 포함할 수 있다.

[0014]

일부 실시예들에서, 제1 지연 섹션은, 제2 RC 네트워크와 직렬로 연결되고 저항기 및 가변 커패시터를 포함하는 적어도 제3 RC 네트워크를 더 포함할 수 있다.

[0015]

일부 실시예들에서, 제2 지연 섹션은, 고정 값 저항성 컴포넌트 및 고정 값 용량성 컴포넌트를 포함하는 RC 네트워크를 포함할 수 있다. 용량성 컴포넌트의 적어도 하나의 노드는 발진기 회로의 공급 전압 위로 스윙할 수 있다. 용량성 컴포넌트의 적어도 하나의 노드는 추가로 접지 전위 아래로 스윙할 수 있다.

[0016]

본 개시내용의 양상들에 따라, 발진기 회로는 제1 인버터 스테이지, 및 제1 인버터 스테이지의 출력에 전기적으로 연결된 입력을 갖는 제2 인버터 스테이지를 포함할 수 있다. 제2 인버터 스테이지는 발진기 회로의 출력 신호를 위한 출력을 가질 수 있다. 발진기 회로는 용량성 엘리먼트에 연결된 저항기 엘리먼트를 포함하는 RC 회로를 포함할 수 있다. RC 회로는 제2 인버터 스테이지의 입력과 출력 사이에 전기적으로 연결될 수 있다. 발진기 회로는 적어도 하나의 가변 지연 스테이지에 제공되는 제어 신호에 의해 설정되는 지연을 갖는 적어도 하나의 가변 지연 스테이지를 포함할 수 있다. 적어도 하나의 가변 지연 스테이지는, 저항기 엘리먼트와 커패시터 엘리먼트를 연결하는 RC 회로의 노드와 제1 인버터 스테이지의 입력 사이에 전기적으로 연결될 수 있다. 출력 신호의 주파수는 적어도 하나의 가변 지연 스테이지의 지연에 의존할 수 있다.

[0017]

일부 실시예들에서, 발진기 회로는, 적어도 하나의 가변 지연 스테이지와 직렬로 연결되고, 적어도 하나의 추가 가변 지연 스테이지에 제공되는 제어 신호에 의존하는 지연을 갖는 적어도 하나의 추가 가변 지연 스테이지를 더 포함할 수 있다.

[0018]

일부 실시예들에서, 저항기 엘리먼트 및 커패시터 엘리먼트를 연결하는 노드에서의 전압 레벨은 발진기 회로의 공급 전압 위로 그리고 아래로 스윙하고, 발진기 회로의 동작 동안에 접지 전위 위로 그리고 아래로 스윙할 수 있다.

[0019]

일부 실시예들에서, 적어도 하나의 가변 지연 스테이지는 저항기 및 가변 커패시터를 포함할 수 있고, 적어도 하나의 가변 지연 스테이지에 제공되는 제어 신호는 가변 커패시터의 커패시턴스를 설정한다. 적어도 하나의 가변 지연 스테이지의 지연은 가변 커패시터의 커패시턴스에 의존할 수 있다.

[0020]

일부 실시예들에서, 적어도 하나의 가변 지연 스테이지는 복수의 스위칭형 커패시터들을 포함할 수 있고, 제어 신호는 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 설정한다. 일부 실시예들에서, 스위칭형 커패시터가 ON 상태에 있을 때, 스위칭형 커패시터의 노드는 DC 전압 또는 접지 전위에 전기적으로 연결된다.

[0021]

일부 실시예들에서, RC 회로의 용량성 엘리먼트의 적어도 하나의 노드는 발진기 회로의 공급 전압 위로 그리고 접지 전위 아래로 스윙한다.

[0022]

하기의 상세한 설명 및 첨부 도면들은 본 개시내용의 특성 및 이점들의 더 양호한 이해를 제공한다.

[0023]

이하의 논의 그리고 특히 도면들에 관련하여, 도시된 특정사항들이 예시적인 논의 목적으로 예들을 도시하고, 본 개시내용의 원리들 및 개념적인 양상들의 설명을 제공하기 위해 제시된다는 점이 강조된다. 이와 관련하여, 본 개시내용의 기본적인 이해를 위해 필요한 것 이상으로 구현 세부사항들을 도시하려는 어떠한 시도도 이루어지지 않는다. 도면들과 관련하여 이어지는 논의는 본 개시내용에 따른 실시예들이 어떻게 실시될 수 있는지를 당업자들에게 자명하게 한다. 유사하거나 동일한 참조 번호들은 다양한 도면들 및 이를 지지하는 설명들에서 동일하거나 유사한 엘리먼트들을 식별하거나 그렇지 않다면 이들을 지칭하는데 사용될 수 있다. 첨부된 도면에서:

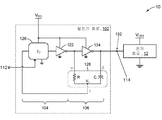

[0024] 도 1a 및 1b는 본 개시내용에 따른 발진기 회로를 도시한다.

[0025] 도 2는 본 개시내용에 따른 발진기 회로를 도시한다.

[0026] 도 2a는 본 개시내용에 따른 가변 커패시터의 세부사항들을 도시한다.

[0027] 도 3은 본 개시내용에 따른 발진기 회로를 도시한다.

[0028] 도 3a는 본 개시내용에 따른 가변 커패시터의 세부사항들을 도시한다.

[0029] 도 4a 및 4b는 본 개시내용에 따른 대안적인 실시예들을 예시한다.

[0030] 도 5는 종래의 RC 발진기의 예를 도시한다.

[0024] 도 1a 및 1b는 본 개시내용에 따른 발진기 회로를 도시한다.

[0025] 도 2는 본 개시내용에 따른 발진기 회로를 도시한다.

[0026] 도 2a는 본 개시내용에 따른 가변 커패시터의 세부사항들을 도시한다.

[0027] 도 3은 본 개시내용에 따른 발진기 회로를 도시한다.

[0028] 도 3a는 본 개시내용에 따른 가변 커패시터의 세부사항들을 도시한다.

[0029] 도 4a 및 4b는 본 개시내용에 따른 대안적인 실시예들을 예시한다.

[0030] 도 5는 종래의 RC 발진기의 예를 도시한다.

[0031]

다음의 설명에서, 설명의 목적으로, 다수의 예들 및 특정 세부사항들이 본 개시내용의 철저한 이해를 제공하기 위해 제시된다. 그러나, 청구항들에서 표현되는 바와 같은 본 개시내용은 이들 예들의 특징들 중 일부 또는 전부를 단독으로 또는 아래에서 설명되는 다른 특징들과 결합하여 포함할 수 있으며, 본원에서 설명되는 특징들 및 개념들의 수정들 및 등가물들을 더 포함할 수 있다는 것이 당업자에게 자명할 것이다.

[0032]

도 1a는 본 개시내용의 실시예에 따른 전자 회로(10)를 도시한다. 전자 회로(10)는 발진기 회로(102) 및 전자 회로(12)를 포함할 수 있다. 발진기 회로(102)는, 예컨대, 전자 회로(12)에 의해 사용될 수 있는 출력 신호(예컨대, 클록 신호(132))를 위한 출력(114)을 가질 수 있다. 전자 회로(10)는 전자 디바이스(도시되지 않음) 내의 컴포넌트일 수 있다. 발진기 회로(102)는 소스(VDD)에 의해 전력이 공급될 수 있고, 전자 회로(12)는 소스(VDD1)에 의해 전력이 공급될 수 있다. 일부 실시예들에서, VDD는 VDD1과 동일할 수 있고, 다른 실시예들에서 VDD는 VDD1과 상이할 수 있다.

[0033]

발진기(102)는 제1 지연 섹션(104) 및 제1 지연 섹션(104)과 직렬로 전기적으로 연결된 제2 지연 섹션(106)을 포함할 수 있다. 본 개시내용에 따라, 제1 지연 섹션(104)은, 제1 지연 섹션(104)의 입력단과 제1 지연 섹션(104)의 출력단 사이의 음의 게인을 특징으로 할 수 있다. 예컨대, 도 1a를 참조하면, 일부 실시예들에서, 제1 지연 섹션(104)은 반전 스테이지(122)와 직렬로 연결된 지연 스테이지(126)를 포함할 수 있다. 아래에 더 상세히 논의되는 바와 같이, 제1 지연 섹션(104)은 추가로 가변 지연을 갖는 것을 특징으로 할 수 있다. 또한, 음의 게인에 의해, 입력단에서의 (전압에 대해) 주어진 양의 변화는 출력단에서 (전압의) 음의 변화를 생성한다는 것을 의미한다.

[0034]

제1 지연 섹션(104)의 입력단은 지연 스테이지(126)의 입력측에 의해 정의될 수 있다. 제1 지연 섹션(104)의 출력단은 반전 스테이지(122)의 출력에 의해 정의될 수 있다. 아래의 논의에서, 지연 스테이지(126)의 게인이 양이라는 것이 명백해질 것이다. 반전 스테이지(122)는 음의 게인을 갖고, 그래서 제1 지연 섹션(104)은 음의 게인을 갖는다. 일부 실시예들에서, 반전 스테이지(122)는 도 1a에 도시된 바와 같은 단일 인버터를 포함할 수 있다. 다른 실시예들에서, 반전 스테이지(122)는 임의의 홀수 개의 인버터들, 일반적으로, 음의 게인을 제공할 수 있는 임의의 적절한 회로를 포함할 수 있다.

[0035]

제2 지연 섹션(106)은 마찬가지로 자신의 입력단과 자신의 출력단 사이에 음의 게인을 특징으로 할 수 있다. 일부 실시예들에서, 제2 지연 섹션(106)은, 예컨대, 지연 스테이지(128)의 단자들(α 및 β)에서 지연 스테이지(128) 양단에(병렬로) 연결된 반전 스테이지(124)를 포함할 수 있다. 제2 지연 섹션(106)의 입력단 및 출력단은 각각 반전 스테이지(124)의 입력 및 출력일 수 있다. 반전 스테이지(124)는 음의 게인을 갖고, 그래서 제2 지연 섹션(106)은 음의 게인을 갖는다. 일부 실시예들에서, 반전 스테이지(124)는 도 1a에 도시된 바와 같이 단일 인버터를 포함할 수 있다. 다른 실시예들에서, 반전 스테이지(124)는 임의의 홀수 개의 인버터들, 그리고 일반적으로 음의 게인을 제공할 수 있는 임의의 적절한 회로를 포함할 수 있다.

[0036]

제1 지연 섹션(104)은, 클록 신호(132)를 생성하기 위해 진동들이 전파될 수 있는 피드백 루프를 정의하도록 제2 지연 섹션(106)을 통해 출력(114)에 연결될 수 있다. 클록 신호(132)의 주파수(fCLOCK)는 일반적으로, 지연 스테이지(128)의 지연(τ1) 및 지연 스테이지(126)의 지연(τ2)의 함수이다. 클록 신호(132)는, 도 1a에 도시된 바와 같이, 제2 반전 스테이지(124)의 출력에 탭 아웃(tapped out)되거나 그렇지 않다면 이 출력에서 생성될 수 있다. 그러나, 클록 신호(132)가 루프 내의 다른 포인트들(114')에서 획득될 수 있음이 이해된다.

[0037]

도 1b를 참조하면, 일부 실시예들에서, 지연 스테이지(128)는 저항기(R) 및 커패시터(C)를 포함하는 RC 네트워크를 포함할 수 있다. 지연 스테이지(128)의 단자(α)는 저항기(R)에 연결될 수 있고, 커패시터(C)는 단자(β)에 연결될 수 있다. 지연 스테이지(128)의 단자(γ)는 저항기(R) 및 커패시터(C)가 연결되는 노드(VX)에 연결될 수 있다. RC 네트워크의 지연(τ1)은 일반적으로, 저항기(R) 및 커패시터(C)의 개개의 엘리먼트 값들을 나타내는 R×C로 정의된 시간 상수(때때로 RC 시간 상수로 지칭됨)의 함수이다. 일부 실시예들에서, 저항기(R) 및 커패시터(C)는 고정 값 엘리먼트들일 수 있다. 따라서, 지연 스테이지(128)는 고정 지연을 제공할 수 있다.

[0038]

노드(VX)는, 발진기 회로(102)의 다른 엘리먼트들(예컨대, 반전 스테이지들(122, 124), 지연 스테이지(126))과 비교하여, 접지 전위에 연결되지 않는다는 것이 주목된다. 오히려, 노드(VX)는 "플로팅(floating)" 노드이고, 이는, 노드(VX)에서의 전위가 발진기 회로(102)의 동작 동안 커패시터(C) 양단의 전압이 변함에 따라 변할 수 있음을 의미한다. 예컨대, 동작 동안에 노드(VX)의 전압은 출력(114)에서의 클록 신호(132)의 사이클의 하나의 절반부에서 공급 전압 위로 그리고 아래로 스윙할 수 있고, 사이클의 다른 절반부에서 접지 전위의 위로 그리고 아래로 스윙할 수 있다. 본 개시내용의 이러한 양상은 아래에 논의된다.

[0039]

도 1a를 참조하면, 일부 실시예들에 따라, 지연 스테이지(126)는 가변(튜닝 가능한, 프로그래밍 가능한) 지연을 가질 수 있다. 지연 스테이지(126)는 지연 스테이지(126)의 지연(τ2)을 선택하거나 그렇지 않다면 설정하기 위해 선택기 입력 신호(112)를 수신할 수 있다. 일부 실시예들에서, 선택기 입력(112)은 디지털 코드일 수 있다. 본 발명에 따라, 선택기 입력(112)은, 전자 회로(10)의 동작 동안에 지연 스테이지(126)에 대해 상이한 지연(τ2)을 선택하기 위해 변경될 수 있다. 예컨대, 선택기 입력(112)은 상이한 디지털 코드들을 지연 스테이지(126)에 제공할 수 있고, 따라서, 지연(τ2)의 온-더-플라이(on-the-fly) 선택을 허용한다.

[0040]

발진기 회로(102)에서의 발진 주파수는 지연들(τ1 및 τ2)에 따라 제어될 수 있다. 지연(τ1)은, 예컨대, 지연 스테이지(128)의 저항기(R) 및 커패시터(C)에 대한 적절한 엘리먼트 값들을 선택함으로써 설계 단계 동안에 결정될 수 있다. τ2의 지연은 적절한 선택기 입력(112)을 지연 스테이지(126)에 제공함으로써 설정될 수 있다. 지연 스테이지(126)의 지연(τ2)이 온-더-플라이로 설정될 수 있기 때문에, 발진기 회로(102)에 의해 생성된 클록 신호(132)의 주파수는 마찬가지로, 즉, 온-더-플라이로 적절한 선택기 입력(112)을 지연 스테이지(126)에 제공함으로써 설정될 수 있다.

[0041]

도 2는 본 개시내용의 일부 실시예들에 따른 제1 지연 섹션(104)의 지연 스테이지(126)에 대한 추가 세부사항들을 도시한다. 일부 실시예들에서, 예컨대, 지연 스테이지(126)는 높은 입력 임피던스 비-반전 입력 버퍼(202) 및 가변 RC 네트워크(204)를 포함할 수 있다. 입력 버퍼(202)에 대한 공급기(도시되지 않음)는, 예컨대, 도 1a에 예시된 바와 같이, 지연 스테이지(126)에 제공되는 VDD 공급기일 수 있다.

[0042]

가변 RC 네트워크(204)는 저항기(R1) 및 가변 커패시터(C1)를 포함할 수 있다. 선택기 입력(112)은 가변 커패시터(C1)에 대한 커패시턴스를 선택하거나 그렇지 않다면 설정하기 위해 가변 커패시터(C1)에 제공될 수 있는 n-비트 신호 버스일 수 있다. 지연 스테이지(126)의 지연(τ2)은, 각각 저항기(R1)와 가변 커패시터(C1)의 값들인 R×C로 정의되는 시간 상수에 기반하여 결정될 수 있다. 따라서, 지연(τ2)은 가변 커패시터(C1)의 커패시턴스 설정에 따라 설정될 수 있다.

[0043]

임의의 적절한 지연 회로가 지연 스테이지(126)를 위해 사용될 수 있다는 것을 당업자는 인식할 것이다. 단지 이 점을 예시하기 위해, 다른 실시예들에서, 예컨대, 지연 스테이지(126)는 고정 커패시터를 충전하기 위해 튜닝 가능한 전류 소스를 이용할 수 있다. 지연 스테이지(126)는 튜닝 가능한 전류 소스 및/또는 튜닝 가능한 커패시터 등을 갖는 전류 결핍 인버터(current starved inverter)를 사용할 수 있다.

[0044]

도 2a는 가변 커패시터(C1)의 추가 세부사항들을 도시한다. 일부 실시예들에 따라, 가변 커패시터(C1)는 n 개의 고정 값 스위칭형 용량성 엘리먼트들(CX)의 세트를 포함할 수 있다. 용량성 엘리먼트들(CX)은 서로 병렬로 연결될 수 있다. 예컨대, 각각의 용량성 엘리먼트(CX)는 저항기(R1)와 대응하는 스위치들(M0-Mn-1)을 통한 접지 전위 연결 사이의 연결을 가질 수 있다. 다른 실시예들에서, 용량성 엘리먼트들(CX)이 병렬 이외에 연결 토폴로지들로 배열될 수 있음이 인지될 것이다.

[0045]

용량성 엘리먼트(CX)는 발진기 회로(102)의 주어진 애플리케이션에 적합한 임의의 반도체 기술을 사용하여 실현될 수 있다. 단지 이 점을 예시하기 위해, 다양한 실시예들에서, 용량성 엘리먼트들(CX)은 PN 접합 커패시터들, MOSFET 게이트 커패시터들, MIM(metal-insulator-metal) 커패시터들, MOM(metal-oxide-metal) 커패시터들 등일 수 있다. 용량성 엘리먼트들(CX)은 동일한 반도체 기술에 기반할 수 있거나, 그들은 상이한 기술들에 기반할 수 있다. 일부 실시예들에서, 용량성 엘리먼트들(CX) 각각은 동일한 커패시턴스를 가질 수 있다. 다른 실시예들에서, 용량성 엘리먼트들(CX)은 상이한 커패시턴스들을 가질 수 있다.

[0046]

용량성 엘리먼트들(CX)은 대응하는 스위치들(M0-Mn-1)의 세트를 통해 접지 전위로 선택적으로 스위칭될 수 있다. 스위치들(M0-Mn-1)은 임의의 적절한 스위칭 디바이스일 수 있다. 일부 실시예들에서, 예컨대, 스위치들(M0-Mn-1)은 도 2a에 도시된 NMOS 트랜지스터들과 같은 반도체 스위치들일 수 있지만, 다른 실시예들에서, 예컨대, NFET들과 같은 다른 트랜지스터 기술들 또는 설계들이 사용될 수 있다. 일부 실시예들에서, 모든 스위치들(M0-Mn-1)은 동일한 기술에 기반할 수 있거나, 또는 그들은 몇몇의 상이한 기술들에 기반할 수 있다. 선택기 입력(112)을 포함하는 n 개의 신호 라인들 각각은 스위치들(M0-Mn-1)의 개개의 스위치에 연결될 수 있다. 예컨대, 도 2a에서, 선택기 입력(112)의 각각의 신호 라인은 스위치들(M0-Mn-1)의 개개의 게이트 단자에 연결된다. 선택기 입력(112)에 대한 입력은 발진기 회로(102) 또는 전자 회로(10)(도 1a)와 연관된 디지털 로직 또는 다른 적절한 회로에 의해 생성될 수 있다.

[0047]

본 개시내용에 따라, 도 2a의 용량성 엘리먼트들(CX)의 노드들은, 노드(VX)와 관련하여 위에서 설명한 바와 같이 플로팅 노드들이 아니다. 오히려, 일부 실시예들에서, 용량성 엘리먼트들(CX)의 노드들은 접지 전위에 전기적으로 연결되거나 그렇지 않으면 이에 레퍼런싱될 수 있다. 다른 실시예들에서, 용량성 엘리먼트들(CX)은 DC 전압, 예컨대, VDD와 같은 공급 전압에 전기적으로 연결되거나 그렇지 않다면 이에 레퍼런싱될 수 있다. 더 일반적으로, 용량성 엘리먼트들(CX)이 임의의 적절한 낮은 임피던스 노드에 전기적으로 연결될 수 있다는 것을 당업자는 인식할 것이다.

[0048]

동작 시에, 선택기 입력(112) 내의 n 개의 신호 라인들 중 임의의 하나 또는 그 초과의 신호 라인들은 자신들의 대응하는 스위치들(M0-Mn-1), 및 따라서 대응하는 용량성 엘리먼트(CX)를 턴 온하도록 어서팅될 수 있다. ON 상태에 있는 스위치(예컨대, M0)는 자신의 대응하는 용량성 엘리먼트(CX)를 RC 네트워크(204)에 연결하고(스위칭 온됨), 반대로 OFF 상태에 있는 스위치는 자신의 대응하는 용량성 엘리먼트(CX)를 RC 네트워크(204)로부터 분리한다(스위칭 오프됨). 용량성 엘리먼트들(CX)이 병렬로 연결되면, 예컨대, 도 2a에 도시된 바와 같이, 가변 커패시터(C1)의 커패시턴스는 스위칭-온된 용량성 엘리먼트들의 합으로서 컴퓨팅될 수 있다. 따라서, 지연 스테이지(126)의 지연(τ2)은 RC 네트워크(204)에서 어떠한 용량성 엘리먼트들이 스위칭 온되는지 또는 스위칭 오프되는지에 따라 설정될 수 있다.

[0049]

일부 실시예들에서, 저항기(R1)는, 도 2a에 도시된 바와 같은 고정 값 엘리먼트일 수 있다. 다른 실시예들(도시되지 않음)에서, 저항기(R1)는 가변 저항기일 수 있고, 커패시터(C1)는 고정 값 엘리먼트일 수 있다. 또 다른 실시예들에서, 저항기(R1)는 가변 저항기일 수 있고, 커패시터(C1)는 가변 커패시터일 수 있다.

[0050]

도 3을 참조하면, 본 개시내용에 따른 일부 실시예들에서, 제1 지연 섹션(104)은 지연 스테이지(126)와 직렬로 연결된 추가 지연 스테이지(326)를 포함할 수 있다. 입력 인버터(322)는 지연 스테이지(126)의 출력에서 생성된 발진들을 추가 지연 스테이지(326)의 입력에 커플링하도록 제공될 수 있고, 다시 말해서, 인버터(322)는 발진들을 계속 유지한다. 출력 인버터(324)는 제1 지연 섹션(104)의 입력단과 출력단 사이에서 음의 순 게인(net negative gain)을 유지하도록 제공될 수 있다. 입력 인버터(322) 및 출력 인버터(324)에 대한 공급기(도시되지 않음)는, 예컨대, 도 1a에 예시된 바와 같이, 지연 스테이지(126)에 제공되는 동일한 VDD 공급기일 수 있다. 일부 실시예들에서, 추가 지연 스테이지(326)는 발진기 회로(102)의 잡음 성능을 향상시킬 수 있다.

[0051]

추가 지연 스테이지(326)는, 저항기(R2) 및 가변 커패시터(C2)를 포함하는 가변 RC 네트워크(304)를 포함할 수 있다. 선택기 입력(312)은, 가변 커패시터(C2)에 대한 커패시턴스를 선택하거나 그렇지 않으면 설정하기 위해 가변 커패시터(C2)에 제공될 수 있는 m-비트 신호 버스를 포함할 수 있다. 추가 지연 스테이지(326)는, 저항기(R2) 및 가변 커패시터(C2)의 개개의 값들인, R×C로 정의된 시간 상수에 기반하여 결정될 수 있는 지연(τ3)을 제공할 수 있다. 따라서, 추가 지연 스테이지(326)에 의해 제공되는 지연(τ3)은 가변 커패시터(C2)의 커패시턴스 설정에 따라 설정될 수 있다.

[0052]

도 3a는 가변 커패시터(C2)의 추가 세부사항들을 도시한다. 일부 실시예들에 따라, 가변 커패시터(C2)는 m 개의 고정 값 스위칭형 용량성 엘리먼트들(Cy)의 세트를 포함할 수 있다. 용량성 엘리먼트들(Cy)은 서로 병렬로 연결될 수 있다. 다시 말해서, 각각의 용량성 엘리먼트(Cy)는 저항기(R2)와 대응하는 스위치(M0-Mm-1)를 통한 접지 전위 연결 사이에 연결될 수 있다. 다른 실시예들에서, 용량성 엘리먼트들(Cy)이 병렬 이외의 연결 토폴로지들로 연결될 수 있다는 것이 인지될 것이다.

[0053]

용량성 엘리먼트(Cy)는, 발진기 회로(102)의 주어진 애플리케이션에 적합한 임의의 반도체 기술을 사용하여 실현될 수 있다. 단지 이 점을 예시하기 위해, 다양한 실시예들에서, 용량성 엘리먼트(Cy)는 PN 접합 커패시터들, MOSFET 게이트 커패시터들, MIM(metal-insulator-metal) 커패시터들, MOM(metal-oxide-metal) 커패시터들 등일 수 있다. 용량성 엘리먼트(Cy)는 동일한 반도체 기술에 기반할 수 있거나, 그들은 상이한 기술들에 기반할 수 있다. 일부 실시예들에서, 용량성 엘리먼트들(Cy) 각각은 동일한 커패시턴스를 가질 수 있다. 다른 실시예들에서, 용량성 엘리먼트들(Cy)은 상이한 커패시턴스들을 가질 수 있다.

[0054]

용량성 엘리먼트들(Cy)은 대응하는 스위치들(M0-Mm-1)의 세트를 통해 접지 전위로 선택적으로 스위칭될 수 있다. 스위치들(M0-Mm-1)은 임의의 적절한 스위칭 디바이스일 수 있다. 일부 실시예들에서, 예컨대, 스위치들(M0-Mm-1)은, 예컨대, 도 3a에 도시된 PNP 트랜지스터들과 같은 반도체 스위치들일 수 있다. 일부 실시예들에서, 모든 스위치들(M0-Mm-1)은 동일한 기술에 기반할 수 있거나, 그들은 상이한 기술들에 기반할 수 있다. 선택기 입력(312)을 포함하는 m 개의 신호 라인들 각각은 스위치들(M0-Mm-1)의 개개의 스위치에 연결될 수 있다. 선택기 입력(312)에 대한 입력은 디지털 로직, 또는 발진기 회로(102) 또는 전자 회로(10)(도 1a)와 연관된 다른 적절한 회로에 의해 생성될 수 있다.

[0055]

본 개시내용에 따라, 도 3a의 용량성 엘리먼트들(Cy)의 노드들은 플로팅하지 않는다. 오히려, 용량성 엘리먼트들(Cy)의 노드들은 접지 전위에 전기적으로 연결될 수 있다. 당업자는, 다른 실시예들에서, 용량성 엘리먼트들(Cy)이 DC 전압(예컨대, 공급 전압 VDD)에 전기적으로 연결될 수 있다는 것을 인지할 것이다. 더 일반적으로, 용량성 엘리먼트들(Cy)은 임의의 적절한 낮은 임피던스 노드에 전기적으로 연결될 수 있다.

[0056]

동작 시에, 선택기 입력(312) 내의 m 개의 신호 라인들 중 임의의 하나 또는 그 초과의 신호 라인들은 자신들의 대응하는 스위치들(M0-Mm-1)을 턴 온하도록 어서팅될 수 있다. ON 상태에 있는 스위치(예컨대, M0)는 자신의 대응하는 용량성 엘리먼트를 RC 네트워크(304)에 연결하고(스위칭 온됨), 반대로 OFF 상태에 있는 스위치는 RC 네트워크(304)로부터 자신의 대응하는 용량성 엘리먼트를 분리한다(스위칭 오프됨). 예컨대, 도 3a에 도시된 바와 같이, 용량성 엘리먼트들(Cy)이 병렬로 연결되면, 가변 커패시터(C2)의 커패시턴스는 스위칭-온된 용량성 엘리먼트들의 합으로서 컴퓨팅될 수 있다. 따라서, 추가 지연 스테이지(326)의 지연(τ3)은, RC 네트워크(304)에서 어떤 용량성 엘리먼트들(Cy)이 스위칭 온되는지 또는 스위칭 오프되는지에 따라 설정될 수 있다.

[0057]

일부 실시예들에서, 저항기(R2)는 도 3a에 도시된 바와 같은 고정 값 엘리먼트일 수 있다. 다른 실시예들(도시되지 않음)에서, 저항기(R2)는 가변 저항기일 수 있고, 커패시터(C2)는 고정 값 엘리먼트일 수 있다. 또 다른 실시예들(도시되지 않음)에서, 저항기(R2)는 가변 저항기일 수 있고, 커패시터(C2)는 가변 커패시터일 수 있다.

[0058]

일부 실시예들에서, 개개의 지연 스테이지들(126, 326)의 선택기 입력들(112, 312)은 동일한 선택 입력을 수신할 수 있고; 예컨대, 동일한 n-비트 코드가 각각의 선택기 입력(112, 312)에 제공될 수 있다. 다른 실시예들에서, 각각의 선택기 입력(112, 312)은 상이한 선택 입력들을 수신할 수 있다.

[0059]

발진기 회로(102)의 발진 주파수는 지연들(τ1, τ2, 및 τ3)에 따라 제어될 수 있다. 위에 설명된 바와 같이, 지연 스테이지(128)의 지연(τ1)은 저항기(R) 및 커패시터(C)에 대해 고정될 수 있다. 지연 스테이지(126)의 지연(τ2)은 지연 스테이지(126)에 대한 선택기 입력(112)을 포함하는 적절한 비트 라인들을 어서팅함으로써 설정될 수 있다. 유사하게, 지연 스테이지(326)의 지연(τ3)은, 선택기 신호(312)를 포함하는 적절한 비트 라인들을 어서팅함으로써 설정될 수 있다. 따라서, 클록 신호(132)의 주파수는 가변 지연들(τ2 및 τ3)의 함수로서 선택될 수 있다.

[0060]

본 개시내용에 따른 일부 실시예들에서, 제1 지연 섹션(104)은 직렬로 연결된 몇몇의 추가 지연 스테이지들을 포함할 수 있다. 도 4a는, 예컨대, 본 개시내용의 일부 실시예들에 따른 발진기 회로(102a)의 개략도이다. 제1 지연 섹션(104)은 지연 스테이지(126) 및 2 개의 추가 지연 스테이지들(426a, 426b)을 포함할 수 있다. 인버터들(422a, 422b)은 지연 스테이지들 사이의 신호를 커플링하도록 제공될 수 있다. 예컨대, 인버터(422a)는 지연 스테이지(126)와 지연 스테이지(422a) 사이에서 신호를 커플링할 수 있고, 마찬가지로 인버터(422b)는 지연 스테이지(422a)와 지연 스테이지(422b) 사이에서 신호를 커플링할 수 있다. 제1 지연 섹션(104)을 포함하는 인버터들(422a, 422b, 122)이 음의 순 게인을 제공한다는 것이 주목된다.

[0061]

도 4b는, 3 개의 추가 지연 스테이지들(426a, 426b, 426c) 및 인버터들(422a, 422b, 422c, 422d)를 갖는 제1 지연 섹션(102)을 포함하는 발진기 회로(102b)의 개략도이다. 인버터들(422a 내지 422c)은 지연 스테이지들(126 및 426-426c) 사이에서 신호를 커플링한다. 인버터(424)가 제1 지연 섹션(104)에 음의 순 게인을 제공한다는 것을 알 수 있다.

기술적 효과와 이점들

[0062]

도 5에 도시된 바와 같은 종래의 RC 발진기 설계는 많은 바람직한 특성들을 갖는다. 이러한 설계들은 일반적으로 공급 전압의 변동들에 둔감하다. 그 설계는 비교적 간단하며, 적은 컴포넌트들을 갖는다. 결과적으로, 이들 RC 발진기들은 저잡음 성능을 달성할 수 있다. 예컨대, 일부 설계들은 이론적인 하한치(low limit)에서 단지 3dB을 초과하는 잡음 레벨들을 달성할 수 있다. 그들의 비교적 간단한 설계들로 인해, RC 발진기들은 IC 칩 상의 더 작은 풋프린트들을 갖는다.

[0063]

본 개시내용은, RC 발진기들의 유용성을 추가로 향상시키기 위해 프로그래밍 가능한 주파수의 성능을 갖는 발진기 회로를 제공한다. 도 5에 도시된 바와 같이, 예컨대, 기본 RC 발진기 설계는 2 개의 인버터들(예컨대, 반전 스테이지들(122, 124)), 및 저항기(R) 및 커패시터(C)를 포함하는 RC 네트워크를 포함한다. RC 네트워크는, RC 발진기의 동작 주파수를 설정하는 지연을 제공한다. 따라서, R 또는 C 중 어느 하나의 엘리먼트 값들을 변경하는 것은 RC 발진기의 동작 주파수에서의 프로그래밍 가능성을 제공하는 역할을 할 수 있다.

[0064]

그러나, R 또는 C를 제조하는 방법은 실용적이지 않을 수 있다. 프로그래밍 가능한 저항기들은 제공하기에 어려울 수 있다. 높은 프로그래밍 가능성은 작은 증분들로 총 R을 수정하는 능력을 요구한다. 이는, 낮은 ON 저항을 갖는 매우 많은 수의 스위치들 및 큰 네트워크의 저항기들을 필요로 한다. 또한, 스위치 양단의 전압은 발진 사이클에 따라 변동할 수 있고, 이로써 스위치 설계를 복잡하게 한다. 가변 저항기를 구축하기 위해 스위칭형 저항기들을 사용하는 것은 실용적이지 않을 수 있다.

[0065]

커패시터(C)가 노드(VX)에서의 거동으로 인해 "플로팅(floating)" 커패시터이기 때문에, 프로그래밍 가능한 커패시터들은 어려울 수 있다. 위에 설명된 바와 같이, 노드(VX)에서의 전압이 출력 사이클의 하나의 절반부에서 공급 전압 위로 그리고 아래로 스윙하고, 사이클의 다른 절반부에서 접지 전위 위로 그리고 아래로 스윙할 수 있기 때문에, 노드(VX)는 플로팅 노드이다. 프로그래밍 가능한 커패시터들은 통상적으로 스위칭형 커패시터 엘리먼트들의 뱅크를 포함한다. 스위치의 소스(또는 드레인)가 노드(VX)에 연결될 때, 스위치의 상태는 사이클의 일부분들 동안에 순방향으로 바이어싱되고, 스위치가 OFF(비-전도) 상태에 있는 것으로 여겨질 때 전도할 수 있다. 플로팅 노드(VX)의 존재는, 가변 지연 RC 네트워크 및 따라서 가변 주파수 발진기 회로를 제공하기 위해 이러한 위치에서 가변 커패시터를 사용하는 데 있어서 난제를 야기한다. 따라서, 가변 커패시터를 구축하기 위해 C를 스위칭형 커패시터들의 뱅크로 대체하는 것은 용이하게 달성되지 않을 수 있다.

[0066]

본 개시내용에 따른 발진기 회로들은 이러한 난제를 극복할 수 있다. 도 1b에 도시된 바와 같이, 지연 스테이지(126)는 RC 네트워크(128)와 별개로 제공될 수 있다. 지연 스테이지(126)는, 지연 스테이지(126)의 동작이 회로에서의 전압 스윙들에 의해 크게 영향을 받지 않도록 접지될 수 있다.

[0067]

위의 설명은 특정 실시예들의 양상들이 어떻게 구현될 수 있는지의 예들과 함께 본 개시내용의 다양한 실시예들을 예시한다. 위의 예들은 유일한 실시예들인 것으로 간주되어선 안 되고, 아래의 청구항들에 의해 정의된 바와 같은 특정 실시예들의 유연성 및 이점들을 예시하도록 제시된다. 위의 개시내용 및 아래의 청구항들에 기반하여, 다른 어레인지먼트들, 실시예들, 구현들 및 등가물들이 청구항들에 의해 정의된 바와 같은 본 개시내용의 범위로부터 벗어남 없이 이용될 수 있다.

Claims (27)

- 프로그래밍 가능한 출력 주파수를 갖는 발진기 회로로서,

출력 신호를 출력하도록 구성된 회로 출력;

입력단 및 출력단을 갖는 제1 지연 섹션 ― 상기 제1 지연 섹션은 상기 입력단과 상기 출력단 간의 음의 게인(negative gain)을 갖고, 상기 제1 지연 섹션은 상기 제1 지연 섹션에 제공되는 제어 신호에 의해 설정된 가변 지연을 제공하도록 구성됨 ― ; 및

상기 제1 지연 섹션과 상기 회로 출력 사이에 직렬로 전기적으로 연결된 제2 지연 섹션 ― 상기 제2 지연 섹션은 입력단 및 출력단을 갖고, 상기 제2 지연 섹션은 상기 입력단과 상기 출력단 간의 음의 게인을 갖고, 상기 제2 지연 섹션은 고정 지연을 제공하도록 구성됨 ― 을 포함하고,

상기 출력 신호는, 상기 제1 지연 섹션으로 인한 지연 및 상기 제2 지연 섹션으로 인한 지연의 함수인 주파수를 갖는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제1 항에 있어서,

상기 제1 지연 섹션은: 저항기 및 가변 커패시터(variable capacitor)를 포함하는 제1 RC 네트워크; 및 상기 제1 RC 네트워크와 직렬로 연결되고 저항기 및 가변 커패시터를 포함하는 제2 RC 네트워크를 포함하고, 상기 제1 지연 섹션의 지연은 상기 제1 RC 네트워크 및 제2 RC 네트워크의 가변 커패시터들의 커패시턴스들에 기반하여 결정되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제2 항에 있어서,

상기 제어 신호는 상기 제1 RC 네트워크의 가변 커패시터의 커패시턴스를 설정하도록 구성되고, 추가 제어 신호가 상기 제2 RC 네트워크의 가변 커패시터의 커패시턴스를 설정하도록 구성되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제1 항에 있어서,

상기 제1 지연 섹션은 저항기 및 가변 커패시터를 포함하는 RC 네트워크를 포함하고, 상기 제1 지연 섹션에 제공되는 상기 제어 신호는 상기 제1 RC 네트워크의 가변 커패시터의 커패시턴스를 설정하도록 구성되고, 상기 제1 지연 섹션의 지연은 상기 가변 커패시터의 커패시턴스에 기반하여 결정되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제1 항에 있어서,

상기 제1 지연 섹션은 복수의 스위칭형 커패시터들을 포함하고, 상기 제어 신호는 상기 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 선택적으로 설정하도록 구성되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제5 항에 있어서,

스위칭형 커패시터가 ON 상태에 있을 때, 상기 스위칭형 커패시터는 DC 전압에 전기적으로 연결된 노드를 갖는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제5 항에 있어서,

스위칭형 커패시터가 ON 상태에 있을 때, 상기 스위칭형 커패시터는 접지 전위(ground potential)에 전기적으로 연결된 노드를 갖는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제5 항에 있어서,

상기 제어 신호는 n-비트 워드인,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제1 항에 있어서,

상기 제2 지연 섹션은, 고정 값 저항성 컴포넌트 및 고정 값 용량성 컴포넌트를 포함하는 RC 네트워크를 포함하는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제9 항에 있어서,

상기 고정 값 용량성 컴포넌트의 적어도 하나의 노드는 상기 발진기 회로의 공급 전압 위로 스윙(swing)하도록 구성되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제10 항에 있어서,

상기 고정 값 용량성 컴포넌트의 적어도 하나의 노드는 접지 전위 아래로 스윙하도록 구성되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 제1 항에 있어서,

상기 제1 지연 섹션은 피드백 루프 내의 상기 제2 지연 섹션을 통해 상기 회로 출력에 전기적으로 연결되는,

프로그래밍 가능한 출력 주파수를 갖는 발진기 회로. - 발진기 회로로서,

출력 신호를 출력하도록 구성된 회로 출력;

입력단 및 출력단을 갖는 제1 지연 섹션 ― 상기 제1 지연 섹션은 상기 입력단과 상기 출력단 간의 음의 게인을 갖고, 상기 제1 지연 섹션은 저항기 및 가변 커패시터를 포함하는 제1 RC 네트워크, 상기 제1 RC 네트워크와 직렬로 연결된 인버터, 및 상기 인버터의 출력에서 직렬로 연결되고 저항기 및 가변 커패시터를 포함하는 제2 RC 네트워크를 포함함 ― ;

상기 제1 지연 섹션의 지연을 설정하기 위해 상기 제1 RC 네트워크의 적어도 가변 커패시터에 제공되는 적어도 하나의 제어 신호; 및

상기 제1 지연 섹션과 상기 회로 출력 사이에 직렬로 전기적으로 연결된 제2 지연 섹션 ― 상기 제2 지연 섹션은 입력단 및 출력단을 갖고, 상기 제2 지연 섹션은 상기 입력단과 상기 출력단 간의 음의 게인을 갖고, 상기 제2 지연 섹션은 고정 지연을 가짐 ― 을 포함하고,

상기 출력 신호는 상기 제1 지연 섹션으로 인한 지연 및 상기 제2 지연 섹션으로 인한 지연의 함수인 주파수를 갖고, 상기 회로 출력은 상기 제2 지연 섹션의 출력단을 포함하는,

발진기 회로. - 제13 항에 있어서,

상기 제1 지연 섹션 내의 상기 제1 RC 네트워크 및 제2 RC 네트워크 내의 가변 커패시터들 각각은 복수의 스위칭형 커패시터들을 포함하고, 프로그래밍 가능한 지연 스테이지에 제공되는 상기 제어 신호는 상기 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 선택적으로 설정하도록 구성된,

발진기 회로. - 제14 항에 있어서,

스위칭형 커패시터가 ON 상태에 있을 때, 상기 스위칭형 커패시터의 노드는 DC 전압에 전기적으로 연결되는,

발진기 회로. - 제14 항에 있어서,

스위칭형 커패시터가 ON 상태에 있을 때, 상기 스위칭형 커패시터의 노드는 접지 전위에 전기적으로 연결되는,

발진기 회로. - 제13 항에 있어서,

상기 제어 신호는 상기 제1 RC 네트워크 내의 상기 가변 커패시터에 제공되고, 상기 회로는 상기 제2 RC 네트워크 내의 상기 가변 커패시터에 제공되는 추가 제어 신호를 더 포함하는,

발진기 회로. - 제13 항에 있어서,

상기 제1 지연 섹션은, 상기 제2 RC 네트워크와 직렬로 연결되고 저항기 및 가변 커패시터를 포함하는 적어도 제3 RC 네트워크를 더 포함하는,

발진기 회로. - 제13 항에 있어서,

상기 제2 지연 섹션은, 고정 값 저항성 컴포넌트 및 고정 값 용량성 컴포넌트를 포함하는 RC 네트워크를 포함하고, 상기 용량성 컴포넌트의 적어도 하나의 노드는 상기 발진기 회로의 공급 전압 위로 스윙하도록 구성되는,

발진기 회로. - 제19 항에 있어서,

상기 용량성 컴포넌트의 적어도 하나의 노드는 접지 전위 아래로 스윙하도록 구성되는,

발진기 회로. - 발진기 회로로서,

제1 인버터 스테이지;

상기 제1 인버터 스테이지의 출력에 전기적으로 연결된 입력을 갖는 제2 인버터 스테이지 ― 상기 제2 인버터 스테이지는 상기 발진기 회로의 출력 신호를 위한 출력을 가짐 ― ;

용량성 엘리먼트에 연결된 저항기 엘리먼트를 포함하는 고정 지연 스테이지 ― 상기 고정 지연 스테이지는 상기 제2 인버터 스테이지의 입력과 출력 사이에 전기적으로 연결됨 ― ; 및

적어도 하나의 가변 지연 스테이지에 제공되는 제어 신호에 의해 설정되는 지연을 갖는 상기 적어도 하나의 가변 지연 스테이지 ― 상기 적어도 하나의 가변 지연 스테이지는, 상기 저항기 엘리먼트 및 커패시터 엘리먼트를 연결하는 상기 고정 지연 스테이지의 노드와 상기 제1 인버터 스테이지의 입력 사이에 전기적으로 연결됨 ― 를 포함하고,

상기 출력 신호의 주파수는 상기 적어도 하나의 가변 지연 스테이지의 지연에 의존하는,

발진기 회로. - 제21 항에 있어서,

상기 적어도 하나의 가변 지연 스테이지와 직렬로 연결되고, 적어도 하나의 추가 가변 지연 스테이지에 제공되는 제어 신호에 의존하는 지연을 갖는 상기 적어도 하나의 추가 가변 지연 스테이지를 더 포함하는,

발진기 회로. - 제21 항에 있어서,

상기 저항기 엘리먼트 및 상기 커패시터 엘리먼트를 연결하는 상기 노드에서의 전압 레벨은 상기 발진기 회로의 공급 전압 위로 그리고 아래로 스윙하고, 상기 발진기 회로의 동작 동안에 접지 전위 위로 그리고 아래로 스윙하는,

발진기 회로. - 제21 항에 있어서,

상기 적어도 하나의 가변 지연 스테이지는 저항기 및 가변 커패시터를 포함하고, 상기 적어도 하나의 가변 지연 스테이지에 제공되는 제어 신호는 상기 가변 커패시터의 커패시턴스를 설정하고, 상기 적어도 하나의 가변 지연 스테이지의 지연은 상기 가변 커패시터의 커패시턴스에 의존하는,

발진기 회로. - 제21 항에 있어서,

상기 적어도 하나의 가변 지연 스테이지는 복수의 스위칭형 커패시터들을 포함하고, 상기 제어 신호는 상기 복수의 스위칭형 커패시터들 각각을 ON 상태 또는 OFF 상태로 설정하는,

발진기 회로. - 제25 항에 있어서,

스위칭형 커패시터가 ON 상태에 있을 때, 상기 스위칭형 커패시터의 노드는 DC 전압 또는 접지 전위에 전기적으로 연결되는,

발진기 회로. - 제21 항에 있어서,

상기 고정 지연 스테이지의 용량성 엘리먼트의 적어도 하나의 노드는 상기 발진기 회로의 공급 전압 위로 그리고 접지 전위 아래로 스윙하도록 구성되는,

발진기 회로.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662302735P | 2016-03-02 | 2016-03-02 | |

| US62/302,735 | 2016-03-02 | ||

| US15/191,350 US9755575B1 (en) | 2016-03-02 | 2016-06-23 | Variable frequency RC oscillator |

| US15/191,350 | 2016-06-23 | ||

| PCT/US2017/017518 WO2017151295A1 (en) | 2016-03-02 | 2017-02-10 | A variable frequency rc oscillator |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180118137A true KR20180118137A (ko) | 2018-10-30 |

Family

ID=59702466

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187025097A KR20180118137A (ko) | 2016-03-02 | 2017-02-10 | 가변 주파수 rc 발진기 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9755575B1 (ko) |

| EP (1) | EP3424147B1 (ko) |

| JP (1) | JP2019511168A (ko) |

| KR (1) | KR20180118137A (ko) |

| CN (1) | CN108781070B (ko) |

| WO (1) | WO2017151295A1 (ko) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10873325B2 (en) * | 2018-10-12 | 2020-12-22 | Texas Instruments Incorporated | Robust noise immune, low-skew, pulse width retainable glitch-filter |

| TWI675280B (zh) * | 2018-10-25 | 2019-10-21 | 新唐科技股份有限公司 | 時脈產生電路及其時脈調整方法 |

| GB2583353B (en) | 2019-04-24 | 2023-04-12 | Pragmatic Printing Ltd | An oscillator with improved frequency stability |

| US11811364B2 (en) | 2021-06-22 | 2023-11-07 | Samsung Electronics Co., Ltd. | Clock integrated circuit including heterogeneous oscillators and apparatus including the clock integrated circuit |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS54181853U (ko) * | 1978-06-12 | 1979-12-22 | ||

| JPS5937611B2 (ja) * | 1979-01-17 | 1984-09-11 | 株式会社日本自動車部品総合研究所 | 抵抗容量型発振回路 |

| JPS60100819A (ja) * | 1984-10-01 | 1985-06-04 | Fujitsu General Ltd | 発振回路 |

| US5519265A (en) | 1993-05-24 | 1996-05-21 | Latham, Ii; Paul W. | Adaptive RC product control in an analog-signal-manipulating circuit |

| US5552748A (en) | 1995-06-07 | 1996-09-03 | American Microsystems, Inc. | Digitally-tuned oscillator including a self-calibrating RC oscillator circuit |

| JP2002271173A (ja) * | 2001-03-13 | 2002-09-20 | Fujitsu Ltd | フィルタ回路、半導体装置、フィルタシステム及び信号周波数制御方法 |

| US6737926B2 (en) * | 2001-08-30 | 2004-05-18 | Micron Technology, Inc. | Method and apparatus for providing clock signals at different locations with minimal clock skew |

| DE10345236B3 (de) * | 2003-09-29 | 2005-03-10 | Infineon Technologies Ag | Verzögerungsregelkreis |

| JP2006261833A (ja) * | 2005-03-15 | 2006-09-28 | Sanyo Electric Co Ltd | リング発振器 |

| US7245519B2 (en) | 2005-08-22 | 2007-07-17 | Freescale Semiconductor, Inc. | Digitally programmable capacitor array |

| JP2007081593A (ja) * | 2005-09-13 | 2007-03-29 | Neuro Solution Corp | 発振器、pll回路および受信機、送信機 |

| KR20070081532A (ko) * | 2006-02-13 | 2007-08-17 | 엘지전자 주식회사 | Rc 발진회로 |

| US7605668B2 (en) | 2006-12-12 | 2009-10-20 | Intel Corporation | Delay stage with controllably variable capacitive load |

| CN102006057B (zh) * | 2009-09-01 | 2013-05-08 | 杭州中科微电子有限公司 | 可编程调整起振条件的低功耗、快速起振晶体振荡器模块 |

| US8222966B2 (en) * | 2010-09-10 | 2012-07-17 | Intel Corporation | System, method and apparatus for an open loop calibrated phase wrapping phase modulator for wideband RF outphasing/polar transmitters |

| JP5807508B2 (ja) * | 2011-10-24 | 2015-11-10 | 株式会社ソシオネクスト | 発振回路を有するマイクロコントローラ |

| US9490823B2 (en) * | 2012-03-19 | 2016-11-08 | Intel Corporation | Self-biased oscillator |

| US9584133B2 (en) | 2012-05-31 | 2017-02-28 | Silicon Laboratories Inc. | Temperature compensated oscillator with improved noise performance |

| CN104935294B (zh) * | 2014-03-20 | 2018-07-20 | 晶宏半导体股份有限公司 | 振荡器 |

-

2016

- 2016-06-23 US US15/191,350 patent/US9755575B1/en active Active

-

2017

- 2017-02-10 CN CN201780014246.6A patent/CN108781070B/zh not_active Expired - Fee Related

- 2017-02-10 JP JP2018545918A patent/JP2019511168A/ja active Pending

- 2017-02-10 WO PCT/US2017/017518 patent/WO2017151295A1/en active Application Filing

- 2017-02-10 KR KR1020187025097A patent/KR20180118137A/ko unknown

- 2017-02-10 EP EP17706649.5A patent/EP3424147B1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN108781070A (zh) | 2018-11-09 |

| EP3424147A1 (en) | 2019-01-09 |

| US20170257065A1 (en) | 2017-09-07 |

| CN108781070B (zh) | 2022-05-17 |

| JP2019511168A (ja) | 2019-04-18 |

| US9755575B1 (en) | 2017-09-05 |

| EP3424147B1 (en) | 2024-07-10 |

| WO2017151295A1 (en) | 2017-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8031011B2 (en) | Digitally controlled oscillators | |

| KR100684050B1 (ko) | 지연회로및그것을이용한발진회로 | |

| JP5229218B2 (ja) | スイッチング容量生成回路、電圧制御発振器、及びlcバンドパスフィルター | |

| US9876489B1 (en) | Method of implementing a differential integrating phase interpolator | |

| EP3424147B1 (en) | A variable frequency rc oscillator | |

| KR20080043978A (ko) | 고해상도 타임투디지털컨버터 | |

| JP2006311561A (ja) | 回路、発振器、リング発振器および複数の発振信号を生成する方法 | |

| WO2002056469A2 (en) | Ring vco based on rc timing | |

| US8466729B2 (en) | Delay cell and digitally controlled oscillator | |

| US6509803B2 (en) | Voltage-controlled oscillator having short synchronous pull-in time | |

| CN111510114B (zh) | 一种时钟发生器电路 | |

| CN115149943A (zh) | 分频电路 | |

| US6861911B2 (en) | Self-regulating voltage controlled oscillator | |

| JP3718932B2 (ja) | 中間位相クロック生成回路 | |

| JP4010328B2 (ja) | 遅延回路 | |

| US20120092078A1 (en) | Variable resistor circuit and oscillation circuit | |

| US6943608B2 (en) | Wide frequency range voltage-controlled oscillators (VCO) | |

| US6965273B2 (en) | Oscillator with improved parameters variation tolerance | |

| JP4238931B2 (ja) | 発振回路 | |

| WO2020059494A1 (ja) | 発振回路および位相同期回路 | |

| JP2006060874A (ja) | 発振回路 | |

| KR20230029512A (ko) | 2상 클록 생성 회로 | |

| KR0139906B1 (ko) | 신호지연회로 및 그 회로를 이용한 클럭신호발생회로 |