KR20160013161A - 확산-길이 보호된 회로 및 설계 방법 - Google Patents

확산-길이 보호된 회로 및 설계 방법 Download PDFInfo

- Publication number

- KR20160013161A KR20160013161A KR1020157036436A KR20157036436A KR20160013161A KR 20160013161 A KR20160013161 A KR 20160013161A KR 1020157036436 A KR1020157036436 A KR 1020157036436A KR 20157036436 A KR20157036436 A KR 20157036436A KR 20160013161 A KR20160013161 A KR 20160013161A

- Authority

- KR

- South Korea

- Prior art keywords

- circuit

- pulse

- gap

- transistors

- circuit design

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/037—Bistable circuits

-

- G06F17/5068—

-

- G06F17/5081—

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/398—Design verification or optimisation, e.g. using design rule check [DRC], layout versus schematics [LVS] or finite element methods [FEM]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/01—Details

- H03K3/012—Modifications of generator to improve response time or to decrease power consumption

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Manipulation Of Pulses (AREA)

Abstract

회로는 펄스-래치 회로를 포함한다. 펄스-래치 회로는 제 1 복수의 트랜지스터들을 포함한다. 제 1 복수의 트랜지스터들 중 하나 또는 둘 이상은 LOD(length-of-diffusion) 보호된다.

Description

[0001]

본 개시내용은 일반적으로 회로들 및 회로들을 설계하는 방법들에 관한 것이다.

[0002]

기술의 발전들은 더 작고 더 강력한 전자 디바이스들을 초래했다. 예컨대, 무선 전화들, PDA(personal digital assistant)들, 및 페이징 디바이스들과 같은 다양한 모바일 디바이스들이 현재 존재하고 있다. 모바일 디바이스들은 소형이며, 경량이어서 사용자들이 용이하게 휴대할 수 있다. 무선 전화들, 이를테면, 셀룰러 전화들 및 인터넷 프로토콜(IP) 전화들은 무선 네트워크들을 통해 음성 및 데이터 패킷들을 통신할 수 있다. 또한, 많은 이러한 무선 전화들은 거기에 통합되는 다른 유형들의 디바이스들을 포함한다. 예컨대, 무선 전화는 또한 디지털 스틸 카메라, 디지털 비디오 카메라, 디지털 레코더, 및 오디오 파일 플레이어를 포함할 수 있다. 또한, 이러한 무선 전화들은 인터넷에 액세스하기 위해 이용될 수 있는 웹 브라우저 애플리케이션과 같은 소프트웨어 애플리케이션들을 포함하는 실행가능 명령들을 프로세싱할 수 있다. 이와 같이, 무선 전화들 및 다른 전자 디바이스들은 중요한 컴퓨팅 능력들을 포함할 수 있다.

[0003]

집적 회로들은 점점 더 많은 수들의 트랜지스터들을 포함한다. 예컨대, 반도체 프로세스들이 스케일 다운됨에 따라, 특정 반도체 영역에 더 많은 트랜지스터들이 제조될 수 있으며, 이는 더 작고 더 강력한 전자 디바이스들을 가능하게 할 수 있다. 그러나, 일부 회로 특징들은 반도체 프로세스들을 이용해 선형으로 "스케일링"되지 않을 수 있다. 예컨대, 트랜지스터들 사이의 물리적 특징들이 상이해지는 것에 의해 야기되는 성능 변동(performance variation)들은 감소된 크기의 반도체 프로세스에 대해, 특히, "매칭된" 트랜지스터들 및/또는 정확한 시간 인터벌들을 이용하여 동작하도록 설계된 회로 컴포넌트들에 대해 더 확연해질 수 있다. 이러한 변동들은 전자 디바이스들과 연관된 동작을 변경할 수 있고(예컨대, 드라이브 전류 저하), 그리고 반도체 디바이스의 레이아웃을 발생시키는 것(예컨대, 특정 영역을 위해 많은 수의 트랜지스터들을 포함하면서 회로 설계 파리미터들에 따르는 레이아웃을 발생시키는 것)에 대해 중요한 난제들을 만들 수 있다.

[0004]

본 개시내용에 따른 집적 회로는 브리징(bridge)된(예컨대, 연장된) OD(oxide-on-diffusion) "섬(island)들"을 포함할 수 있다. OD 구역의 에지들에 형성된 트랜지스터들이 OD 구역의 중심의 트랜지스터들과 비교하여 상이한 또는 "미스매칭된" 성능 특징들(예컨대, 임계 전압 및/또는 드레인 전류)을 나타낼 수 있기 때문에, 연속적인 OD 구역을 형성하기 위해 다수의 OD 구역들 또는 "섬들"을 브리징하는 것은 트랜지스터들 사이의 성능 유사성을 증가시킬 수 있다. 예컨대, OD 구역의 단부들의 STI(shallow trench isolation) 에지들은 중심 트랜지스터들보다 에지 트랜지스터들에 더 많이 기계적으로 스트레스를 가할 수 있어서, (예컨대, LOD(length-of-diffusion) 영향으로 인해) 종래의 디바이스들에서 성능 미스매치를 잠재적으로 야기한다.

[0005]

집적 회로의 OD 구역들을 브리징함으로써, 트랜지스터들 사이의 증가된 성능 유사성이 달성될 수 있으며, 이는 집적 회로의 동작을 개선할 수 있다. 예시하자면, 짧은 펄스 폭(예컨대, 대략 200 피코초(picoseconds))에 기초하여 동작하도록 설계된 펄스-래치 회로(pulsed-latch circuit)에 있어서, OD 구역의 에지 및 중심 구역들의 트랜지스터들 사이의 성능 차이들에 의해 야기되는 "미스매치"가 회피될 수 있다. 따라서, 펄스-래치 회로는 변동 제어, 더 높은 드라이브 전류/더 양호한 성능, 더 높은 수율, 더 정확한 펄스 폭 제어, 펄스 폭의 더 엄격한 분배, 및/또는 다른 바람직한 성능 특징들을 나타낼 수 있다.

[0006]

OD 구역을 연장시키는 것은 더미 디바이스(dummy device)를 생성하는 것을 포함할 수 있다. 예컨대, OD 구역을 연장시키는 것은 OD 구역이 pSi(poly-silicon) 구역에 연결되는 것을 야기하여, 적어도 하나의 "더미(dummy)" 트랜지스터를 생성할 수 있다. 더미 트랜지스터는 게이트 개방되고(예컨대, 소스-드레인 단락되고) 그리고 전력 단자 또는 접지 단자에 커플링되어, 더미 트랜지스터가 (예컨대, 신호의 특정 주파수들을 접지에 대해 분로(shunting)하거나 또는 "디커플링(decoupling)"함으로써) "디커플링 커패시터(decoupling capacitor)"로서 기능하도록 야기할 수 있으며, 이는 유리할 수 있다. 대안적인 실시예들에 따르면, 더미 트랜지스터는 게이트 폐쇄될 수 있고, 다른 전기 노드들에 연결될 수 있다.

[0007]

특정 실시예에서, 회로는 펄스-래치 회로를 포함한다. 펄스-래치 회로는 제 1 복수의 트랜지스터들을 포함한다. 제 1 복수의 트랜지스터들 중 하나 또는 둘 이상은 LOD(length-of-diffusion) 보호된다.

[0008]

다른 특정 실시예에서, 방법은, 회로 설계에서 그리고 프로세서에 의해, 제 1 OD(oxide-on-diffusion) 구역과 제 2 OD 구역 사이의 갭을 식별하는 단계를 포함한다. 갭을 식별하는 것에 응답하여, 프로세서는 수정된 회로 설계(modified circuit design)를 발생시키기 위해 더미 디바이스를 회로 설계에 부가함으로써 갭을 브리징한다.

[0009]

다른 특정 실시예에서, 방법은 복수의 트랜지스터들을 포함하는 펄스-래치 회로에서 출력 신호를 발생시키는 단계를 포함한다. 복수의 트랜지스터들 각각은 LOD(length-of-diffusion) 보호된다.

[0010]

다른 특정 실시예에서, 컴퓨터-판독가능 저장 매체는, 동작들을 수행하도록 프로세서에 의해 실행가능한 명령들을 저장하고, 동작들은, 회로 설계에서 그리고 프로세서에 의해, 제 1 OD(oxide-on-diffusion) 구역과 제 2 OD 구역 사이의 갭을 식별하는 것을 포함한다. 동작들은, 갭을 식별하는 것에 응답하여 그리고 프로세서에 의해, 수정된 회로 설계를 발생시키기 위해 더미 디바이스를 회로 설계에 부가함으로써 갭을 브리징하는 것을 더 포함한다.

[0011]

다른 특정 실시예에서, 장치는 클록 신호에 응답하여 펄스 신호를 발생시키기 위한 수단을 포함한다. 장치는 펄스 신호에 응답하여 출력 신호를 발생시키기 위한 수단을 더 포함한다. 출력 신호를 발생시키기 위한 수단은 각각이 LOD(length-of-diffusion) 보호되는 다수의 트랜지스터들을 포함한다.

[0012]

개시된 실시예들 중 적어도 하나에 의해 제공되는 하나의 특정한 이점은, 집적 회로의 트랜지스터들 사이의 증가된 성능 유사성이다. 예컨대, 짧은 펄스 폭(예컨대, 대략 200 피코초)에 기초하여 동작하도록 설계된 펄스-래치 회로에 대해, OD 구역의 에지 및 중심 구역들의 트랜지스터들 사이의 성능 차이들에 의해 야기되는 "미스매치"가 회피될 수 있다. 따라서, 펄스-래치 회로는 변동 제어, 더 높은 드라이브 전류/더 양호한 성능, 더 높은 수율, 더 정확한 펄스 폭 제어, 펄스 폭의 더 엄격한 분배, 및/또는 다른 바람직한 성능 특징들을 나타낼 수 있다. 본 개시내용의 다른 양상들, 이점들, 및 특징들은, 다음의 부분들: 도면의 간단한 설명, 발명을 실시하기 위한 구체적인 내용, 및 청구범위를 포함하는 전체 출원의 리뷰 후에 명백해질 것이다.

[0013]

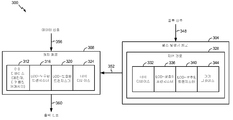

도 1은 회로 설계의 수정의 특정 실시예를 예시하는 도면이고;

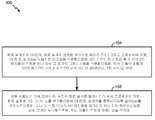

[0014] 도 2는 회로 설계의 수정의 다른 특정 실시예를 예시하는 도면이고;

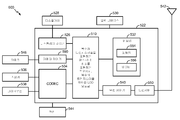

[0015] 도 3은 펄스-래치 회로의 특정 실시예를 예시하는 도면이고;

[0016] 도 4a는 도 3의 펄스-래치 회로와 같은 회로를 설계하는 방법의 특정 예시적 실시예를 도시하는 흐름도이고;

[0017] 도 4b는 도 3의 펄스-래치 회로를 동작시키는 방법의 특정 예시적 실시예를 도시하는 흐름도이고;

[0018] 도 5는 도 3의 펄스-래치 회로를 포함하는 모바일 디바이스의 특정 예시적 실시예의 블록도이고; 그리고

[0019] 도 6은 도 3의 펄스-래치 회로를 포함하는 전자 디바이스들을 제조하기 위한 제조 프로세스의 특정 예시적 실시예의 데이터 흐름도이다.

[0014] 도 2는 회로 설계의 수정의 다른 특정 실시예를 예시하는 도면이고;

[0015] 도 3은 펄스-래치 회로의 특정 실시예를 예시하는 도면이고;

[0016] 도 4a는 도 3의 펄스-래치 회로와 같은 회로를 설계하는 방법의 특정 예시적 실시예를 도시하는 흐름도이고;

[0017] 도 4b는 도 3의 펄스-래치 회로를 동작시키는 방법의 특정 예시적 실시예를 도시하는 흐름도이고;

[0018] 도 5는 도 3의 펄스-래치 회로를 포함하는 모바일 디바이스의 특정 예시적 실시예의 블록도이고; 그리고

[0019] 도 6은 도 3의 펄스-래치 회로를 포함하는 전자 디바이스들을 제조하기 위한 제조 프로세스의 특정 예시적 실시예의 데이터 흐름도이다.

[0020]

도 1을 참조하면, 회로 설계(108)를 발생시키기 위한 시스템이 도시되고 일반적으로 100으로 지정된다. 수정된 회로 설계(154)를 발생시키기 위한 회로 설계(108)의 수정 이후의 시스템이 도시되고 일반적으로 150으로 지정된다. 회로 설계(108)는 컴퓨터(104)를 이용하여 발생된다. 도 1에 도시된 바와 같이, 컴퓨터(104)는 메모리(112)에 커플링된 프로세서(116)를 포함한다. 메모리(112)는 프로세서(116)에 의해 실행가능한 명령들(120)을 저장할 수 있다. 특정 실시예에서, 회로 설계(108)는 컴퓨터(104)의 디스플레이 디바이스에 디스플레이된다.

[0021]

회로 설계(108)는 제 1 OD(oxide-on-diffusion) 구역(124)(예컨대, 연속적인 확산 및 트랜지스터 게이트 산화물 구역) 및 제 2 OD 구역(128)을 포함할 수 있다. OD 구역들(124, 128)은 회로 설계(108)에 기초하여 제조될 집적 회로의 하나 또는 둘 이상의 트랜지스터들에 대응할 수 있다. 예컨대, 회로 설계(108)는 집적 회로의 적어도 일부의 제 1 레이아웃에 대응할 수 있고, 집적 회로를 설계하는 레이아웃 페이즈(layout phase) 동안 발생될 수 있다.

[0022]

도 1에 도시된 바와 같이, 회로 설계(108)의 갭(144)은 제 1 OD 구역(124)과 제 2 OD 구역(128)을 분리시킨다. 특정 실시예에서, 명령들(120)은 OD 구역들(124, 128) 사이의 갭(144)을 식별하도록 프로세서(116)에 의해 실행가능하다. 예컨대, 명령들(120)은 OD 구역들(124, 128)을 분리시키는 갭(144)과 같은, 회로 설계(108)의 OD 구역들 사이의 갭들을 식별하기 위해 회로 설계(108)와 연관된 데이터를 분석하도록 프로세서(116)에 의해 실행가능할 수 있다. 명령들(120)은 수정된 회로 설계(154)를 발생시키기 위해 갭(144)을 브리징하도록 프로세서(116)에 의해 실행가능할 수 있다. 수정된 회로 설계(154)는 집적 회로의 적어도 일부의 제 2 레이아웃에 대응할 수 있고 집적 회로를 설계하는 레이아웃 페이즈 동안 발생될 수 있다.

[0023]

수정된 회로 설계(154)에서, 브리징된(예컨대, 연속적인) OD 구역(158)을 형성하기 위해 갭(144)이 브리징된다. 브리징된 OD 구역(158)은 제 1 OD 구역(124) 및 제 2 OD 구역(128)을 포함한다. 브리징된 OD 구역(158)은 갭(144)을 브리징하는 더미 디바이스(162)를 더 포함한다(예컨대, 수정된 회로 설계(154)를 발생시키기 위해 더미 디바이스(162)가 회로 설계(108)에 부가되었음).

[0024]

아래에서 추가로 설명되는 바와 같이, 수정된 회로 설계(154)를 발생시키기 위해 갭(144)을 브리징하는 것은, 수정된 회로 설계(154)에 기초하여 발생되는 집적 회로의 성능을 개선할 수 있다. 예컨대, 갭(144)을 제거함으로써, OD 구역들(124, 128) 중 하나 또는 양쪽 모두의 "에지 구역" 상에 있는 트랜지스터들의 성능이, OD 구역들(124, 128) 중 하나 또는 양쪽 모두의 에지 구역 상에 있지 않은 트랜지스터들 또는 중심 구역에 있는 트랜지스터들과 비교하여 개선될 수 있다. 예컨대, STI(shallow trench isolation) 구역에 가까운 트랜지스터들(예컨대, "에지" 트랜지스터들)은, 도 2와 관련하여 추가로 설명되는 바와 같이, STI 구역에 인접하지 않은 트랜지스터들(예컨대, 비-에지(non-edge) 트랜지스터들))과 비교하여 더 많은 물리적 스트레스를 경험할 수 있다. 갭(144)을 브리징하는 것은 LOD(length-of-diffusion) 영향과 연관된 물리적 스트레스를 완화시키거나 감소시킬 수 있어서, 회로 성능을 향상시킨다.

[0025]

도 2를 참조하면, 회로 설계의 특정 예시적 실시예가 도시되고 일반적으로 200으로 지정되며, 수정된 회로 설계의 특정 예시적 실시예가 도시되고 일반적으로 250으로 지정된다. 회로 설계들(200, 250)은 도 1의 회로 설계들(100, 150)에 각각 대응할 수 있고, 도 1의 컴퓨터(104)에 의해 발생될 수 있다.

[0026]

회로 설계들(200, 250)은 각각 기판(204), 제 1 OD 구역(208), 제 2 OD 구역(212) 및 복수의 pSi(poly-silicon) 구역들을 포함한다. OD 구역들(208, 212)은 도 1의 OD 구역들(124, 128)에 대응할 수 있다. 도 2의 예에서, 복수의 pSi 구역들은 제 1 pSi 구역(216), 제 2 pSi 구역(220), 제 3 pSi 구역(224), 및 제 4 pSi 구역(228)을 포함한다. 회로 설계들(200, 250)은 STI(shallow trench isolation) 구역(206)을 더 포함한다. STI 구역(206)은 STI 에지(210)를 갖는다(즉, STI 구역(206)은 STI 에지(210)에 의해 제 1 OD 구역(208)으로부터 분리됨). 대안적으로, STI 구역(206) 대신에, 필드 산화물 구역이 제 1 OD 구역(208)에 인접할 수 있다(도 2에 도시되지 않음).

[0027]

도 2의 예에서, 회로 설계(200)는 제 1 OD 구역(208)과 제 2 OD 구역(212)을 분리시키는 갭(244)을 포함한다. 갭(244)은 도 1의 갭(144)에 대응할 수 있다. 도 2에 도시된 바와 같이, 제 1 OD 에지(236) 및 제 2 OD 에지(240)는 갭(244)을 정의한다. 특정 실시예에서, 갭(244)은 OD 구역들(208, 212)을 분리시키는 STI 구역과 같은 STI 구역에 대응한다.

[0028]

복수의 pSi 구역들(216, 220, 224, 228) 각각은, 각각의 pSi 구역의 에지와 OD 구역들(208, 212) 중 하나의 OD 구역의 에지 사이의 각각의 길이와 연관될 수 있다. 예컨대, 도 2에서, 제 1 pSi 구역(216)은 길이(sa0)와 연관된다. 길이(sa0)는 pSi 구역(216)과 STI 에지(210) 사이의 거리를 표시한다. 부가적인 예로서, pSi 구역들(220, 224)은 pSi 구역들(220, 224)과 OD 에지들(236, 240) 사이의 거리들을 각각 표시하는 각각의 길이들(sa1 및 sa2)과 연관될 수 있다. 특정 실시예에서, 거리(sa0)는, pSi 구역(216)을 포함하는 트랜지스터를 제조하기 위해 이용되는 제조 기술과 연관된 최소 길이와 같은 임계 길이보다 더 크다. 그러므로, 본원에서 이용되는 바와 같이, pSi 구역(216)을 포함하는 트랜지스터는, 도 3과 관련하여 추가로 설명되는 바와 같이 "LOD 보호된다(LOD protected)". 부가하여, 아래에서 추가로 설명되는 바와 같이, 갭(244)은 길이들(sa1, sa2)을 연장시키기 위해(예컨대, pSi 구역들(220, 224)을 포함하는 트랜지스터들을 제조하기 위해 이용되는 제조 기술에 의해 정의된 최소 길이들보다 더 크도록 길이들(sa1, sa2)을 연장시키기 위해), 수정된 회로 설계(250)에서 브리징될 수 있다. 본원에서 이용되는 바와 같이, "에지"는, 에지에 의해 정의된 2개의 부분들을 연결하기 위해(예컨대, 에지들(236, 240)을 제거하도록 OD 구역들(208, 212)을 연결하기 위해) 재료(예컨대, 더미 디바이스(248))를 부가함으로써 "제거"된다.

[0029]

예컨대, 수정된 회로 설계(250)에서는, 더미 디바이스(248)가 OD 구역들(208, 212) 사이에 부가된다. 더미 디바이스(248)는 더미 트랜지스터에 대응할 수 있다. 예컨대, 더미 디바이스(248)는 더미 트랜지스터의 게이트에 대응하는 pSi 재료를 포함할 수 있다. 따라서, pSi 재료로 OD 구역들(208, 212)을 브리징함으로써, 더미 트랜지스터가 형성될 수 있다. 부가하여, 더미 디바이스(248)를 부가함으로써 길이들(sa1, sa2) 각각이 연장(lengthen)되는데, 그 이유는, 예컨대, 더미 디바이스(248)를 부가하는 것은 갭(244)을 제거하고 그에 따라 회로 설계(200)로부터 OD 에지들(236, 240)을 제거하여 수정된 회로 설계(250)를 발생시키기 때문이다. 본원에서 이용되는 바와 같이, "에지"는, 에지에 의해 정의된 2개의 부분들을 연결하기 위해(예컨대, 에지들(236, 240)을 제거하도록 OD 구역들(208, 212)을 연결하기 위해) 재료(예컨대, 더미 디바이스(248))를 부가함으로써 "제거"될 수 있다.

[0030]

더미 디바이스(248)를 부가함으로써, OD 에지들(236, 240)에 가까웠을 pSi 구역들(220, 224)을 이용하여 형성된 트랜지스터들은, 수정된 회로 설계(250)에서 에지에 인접하지 않는다(즉, 비-인접함)(예컨대, 대신에 더미 디바이스(248)에 가까움). 따라서, 에지 디바이스들이 비-에지(non-edge) 디바이스들과 상이한 성능을 나타낼 수 있기 때문에, 더미 디바이스(248)를 부가하는 것은, 회로 설계(200)에 기초하여 제조되는 집적 회로에 비해 수정된 회로 설계(250)에 기초하여 제조되는 집적 회로에서 트랜지스터들 사이의 균일성을 개선할 수 있다.

[0031]

도 3을 참조하면, 펄스-래치 회로의 특정 예시적 실시예가 도시되고 일반적으로 300으로 지정된다. 도 3에서 도시된 바와 같이, 펄스-래치 회로(300)는 펄스 발생기 회로(304) 및 래치 회로(308)를 포함한다.

[0032]

래치 회로(308)는 복수의 LOD 보호된 트랜지스터들을 포함한다. 예컨대, 래치 회로(308)는 제 1 LOD 보호된 트랜지스터(316) 및 제 2 LOD 보호된 트랜지스터(320)를 포함한다. 본원에서 이용되는 바와 같이, "LOD 보호된(LOD protected)"은 트랜지스터를 제조하기 위해 이용되는 제조 기술과 연관된(예컨대, 제조 기술에 의해 정의된) 최소 길이와 같은 임계 길이보다 더 큰 길이(sa)(도 2와 관련하여 설명되는 바와 같음)를 가진 트랜지스터를 표시할 수 있다. 래치 회로(308)는 제 1 더미 디바이스(312) 및 제 2 더미 디바이스(324)와 같은 하나 또는 둘 이상의 더미 디바이스들을 더 포함한다. 더미 디바이스들(312, 324) 중 하나 또는 둘 이상은 도 1의 더미 디바이스(162), 도 2의 더미 디바이스(248), 또는 이들의 조합에 대응할 수 있다.

[0033]

펄스 발생기 회로(304)는 하나 또는 둘 이상의 LOD 보호된 트랜지스터들 및 하나 또는 둘 이상의 더미 디바이스들을 포함하는 지연 경로(328)를 포함할 수 있다. 도 3의 특정 예에서, 지연 경로(328)는 제 3 더미 디바이스(332), 제 3 LOD 보호된 트랜지스터(336), 제 4 LOD 보호된 트랜지스터(340), 및 제 4 더미 디바이스(344)를 포함한다. 더미 디바이스들(332, 344) 중 하나 또는 둘 이상은 도 1의 더미 디바이스(162), 도 2의 더미 디바이스(248), 또는 이들의 조합에 대응할 수 있다. 펄스-래치 회로(300)에서 이용되는 특정한 수의 트랜지스터들 및 더미 디바이스들은 특정 애플리케이션에 좌우될 수 있고, 도 3의 특정 예에서 도시된 것과 상이할 수 있음이 인식되어야 한다.

[0034]

동작에서, 펄스 발생기 회로(304)는 클록 신호(348)에 응답하여 펄스 신호(352)를 발생시킨다. 래치 회로(308)는 펄스 발생기 회로(304)에 의해 발생된 펄스 신호(352)에 응답하고 데이터 신호(356)에 추가로 응답한다. 예컨대, 래치 회로(308)는 펄스 신호(352)에 의해 결정된 시간들에서 데이터 신호(356)를 샘플링할 수 있다. 펄스 신호(352)에 따라 결정된 시간들에서 데이터 신호(356)를 샘플링함으로써, 래치 회로(308)는 출력 신호(360)(예컨대, 대략 200 피코초(ps)의 펄스 폭을 가진 펄스)를 발생시킬 수 있다.

[0035]

펄스-래치 회로(300)가 정확한 타이밍 파라미터들을 요구할 수 있기 때문에, 펄스-래치 회로(300)는 펄스-래치 회로(300)를 제조하기 위해 이용되는 프로세스와 연관된 프로세스 변동들에 민감할 수 있다. 예컨대, 더미 디바이스들(312, 324, 332, 344)을 포함함으로써 에지 디바이스가 도 2와 관련하여 설명된 바와 같은 비-에지 디바이스와 비교하여 상이한 성능을 나타낼 수 있기 때문에, LOD 보호된 트랜지스터들(316, 320, 336, 340) 중 어느 것도 에지, 이를테면, STI(shallow trench isolation) 구역의 에지(예컨대, 도 2의 STI 구역(206)의 STI 에지(210))에 인접하지 않음을 보장함으로써, 펄스-래치 회로(300)의 성능이 개선될 수 있다. 또한, LOD 보호된 트랜지스터들(316, 320, 336, 340) 각각의 길이(sa)가, LOD 보호된 트랜지스터들(316, 320, 336, 340)을 제조하기 위해 이용되는 제조 기술에 의해 정의된 최소 길이보다 더 크다는 것을 보장함으로써, LOD 보호된 트랜지스터들(316, 320, 336, 340) 사이의 프로세스 변동들은, 트랜지스터들이 최소 길이에 따라 제조되는 디바이스들과 비교하여 펄스-래치 회로(300)의 성능에 대해 감소된 영향을 가질 수 있다(예컨대, LOD 보호된 트랜지스터들은 더 균일하게 "매칭"될 수 있음).

[0036]

도 4a를 참조하면, 방법의 특정 예시적 실시예가 도시되고 일반적으로 400으로 지정된다. 방법(400)은 404에서, 회로 설계에서 그리고 프로세서에 의해, 제 1 OD(oxide on-diffusion) 구역과 제 2 OD 구역 사이의 갭을 식별하는 단계를 포함한다. 회로 설계는 도 1의 회로 설계(108), 도 2의 회로 설계(200), 또는 이들의 조합에 대응할 수 있다. 프로세서는 도 1의 프로세서(116)에 대응할 수 있다.

[0037]

특정 예시적 실시예에서, 갭은 회로 설계와 연관된 레이아웃 페이즈 동안 식별된다. 갭은 도 1의 갭(144), 도 2의 STI 구역(206), 도 2의 갭(244) 또는 이들의 조합에 대응할 수 있다. 특정 예시적 실시예에서, 갭을 식별하는 단계는 STI 구역의 STI 에지에 가까운 하나 또는 둘 이상의 디바이스들을 식별하는 단계를 포함한다. 예컨대, 도 2의 pSi 구역들(216, 220, 224)이 각각 에지들(210, 236, 240)에 가깝기 때문에, 프로세서는 갭(예컨대, 갭(144), STI 구역(206), 또는 갭(244))이, pSi 구역들(216, 220, 224)을 포함하는 제 1, 제 2, 및 제 3 디바이스들(예컨대, 제 1, 제 2, 및 제 3 트랜지스터들)에 각각 인접함을 결정할 수 있다. 특정 예시적 실시예에서, 프로세서는, 길이(sa)(예컨대, 길이들(sa0, sa1, 및 sa2) 중 하나 또는 둘 이상)가 임계치 미만임을(예컨대, 제조 프로세스와 연관된 최소 길이와 동등함을) 결정함으로써, 갭을 식별한다. 대안적으로 또는 부가하여, 프로세서는 각각의 에지에 각각 가까운 2개의 디바이스들을 식별함으로써, 이를테면, 도 2와 관련하여 설명된 바와 같이, OD 에지들(236, 240)에 각각 인접한 pSi 구역들(220, 224)을 포함한 디바이스들(예컨대, 트랜지스터들)을 식별함으로써 갭을 식별할 수 있다.

[0038]

갭을 식별하는 것에 응답하여, 방법(400)은 408에서, 수정된 회로 설계를 발생시키기 위해 프로세서에 의해 더미 디바이스를 회로 설계에 부가함으로써 갭을 브리징하는 단계를 더 포함한다. 수정된 회로 설계는 도 1의 수정된 회로 설계(154), 도 2의 수정된 회로 설계(250), 또는 이들의 조합에 대응할 수 있다. 특정 실시예에서, 프로세서는, 임계치를 충족시키기 위해 길이(sa)를 증가시킴으로써, STI 에지를 제거하기 위해 더미 디바이스를 회로 설계에 부가함으로써, 또는 이들의 조합에 의해 갭을 브리징한다. 예컨대, 프로세서는 도 2와 관련하여 설명된 바와 같이 길이(sa0)를 연장시킬 수 있다. 대안적으로 또는 부가하여, 프로세서는 도 2의 에지들(236, 240)을 제거하기 위해(예컨대, 길이들(sa1 및 sa2)을 연장시키기 위해) 더미 디바이스(248)를 부가할 수 있다. 더미 디바이스는 디커플링 커패시터로서 구성된 더미 트랜지스터와 같은 더미 트랜지스터에 대응할 수 있다. 예컨대, 더미 트랜지스터는 게이트 개방되고(예컨대, 소스-드레인 단락되고) 그리고 전력 단자에 또는 접지 단자에 커플링되어, 더미 트랜지스터가 신호의 특정 주파수들을 접지에 대해 분로(shunting)하거나 또는 "디커플링"함으로써 "디커플링 커패시터(decoupling capacitor)"로서 기능하도록 야기할 수 있다.

[0039]

방법(400)은 수정된 회로 설계에 따라 집적 회로를 제조하는 단계(도 4a에 도시되지 않음)를 더 포함할 수 있다. 예컨대, 집적 회로는 도 3의 펄스-래치 회로(300)를 포함할 수 있다. 집적 회로들의 제조는 도 6과 관련하여 추가로 설명된다.

[0040]

도 4a의 방법(400)에 따라 수정된 회로 설계들을 발생시킴으로써, 집적 회로의 전력 소비 및 성능이 개선될 수 있다. 예컨대, 임계치 ― 그 임계치까지 길이(sa)가 연장됨 ― 는 특정 애플리케이션에 기초하여(예컨대, 특정 애플리케이션을 위해 이용되는 제조 프로세스와 연관된 프로세스 변동들에 대한 민감성과 같은 회로 파라미터들에 기초하여) 선택될 수 있다. 또한, 방법(400)은 OD 구역들 사이의 갭들을 "자동으로" 식별하기 위해 회로 파라미터들을 분석함으로써 그리고 수정된 회로 설계들을 발생시키기 위해 이러한 갭들을 자동으로 브리징함으로써, 회로 설계 데이터의 자동화된 프로세싱을 가능하게 할 수 있다.

[0041]

도 4b를 참조하면, 도 3의 펄스-래치 회로를 동작시키는 방법의 특정 예시적 실시예를 도시하는 흐름도가 도시되고 일반적으로 450으로 지정된다. 454에서, 클록 신호(348)가 펄스-래치 회로(300)의 펄스 발생기 회로(304)에서 수신된다. 펄스-래치 회로(300)는 복수의 트랜지스터들(예컨대, LOD 보호된 트랜지스터들(316, 320, 336, 340))을 포함하고, 복수의 트랜지스터들 각각은 LOD 보호된다. 458에서, 클록 신호(348)에 기초하여 펄스 신호(352)가 펄스 발생기 회로(304)에서 발생된다.

[0042]

462에서, 데이터 신호(356)가 펄스-래치 회로(300)의 래치 회로(308)에서 수신된다. 466에서, 출력 신호(360)가 펄스-래치 회로(300)에서 발생된다. 예컨대, 펄스 신호(352)에 기초하여 데이터 신호(356)를 샘플링함으로써 출력 신호(360)가 발생될 수 있다. 출력 신호(360)는 대략 200 피코초(ps)의 펄스 폭을 가진 펄스에 대응할 수 있다.

[0043]

출력 신호(360)가, LOD 보호되는 복수의 트랜지스터들을 이용하여 발생되기 때문에, 출력 신호(360)의 펄스 폭이 정확하게 결정될 수 있으며, 펄스-래치 회로(300)를 제조하기 위해 이용되는 프로세스와 연관된 프로세스 변동들에 덜 취약하다. 따라서, 펄스-래치 회로(300)와 연관된 설계 규격에 더 정확하게 대응하도록 펄스 폭을 제어함으로써, 펄스-래치 회로(300)의 성능이 개선될 수 있다.

[0044]

도 5를 참조하면, 모바일 디바이스의 특정 예시적 실시예의 블록도가 도시되고 일반적으로 500으로 지정된다. 모바일 디바이스(500)는 프로세서(510)를 포함한다. 프로세서(510)는 컴퓨터-판독가능 저장 매체, 이를테면, 메모리(532)(예컨대, 비-일시적 컴퓨터-판독가능 매체)에 커플링될 수 있다. 메모리(532)는 프로세서(510)에 의해 실행가능한 명령들(554), 프로세서에 액세스가능한 데이터(556), 또는 이들의 조합을 저장할 수 있다.

[0045]

도 5에서, 프로세서는 펄스-래치 회로(예컨대, 도 3의 펄스-래치 회로(300))를 포함한다. 펄스-래치 회로는 복수의 트랜지스터들을 포함하고, 복수의 트랜지스터들 각각은 LOD(length-of-diffusion) 보호된다. 복수의 트랜지스터들은 도 3의 LOD 보호된 트랜지스터들(316, 320, 336, 340)을 포함할 수 있다. 특정 실시예에서, 출력 신호는 대략 200 피코초(ps)의 펄스 폭을 가진 펄스이다.

[0046]

도 5는 또한, 프로세서(510) 및 디스플레이(528)에 커플링되는 디스플레이 제어기(526)를 도시한다. 코더/디코더(CODEC)(534)가 또한 프로세서(510)에 커플링될 수 있다. 스피커(536) 및 마이크로폰(538)은 CODEC(534)에 커플링될 수 있다. 도 5는 또한, 무선 제어기(540)가 프로세서(510)에 커플링될 수 있음을 표시한다. 무선 제어기는 추가로, 트랜시버(550)를 통해 안테나(542)에 커플링될 수 있다. 카메라(546)는 카메라 제어기(590)에 커플링될 수 있다. 카메라 제어기(590)는 프로세서(510)에 커플링될 수 있다.

[0047]

특정 실시예에서, 프로세서(510), 메모리(532), 디스플레이 제어기(526), 카메라 제어기(590), CODEC(534), 무선 제어기(540), 및 트랜시버(550)는 시스템-인-패키지 또는 시스템-온-칩 디바이스(522)와 같은 집적 회로에 포함된다. 입력 디바이스(530) 및 전원(544)은 시스템-온-칩 디바이스(522)에 커플링될 수 있다.

[0048]

더욱이, 특정 실시예에서, 그리고 도 5에서 예시된 바와 같이, 디스플레이(528), 입력 디바이스(530), 카메라(546), 스피커(536), 마이크로폰(538), 안테나(542), 및 전원(544)은 시스템-온-칩 디바이스(522) 외부에 있다. 그러나, 디스플레이(528), 입력 디바이스(530), 카메라(546), 스피커(536), 마이크로폰(538), 안테나(542), 및 전원(544) 각각은, 인터페이스 또는 제어기와 같은, 시스템-온-칩 디바이스(522)의 컴포넌트에 커플링될 수 있다.

[0049]

펄스-래치 회로가 LOD 보호되는 트랜지스터들을 포함하기 때문에, 출력 신호의 펄스 폭은 정확하게 결정될 수 있고, 회로를 제조하기 위해 이용되는 프로세스와 연관된 프로세스 변동들에 덜 취약하다. 따라서, 시스템-온-칩 디바이스(522)와 연관된 설계 규격에 더 정확하게 대응하도록 펄스 폭을 제어함으로써, 시스템-온-칩 디바이스(522)의 전력 소비 및 성능이 (예컨대, 전원(544)으로부터 소모되는 전류량을 절약함으로써) 개선될 수 있다.

[0050]

당업자들은, 앞서 개시된 디바이스들 및 기능성들이 컴퓨터-판독가능 매체들 상에 저장된 컴퓨터 파일들(예컨대, RTL, GDSII, GERBER 등)로 설계되고 구성될 수 있음을 인식할 것이다. 일부 또는 모든 이러한 파일들은 이러한 파일들에 기초하여 디바이스들을 제조하는 제조 핸들러들에게 제공될 수 있다. 결과적인 제품들은 반도체 웨이퍼들을 포함하며, 이 반도체 웨이퍼들은 이후 반도체 다이들로 절단되고 반도체 칩들로 패키지화된다. 반도체 칩들은 이후, 도 6과 관련하여 추가로 설명되는 바와 같이 디바이스들(예컨대, 모바일 디바이스(500))에서 이용된다.

[0051]

도 6을 참조하면, 물리적 디바이스 정보(602)는 제조 프로세스(600)에서, 이를테면, 리서치 컴퓨터(606)에서 수신된다. 물리적 디바이스 정보(602)는 반도체 디바이스의 적어도 하나의 물리적 특성을 나타내는 설계 정보를 포함할 수 있다. 예컨대, 물리적 디바이스 정보(602)는 물리적 파라미터들, 재료 특징들, 및 리서치 컴퓨터(606)에 커플링되는 사용자 인터페이스(604)를 통해 입력되는 구조 정보를 포함할 수 있다. 물리적 디바이스 정보(602)는 본원에서 설명되는 물리적 구조들에 대응하는 물리적 디바이스 정보를 포함할 수 있다. 리서치 컴퓨터(606)는 메모리(610)와 같은 컴퓨터 판독가능 매체에 커플링되는 하나 또는 둘 이상의 프로세싱 코어들과 같은 프로세서(608)를 포함한다. 메모리(610)는 프로세서(608)로 하여금 물리적 디바이스 정보(602)를 파일 포맷에 따르도록 변환하여 라이브러리 파일(612)을 발생시키도록 실행가능한 컴퓨터 판독가능 명령들을 저장할 수 있다.

[0052]

특정 실시예에서, 라이브러리 파일(612)은 변환된 설계 정보를 포함하는 적어도 하나의 데이터 파일을 포함한다. 예컨대, 라이브러리 파일(612)은 전자 설계 자동화(EDA) 도구(620)와 함께 사용하기 위해 제공되는 반도체 디바이스들의 라이브러리를 포함할 수 있다.

[0053]

라이브러리 파일(612)은 메모리(예컨대, 메모리(112))에 커플링되는 하나 또는 둘 이상의 프로세싱 코어들과 같은 프로세서(예컨대, 프로세서(116))를 포함하는 설계 컴퓨터(예컨대, 도 1의 컴퓨터(104))에서 EDA 도구(620)와 함께 사용될 수 있다. EDA 도구(620)는 컴퓨터(104)의 사용자로 하여금 라이브러리 파일(612)을 이용하여 회로를 설계하도록 하는 것을 가능하게 하기 위해 메모리(112)에 프로세서 실행가능 명령들로서 저장될 수 있다. 예컨대, 컴퓨터(104)의 사용자는 컴퓨터(104)에 커플링된 사용자 인터페이스(624)를 통해 회로 설계 정보(622)를 입력할 수 있다. 회로 설계 정보(622)는 반도체 디바이스의 물리적 특성들을 표시할 수 있고 그리고 도 1의 회로 설계(108), 도 2의 회로 설계(200), 또는 이들의 조합에 대응할 수 있다. 물리적 특성들은 회로 설계들(108, 200) 중 하나 또는 양쪽 모두의 구조들 및 구조들의 관계들, 이를테면, 레이아웃 정보(예컨대, OD(oxide-on-diffusion) 구역들, STI(shallow trench isolation) 구역들, 필드 산화물 구역(field oxide region)들, 또는 이들의 조합), 포지셔닝 정보, 피쳐(feature) 크기 정보, 상호연결 정보, 또는 반도체 디바이스의 물리적 특성들을 나타내는 다른 정보를 표시할 수 있다. 컴퓨터(104)는 도 1의 수정된 회로 설계(108), 도 2의 수정된 회로 설계(250), 또는 이들의 조합을 발생시키기 위해 물리적 특성들을 (예컨대, 도 1의 명령들(120)을 실행시킴으로써) 분석할 수 있다. 예컨대, 컴퓨터(104)는, 앞서 설명된 바와 같이, 수정된 회로 설계(108), 수정된 회로 설계(250), 또는 이들의 조합을 발생시키게, OD 구역들 사이의 하나 또는 둘 이상의 갭들을 식별하고 그리고 하나 또는 둘 이상의 갭들을 브리징하기 위해, 레이아웃 정보, 포지셔닝 정보, 피쳐 크기 정보, 상호연결 정보, 반도체 디바이스의 물리적 특성들을 나타내는 다른 정보, 또는 이들의 조합을 분석할 수 있다.

[0054]

컴퓨터(104)는 파일 포맷에 따르도록, 수정된 회로 설계(108), 수정된 회로 설계(250), 또는 이들의 조합을 포함하는 회로 설계 정보(622)를 변환하도록 구성될 수 있다. 예시하자면, 파일 포맷은 평면 기하학적 형상들, 텍스트 라벨들, 및 계층적 포맷인 회로 레이아웃에 관한 다른 정보를 나타내는 데이터베이스 이진 파일 포맷, 이를테면, GDSII(Graphic Data System) 파일 포맷을 포함할 수 있다. 컴퓨터(104)는, 다른 회로들 또는 정보에 부가하여, 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 설명하는 정보를 포함하는 GDSII 파일(626)과 같은 변환된 설계 정보를 포함하는 데이터 파일을 발생시키도록 구성될 수 있다. 예시하자면, 데이터 파일은 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522)를 포함하고 그리고 또한 집적 회로 내의 부가적인 전자 회로들 및 컴포넌트들을 포함하는 집적 회로에 대응하는 정보를 포함할 수 있다.

[0055]

GDSII 파일(626)은, GDSII 파일(626) 내의 변환된 정보에 따라, 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 제조하기 위해 제조 프로세스(628)에서 수신될 수 있다. 예컨대, 디바이스 제조 프로세스는 대표 마스크(632)로서 예시된, 포토리소그래피 프로세싱과 함께 사용될 마스크들과 같은 하나 또는 둘 이상의 마스크들을 생성하기 위해 마스크 제조자(630)에게 GDSII 파일(626)을 제공하는 단계를 포함할 수 있다. 마스크(632)는, 테스트되어 대표 다이(636)와 같은 다이들로 분리될 수 있는 하나 또는 둘 이상의 웨이퍼들(634)을 생성하기 위해 제조 프로세스 동안 사용될 수 있다. 다이(636)는 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 포함하는 회로를 포함한다.

[0056]

다이(636)는 패키징 프로세스(638)에 제공될 수 있으며, 여기서 다이(636)가 대표 패키지(640) 내에 포함된다. 예컨대, 패키지(640)는 시스템-인-패키지(SiP) 배열(arrangement)과 같은 다수의 다이들 또는 단일 다이(636)를 포함할 수 있다. 패키지(640)는 JEDEC(Joint Electron Device Engineering Council) 표준들과 같은 하나 또는 둘 이상의 표준들 또는 규격들에 따르도록 구성될 수 있다.

[0057]

패키지(640)에 관한 정보는, 이를테면, 컴퓨터(646)에 저장되는 컴포넌트 라이브러리를 통해, 다양한 제품 설계자들에게 분배될 수 있다. 컴퓨터(646)는 메모리(650)에 커플링되는 하나 또는 둘 이상의 프로세싱 코어들과 같은 프로세서(648)를 포함할 수 있다. PCB(printed circuit board) 도구는 사용자 인터페이스(644)를 통해 컴퓨터(646)의 사용자로부터 수신되는 PCB 설계 정보(642)를 프로세싱하도록 메모리(650)에 프로세서 실행가능 명령들로서 저장될 수 있다. PCB 설계 정보(642)는 회로 기판 상에서 패키지화된 반도체 디바이스의 물리적 포지셔닝 정보를 포함할 수 있다. 패키지화된 반도체 디바이스는 패키지(640)에 대응하고, 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 포함한다.

[0058]

컴퓨터(646)는 회로 기판 상에 패키지화된 반도체 디바이스의 물리적 포지셔닝 정보뿐만 아니라 트레이스들 및 비아들과 같은 전기적 연결들의 레이아웃을 포함하는 데이터를 가지는 GERBER 파일(652)과 같은 데이터 파일을 발생시키기 위해 PCB 설계 정보(642)를 변환하도록 구성될 수 있으며, 패키지화된 반도체 디바이스는 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 포함하는 패키지(640)에 대응한다. 다른 실시예들에서, 변환된 PCB 설계 정보에 의해 발생된 데이터 파일은 GERBER 포맷 이외의 포맷을 가질 수 있다.

[0059]

GERBER 파일(652)은 보드 어셈블리 프로세스(654)에서 수신되어 GERBER 파일(652) 내에 저장된 설계 정보에 따라 제조되는 대표 PCB(656)와 같은 PCB들을 생성하기 위해 사용될 수 있다. 예컨대, GERBER 파일(652)은 PCB 생산 프로세스의 다양한 단계들을 수행하기 위한 하나 또는 둘 이상의 머신들에 업로딩될 수 있다. PCB(656)는 대표 PCA(printed circuit assembly)(658)를 형성하기 위해 패키지(640)를 포함하는 전자 컴포넌트들로 파퓰레이팅(populate)될 수 있다.

[0060]

PCA(658)는 제품 제조 프로세스(660)에서 수신되어 하나 또는 둘 이상의 전자 디바이스들, 이를테면, 제 1 대표 전자 디바이스(662) 및 제 2 대표 전자 디바이스(664) 내에 통합될 수 있다. 예시적인 비제한적 예로서, 제 1 대표 전자 디바이스(662), 제 2 대표 전자 디바이스(664), 또는 양쪽 모두는, 셋톱 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, PDA(personal digital assistant), 고정 위치 데이터 유닛, 및 컴퓨터의 그룹으로부터 선택될 수 있으며, 이들에 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522)가 통합된다. 또다른 예시적인 비제한적 예로서, 전자 디바이스들(662 및 664) 중 하나 또는 둘 이상은 모바일 전화들과 같은 원격 유닛들, 핸드-헬드 PCS(personal communication systems) 유닛들, 개인 데이터 어시스턴트들과 같은 휴대용 데이터 유닛들, GPS(global positioning system) 인에이블형 디바이스들, 내비게이션 디바이스들, 미터 판독 장비와 같은 고정 위치 데이터 유닛들, 또는 데이터 또는 컴퓨터 명령들을 저장 또는 리트리빙(retrieve)하는 임의의 다른 디바이스, 또는 이들의 임의의 조합일 수 있다. 특정 실시예에서, 전자 디바이스들(662 및 664)은 도 5의 모바일 디바이스(500)에 대응한다.

[0061]

따라서, 도 3의 펄스-래치 회로(300), 도 5의 시스템-온-칩 디바이스(522), 또는 이들의 임의의 조합을 포함하는 디바이스는, 예시적인 프로세스(600)에서 설명된 바와 같이 제조되고 프로세싱되고, 전자 디바이스 내에 포함될 수 있다. 도 1 내지 도 5와 관련하여 개시된 실시예들의 하나 또는 둘 이상의 양상들은 다양한 프로세싱 스테이지들에서, 이를테면, 라이브러리 파일(612), GDSII 파일(626), 및 GERBER 파일(652) 내에 포함될 수 있을 뿐만 아니라, 리서치 컴퓨터(606)의 메모리(610), 컴퓨터(104)의 메모리(112), 컴퓨터(646)의 메모리(650), 다양한 스테이지들에서, 이를테면, 기판 어셈블리 프로세스(654)에서 사용되는 하나 또는 둘 이상의 다른 컴퓨터들 또는 프로세서들(도시되지 않음)의 메모리에 저장될 수 있고, 또한, 하나 또는 둘 이상의 다른 물리적 실시예들, 이를테면, 마스크(632), 다이(636), 패키지(640), PCA(658), 프로토타입 회로들 또는 디바이스들(도시되지 않음)과 같은 다른 제품들, 또는 이들의 임의의 조합에 포함될 수 있다. 물리적 디바이스 설계에서 최종 제품까지의 다양한 대표적인 생산 스테이지들이 도시되지만, 다른 실시예들에서는 더 적은 스테이지들이 사용될 수 있거나 부가적인 스테이지들이 포함될 수 있다. 유사하게, 프로세스(600)는 단일 엔티티에 의해, 또는 프로세스(600)의 다양한 스테이지들을 수행하는 하나 또는 둘 이상의 엔티티들에 의해 수행될 수 있다.

[0062]

특정 실시예에서, 컴퓨터-판독가능 저장 매체(예컨대, 도 1의 메모리(112))는, 회로 설계(예컨대, 회로 설계(108), 회로 설계(200), 또는 이들의 조합)에서 그리고 프로세서에 의해, 제 1 OD(oxide-on-diffusion) 구역(예컨대, OD 구역들(124, 128, 208, 212) 중 하나)과 제 2 OD 구역(예컨대, OD 구역들(124, 128, 208, 212) 중 또다른 하나) 사이의 갭(예컨대, 갭(144), 갭(244), 또는 이들의 조합)을 식별하는 것을 포함하는 동작들을 수행하도록 프로세서(예컨대, 프로세서(116))에 의해 실행가능한 명령들(예컨대, 명령들(120))을 저장한다. 동작들은 갭을 식별하는 것에 응답하여 그리고 프로세서에 의해, 수정된 회로 설계(예컨대, 수정된 회로 설계(154), 수정된 회로 설계(250), 또는 이들의 조합)를 발생시키기 위해 회로 설계에 더미 디바이스(예컨대, 더미 디바이스들(162, 248, 312, 324, 332, 344) 중 임의의 것 또는 이들의 조합)를 부가함으로써, 갭을 브리징하는 것을 더 포함한다.

[0063]

특정 실시예에서, 장치는 클록 신호(예컨대, 클록 신호(348))에 응답하여 펄스 신호(예컨대, 펄스 신호(352))를 발생시키기 위한 수단(예컨대, 펄스 발생기 회로(304))을 포함한다. 장치는 펄스 신호에 응답하여 출력 신호(예컨대, 출력 신호(360))를 발생시키기 위한 수단(예컨대, 래치 회로(308))을 더 포함한다. 출력 신호를 발생시키기 위한 수단은 각각이 LOD(length-of-diffusion) 보호되는 다수의 트랜지스터들(예컨대, LOD 보호된 트랜지스터들(336, 340))을 포함한다.

[0064]

본원에서 이용되는 바와 같이, "OD(oxide-on-diffusion)"는 기판의 확산 구역 및 확산 구역에 인접한 임의의 트랜지스터 게이트 산화물 구역들을 나타낼 수 있다. 예컨대, "OD(oxide-on-diffusion)"는 드레인, 소스를 형성하는 기판의 도핑된 구역들 그리고 도핑된 구역들에 인접한(예컨대, 접촉하는) 임의의 트랜지스터 게이트 산화물 구역들에 부가하여 하나 또는 둘 이상의 트랜지스터들의 벌크 구역들을 나타낼 수 있다. 본원에서 이용되는 바와 같이, "LOD 보호된"은 트랜지스터를 제조하기 위해 이용되는 제조 기술과 연관된(예컨대, 제조 기술에 의해 정의된) 최소 길이와 같은 임계 길이보다 더 큰 길이(sa)(도 2와 관련하여 설명된 바와 같음)를 가진 트랜지스터를 표시할 수 있다.

[0065]

당업자들은 본원에서 개시된 실시예들과 관련하여 설명되는 다양한 예시적인 논리 블록들, 구성들, 모듈들, 회로들 및 알고리즘 단계들이 전자 하드웨어, 프로세서에 의해 실행되는 컴퓨터 소프트웨어, 또는 이들 모두의 조합들로서 구현될 수 있음을 추가로 인식할 것이다. 다양한 예시적인 컴포넌트들, 블록들, 구성들, 모듈들, 회로들 및 단계들이 이들의 기능성의 관점에서 일반적으로 전술되었다. 이러한 기능성이 하드웨어로 구현될지 또는 프로세서 실행가능 명령들로서 구현될지는 특정 애플리케이션 및 전체 시스템에 부과되는 설계 제약들에 의존한다. 당업자들은 설명된 기능성을 각각의 특정 애플리케이션에 대해 다양한 방식들로 구현할 수 있지만, 이러한 구현 결정들은 본 개시내용의 범주로부터의 이탈을 야기하는 것으로서 해석되지 않아야 한다.

[0066]

본원에서 개시된 실시예들과 관련하여 설명된 알고리즘 또는 방법의 단계들은 직접 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로 또는 이들 둘의 조합으로 구현될 수 있다. 소프트웨어 모듈은 RAM(random access memory), 플래시 메모리, ROM(read-only memory), PROM(programmable read-only memory), EPROM(erasable programmable read-only memory), EEPROM(electrically erasable programmable read-only memory), 레지스터들, 하드 디스크, 착탈식 디스크, CD-ROM(compact disc read-only memory), 또는 당해 기술분야에 알려진 임의의 다른 형태의 비-일시적 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독하고 저장 매체에 정보를 기록할 수 있도록 프로세서에 커플링된다. 대안적으로, 저장 매체는 프로세서와 일체화될 수 있다. 프로세서 및 저장 매체는 ASIC(application-specific integrated circuit)에 상주할 수 있다. ASIC는 컴퓨팅 디바이스 또는 사용자 단말에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 컴퓨팅 디바이스 또는 사용자 단말 내에서 이산 컴포넌트들로서 상주할 수 있다.

[0067]

개시된 실시예들의 이전 설명은 당업자가 개시된 실시예들을 실시 또는 사용하는 것을 가능하게 하기 위해 제공된다. 이러한 실시예들에 대한 다양한 수정들은 당업자들에게 용이하게 명백할 것이며, 본원에서 정의된 원리들은 본 개시내용의 범주로부터 벗어남이 없이 다른 실시예들에 적용될 수 있다. 따라서, 본 개시내용은 본원에서 도시된 실시예들에 제한되도록 의도되는 것이 아니라 후속하는 청구항들에 의해 정의되는 원리들 및 신규한 특징들과 부합하는 가능한 가장 넓은 범주에 따르도록 의도된다.

Claims (24)

- 회로로서,

제 1 복수의 트랜지스터들을 포함하는 펄스-래치 회로(pulsed-latch circuit)

를 포함하고,

상기 제 1 복수의 트랜지스터들 중 하나 또는 둘 이상은 LOD(length-of-diffusion) 보호되는,

회로. - 제 1 항에 있어서,

상기 펄스-래치 회로는,

클록 신호에 응답하는 펄스 발생기 회로 ― 상기 펄스 발생기 회로는 상기 클록 신호에 응답하여 펄스를 발생시키도록 구성됨 ―, 및

발생된 펄스에 응답하여 데이터를 샘플링하도록 구성된 래치 회로

를 더 포함하고,

상기 펄스 발생기 회로는 상기 제 1 복수의 트랜지스터들을 포함하는 지연 경로를 포함하는,

회로. - 제 2 항에 있어서,

상기 래치 회로는 각각이 LOD 보호되는 제 2 복수의 트랜지스터들을 포함하는,

회로. - 제 1 항에 있어서,

상기 펄스-래치 회로는 STI(shallow trench isolation) 에지를 갖는 STI 구역을 더 포함하고,

상기 제 1 복수의 트랜지스터들 중 적어도 제 1 트랜지스터는 pSi(poly-silicon) 구역을 포함하고, 그리고

상기 pSi 구역의 에지와 상기 STI 에지 사이의 길이는 상기 제 1 트랜지스터를 제조하기 위해 이용되는 제조 기술과 연관된 임계 길이보다 더 큰,

회로. - 제 1 항에 있어서,

상기 트랜지스터들 각각은 상기 펄스-래치 회로의 STI(shallow trench isolation) 구역의 STI 에지에 인접하지 않는(non-adjacent),

회로. - 방법으로서,

회로 설계에서 그리고 프로세서에 의해, 제 1 OD(oxide-on-diffusion) 구역과 제 2 OD 구역 사이의 갭을 식별하는 단계; 및

상기 갭을 식별하는 것에 응답하여, 수정된 회로 설계(modified circuit design)를 발생시키기 위해 상기 프로세서에 의해 상기 회로 설계에 더미 디바이스(dummy device)를 부가함으로써 상기 갭을 브리징(bridging)하는 단계

를 포함하는,

방법. - 제 6 항에 있어서,

상기 더미 디바이스는 더미 트랜지스터에 대응하는,

방법. - 제 7 항에 있어서,

상기 더미 트랜지스터는 디커플링 커패시터(decoupling capacitor)로서 구성되는,

방법. - 제 6 항에 있어서,

상기 갭은 상기 회로 설계의 STI(shallow trench isolation) 구역에 대응하는,

방법. - 제 6 항에 있어서,

상기 갭을 식별하는 단계는 상기 회로 설계에서 STI(shallow trench isolation) 구역의 제 1 STI 에지에 가까운 제 2 디바이스를 식별하는 단계를 포함하고, 그리고

상기 더미 디바이스를 부가하는 것은 상기 제 1 OD 구역과 상기 제 2 OD 구역 사이의 갭을 브리징함으로써 상기 회로 설계로부터 상기 제 1 STI 에지를 제거하는,

방법. - 제 10 항에 있어서,

상기 STI 구역의 제 2 STI 에지에 가까운 제 3 디바이스를 식별하는 단계

를 더 포함하고,

상기 더미 디바이스를 부가하는 것은 상기 제 1 OD 구역과 상기 제 2 OD 구역 사이의 갭을 브리징함으로써 상기 회로 설계로부터 상기 제 2 STI 에지를 제거하는,

방법. - 제 11 항에 있어서,

상기 갭을 식별하는 단계 및 상기 갭을 브리징하는 단계는 메모리로부터 리트리빙(retrieve)된 명령들을 실행하는 상기 프로세서에 의해 수행되고, 그리고

상기 갭을 식별하는 단계 및 상기 갭을 브리징하는 단계는 상기 회로 설계의 레이아웃 페이즈(layout phase) 동안 상기 프로세서에 의해 수행되는,

방법. - 제 6 항에 있어서,

상기 수정된 회로 설계는, 각각 STI(shallow trench isolation) 에지에 인접하지 않는 다수의 트랜지스터들을 포함하는 펄스-래치 회로에 대응하는,

방법. - 제 6 항에 있어서,

상기 수정된 회로 설계에 따라 회로를 제조하는 단계

를 더 포함하는,

방법. - 방법으로서,

복수의 트랜지스터들을 포함하는 펄스-래치 회로에서 출력 신호를 발생시키는 단계

를 포함하고,

상기 복수의 트랜지스터들 각각은 LOD(length-of-diffusion) 보호되는,

방법. - 제 15 항에 있어서,

상기 출력 신호는 대략 200 피코초(ps)의 펄스 폭을 갖는,

방법. - 제 15 항에 있어서,

클록 신호를 수신하는 단계;

상기 클록 신호에 기초하여 펄스 신호를 발생시키는 단계; 및

데이터 신호를 수신하는 단계

를 더 포함하고,

상기 출력 신호는 상기 펄스 신호에 기초하여 상기 데이터 신호를 샘플링함으로써 발생되는,

방법. - 컴퓨터-판독가능 저장 매체로서,

상기 컴퓨터-판독가능 저장 매체는, 동작들을 수행하도록 프로세서에 의해 실행가능한 명령들을 저장하고,

상기 동작들은,

회로 설계에서 그리고 상기 프로세서에 의해, 제 1 OD(oxide-on-diffusion) 구역과 제 2 OD 구역 사이의 갭을 식별하는 것, 및

상기 갭을 식별하는 것에 응답하여, 수정된 회로 설계를 발생시키기 위해 상기 프로세서에 의해 상기 회로 설계에 더미 디바이스를 부가함으로써 상기 갭을 브리징하는 것

을 포함하는,

컴퓨터-판독가능 저장 매체. - 제 18 항에 있어서,

상기 갭을 식별하는 것 및 상기 갭을 브리징하는 것은 상기 회로 설계와 연관된 레이아웃 페이즈 동안 수행되는,

컴퓨터-판독가능 저장 매체. - 장치로서,

클록 신호에 응답하여 펄스 신호를 발생시키기 위한 수단; 및

상기 펄스 신호에 응답하여 출력 신호를 발생시키기 위한 수단

을 포함하고,

상기 출력 신호를 발생시키기 위한 수단은 각각이 LOD(length-of-diffusion) 보호되는 다수의 트랜지스터들을 포함하는,

장치. - 제 20 항에 있어서,

상기 펄스 신호를 발생시키기 위한 수단은 펄스 발생기 회로를 포함하는,

장치. - 제 20 항에 있어서,

상기 펄스 신호를 발생시키기 위한 수단은 각각이 LOD 보호되는 제 2 복수의 트랜지스터들을 포함하는,

장치. - 제 20 항에 있어서,

상기 출력 신호를 발생시키기 위한 수단은 추가로 데이터 신호에 응답하고, 그리고

상기 출력 신호는 상기 펄스 신호에 의해 결정된 시간들에서 상기 데이터 신호를 샘플링함으로써 발생되는,

장치. - 제 20 항에 있어서,

상기 펄스 신호를 발생시키기 위한 수단 및 상기 출력 신호를 발생시키기 위한 수단을 포함하는 집적 회로

를 더 포함하는,

장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/905,052 US9093995B2 (en) | 2013-05-29 | 2013-05-29 | Length-of-diffusion protected circuit and method of design |

| US13/905,052 | 2013-05-29 | ||

| PCT/US2014/039867 WO2014194007A2 (en) | 2013-05-29 | 2014-05-28 | Length-of-diffusion protected circuit and method of design |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160013161A true KR20160013161A (ko) | 2016-02-03 |

Family

ID=51022461

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157036436A KR20160013161A (ko) | 2013-05-29 | 2014-05-28 | 확산-길이 보호된 회로 및 설계 방법 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9093995B2 (ko) |

| EP (1) | EP3005183B1 (ko) |

| JP (1) | JP6312818B2 (ko) |

| KR (1) | KR20160013161A (ko) |

| CN (1) | CN105264531B (ko) |

| BR (1) | BR112015029871A2 (ko) |

| WO (1) | WO2014194007A2 (ko) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10282503B2 (en) * | 2016-06-25 | 2019-05-07 | Qualcomm Incorporated | Mitigating length-of-diffusion effect for logic cells and placement thereof |

| CN113204935B (zh) * | 2021-05-08 | 2023-03-24 | 山东英信计算机技术有限公司 | 一种电源模块化设计方法及装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001285028A (ja) * | 2000-03-29 | 2001-10-12 | Fujitsu General Ltd | 同期終端回路 |

| WO2004038917A1 (ja) * | 2002-10-25 | 2004-05-06 | Renesas Technology Corp. | 半導体集積回路 |

| JP2006121443A (ja) * | 2004-10-21 | 2006-05-11 | Matsushita Electric Ind Co Ltd | パルス生成装置 |

| JP2006339948A (ja) * | 2005-06-01 | 2006-12-14 | Renesas Technology Corp | パルスラッチ回路及び半導体集積回路 |

| US7920403B2 (en) * | 2005-07-27 | 2011-04-05 | Taiwan Semiconductor Manufacturing Co., Ltd. | ROM cell array structure |

| US7484198B2 (en) | 2006-02-27 | 2009-01-27 | Synopsys, Inc. | Managing integrated circuit stress using dummy diffusion regions |

| US7475381B2 (en) * | 2006-03-30 | 2009-01-06 | Intel Corporation | Shallow trench avoidance in integrated circuits |

| JP2008118004A (ja) * | 2006-11-07 | 2008-05-22 | Nec Electronics Corp | 半導体集積回路 |

| US7958465B2 (en) | 2008-05-08 | 2011-06-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dummy pattern design for reducing device performance drift |

| US8232824B2 (en) | 2009-04-08 | 2012-07-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Clock circuit and method for pulsed latch circuits |

| JP5329673B2 (ja) * | 2009-10-06 | 2013-10-30 | 株式会社日立製作所 | 半導体集積回路装置 |

| US8610236B2 (en) | 2010-08-06 | 2013-12-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Edge devices layout for improved performance |

| CN103403859B (zh) * | 2011-03-04 | 2016-11-09 | 瑞萨电子株式会社 | 半导体器件 |

| EP2509027B1 (en) * | 2011-04-04 | 2019-02-06 | Nxp B.V. | Method for handling collision in an identification system |

| TW201241992A (en) | 2011-04-08 | 2012-10-16 | United Microelectronics Corp | Method of unifying device performance within die |

-

2013

- 2013-05-29 US US13/905,052 patent/US9093995B2/en active Active

-

2014

- 2014-05-28 BR BR112015029871A patent/BR112015029871A2/pt not_active Application Discontinuation

- 2014-05-28 JP JP2016516800A patent/JP6312818B2/ja active Active

- 2014-05-28 EP EP14733458.5A patent/EP3005183B1/en active Active

- 2014-05-28 CN CN201480030890.9A patent/CN105264531B/zh active Active

- 2014-05-28 KR KR1020157036436A patent/KR20160013161A/ko not_active Application Discontinuation

- 2014-05-28 WO PCT/US2014/039867 patent/WO2014194007A2/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| WO2014194007A3 (en) | 2015-01-22 |

| WO2014194007A2 (en) | 2014-12-04 |

| CN105264531A (zh) | 2016-01-20 |

| JP2016526301A (ja) | 2016-09-01 |

| US20140354338A1 (en) | 2014-12-04 |

| BR112015029871A2 (pt) | 2017-07-25 |

| JP6312818B2 (ja) | 2018-04-18 |

| US9093995B2 (en) | 2015-07-28 |

| CN105264531B (zh) | 2019-04-19 |

| EP3005183A2 (en) | 2016-04-13 |

| EP3005183B1 (en) | 2020-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8381144B2 (en) | System and method of test mode gate operation | |

| JP6084308B2 (ja) | メモリセルをプログラミングするシステムおよび方法 | |

| US8610176B2 (en) | Standard cell architecture using double poly patterning for multi VT devices | |

| US9607988B2 (en) | Off-center gate cut | |

| US20140025325A1 (en) | Voltage Level-Shifting | |

| US8631368B2 (en) | Method and circuit to generate race condition test data at multiple supply voltages | |

| US20140327510A1 (en) | Electronic device having asymmetrical through glass vias | |

| US20140219015A1 (en) | System and method of programming a memory cell | |

| KR101424663B1 (ko) | 로컬 전류 싱크를 갖는 메모리 디바이스 | |

| US9054520B2 (en) | ESD clamping transistor with switchable clamping modes of operation | |

| US8829965B2 (en) | System and method to perform scan testing using a pulse latch with a blocking gate | |

| EP3005183B1 (en) | Length-of-diffusion protected circuit and method of design | |

| US9461040B2 (en) | System and method of varying gate lengths of multiple cores | |

| US20230345692A1 (en) | Gate spacer structure | |

| US9542518B2 (en) | User experience based management technique for mobile system-on-chips |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |