KR20150084908A - 전-대역 증폭기들 - Google Patents

전-대역 증폭기들 Download PDFInfo

- Publication number

- KR20150084908A KR20150084908A KR1020157015072A KR20157015072A KR20150084908A KR 20150084908 A KR20150084908 A KR 20150084908A KR 1020157015072 A KR1020157015072 A KR 1020157015072A KR 20157015072 A KR20157015072 A KR 20157015072A KR 20150084908 A KR20150084908 A KR 20150084908A

- Authority

- KR

- South Korea

- Prior art keywords

- band

- coupled

- transistor

- signal

- gain

- Prior art date

Links

- 238000000034 method Methods 0.000 claims description 26

- 230000003321 amplification Effects 0.000 claims description 4

- 230000008878 coupling Effects 0.000 claims description 4

- 238000010168 coupling process Methods 0.000 claims description 4

- 238000005859 coupling reaction Methods 0.000 claims description 4

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 4

- 230000003139 buffering effect Effects 0.000 claims 4

- 230000001131 transforming effect Effects 0.000 claims 1

- 238000013461 design Methods 0.000 abstract description 67

- 230000007850 degeneration Effects 0.000 abstract description 24

- 239000003990 capacitor Substances 0.000 description 25

- 238000010586 diagram Methods 0.000 description 8

- 230000005540 biological transmission Effects 0.000 description 7

- 238000004891 communication Methods 0.000 description 7

- 230000006854 communication Effects 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910044991 metal oxide Inorganic materials 0.000 description 3

- 150000004706 metal oxides Chemical class 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 230000002776 aggregation Effects 0.000 description 2

- 238000004220 aggregation Methods 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000007175 bidirectional communication Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000004590 computer program Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 229920000729 poly(L-lysine) polymer Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/189—High-frequency amplifiers, e.g. radio frequency amplifiers

- H03F3/19—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only

- H03F3/193—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only with field-effect devices

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W88/00—Devices specially adapted for wireless communication networks, e.g. terminals, base stations or access point devices

- H04W88/02—Terminal devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/68—Combinations of amplifiers, e.g. multi-channel amplifiers for stereophonics

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/005—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission adapting radio receivers, transmitters andtransceivers for operation on two or more bands, i.e. frequency ranges

- H04B1/0053—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission adapting radio receivers, transmitters andtransceivers for operation on two or more bands, i.e. frequency ranges with common antenna for more than one band

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

Abstract

다수의 대역 그룹들을 지원하는 전-대역 증폭기들이 개시된다. 예시적인 설계에서, 장치(예를 들어, 무선 디바이스, 집적 회로 등)는 적어도 하나의 이득 트랜지스터 및 복수의 대역 그룹들에 대한 복수의 캐스코드 트랜지스터들을 포함한다. 각각의 대역 그룹은 복수의 대역들을 커버한다. 이득 트랜지스터(들)는 입력 라디오 주파수(RF) 신호를 수신한다. 캐스코드 트랜지스터들은 이득 트랜지스터(들)에 커플링되고 복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 제공한다. 예시적인 설계에서, 이득 트랜지스터(들)는 복수의 대역 그룹들에 대한 복수의 이득 트랜지스터들을 포함한다. 하나의 이득 트랜지스터 및 하나의 캐스코드 트랜지스터는 입력 RF 신호를 증폭하고 선택된 대역 그룹에 대한 출력 RF 신호를 제공하도록 인에이블된다. 이득 트랜지스터들은 단일 소스 디제너레이션 인덕터의 상이한 탭들에 또는 상이한 소스 디제너레이션 인덕터들에 커플링될 수 있다.

Description

[0001] 본 개시는 일반적으로 전자기기에 관한 것으로서, 보다 구체적으로 증폭기들에 관한 것이다.

[0002] 무선 통신 시스템에서 무선 디바이스(예를 들어, 셀룰러 전화 또는 스마트폰)는 양방향 통신을 위해 데이터를 전송 및 수신할 수 있다. 무선 디바이스는 데이터 전송을 위한 전송기 및 데이터 수신을 위한 수신기를 포함할 수 있다. 데이터 전송을 위해, 전송기는 변조된 라디오 주파수(RF) 신호를 획득하기 위해 데이터로 RF 캐리어 신호를 변조하고, 적절한 출력 전력 레벨을 갖는 증폭된 RF 신호를 획득하기 위해 변조된 RF 신호를 증폭하고, 안테나를 통해 기지국에 증폭된 RF 신호를 전송할 수 있다. 데이터 수신을 위해, 수신기는 안테나를 통해 수신된 RF 신호를 획득하고, 기지국에 의해 송신된 데이터를 복구하기 위해 수신된 RF 신호를 증폭 및 프로세싱할 수 있다.

[0003] 무선 디바이스는 넓은 주파수 범위 상의 동작을 지원할 수 있다. 무선 디바이스는 다수의 증폭기들을 포함할 수 있으며, 각각의 증폭기는 무선 디바이스에 의해 지원되는 넓은 주파수 범위의 부분 상에서 동작하도록 설계된다. 가능한 소수의 증폭기들로 넓은 주파수 범위 상의 동작을 지원하는 것이 바람직하다.

[0004] 도 1은 무선 시스템과 통신하는 무선 디바이스를 도시한다.

[0005] 도 2는 3개의 예시적인 대역 그룹들을 도시한다.

[0006] 도 3은 도 1의 무선 디바이스의 블록도를 도시한다.

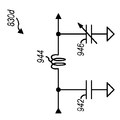

[0007] 도 4a 내지 도 4d는 공유된 소스 디제너레이션 인덕터를 갖는 전-대역 저 잡음 증폭기(LNA)를 도시한다.

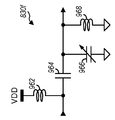

[0008] 도 5는 별개의 소스 디제너레이션 인덕터들을 갖는 전-대역 LNA를 도시한다.

[0009] 도 6은 소스 디제너레이션 인덕터가 없는 전-대역 LNA를 도시한다.

[0010] 도 7은 공유된 소스 디제너레이션 인덕터 및 피드백을 갖는 전-대역 LNA를 도시한다.

[0011] 도 8은 튜닝 가능한 매칭 회로를 갖는 전-대역 LNA를 도시한다.

[0012] 도 9a 내지 도 9f는 튜닝 가능한 매칭 회로의 6개의 예시적인 설계들을 도시한다.

[0013] 도 10은 3개의 대역 그룹들에 대한 3개의 변압기들의 상면도를 도시한다.

[0014] 도 11은 신호 증폭을 수행하기 위한 프로세스를 도시한다.

[0005] 도 2는 3개의 예시적인 대역 그룹들을 도시한다.

[0006] 도 3은 도 1의 무선 디바이스의 블록도를 도시한다.

[0007] 도 4a 내지 도 4d는 공유된 소스 디제너레이션 인덕터를 갖는 전-대역 저 잡음 증폭기(LNA)를 도시한다.

[0008] 도 5는 별개의 소스 디제너레이션 인덕터들을 갖는 전-대역 LNA를 도시한다.

[0009] 도 6은 소스 디제너레이션 인덕터가 없는 전-대역 LNA를 도시한다.

[0010] 도 7은 공유된 소스 디제너레이션 인덕터 및 피드백을 갖는 전-대역 LNA를 도시한다.

[0011] 도 8은 튜닝 가능한 매칭 회로를 갖는 전-대역 LNA를 도시한다.

[0012] 도 9a 내지 도 9f는 튜닝 가능한 매칭 회로의 6개의 예시적인 설계들을 도시한다.

[0013] 도 10은 3개의 대역 그룹들에 대한 3개의 변압기들의 상면도를 도시한다.

[0014] 도 11은 신호 증폭을 수행하기 위한 프로세스를 도시한다.

[0015] 아래에 제시되는 상세한 설명은 본 개시의 예시적인 설계들의 설명으로서 의도되며 본 개시가 실시될 수 있는 유일한 설계들만을 표현하도록 의도되는 것은 아니다. "예시적인" 이란 용어는 "예, 인스턴스 또는 예시로서 작용하는 것"을 의미하도록 본 명세서에서 이용된다. "예시적인" 것으로서 본 명세서에서 설명되는 임의의 설계는 반드시 다른 설계들보다 선호되거나 유리한 것으로서 해석될 필요는 없다. 상세한 설명은 본 개시의 예시적인 설계들의 완전한 이해를 제공하기 위한 특정한 세부사항들을 포함한다. 본 명세서에서 설명되는 예시적인 설계들은 이들 특정한 세부사항들 없이 실시될 수 있다는 것이 당업자들에게 자명할 것이다. 몇몇 인스턴스들에서, 잘 알려진 구조들 및 디바이스들은 본 명세서에서 제시되는 예시적인 설계들의 신규성을 모호하게 하지 않도록 블록도 형태로 도시된다.

[0016] 다수의 대역 그룹들을 커버하는 넓은 주파수 범위를 지원하는 전-대역 증폭기들이 본 명세서에서 개시된다. 전-대역 증폭기들은 또한 유니버셜 증폭기들(universal amplifiers) 등으로서 또한 지칭될 수 있다. 전-대역 증폭기들은 무선 통신 디바이스들과 같은 다양한 타입들의 전자 디바이스들에 대해 이용될 수 있다.

[0017]도 1은 무선 통신 시스템(120)과 통신하는 무선 디바이스(110)를 도시한다. 무선 시스템(120)은 LTE(Long Term Evolution) 시스템, CDMA(Code Division Multiple Access) 시스템, GSM(Global System for Mobile Communications) 시스템, WLAN(wireless local area network) 시스템, 또는 몇몇 다른 무선 시스템일 수 있다. CDMA 시스템은 WCDMA(Wideband CDMA), CDMA 1X, EVDO(Evolution-Data Optimized), TD-SCDMA(Time Division Synchronous CDMA), 또는 몇몇 다른 버전의 CDMA를 구현할 수 있다. 단순함을 위해, 도 1은 2개의 기지국들(130 및 132) 및 하나의 시스템 제어기(140)를 포함하는 무선 시스템(120)을 도시한다. 일반적으로, 각각의 무선 시스템은 임의의 수의 기지국들 및 임의의 세트의 네트워크 엔티티들을 포함할 수 있다.

[0018] 무선 디바이스(110)는 사용자 장비(UE), 모바일 스테이션, 단말, 액세스 단말, 가입자 유닛, 스테이션 등으로서 또한 지칭될 수 있다. 무선 디바이스(110)는 셀룰러 전화, 스마트폰, 태블릿, 무선 모뎀, 개인용 디지털 보조기기(PDA), 핸드헬드 디바이스, 랩톱 컴퓨터, 스마트북, 넷북, 코드리스 전화, 무선 로컬 루프(WLL) 스테이션, 블루투스 디바이스 등일 수 있다. 무선 디바이스(110)는 무선 시스템(120)과 통신할 수 있다. 무선 디바이스(110)는 브로드캐스트 스테이션들(예를 들어, 브로드캐스트 스테이션(134))로부터의 신호들, 하나 또는 그 초과의 GNSS(global navigation satellite systems)에서 위성들(예를 들어, 위성(150))로부터의 신호들 등을 또한 수신할 수 있을 수 있다. 무선 디바이스(110)는 LTE, WCDMA, CDMA 1X, EVDO, TD-SCDMA, GSM, 802.11 등과 같은 무선 통신을 위한 하나 또는 그 초과의 라디오 기술들을 지원할 수 있다.

[0019] 도 2는 무선 디바이스(110)에 의해 지원될 수 있는 3개의 예시적인 대역 그룹들을 도시한다. 무선 디바이스(110)는 1000MHz(megahertz) 보다 낮은 주파수들을 커버하는 저-대역(LB), 1000 MHz 내지 2300 MHz의 주파수들을 커버하는 중-대역(MB) 및/또는 2300 MHz보다 높은 주파수들을 커버하는 고-대역(HB)에서 동작할 수 있을 수도 있다. 예를 들어, 도 2에서 도시된 바와 같이, 저-대역은 698 내지 960 MHz를 커버할 수 있고, 중-대역은 1475 MHz 내지 2170 MHz를 커버할 수 있고 고-대역은 2300 MHz 내지 2690 MHz 및 3400 MHz 내지 3800 MHz를 커버할 수 있다. 저-대역, 중-대역 및 고-대역은 대역들의 3개의 그룹들(또는 대역 그룹들)을 지칭하며, 각각의 대역 그룹은 다수의 주파수 대역들(또는 단순히 "대역들")을 포함한다. 각각의 대역은 200MHz까지 커버할 수 있다. LTE 릴리즈 11은 LTE/UMTS 대역들로서 지칭되고 3GPP TS 36.101에서 나열되는 35개의 대역들을 지원한다.

[0020] 일반적으로, 임의의 수의 대역 그룹들이 정의될 수 있다. 각각의 대역 그룹은, 도 2에서 도시된 주파수 범위들 중 임의의 것에 매칭하거나 매칭하지 않을 수 있는 임의의 주파수들의 범위를 커버할 수 있다. 각각의 대역 그룹은 또한 임의의 수의 대역들을 포함할 수 있다.

[0021] 도 3은 도 1의 무선 디바이스(110)의 예시적인 설계의 블록도를 도시한다. 예시적인 설계에서, 무선 디바이스(110)는 주 안테나(310)에 커플링되는 트랜시버(320), 보조 안테나(312)에 커플링되는 트랜시버들(322) 및 데이터 프로세서/제어기(380)를 포함한다. 트랜시버(320)는 다수의 주파수 대역들, 다수의 라디오 기술들, 캐리어 어그리게이션들 등을 지원하기 위해 다수(K개)의 수신기들(330pa 내지 330pk) 및 다수(K개)의 전송기들(350p 내지 350p)을 포함한다. 트랜시버들(322)은 다수의 주파수 대역들, 다수의 라디오 기술들, 캐리어 어그리게이션들, 수신 다이버시티, 다수의 전송 안테나들로부터 다수의 수신 안테나들로의 MIMO(multiple-input multiple-output) 전송 등을 지원하기 위해 L개의 수신기들(330sa 내지 330sl) 및 L개의 전송기들(350sa 내지 350sl)을 포함한다.

[0022] 도 3에서 도시된 예시적인 설계에서, 각각의 수신기(330)는 LNA(340), 및 수신 회로들(342)을 포함한다. 데이터 수신을 위해, 안테나(310)는 기지국들 및/또는 다른 전송기 스테이션들로부터 신호들을 수신하고, 안테나 인터페이스 회로(324)를 통해 라우팅되고 선택된 수신기에 입력 RF 신호로서 제공되는 수신된 RF 신호를 제공한다. 안테나 인터페이스 회로(324)는 스위치들, 듀플렉서들, 전송 필터들, 수신 필터들, 매칭 회로들 등을 포함할 수 있다. 아래의 설명은 수신기(330pa)가 선택된 수신기라고 가정한다. 수신기(330pa) 내에서, LNA(340pa)는 입력 RF 신호를 증폭하고 출력 RF 신호를 제공한다. 수신 회로들(342pa)은 출력 RF 신호를 RF로부터 기저대역으로 하향변환하고, 하향변환된 신호를 증폭 및 필터링하고 아날로그 입력 신호를 데이터 프로세서(380)에 제공한다. 수신 회로들(342pa)은 믹서들, 필터들, 증폭기들, 매칭 회로들, 발진기, 로컬 발진기(LO) 생성기, 위상 동기 루프(PLL) 등을 포함할 수 있다. 트랜시버들(320 및 322)의 각각의 잔여 수신기(330)는 수신기(330pa)와 유사한 방식으로 동작할 수 있다.

[0023] 도 3에서 도시된 예시적인 설계에서, 각각의 전송기(350)는 전송 회로들(352), 및 전력 증폭기(PA)(354)를 포함한다. 데이터 전송을 위해, 데이터 프로세서(380)는 전송될 데이터를 프로세싱(예를 들어, 인코딩 및 변조)하고 아날로그 출력 신호를 선택된 전송기에 제공한다. 아래의 설명은 전송기(350pa)가 선택된 전송기라고 가정한다. 전송기(350pa) 내에서, 전송 회로들(352pa)은 아날로그 출력 신호를 기저대역으로부터 RF로 증폭, 필터링 및 상향변환하고 변조된 RF 신호를 제공한다. 전송 회로(352pa)는 믹서들, 증폭기들, 필터들, 매칭 회로들, 발진기, LO 생성기, PLL 등을 포함할 수 있다. PA(354pa)는 변조된 RF 신호를 수신 및 증폭하고 적절한 출력 전력 레벨을 갖는 전송 RF 신호를 제공한다. 전송 RF 신호는 안테나 인터페이스 회로(324)를 통해 라우팅되고 안테나(310)를 통해 전송된다. 트랜시버들(320 및 322)의 각각의 잔여 전송기(350)는 전송기(350pa)와 유사한 방식으로 동작할 수 있다.

[0024] 도 3은 수신기(330) 및 전송기(350)의 예시적인 설계를 도시한다. 수신기 및 전송기는 또한 필터, 매칭 회로들 등과 같이 도 3에서 도시되지 않은 다른 회로들을 포함할 수 있다. 트랜시버들(320 및 322) 중 일부 또는 모두 다는 하나 또는 그 초과의 아날로그 집적 회로들(IC들), RF IC들(RFIC들), 믹싱된-신호 IC들 등 상에서 구현될 수 있다. 예를 들어, LNA들(340) 및 수신 회로들(342)은 RFIC 등일 수 있는 하나의 모듈 상에서 구현될 수 있다. 트랜시버들(320 및 322) 내의 회로들은 또한 다른 방식으로 구현될 수 있다.

[0025] 데이터 프로세서/제어기(380)는 무선 디바이스(110)에 대한 다양한 기능들을 수행할 수 있다. 예를 들어, 데이터 프로세서(380)는 수신기들(330)을 통해 수신되는 데이터 및 전송기들(350)을 통해 전송되는 데이터에 대한 프로세싱을 수행할 수 있다. 제어기(380)는 트랜시버들(320 및 322) 내의 다양한 회로들의 동작을 제어할 수 있다. 메모리(382)는 데이터 프로세서/제어기(380)에 대한 프로그램 코드들 및 데이터를 저장할 수 있다. 데이터 프로세서/제어기(380)는 하나 또는 그 초과의 주문형 집적 회로들(ASIC들) 및/또는 다른 IC들 상에 구현될 수 있다.

[0026] 무선 디바이스(110)는 다수의 대역 그룹들, 다수의 라디오 기술들 및/또는 다수의 안테나들을 지원할 수 있다. 무선 디바이스(110)는 다수의 대역 그룹들, 다수의 라디오 기술들 및/또는 다수의 안테나들을 통한 수신을 지원하도록 다수의 LNA들을 포함할 수 있다.

[0027] 본 개시의 양상에서, 전-대역 LNA들은 다수의 대역 그룹들을 통한 수신을 지원하는데 이용될 수 있다. 전-대역 LNA는 다수의 대역 그룹들을 지원하는 LNA이고 (i) 모든 지원되는 대역 그룹들에 대한 단일 입력 및 (ii) 다수의 대역 그룹들에 대한 다수의 출력들, 예를 들어, 각각의 대역 그룹에 대한 하나의 출력을 갖는다. 전-대역 LNA는 그의 입력에서 입력 RF 신호를 수신하고 그의 다수의 출력들 중 하나에서 출력 RF 신호를 제공할 수 있다. 전-대역 LNA는 다수의 대역 그룹들을 커버하며, 동일한 대역 그룹 내의 다수의 대역들을 커버하는 다중-대역 LNA와 상이하다.

[0028] 전-대역 LNA들은 다양한 회로 설계들로 구현될 수 있다. 전-대역 LNA들의 몇몇 예시적인 설계들이 아래에서 설명된다. 전-대역 LNA들은 또한 다양한 타입들의 트랜지스터들로 구현될 수 있다. NMOS(N-channel metal oxide semiconductor) 트랜지스터들로 구현되는 전-대역 LNA들의 몇몇 예시적인 설계들이 아래에서 설명된다.

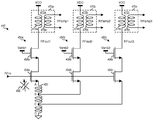

[0029] 도 4a는 공유된 소스 디제너레이션 인덕터를 갖는 전-대역 LNA(440)의 예시적인 설계의 개략도를 도시한다. 전-대역 LNA(440)는 도 3의 LNA들(340) 중 임의의 것에 대해 이용될 수 있다. 도 4a에서 도시된 예시적인 설계에서, 전-대역 LNA(440)는 각각, 저-대역, 중-대역 및 고-대역의 3개의 대역 그룹들에 대한 증폭기 회로들(450a, 450b 및 450c)을 포함한다.

[0030] 도 4a에서 도시된 예시적인 설계에서, 각각의 증폭기 회로(450)는 캐스코드 트랜지스터(456)에, 그리고 또한 다중-탭 소스 디제너레이션 인덕터(452)에 커플링되는 이득 트랜지스터(454)를 포함한다. 저-대역에 대한 증폭기 회로(450a) 내에서, 이득 트랜지스터(454a)는 입력 RF 신호(RFin)를 수신하는 그의 게이트 및 다중-탭 인덕터(452)의 한 단부에 커플링되는 그의 소스를 갖는다. 다중-탭 인덕터(452)는 4개의 탭들(A, B, C 및 D)을 갖고, 탭들(A 및 D)은 인덕터(452)의 2개의 단부들에 대응한다. 인덕터(452)는 이득 트랜지스터(454a)의 소스에 커플링되는 탭(A) 및 회로 접지에 커플링되는 탭(D)을 갖는다. 캐스코드 트랜지스터(456a)는 이득 트랜지스터(454a)의 드레인에 커플링되는 그의 소스, 저-대역에 대한 제 1 인에이블 제어 신호(Venb1)를 수신하는 그의 게이트 및 증폭기 회로(450a)의 출력에 커플링되는 그의 드레인을 갖는다.

[0031] 중-대역에 대한 증폭기 회로(450b)는, 저-대역에 대한 증폭기 회로(450a)에서의 이득 트랜지스터(454a) 및 캐스코드 트랜지스터(456a)와 유사한 방식으로 커플링되는 이득 트랜지스터(454b) 및 캐스코드 트랜지스터(456b)를 포함한다. 고-대역에 대한 증폭기 회로(450c)는, 저-대역에 대한 증폭기 회로(450a)에서의 이득 트랜지스터(454a) 및 캐스코드 트랜지스터(456a)와 유사한 방식으로 또한 커플링되는 이득 트랜지스터(454c) 및 캐스코드 트랜지스터(456c)를 포함한다. 중-대역에 대한 이득 트랜지스터(454b)의 소스는 다중-탭 인덕터(452)의 탭(B)에 커플링되고, 고-대역에 대한 이득 트랜지스터(454c)의 소스는 다중-탭 인덕터(452)의 탭(C)에 커플링된다. 이득 트랜지스터들(454a 내지 454c) 및 캐스코드 트랜지스터들(456a 내지 456c)은 도 4a에서 도시된 바와 같이 NMOS 트랜지스터들로, 또는 다른 타입들의 트랜지스터들로 구현될 수 있다.

[0032] 인덕터(452)는, 인덕터(452)의 상이한 탭들에서의 그 연결로 인해 점점 더 작은 소스 인덕턴스를 관찰하는 3개의 모든 이득 트랜지스터(454a, 454b 및 454c)에 대한 소스 디제너레이션 인덕터들로서의 역할을 한다. 특히, 고-대역에 대한 이득 트랜지스터(454c)는 회로 접지에 가장 근접한 탭(C)에 커플링되고 이에 따라 최소 소스 디제너레이션 인덕턴스를 관찰한다. 중-대역에 대한 이득 트랜지스터(454b)는 더 높은 탭(B)에 커플링되고 이에 따라 더 큰 소스 디제너레이션 인덕턴스를 관찰한다. 저-대역에 대한 이득 트랜지스터(454a)는 탭(A)에서 인덕터(452)의 최상부 단부에 커플링되며, 이에 따라 최대 소스 디제너레이션 인덕턴스를 관찰한다.

[0033] 도 4a에서 도시된 예시적인 설계에서, 가변 커패시터(458)는 이득 트랜지스터(454a)의 게이트 및 소스에 걸쳐 존재할 수 있다. 커패시터(458)는 이득 트랜지스터들(454a, 454b 및 454c)의 기생 커패시턴스를 포함할 수 있다. 커패시터(458)는 또한, 이득 트랜지스터(454a)의 게이트와 소스 간에 커플링될 수 있고 전-대역 LNA(440)의 입력 임피던스를 미세-튜닝하는데 이용될 수 있는 스위칭 가능한 커패시터들의 뱅크(bank)를 포함할 수 있다. 각각의 스위칭 가능한 커패시터는 스위치와 직렬로 커플링되는 커패시터로 구현될 수 있다. 뱅크 내의 커패시터들은 전-대역 LNA(440)에 대한 양호한 입력 매칭을 획득하도록 선택될 수 있다.

[0034] 증폭기 회로들(450a, 450b 및 450c)은 3개의 로드 회로들(470a, 470b 및 470c)에 각각 커플링된다. 도 4a에서 도시된 예시적인 설계에서, 각각의 로드 회로(470)는 주 코일(474) 및 보조 코일(476)을 포함하는 변압기(472)를 포함한다. 코일은 또한 인덕터 코일, 권선, 도체 등으로서 지칭될 수 있다. 저-대역에 대한 로드 회로(470a) 내에서, 변압기(472a)는 (i) 증폭기 회로(450a)의 출력과 전원(VDD) 간에 커플링되는 주 코일(474a) 및 (ii) 제 1 차동 증폭된 RF 신호(RFamp1)를 저-대역에 대한 하향변환기(도 4a에서 도시되지 않음)에 제공하는 보조 코일(476a)을 포함한다. 중-대역에 대한 로드 회로(470b)는 (i) 증폭기 회로(450b)의 출력과 VDD 공급기 간에 커플링되는 주 코일(474b) 및 (ii) 제 2 차동 증폭된 RF 신호(RFamp2)를 중-대역에 대한 하향변환기(도 4a에서 도시되지 않음)에 제공하는 보조 코일(476b)을 갖는 변압기(472b)를 포함한다. 고-대역에 대한 로드 회로(470c)는 (i) 증폭기 회로(450c)의 출력과 VDD 공급기 간에 커플링되는 주 코일(474c) 및 (ii) 제 3 차동 증폭된 RF 신호(RFamp3)를 고-대역에 대한 하향변환기(도 4a에서 도시되지 않음)에 제공하는 보조 코일(476c)을 갖는 변압기(472c)를 포함한다. 변압기들(472a, 472b 및 472c)은 캐스코드 트랜지스터들(456a, 456b 및 456c)의 드레인에 각각 커플링된다. 변압기들(472a, 472b 및 472c)은 각각 저-대역, 중-대역 및 고-대역에 대해 양호한 성능을 제공하도록 설계될 수 있다.

[0035] 일 예시적인 설계에서, 각각의 로드 회로(470)는 별개의 하향변환기에 커플링될 수 있다. 다른 예시적인 설계에서, 다수의 로드 회로들(470)은 스위치들을 통해 공유 하향변환기에 커플링될 수 있다. 스위치들은 임의의 주어진 순간에 하나의 로드 회로로부터 공유 하향변환기로 증폭된 RF 신호를 전달하도록 제어될 수 있다. 양자의 예시적인 설계들에서, 각각의 하향변환기는 RF로부터 기저대역 또는 중간 주파수(IF) 중 어느 하나로의 증폭된 RF 신호의 직교 하향변환을 수행하는 2개의 믹서들을 포함할 수 있다.

[0036] 로드 회로들(470)은 또한 다른 방식으로 구현될 수 있다. 다른 예시적인 설계에서, 로드 회로는 인덕터 및 가능하게는, 증폭기 회로의 출력과 VDD 공급기 간에 커플링되는 커패시터를 포함할 수 있다. 또 다른 예시적인 설계에서, 로드 회로는 VDD 공급기에 커플링되는 그의 소스 및 캐스코드 트랜지스터(456)의 드레인에 커플링되는 그의 드레인을 갖는 PMOS(P-channel metal oxide semiconductor) 트랜지스터를 포함할 수 있다. PMOS 트랜지스터는 캐스코드 트랜지스터(456)에 대한 활성 로드를 제공할 수 있다.

[0037] 증폭기 회로들(450a, 450b 및 450c)은 다양한 방식들로 구현될 수 있다. 예시적인 설계에서, 이득 트랜지스터들(454a, 454b 및 454c)은 유사한 트랜지스터 크기들을 가질 수 있고, 캐스코드 트랜지스터들(456a, 456b 및 456c)도 또한 유사한 트랜지스터 크기들을 가질 수 있다. 다른 예시적인 설계에서, 이득 트랜지스터들(454a, 454b 및 454c)은 상이한 트랜지스터 크기들을 가질 수 있고 및/또는 캐스코드 트랜지스터들(456a, 456b 및 456c)은 상이한 트랜지스터 크기들을 가질 수 있다. 예시적인 설계에서, 이득 트랜지스터들(454a, 454b 및 454c)은, 3개의 모든 대역 그룹들에 대해 양호한 성능을 제공하도록 선택될 수 있는 유사한 바이어스 전류들을 가질 수 있다. 다른 예시적인 설계에서, 이득 트랜지스터들(454a, 454b 및 454c)은 상이한 바이어스 전류들을 가질 수 있다. 각각의 이득 트랜지스터(454)에 대한 바이어스 전류는 연관된 대역 그룹에 대해 양호한 성능을 제공하도록 선택될 수 있다.

[0038] 도 4a는 3개의 대역 그룹들에 대한 3개의 증폭기 회로들(450a, 450b 및 450c)을 포함하는 전-대역 LNA(440)를 도시한다. 전-대역 LNA는 더 적거나 더 많은 대역 그룹들에 대해 3개보다 더 적거나 더 많은 증폭기 회로들(450)을 포함할 수 있다.

[0039] 전-대역 LNA(440)는 3개의 모든 증폭기 회로들(450a, 450b 및 450c)에 인가되는 입력 RF 신호를 수신한다. 입력 RF 신호는 관심의 대역 그룹, 즉 선택된 대역 그룹에서 하나 또는 그 초과의 대역들의 하나 또는 그 초과의 전송들을 포함할 수 있다. 선택된 대역 그룹에 대한 증폭기 회로(450)는 입력 RF 신호를 증폭하고 선택된 대역 그룹에 대한 출력 RF 신호를 제공하도록 인에이블될 수 있다. 선택된 대역 그룹에 대한 로드 회로(470)는 인에이블된 증폭기 회로(450)로부터 출력 RF 신호를 수신하고 선택된 대역 그룹에 대한 증폭된 RF 신호를 제공할 수 있다. 다른 대역 그룹에 대한 잔여 증폭기 회로들(450)은 디스에이블될 수 있다.

[0040] 도 4b는 저-대역이 선택될 때 전-대역 LNA(440)의 동작을 도시한다. 이 경우에, 증폭기 회로(450a)는 캐스코드 트랜지스터(456a)의 게이트에서의 Venb1 신호 상에 적절한 바이어스 전압을 제공함으로써 저-대역에 대한 제 1 출력 RF 신호(RFout1)를 생성하도록 인에이블될 수 있다. 로드 회로(470a)는 RFout1 신호를 수신하고 저-대역에 대한 RFamp1 신호를 하향변환기에 제공한다. 이득 트랜지스터(454a)는 전체 인덕터(452)를 통해 큰 소스 디제너레이션 인덕턴스를 관찰한다. 증폭기 회로들(450b 및 450c)은 각각 캐스코드 트랜지스터들(456b 및 456c)의 게이트들에서의 Venb2 및 Venb3 신호들 상에 낮은 전압들을 제공함으로써 디스에이블된다.

[0041] 도 4c는 중-대역이 선택될 때 전-대역 LNA(440)의 동작을 도시한다. 이 경우에, 증폭기 회로(450b)는 캐스코드 트랜지스터(456b)의 게이트에서의 Venb2 신호 상에 적절한 바이어스 전압을 제공함으로써 중-대역에 대한 제 2 출력 RF 신호(RFout2)를 생성하도록 인에이블된다. 로드 회로(470b)는 RFout2 신호를 수신하고 중-대역에 대한 RFamp2 신호를 하향변환기에 제공한다. 이득 트랜지스터(454b)는 탭(B)으로부터 회로 접지까지; 인덕터(452)의 일부를 통해 중간 소스 디제너레이션 인덕턴스를 관찰한다. 증폭기 회로들(450a 및 450c)은 각각 캐스코드 트랜지스터들(456a 및 456c)의 게이트들에서의 Venb1 및 Venb3 신호들 상에 낮은 전압들을 제공함으로써 디스에이블된다.

[0042] 도 4d는 고-대역이 선택될 때 전-대역 LNA(440)의 동작을 도시한다. 이 경우에, 증폭기 회로(450c)는 캐스코드 트랜지스터(456c)의 게이트에서의 Venb3 신호 상에 적절한 바이어스 전압을 제공함으로써 고-대역에 대한 제 3 출력 RF 신호(RFout3)를 생성하도록 인에이블된다. 로드 회로(470c)는 RFout3 신호를 수신하고 고-대역에 대한 RFamp3 신호를 하향변환기에 제공한다. 이득 트랜지스터(454c)는 탭(C)으로부터 회로 접지까지 인덕터(452)의 일부를 통해 작은 소스 디제너레이션 인덕턴스를 관찰한다. 증폭기 회로들(450a 및 450b)은 각각 캐스코드 트랜지스터들(456a 및 456b)의 게이트들에서의 Venb1 및 Venb2 신호들 상에 낮은 전압들을 제공함으로써 디스에이블된다.

[0043] 예시적인 설계에서, 증폭기 회로의 이득 트랜지스터는 (i) 증폭기 회로가 인에이블될 때 포화 영역(saturation region)에서 또는 (ii) 증폭기 회로가 디스에이블될 때 선형 영역(linear region)에서 동작할 수 있다. 증폭기 회로가 디스에이블될 때 선형 영역에서 이득 트랜지스터를 동작시키는 것은 어느 증폭기 회로 또는 대역 그룹이 선택되었는지에 무관하게, 전-대역 LNA(440)의 입력 임피던스의 변화들을 감소시킬 수 있다. 이득 트랜지스터의 입력 커패시턴스(CIN)는 다음과 같이 표현될 수 있다:

증폭기 회로가 인에이블될 때,

증폭기 회로가 디스에이블될 때,

여기서 W는 폭이고 L은 이득 트랜지스터의 길이이고,

COX는 이득 트랜지스터의 게이트 산화물 커패시턴스이다.

[0044] 수학식 (1) 및 (2)에서 도시된 바와 같이, 증폭기 회로가 인에이블 또는 디스에이블되는지에 의존하여 이득 트랜지스터의 입력 임피던스의 유한의 변화(finite change)가 있을 수 있다. 그러나 전-대역 LNA(440)의 입력 임피던스는, 어느 증폭기 회로가 선택되었는지 무관하게 그리고 심지어 이득 트랜지스터의 입력 임피던스의 변화가 있어도 허용 가능한 제한들 내로 유지될 수 있다. 허용 가능한 제한들 내로 전-대역 LNA(440)의 입력 임피던스를 유지하는 것은 모든 대역 그룹들에 대한 전력 및/또는 임피던스 매칭을 개선할 수 있다.

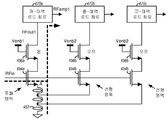

[0045] 도 5는 별개의 소스 디제너레이션 인덕터들을 갖는 전-대역 LNA(540)의 예시적인 설계의 개략도를 도시한다. 전-대역 LNA(540)는 또한 도 3의 LNA들(340) 중 임의의 하나에 대해 이용될 수 있다. 도 5에서 도시된 예시적인 설계에서, 전-대역 LNA(540)는 각각 저-대역, 중-대역, 및 고-대역에 대한 3개의 증폭기 회로들(550a, 550b 및 550c)을 포함한다. 각각의 증폭기 회로(550)는 캐스코드 트랜지스터(556)에 그리고 또한 소스 디제너레이션 인덕터(552)에 커플링되는 이득 트랜지스터(554)를 포함한다. 저-대역에 대한 증폭기 회로(550a) 내에서, 이득 트랜지스터(554a)는 입력 RF 신호를 수신하는 그의 게이트 및 인덕터(552a)의 한 단부에 커플링되는 그의 소스를 갖는다. 인덕터(552a)의 다른 단부는 회로 접지에 커플링된다. 캐스코드 트랜지스터(556a)는 이득 트랜지스터(554a)의 드레인에 커플링되는 그의 소스, 저-대역에 대한 제 1 인에이블 제어 신호(Venb1)를 수신하는 그의 게이트 및 증폭기 회로(550a)의 출력에 커플링되는 그의 드레인을 갖는다.

[0046] 중-대역에 대한 증폭기 회로(550b)는 저-대역에 대한 증폭기 회로(550a)에서의 이득 트랜지스터(554a), 캐스코드 트랜지스터(556a) 및 인덕터(552a)와 유사한 방식으로 커플링되는 이득 트랜지스터(554b), 캐스코드 트랜지스터(556b), 및 인덕터(552b)를 포함한다. 고-대역에 대한 증폭기 회로(550c)는 저-대역에 대한 증폭기 회로(550a)에서의 이득 트랜지스터(554a), 캐스코드 트랜지스터(556a) 및 인덕터(552a)와 유사한 방식으로 커플링되는 이득 트랜지스터(554c), 캐스코드 트랜지스터(556c), 및 인덕터(552c)를 포함한다. 인덕터들(552a, 552b 및 552c)은 각각 저-대역, 중-대역, 및 고-대역에 대해 양호한 성능을 제공하도록 설계된다. 캐스코드 트랜지스터들(556a, 556b, 및 556c)의 드레인들은 각각, (예를 들어, 도 4a에서 도시된 바와 같은) 변압기들 및/또는 다른 회로들을 포함할 수 있는 로드 회로들(570a, 570b 및 570c)에 커플링된다. 로드 회로들(570a, 570b 및 570c)은 각각 저-대역, 중-대역, 및 고-대역에 대한 양호한 성능을 제공하도록 설계될 수 있다.

[0047] 도 6은 소스 디제너레이션 인덕터가 없는 전-대역 LNA(640)의 예시적인 설계의 개략도를 도시한다. 전-대역 LNA(640)는 도 3의 LNA들(340) 중 임의의 하나에 대해 또한 이용될 수 있다. 도 6에서 도시된 예시적인 설계에서, 전-대역 LNA(640)는 공통 이득 트랜지스터(654) 및 각각 저-대역, 중-대역, 및 고-대역에 대한 3개의 캐스코드 트랜지스터들(656a, 656b, 및 656c)을 포함한다. 이득 트랜지스터(654)는 입력 RF 신호(RFin)를 수신하는 그의 게이트 및 회로 접지에 커플링되는 그의 소스를 갖는다. 캐스코드 트랜지스터(656a)는 이득 트랜지스터(654)의 드레인에 커플링되는 그의 소스, 저-대역에 대한 제 1 인에이블 제어 신호(Venb1)를 수신하는 그의 게이트 및 저-대역에 대한 로드 회로(670a)에 커플링되는 그의 드레인을 갖는다. 캐스코드 트랜지스터(656b)는 이득 트랜지스터(654)의 드레인에 커플링되는 그의 소스, 중-대역에 대한 제 2 인에이블 제어 신호(Venb2)를 수신하는 그의 게이트 및 중-대역에 대한 로드 회로(670b)에 커플링되는 그의 드레인을 갖는다. 캐스코드 트랜지스터(656c)는 이득 트랜지스터(654)의 드레인에 커플링되는 그의 소스, 고-대역에 대한 제 3 인에이블 제어 신호(Venb3)를 수신하는 그의 게이트 및 고-대역에 대한 로드 회로(670c)에 커플링되는 그의 드레인을 갖는다. 로드 회로들(670a, 670b 및 670c)은 (예를 들어, 도 4a에서 도시된 바와 같은) 변압기들 및/또는 다른 회로들을 포함할 수 있다. 로드 회로들(670a, 670b 및 670c)은 각각 저-대역, 중-대역, 및 고-대역에 대한 양호한 성능을 제공하도록 설계될 수 있다.

[0048] 도 7은 공유 소스 디제너레이션 인덕터 및 피드백을 갖는 전-대역 LNA(442)의 예시적인 설계의 개략도를 도시한다. 전-대역 LNA(442)는 또한 도 3의 LNA들(340) 중 임의의 하나에 대해 이용될 수 있다. 도 7에서 도시된 예시적인 설계에서, 전-대역 LNA(442)는 도 4a에 대해 위에서 설명된 바와 같이, 각각 저-대역, 중-대역, 및 고-대역에 대한 3개의 증폭기 회로들(450a, 450b 및 450c)을 포함한다. 전-대역 LNA(442)는 추가로 캐스코드 트랜지스터들(456a, 456b 및 456c)의 드레인들과 이득 트랜지스터들(454a, 454b 및 454c)의 게이트들 간에, 즉 공통 입력과 증폭기 회로들(450a, 450b 및 450c)의 출력들 간에 커플링되는 피드백 회로(460)를 포함한다.

[0049] 도 7에서 도시된 예시적인 설계에서, 피드백 회로(460)는 스위치들(462a, 462b, 및 462c), 레지스터(464), 및 커패시터(466)를 포함한다. 레지스터(464) 및 커패시터(466)는 직렬로 커플링되며, 커패시터(466)의 하부 단자는 이득 트랜지스터들(454a, 454b 및 454c)의 게이트들에 커플링된다. 스위치들(462a, 462b, 및 462c)은 레지스터(464)에 커플링되는 한 단자 및 캐스코드 트랜지스터들(456a, 456b 및 456c)의 드레인들에 각각 커플링되는 다른 단자를 갖는다. 스위치들(462a, 462b, 및 462c)은 그의 연관된 캐스코드 트랜지스터(456)에 피드백 회로(460)를 연결하도록 각각 폐쇄될 수 있고 연관된 캐스코드 트랜지스터(456)로부터 피드백 회로(460)를 연결해제하도록 개방될 수 있다. 피드백 회로(460)는 또한 트랜지스터와 같은 하나 또는 그 초과의 능동 회로들을 포함할 수 있다.

[0050] 예시적인 설계에서, 피드백 회로(460)는 인에이블되고 입력 전력 매칭을 제공하도록 저-대역에 대해 이용될 수 있다. 중-대역 및 고-대역에 대해, 피드백 회로(460)는 디스에이블되고, 소스 디제너레이션 인덕터(452)는 입력 전력 매칭을 위해 이용될 수 있다. 피드백 회로(460)는 또한 다른 방식들로 이용될 수 있다.

[0051] 피드백 회로(460)는 전-대역 LNA(442)에 대한 입력 매칭을 도울 수 있다. 피드백 회로(460)는 증폭기 회로들(450a, 450b 및/또는 450c)의 선형성을 또한 개선할 수 있다. 각각의 증폭기 회로(450)는 (i) 연관된 스위치(462)가 폐쇄될 때 소스 디제너레이션 인덕터(452) 및 피드백 회로(460) 둘 다에 의해, 또는 (ii) 연관된 스위치(462)가 개방될 때 오직 소스 디제너레이션 인덕터(452)에 의해서만 선형화될 수 있다. 피드백 회로(460)를 통한 개선된 선형성은 원하는 선형성을 획득하는데 더 작은 인덕터(452)가 이용되도록 허용할 수 있다.

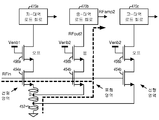

[0052] 도 8은 튜닝 가능한 매칭 회로(830)를 갖는 전-대역 LNA(840)의 예시적인 설계의 개략도를 도시한다. 전-대역 LNA(840)는 위에서 설명된 전-대역 LNA 설계들 중 임의의 것에 기초하여 구현될 수 있다. 전-대역 LNA(840)는 입력 RF 신호(RFin)를 수신하는 입력 및 K개의 대역 그룹들에 대한 출력 RF 신호들(RFout1 내지 RFoutK)을 제공하는 K개의 출력들을 포함하며, 여기서 K는 1보다 큰 임의의 정수값일 수 있다. 튜닝 가능한 매칭 회로(830)는 전-대역 LNA(840)의 입력에 커플링되고 LNA(840)의 입력 매칭을 수행한다. 매칭 회로(830)는 수신된 RF 신호(RFrx)를 수신하고 입력 RF 신호를 전-대역 LNA(840)에 제공한다. K개의 로드 회로들(870a 내지 870k)은 전-대역 LNA(840)의 K개의 출력들에 커플링되고 K개의 대역 그룹들에 대해 설계된다. 각각의 로드 회로(870)는 (예를 들어, 도 4a에서 도시된 바와 같은) 변압기 및/또는 다른 회로 컴포넌트들을 포함할 수 있다.

[0053] 튜닝 가능한 매칭 회로(830)는 다양한 방식들로 구현될 수 있다. 튜닝 가능한 매칭 회로(830)의 몇몇 예시적인 설계들이 하기에 설명된다.

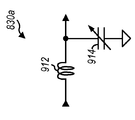

[0054] 도 9a는 L 토폴러지에 기초한 튜닝 가능한 매칭 회로(830a)의 예시적인 설계를 도시한다. L 토폴러지는 션트 회로 컴포넌트에 커플링되는 직렬 회로 컴포넌트를 포함한다. 직렬 회로 컴포넌트는 2개의 노드들 간에 연결된 회로 컴포넌트이다. 션트 회로 컴포넌트는 노드와 회로 접지 간에 연결되는 회로 컴포넌트이다. 회로 컴포넌트는 인덕터, 커패시터, 레지스터 등일 수 있다. 매칭 회로(830a)는 (i) 매칭 회로(830a)의 입력과 출력 간에 커플링되는 직렬 인덕터(912) 및 (ii) 회로 접지와 매칭 회로(830a)의 출력 간에 커플링되는 튜닝 가능한 션트 커패시터(914)를 포함한다.

[0055] 도 9b는 L 토폴러지에 기초한 튜닝 가능한 매칭 회로(830b)의 예시적인 설계를 도시한다. 매칭 회로(830b)는 (i) 매칭 회로(830b)의 입력과 출력 간에 커플링되는 튜닝 가능한 직렬 커패시터(922) 및 (ii) 회로 접지와 매칭 회로(830b)의 출력 간에 커플링되는 션트 인덕터(924)를 포함한다.

[0056] 도 9c는 R 토폴러지에 기초한 튜닝 가능한 매칭 회로(830c)의 예시적인 설계를 도시한다. R 토폴러지는 직렬 회로 컴포넌트에 커플링되는 션트 회로 컴포넌트를 포함한다. 매칭 회로(830c)는 (i) 회로 접지와 매칭 회로(830c)의 입력 간에 커플링되는 튜닝 가능한 션트 커패시터(932) 및 (ii) 매칭 회로(830c)의 입력과 출력 간에 커플링되는 직렬 인덕터(934)를 포함한다.

[0057] 도 9d는 Pi 토폴러지에 기초하여 튜닝 가능한 매칭 회로(830d)의 예시적인 설계를 도시한다. Pi 토폴러지는 다른 션트 회로 컴포넌트에 커플링되는 직렬 회로 컴포넌트에 커플링되는 션트 회로 컴포넌트를 포함한다. 매칭 회로(830d)는 (i) 매칭 회로(830d)의 입력과 회로 접지 간에 커플링되는 션트 커패시터(942), (ii) 매칭 회로(830d)의 출력과 입력 간에 커플링되는 직렬 인덕터(944) 및 (iii) 회로 접지와 매칭 회로(830d)의 출력 간에 커플링되는 튜닝 가능한 션트 커패시터(946)를 포함한다.

[0058] 도 9e는 2개의 R 섹션들을 갖는 튜닝 가능한 매칭 회로(830e)의 예시적인 설계를 도시한다. 매칭 회로(830e)는 (i) VDD 공급기와 매칭 회로(830e)의 입력 간에 커플링되는 션트 인덕터(952), (ii) 노드(E)와 매칭 회로(830e)의 입력 간에 커플링되는 직렬 커패시터(954), (iii) 노드(E)와 회로 접지 간에 커플링되는 튜닝 가능한 션트 커패시터(956) 및 (iv) 매칭 회로(830e)의 출력과 노드(E) 간에 커플링되는 직렬 인덕터(958)를 포함한다.

[0059] 도 9f는 Pi 토폴러지에 기초한 튜닝 가능한 매칭 회로(830f)의 예시적인 설계를 도시한다. 매칭 회로(830f)는 (i) VDD 공급기와 매칭 회로(830f)의 입력 간에 커플링되는 션트 인덕터(962), (ii) 매칭 회로(830f)의 입력과 출력 간에 커플링되는 직렬 커패시터(964), (iii) 회로 접지와 매칭 회로(830f)의 출력 간에 커플링되는 튜닝 가능한 션트 커패시터(966) 및 (iv) 회로 접지와 매칭 회로(830f)의 출력 간에 커플링되는 션트 인덕터(968)를 포함한다.

[0060] 고정된 매칭 회로는 또한 도 9a 내지 도 9f에서 도시된 예시적인 설계들 중 임의의 것에 기초하여 구현될 수 있다. 이 경우에, 각각의 조정 가능한 회로 컴포넌트(예를 들어, 각각의 조정 가능한 커패시터)는 고정된 회로 컴포넌트(예를 들어, 고정된 커패시터)로 대체될 수 있다.

[0061] 상이한 대역 그룹들에 대한 변압기들이 다양한 방식들로 구현될 수 있다. 변압기의 주 및 보조 코일들은 원하는 인덕턴스 및 커플링을 획득하도록 다양한 패턴들로 구현될 수 있다. 주 및 보조 코일들은 또한 하나 또는 그 초과의 전도성 층들 상에 제조될 수 있다.

[0062] 도 10은 3개의 대역 그룹들에 대한 3개의 변압기들의 예시적인 설계의 상면도를 도시한다. 3개의 변압기들은 도 4a의 변압기들(472a 내지 472c), 도 5의 로드 회로들(570a 내지 570c), 도 6의 로드 회로들(670a 내지 670c) 또는 도 8의 로드 회로들(870a 내지 870c)에 대해 이용될 수 있다.

[0063] 도 10에서 도시된 예시적인 설계에서, 저-대역에 대한 변압기는 제 1 전도성 층 상에 나선 패턴으로 형성되는 주 코일(1074a)을 포함한다. 중-대역에 대한 변압기는 제 1 전도성 층 상에 주 코일(1074a) 내부에 나선 패턴으로 형성되는 주 코일(1074b)을 포함한다. 고-대역에 대한 변압기는 제 1 전도성 층 상의 주 코일(1074b) 내부에 나선 패턴으로 형성되는 주 코일(1074c)을 포함한다. 접지 가드 링(1080)은 주 코일들(1074a 및 1074b) 간에 로케이팅되고 이들 두 주 코일들 간의 격리를 제공한다. 접지 가드 링(1082)은 주 코일들(1074b 및 1074c) 간에 로케이팅되고 이들 주 코일들 간에 격리를 제공한다.

[0064] 예시적인 설계에서, 3개의 변압기들에 대한 보조 코일들은 제 2 전도성 층 상에 나선 패턴으로 배열될 수 있다. 각각의 변압기(1072)에 대한 보조 코일은 그 변압기에 대한 주 코일 바로 아래 형성될 수 있다.

[0065] 도 10은, 3개의 대역 그룹들에 대한 3개의 변압기들에 대한 3개의 주 코일들(1074a, 1074b 및 1074c)이 다른 하나의 내부에 형성되는 예시적인 설계를 도시하며, 이는 공간을 절약할 수 있다. 일반적으로, 상이한 대역 그룹들에 대한 변압기들의 주 및 보조 코일들은 임의의 레이아웃, 임의의 패턴 및 임의의 수의 턴들로 구현될 수 있다. 턴들의 수, 턴들의 직경, 각각의 코일의 폭 및 높이, 각각의 변압기에 대한 주 및 보조 코일들 간의 간격 및/또는 2개의 코일들의 다른 속성들이 각각의 코일들에 대한 원하는 인덕턴스 및 품질 팩터(Q) 및 코일들 간의 원하는 커플링 계수를 획득하도록 선택될 수 있다. 커플링 계수는 코일들의 배치 및/또는 코일들 간의 거리를 제어함으로써 변동될 수 있다.

[0066] 도 10의 스택된 토폴러지는 변압기들이 더 작은 영역에서 제조되도록 허용하고 차동 설계들에 대해 보조 코일의 2개의 단부들 간의 매칭을 또한 더 양호하게 할 수 있다. 변압기들은 또한 나란히 있는(side-by-side) 토폴러지 또는 다른 토폴러지로 구현될 수 있다. 일반적으로, 상이한 토폴러지들, 레이아웃 패턴들 및 제조 기법들은 변압기에 대한 여러 이점들을 제공할 수 있다.

[0067] 본 명세서에서 설명되는 전-대역 증폭기들(예를 들어, LNA들)은 다양한 이점들을 제공할 수 있다. 첫째로, 전-대역 증폭기는 다수의 대역 그룹들을 커버하는 넓은 주파수 범위를 지원할 수 있으며, 이는 상이한 대역 그룹들에서 다수의 대역들을 지원하도록 요구되는 새로운 무선 디바이스들에 대해 매우 바람직할 수 있다. 둘째로, 전-대역 증폭기는, 예를 들어, 각각의 대역 그룹에 대한 변압기 및 소스 디제너레이션의 이용을 통해, 모든 지원되는 대역 그룹들에 대해, 양호한 성능을 가질 수 있다. 셋째로, 전-대역 증폭기는, 단일 입력/출력(I/O) 핀이 다수의 대역 그룹들을 지원하도록 입력 RF 신호를 제공할 수 있으므로, IC 칩 상의 I/O 핀들의 수를 감소시킬 수 있다. 넷째로, 전-대역 증폭기는, 각각의 I/O 핀이 임의의 대역 그룹을 지원하도록 구성될 수 있으므로 더 나은 유연성을 제공할 수 있다. 예를 들어, IC는 20개의 전-대역 LNA들을 포함할 수 있으며, (i) 20개의 저-대역 수신기들, 또는 (ii) 10개의 저-대역 수신기들, 5개의 중-대역 수신기들 및 5개의 고-대역 수신기들, 또는 (iii) 10개의 중-대역 수신기들 및 10개의 고-대역 수신기들 또는 (iv) 몇몇 다른 수신기들의 결합을 지원하도록 구성될 수 있다. 전-대역 증폭기들은 여러 이점들을 가질 수 있다.

[0068] 예시적인 설계에서, 장치(예를 들어, 무선 디바이스, IC, 회로 모듈 등)는 적어도 하나의 이득 트랜지스터 및 복수의 대역 그룹들에 대한 복수의 캐스코드 트랜지스터들을 포함할 수 있다. 적어도 하나의 이득 트랜지스터(예를 들어, 도 4a의 이득 트랜지스터(454))는 입력 RF 신호를 수신할 수 있고, 함께 커플링되는 입력(들)을 가질 수 있다. 복수의 캐스코드 트랜지스터들(예를 들어, 캐스코드 트랜지스터(456))은 적어도 하나의 이득 트랜지스터에 커플링될 수 있고, 복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 제공할 수 있다. 복수의 대역 그룹들은 저-대역, 중-대역 및/또는 고-대역을 포함할 수 있다. 각각의 대역 그룹은 복수의 대역들을 커버할 수 있다.

[0069] 도 4a에서 도시된 예시적인 설계에서, 적어도 하나의 이득 트랜지스터는 복수의 대역 그룹들에 대한 복수의 이득 트랜지스터들(예를 들어, 이득 트랜지스터들(454))을 포함할 수 있다. 복수의 이득 트랜지스터들 중 하나 및 복수의 캐스코드 트랜지스터들 중 하나는 입력 RF 신호를 증폭하고 선택된 대역 그룹에 대한 출력 RF 신호를 제공하도록 인에이블된다. 예시적인 설계에서, 복수의 이득 트랜지스터들은 상이한 트랜지스터 크기들 및/또는 상이한 바이어스 전류들을 가질 수 있다. 예시적인 설계에서, 장치는 복수의 이득 트랜지스터들 및 회로 접지에 커플링되는 복수의 탭들을 갖는 인덕터(예를 들어, 도 4a의 인덕터(452))를 더 포함할 수 있다. 다른 예시적인 설계에서, 장치는 복수의 이득 트랜지스터들과 회로 접지 간에 커플링되는 복수의 인덕터들(예를 들어, 도 5의 인덕터들(552))을 더 포함할 수 있다.

[0070] 도 6에서 도시된 다른 예시적인 설계에서, 적어도 하나의 이득 트랜지스터는 복수의 캐스코드 트랜지스터들에 커플링되는 단일 이득 트랜지스터(예를 들어, 이득 트랜지스터(654))를 포함할 수 있다. 이 이득 트랜지스터는 (예를 들어, 도 6에서 도시된 바와 같은) 회로 접지에 또는 소스 디제너레이션 인덕터에 직접 커플링되는 그의 소스를 가질 수 있다.

[0071] 예시적인 설계에서, 장치는 복수의 캐스코드 트랜지스터들 중 적어도 하나와 적어도 하나의 이득 트랜지스터 간에 커플링되는 피드백 회로(예를 들어, 도 7의 피드백 회로(460))를 포함할 수 있다. 피드백 회로는 레지스터, 또는 커패시터, 또는 트랜지스터, 또는 몇몇 다른 회로 컴포넌트, 또는 이들의 결합을 포함할 수 있다. 피드백 회로는 선택된 증폭기 회로 주위에 가까이, 예를 들어, 선택된 증폭기 회로에 대한 이득 트랜지스터와 캐스코드 트랜지스터 간에 있을 수 있다.

[0072] 예시적인 설계에서, 장치는 적어도 하나의 이득 트랜지스터에 커플링되는 튜닝 가능한 매칭 회로(예를 들어, 도 8의 튜닝 가능한 매칭 회로(830))를 더 포함할 수 있다. 튜닝 가능한 매칭 회로는 수신된 RF 신호를 수신하고 입력 RF 신호를 제공할 수 있다. 튜닝 가능한 매칭 회로는 적어도 하나의 조정 가능한 회로 컴포넌트(예를 들어, 조정 가능한 커패시터)를 포함할 수 있다.

[0073] 예시적인 설계에서, 장치는 복수의 캐스코드 트랜지스터들에 커플링되는 복수의 변압기들(예를 들어, 도 4a의 변압기들(472))을 더 포함할 수 있다. 복수의 변압기들 각각은 복수의 대역 그룹들 중 하나에 대해 이용될 수 있다.

[0074] 예시적인 설계에서, 적어도 하나의 이득 트랜지스터는 제 1 대역 그룹에 대한 제 1 이득 트랜지스터 및 제 2 대역 그룹에 대한 제 2 이득 트랜지스터를 포함할 수 있다. 복수의 캐스코드 트랜지스터들은 제 1 대역 그룹에 대한 제 1 캐스코드 트랜지스터 및 제 2 대역 그룹에 대한 제 2 캐스코드 트랜지스터를 포함할 수 있다. 제 1 이득 트랜지스터는 제 1 캐스코드 트랜지스터에 커플링될 수 있다. 제 2 이득 트랜지스터는 제 2 캐스코드 트랜지스터에 커플링될 수 있다. 인덕터는 제 1 이득 트랜지스터와 회로 접지 간에 커플링될 수 있고, 제 2 이득 트랜지스터에 커플링되는 탭을 포함할 수 있다. 제 1 대역 그룹에 대한 제 1 변압기는 제 1 캐스코드 트랜지스터에 커플링될 수 있다. 제 2 대역 그룹에 대한 제 2 변압기는 제 2 캐스코드 트랜지스터에 커플링될 수 있다. 제 1 변압기는 전도성 층 상에 형성되는 제 1 주 코일을 포함할 수 있다. 제 2 변압기는 (예를 들어, 도 10에서 도시된 바와 같이) 전도성 층 상의 제 1 주 코일 내에 형성되는 제 2 주 코일을 포함할 수 있다.

[0075] 예시적인 설계에서, 적어도 하나의 이득 트랜지스터는 제 3 대역 그룹에 대한 제 3 이득 트랜지스터를 더 포함할 수 있다. 복수의 캐스코드 트랜지스터들은 제 3 대역 그룹에 대한 제 3 캐스코드 트랜지스터를 더 포함할 수 있다. 제 3 이득 트랜지스터는 제 3 캐스코드 트랜지스터에 커플링될 수 있다. 제 3 대역 그룹에 대한 제 3 변압기는 제 3 캐스코드 트랜지스터에 커플링될 수 있다.

[0076] 도 11은 신호 증폭을 수행하기 위한 프로세스(1100)의 예시적인 설계를 도시한다. 입력 RF 신호는 증폭된 신호를 획득하도록 적어도 하나의 이득 트랜지스터 중 하나로 증폭될 수 있다(블록 1112). 증폭된 신호는 복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 획득하도록 복수의 대역 그룹들에 대한 복수의 캐스코드 트랜지스터들 중 하나로 버퍼링될 수 있다(블록 1114). 하나의 이득 트랜지스터의 소스는 적어도 하나의 이득 트랜지스터에 커플링되는 인덕터로 디제너레이팅될 수 있다(블록 1116). 출력 RF 신호는 증폭된 RF 신호를 획득하도록 복수의 대역 그룹들에 대한 복수의 변압기들 중 하나에 커플링될 수 있다(블록 1118).

[0077] 본 명세서에서 설명된 바와 같은 전-대역 증폭기들은 IC, 아날로그 IC, RF-IC, 혼합된-신호 IC, ASIC, PCB(printed circuit board), 전자 디바이스 등 상에 구현될 수 있다. 전-대역 증폭기들은 또한 CMOS(complementary metal oxide semiconductor), NMOS(N-channel MOS), PMOS(P-channel MOS), BJT(bipolar junction transistor), BiCMOS(bipolar-CMOS), SiGe(silicon germanium), GaAs(gallium arsenide), HBT들(heterojunction bipolar transistors), HEMT들(high electron mobility transistors), SOI(silicon-on-insulator) 등과 같은 다양한 IC 프로세스 기술들로 제조될 수 있다.

[0078] 본 명세서에서 설명된 전-대역 증폭기들을 구현하는 장치는 자립형 디바이스일 수 있거나, 또는 더 큰 디바이스의 부분일 수 있다. 디바이스는 (i) 자립형 IC, (ii) 데이터 및/또는 명령들을 저장하기 위한 메모리 IC들을 포함할 수 있는 하나 또는 그 초과의 IC들의 세트, (iii) RFR(RF receiver) 또는 RTR(RF transmitter/receiver)과 같은 RFIC, (iv) MSM(mobile station modem)과 같은 ASIC, (v) 다른 디바이스들 내에 임베딩될 수 있는 모듈, (vi) 수신기, 셀룰러 전화, 무선 디바이스, 핸드셋, 또는 모바일 유닛, (vii) 등일 수 있다.

[0079] 하나 또는 그 초과의 예시적인 설계들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 결합으로 구현될 수 있다. 소프트웨어로 구현되는 경우, 상기 기능들은 컴퓨터 판독 가능한 매체 상에 하나 또는 그 초과의 명령들 또는 코드로서 저장되거나, 또는 이들을 통해 전송될 수 있다. 컴퓨터 판독 가능한 매체는 컴퓨터 저장 매체, 및 일 장소에서 다른 장소로 컴퓨터 프로그램의 이전을 용이하게 하는 임의의 매체를 포함하는 통신 매체 둘 다를 포함한다. 저장 매체는 컴퓨터에 의해 액세스될 수 있는 임의의 가용한 매체일 수 있다. 예를 들어, 이러한 컴퓨터 판독 가능한 매체는 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장소, 자기 디스크 저장 또는 다른 자기 저장 디바이스들, 또는 명령 또는 데이터 구조의 형태로 원하는 프로그램 코드를 저장하거나 전달하는데 사용될 수 있고, 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있지만, 이들로 제한되는 것은 아니다. 또한, 임의의 연결 수단이 컴퓨터 판독 가능한 매체로 적절히 칭해질 수 있다. 예를 들어, 소프트웨어가 웹사이트, 서버, 또는 다른 원격 소스로부터 동축 케이블, 광섬유 케이블, 연선, 디지털 가입자 라인(DSL), 또는 적외선, 라디오, 및 마이크로웨이브와 같은 무선 기술들을 이용하여 전송되는 경우, 동축 케이블, 광섬유 케이블, 연선, DSL, 또는 적외선, 라디오, 및 마이크로웨이브와 같은 무선 기술들이 매체의 정의 내에 포함된다. 여기서 사용되는 디스크(disk) 및 디스크(disc)는 컴팩트 디스크(disc)(CD), 레이저 디스크(disc), 광 디스크(disc), 디지털 다용도 디스크(disc)(DVD), 플로피 디스크(disk), 및 블루-레이 디스크(disc)를 포함하며, 여기서 디스크(disk)는 보통 데이터를 자기적으로 재생하지만, 디스크(disc)는 레이저를 통해 광학적으로 데이터를 재생한다. 상기 것들의 조합들 역시 컴퓨터 판독 가능한 매체의 범위 내에 포함되어야 한다.

[0080]본 개시의 이전 설명은 임의의 당업자가 본 개시를 실시 또는 이용하는 것을 가능케 하기 위해 제공된다. 본 개시에 대한 다양한 수정들은 당업자들에게 쉽게 자명하게 될 것이며, 본 명세서에서 정의된 일반적인 원리들은 본 개시의 범위로부터 벗어남 없이 다른 변동물들에 적용될 수 있다. 따라서 본 개시는 본 명세서에서 설명된 예들 및 설계들로 제한되도록 의도되는 것이 아니라 본 명세서에서 기재된 원리들 및 신규한 특징들과 부합하는 최광의의 범위로 허여될 것이다.

Claims (21)

- 장치로서,

입력 라디오 주파수(RF) 신호를 수신하도록 구성된 적어도 하나의 이득 트랜지스터; 및

복수의 대역 그룹들에 대한 복수의 캐스코드 트랜지스터들

을 포함하며,

상기 복수의 캐스코드 트랜지스터들은 상기 적어도 하나의 이득 트랜지스터에 커플링되고 상기 복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 제공하도록 구성되는

장치. - 제 1 항에 있어서,

상기 적어도 하나의 이득 트랜지스터는,

상기 복수의 대역 그룹들에 대한 복수의 이득 트랜지스터들을 포함하는,

장치. - 제 2 항에 있어서,

상기 복수의 이득 트랜지스터들 및 회로 접지에 커플링되는 복수의 탭들을 포함하는 인덕터

를 더 포함하는,

장치. - 제 2 항에 있어서,

상기 복수의 이득 트랜지스터들과 회로 접지 간에 커플링되는 복수의 인덕터들

을 더 포함하는,

장치. - 제 1 항에 있어서,

상기 적어도 하나의 이득 트랜지스터는,

상기 복수의 캐스코드 트랜지스터들에 커플링되는 단일 이득 트랜지스터를 포함하는,

장치. - 제 1 항에 있어서,

상기 복수의 캐스코드 트랜지스터들 중 적어도 하나와 상기 적어도 하나의 이득 트랜지스터 간에 커플링되는 피드백 회로

를 더 포함하는,

장치. - 제 1 항에 있어서,

상기 적어도 하나의 이득 트랜지스터에 커플링되고 수신된 RF 신호를 수신하고 상기 입력 RF 신호를 제공하도록 구성되는 튜닝 가능한 매칭 회로(tunable matching circuit)

를 더 포함하는,

장치. - 제 1 항에 있어서,

상기 복수의 캐스코드 트랜지스터들에 커플링되는 복수의 변압기들

을 더 포함하고,

상기 복수의 변압기들 각각은 상기 복수의 대역 그룹들 중 하나에 대해 이용되는,

장치. - 제 1 항에 있어서,

상기 적어도 하나의 이득 트랜지스터는,

제 1 대역 그룹에 대한 제 1 이득 트랜지스터 및 제 2 대역 그룹에 대한 제 2 이득 트랜지스터를 포함하고,

상기 복수의 캐스코드 트랜지스터들은,

상기 제 1 대역 그룹에 대한 제 1 캐스코드 트랜지스터 및 상기 제 2 대역 그룹에 대한 제 2 캐스코드 트랜지스터를 포함하는,

장치. - 제 9 항에 있어서,

상기 제 1 이득 트랜지스터와 회로 접지 간에 커플링되고 상기 제 2 이득 트랜지스터에 커플링되는 탭을 포함하는 인덕터

를 더 포함하는,

장치. - 제 9 항에 있어서,

상기 제 1 캐스코드 트랜지스터에 커플링되는, 상기 제 1 대역 그룹에 대한 제 1 변압기, 및

상기 제 2 캐스코드 트랜지스터에 커플링되는, 상기 제 2 대역 그룹에 대한 제 2 변압기

를 더 포함하는,

장치. - 제 11 항에 있어서,

상기 제 1 변압기는 전도성 층 상에 형성되는 제 1 주 코일을 포함하고, 상기 제 2 변압기는 상기 전도성 층 상의 상기 제 1 주 코일 내에 형성되는 제 2 주 코일을 포함하는,

장치. - 제 9 항에 있어서,

상기 적어도 하나의 이득 트랜지스터는,

제 3 대역 그룹에 대한 제 3 이득 트랜지스터

를 더 포함하고,

상기 복수의 캐스코드 트랜지스터들은,

상기 제 3 대역 그룹에 대한 제 3 캐스코드 트랜지스터

를 더 포함하는,

장치. - 제 2 항에 있어서,

상기 복수의 이득 트랜지스터들은 상이한 트랜지스터 크기들 또는 상이한 바이어스 전류들 또는 이 둘 다를 갖는,

장치. - 제 1 항에 있어서,

상기 복수의 대역 그룹들은 저-대역, 중-대역, 및 고-대역 중 적어도 하나를 포함하는,

장치. - 방법으로서,

증폭된 신호를 획득하도록 적어도 하나의 이득 트랜지스터 중 하나로 입력 라디오 주파수(RF) 신호를 증폭하는 단계; 및

복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 획득하도록 상기 복수의 대역 그룹에 대한 복수의 캐스코드 트랜지스터들 중 하나로 증폭된 신호를 버퍼링하는 단계

를 포함하는,

방법. - 제 16 항에 있어서,

상기 적어도 하나의 이득 트랜지스터에 커플링되는 인덕터로 하나의 이득 트랜지스터의 소스를 디제너레이팅(degenerating)하는 단계

를 더 포함하는,

방법. - 제 16 항에 있어서,

증폭된 RF 신호를 획득하도록 상기 복수의 대역 그룹들에 대한 상기 출력 RF 신호를 복수의 변압기들 중 하나에 커플링하는 단계

를 더 포함하는,

방법. - 장치로서,

입력 라디오 주파수(RF) 신호를 수신하도록 구성된 적어도 하나의 증폭 수단; 및

복수의 대역 그룹들에 대한 복수의 버퍼링 수단

을 포함하며,

상기 복수의 대역 그룹들에 대한 복수의 버퍼링 수단은 상기 적어도 하나의 증폭 수단에 커플링되고 상기 복수의 대역 그룹들 중 하나에 대한 출력 RF 신호를 제공하도록 구성되는

장치. - 제 19 항에 있어서,

상기 적어도 하나의 증폭 수단은 상기 복수의 대역 그룹들에 대한 복수의 증폭 수단을 포함하고,

상기 장치는,

상기 복수의 증폭 수단 및 회로 접지에 커플링되는 복수의 탭들을 포함하는 소스 디제너레이션 수단

을 더 포함하는,

장치. - 제 19 항에 있어서,

상기 복수의 버퍼링 수단에 커플링되는 복수의 변압 수단

을 더 포함하고,

상기 복수의 변압 수단 각각은 상기 복수의 대역 그룹들 중 하나에 대해 이용되는,

장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/677,017 US9603187B2 (en) | 2012-11-14 | 2012-11-14 | Omni-band amplifiers |

| US13/677,017 | 2012-11-14 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150084908A true KR20150084908A (ko) | 2015-07-22 |

Family

ID=49725347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157015072A KR20150084908A (ko) | 2012-11-14 | 2013-11-12 | 전-대역 증폭기들 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9603187B2 (ko) |

| EP (2) | EP2920879B1 (ko) |

| JP (1) | JP2015534420A (ko) |

| KR (1) | KR20150084908A (ko) |

| CN (1) | CN104798299B (ko) |

| WO (1) | WO2014078333A2 (ko) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9473336B2 (en) * | 2014-05-16 | 2016-10-18 | Qualcomm Incorporated | Radio frequency (RF) front end having multiple low noise amplifier modules |

| US9723560B2 (en) | 2014-05-22 | 2017-08-01 | Qualcomm Incorporated | Multi-stage amplifier with RC network |

| US9479131B2 (en) | 2014-05-23 | 2016-10-25 | Qualcomm Incorporated | Carrier aggregation amplifier with dual gain control |

| US9300264B2 (en) | 2014-08-22 | 2016-03-29 | Mediatek Inc. | Receiver arrangement and method of performing operations of receiver |

| US9369097B2 (en) * | 2014-09-05 | 2016-06-14 | Qualcomm Incorporated | Multi-band low noise amplifier |

| US20160079946A1 (en) * | 2014-09-12 | 2016-03-17 | Qualcomm Incorporated | Multi-band low noise amplifier with a shared degeneration inductor |

| US9431963B2 (en) | 2014-09-19 | 2016-08-30 | Qualcomm Incorporated | Dual stage low noise amplifier for multiband receiver |

| US10211861B2 (en) * | 2015-03-17 | 2019-02-19 | Skyworks Solutions, Inc. | Multi-mode integrated front end module |

| US9608569B2 (en) | 2015-04-01 | 2017-03-28 | Qualcomm Incorporated | Linearizing scheme for baseband filter with active feedback |

| US9712195B2 (en) | 2015-05-13 | 2017-07-18 | Qualcomm Incorporated | Radio frequency low noise amplifier with on-chip matching and built-in tunable filter |

| CN106330099B (zh) * | 2015-06-30 | 2019-03-26 | 展讯通信(上海)有限公司 | 一种射频前端电路 |

| US9774303B1 (en) * | 2015-08-25 | 2017-09-26 | Marvell International Ltd. | Low-noise amplifier for intra-band non contiguous carrier agregation |

| US10177722B2 (en) | 2016-01-12 | 2019-01-08 | Qualcomm Incorporated | Carrier aggregation low-noise amplifier with tunable integrated power splitter |

| SG11201901799UA (en) | 2016-08-31 | 2019-03-28 | Skyworks Solutions Inc | Multi-input amplifier with degeneration switching block and low loss bypass function |

| GB2605900B (en) * | 2016-08-31 | 2023-02-08 | Skyworks Solutions Inc | Amplifier with improved return loss and mismatch over gain modes |

| US9800273B1 (en) | 2017-03-01 | 2017-10-24 | Qualcomm Incorporated | Wideband high linearity LNA with intra-band carrier aggregation support |

| US10038418B1 (en) | 2017-04-04 | 2018-07-31 | Psemi Corporation | Optimized multi gain LNA enabling low current and high linearity including highly linear active bypass |

| US11881828B2 (en) | 2017-04-04 | 2024-01-23 | Psemi Corporation | Tunable effective inductance for multi-gain LNA with inductive source degeneration |

| EP3461004B1 (en) * | 2017-09-20 | 2021-04-28 | Nxp B.V. | An amplifier and a wireless signal receiver comprising said amplifier |

| WO2019142526A1 (ja) * | 2018-01-19 | 2019-07-25 | ソニーセミコンダクタソリューションズ株式会社 | 増幅回路および受信回路 |

| US10797738B2 (en) * | 2018-10-26 | 2020-10-06 | Analog Devices, Inc. | Segmented receiver for wireless communications |

| CN110719074B (zh) * | 2019-09-23 | 2023-06-20 | 航天科工微电子系统研究院有限公司 | 一种可调谐的宽带低噪声放大器 |

| WO2022153926A1 (ja) * | 2021-01-13 | 2022-07-21 | 株式会社村田製作所 | 高周波回路および通信装置 |

| CN115459793A (zh) * | 2021-06-08 | 2022-12-09 | 开元通信技术(厦门)有限公司 | 一种射频装置 |

| US20230142523A1 (en) * | 2021-11-11 | 2023-05-11 | Samsung Electronics Co., Ltd. | Low noise amplifier and receiver |

| CN114553155B (zh) * | 2022-04-22 | 2022-08-16 | 成都嘉纳海威科技有限责任公司 | 一种覆盖基频的超宽带射频放大器 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5015968A (en) * | 1990-07-27 | 1991-05-14 | Pacific Monolithics | Feedback cascode amplifier |

| JP3563321B2 (ja) * | 2000-03-22 | 2004-09-08 | 日本電信電話株式会社 | マルチバンド高周波増幅回路 |

| US7023272B2 (en) | 2004-04-19 | 2006-04-04 | Texas Instruments Incorporated | Multi-band low noise amplifier system |

| US7508260B2 (en) * | 2005-08-24 | 2009-03-24 | Freescale Semiconductor, Inc. | Bypassable low noise amplifier topology with multi-tap transformer |

| US7474158B1 (en) | 2006-04-10 | 2009-01-06 | Rf Micro Devices, Inc. | Dynamic match low noise amplifier with reduced current consumption in low gain mode |

| KR100824783B1 (ko) * | 2006-10-17 | 2008-04-24 | 삼성전자주식회사 | 다중 대역용 저잡음 증폭기 및 다중 대역용 무선 신호수신기 |

| TWI327416B (en) | 2006-10-27 | 2010-07-11 | Nat Univ Tsing Hua | Cascode low noise amplifier with a source coupled active inductor |

| KR20080072383A (ko) | 2007-02-02 | 2008-08-06 | 삼성전자주식회사 | 실리콘 튜너 및 그 신호 처리 방법 |

| JP2009010826A (ja) * | 2007-06-29 | 2009-01-15 | Sony Corp | マルチバンド低雑音増幅器および無線通信装置 |

| KR100952666B1 (ko) * | 2008-02-01 | 2010-04-13 | (주)에프씨아이 | 커패시터 피드백을 이용한 재구성 가능 저잡음 증폭기 |

| JP5168495B2 (ja) * | 2008-12-12 | 2013-03-21 | ルネサスエレクトロニクス株式会社 | 電力増幅回路 |

| JP5296809B2 (ja) * | 2009-01-13 | 2013-09-25 | パナソニック株式会社 | 可変利得増幅器およびそれを備えた高周波信号受信装置 |

| US8022772B2 (en) * | 2009-03-19 | 2011-09-20 | Qualcomm Incorporated | Cascode amplifier with protection circuitry |

| KR20110060735A (ko) * | 2009-11-30 | 2011-06-08 | 한국전자통신연구원 | 고주파 변압기를 이용한 다중 대역 전력증폭기 |

| US8680940B2 (en) * | 2010-01-15 | 2014-03-25 | Wispry, Inc. | Tunable matching network circuit topology devices and methods |

| US8626084B2 (en) * | 2010-05-13 | 2014-01-07 | Qualcomm, Incorporated | Area efficient concurrent matching transceiver |

| US8310314B2 (en) * | 2010-09-06 | 2012-11-13 | Mediatek Inc. | Signal amplification circuits for receiving/transmitting signals according to input signal |

| KR101214761B1 (ko) * | 2011-09-19 | 2013-01-09 | 삼성전기주식회사 | 다중대역 증폭기 및 다중대역 증폭방법 |

| US8742853B2 (en) * | 2011-10-25 | 2014-06-03 | Marvell World Trade Ltd. | Low-stress cascode structure |

| US9154356B2 (en) | 2012-05-25 | 2015-10-06 | Qualcomm Incorporated | Low noise amplifiers for carrier aggregation |

| US9543903B2 (en) | 2012-10-22 | 2017-01-10 | Qualcomm Incorporated | Amplifiers with noise splitting |

-

2012

- 2012-11-14 US US13/677,017 patent/US9603187B2/en active Active

-

2013

- 2013-11-12 KR KR1020157015072A patent/KR20150084908A/ko not_active Application Discontinuation

- 2013-11-12 WO PCT/US2013/069752 patent/WO2014078333A2/en active Application Filing

- 2013-11-12 CN CN201380059119.XA patent/CN104798299B/zh active Active

- 2013-11-12 EP EP13802154.8A patent/EP2920879B1/en active Active

- 2013-11-12 JP JP2015542025A patent/JP2015534420A/ja active Pending

- 2013-11-12 EP EP22205538.6A patent/EP4164123A3/en active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN104798299A (zh) | 2015-07-22 |

| WO2014078333A3 (en) | 2014-07-17 |

| WO2014078333A2 (en) | 2014-05-22 |

| EP2920879B1 (en) | 2022-12-21 |

| US9603187B2 (en) | 2017-03-21 |

| EP4164123A2 (en) | 2023-04-12 |

| US20140134960A1 (en) | 2014-05-15 |

| EP2920879A2 (en) | 2015-09-23 |

| EP4164123A3 (en) | 2023-06-14 |

| JP2015534420A (ja) | 2015-11-26 |

| CN104798299B (zh) | 2018-01-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2920879B1 (en) | Omni-band amplifiers | |

| US9166852B2 (en) | Low noise amplifiers with transformer-based signal splitting for carrier aggregation | |

| KR101672356B1 (ko) | 다수의 출력들 및 구성 가능한 디제너레이션 인덕터를 갖는 증폭기들 | |

| US9837968B2 (en) | Amplifier circuits | |

| EP2974003B1 (en) | Amplifiers with inductive degeneration and configurable gain and input matching | |

| KR101650846B1 (ko) | 구성가능한 상호 커플링된 소스 디제너레이션 인덕터들을 갖는 증폭기들 | |

| US8903343B2 (en) | Single-input multiple-output amplifiers with independent gain control per output | |

| KR101636409B1 (ko) | 부스팅되거나 디부스팅된 소스 디제너레이션 인덕턴스를 갖는 증폭기들 | |

| US9548709B2 (en) | Independent gain control for multiple receive circuits concurrently processing different transmitted signals | |

| WO2018080711A1 (en) | Low gain linearization for high signal-to-noise ratio |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |