JP2015534420A - 全帯域増幅器 - Google Patents

全帯域増幅器 Download PDFInfo

- Publication number

- JP2015534420A JP2015534420A JP2015542025A JP2015542025A JP2015534420A JP 2015534420 A JP2015534420 A JP 2015534420A JP 2015542025 A JP2015542025 A JP 2015542025A JP 2015542025 A JP2015542025 A JP 2015542025A JP 2015534420 A JP2015534420 A JP 2015534420A

- Authority

- JP

- Japan

- Prior art keywords

- band

- coupled

- transistor

- signal

- gain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000007850 degeneration Effects 0.000 claims abstract description 28

- 238000000034 method Methods 0.000 claims description 9

- 230000003139 buffering effect Effects 0.000 claims 3

- 238000013461 design Methods 0.000 abstract description 75

- 239000003990 capacitor Substances 0.000 description 25

- 230000005540 biological transmission Effects 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 238000004891 communication Methods 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910044991 metal oxide Inorganic materials 0.000 description 3

- 150000004706 metal oxides Chemical class 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 230000002776 aggregation Effects 0.000 description 2

- 238000004220 aggregation Methods 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000004590 computer program Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W88/00—Devices specially adapted for wireless communication networks, e.g. terminals, base stations or access point devices

- H04W88/02—Terminal devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

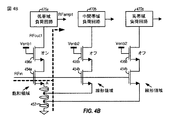

- H03F3/189—High-frequency amplifiers, e.g. radio frequency amplifiers

- H03F3/19—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only

- H03F3/193—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only with field-effect devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/68—Combinations of amplifiers, e.g. multi-channel amplifiers for stereophonics

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/005—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission adapting radio receivers, transmitters andtransceivers for operation on two or more bands, i.e. frequency ranges

- H04B1/0053—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission adapting radio receivers, transmitters andtransceivers for operation on two or more bands, i.e. frequency ranges with common antenna for more than one band

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

Abstract

Description

Claims (21)

- 入力無線周波数(RF)信号を受信するように構成された少なくとも1つの利得トランジスタと、

前記少なくとも1つの利得トランジスタに結合され、複数の帯域グループのうちの1つのための出力RF信号を供給するように構成された、前記複数の帯域グループのための複数のカスコードトランジスタと、

を備える、装置。 - 前記少なくとも1つの利得トランジスタは、前記複数の帯域グループのために複数の利得トランジスタを備える、請求項1に記載の装置。

- 前記複数の利得トランジスタと回路接地とに結合された複数のタップを備えるインダクタ

をさらに備える、請求項2に記載の装置。 - 前記複数の利得トランジスタと回路接地との間で結合された複数のインダクタ

をさらに備える、請求項2に記載の装置。 - 前記少なくとも1つの利得トランジスタは、前記複数のカスコードトランジスタに結合された単一の利得トランジスタを備える、請求項1に記載の装置。

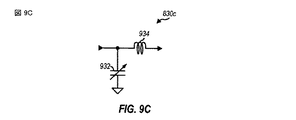

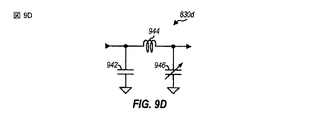

- 前記複数のカスコードトランジスタのうちの少なくとも1つと前記少なくとも1つの利得トランジスタとの間で結合されたフィードバック回路

をさらに備える、請求項1に記載の装置。 - 前記少なくとも1つの利得トランジスタに結合され、受信されたRF信号を受信することと、前記入力RF信号を提供することとを行うように構成された、調節可能な整合回路

をさらに備える、請求項1に記載の装置。 - 前記複数のカスコードトランジスタに結合された複数の変圧器をさらに備え、前記複数の変圧器の各々は、前記複数の帯域グループのうちの1つのために使用される、請求項1に記載の装置。

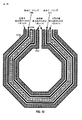

- 前記少なくとも1つの利得トランジスタは、第1の帯域グループのための第1の利得トランジスタと、第2の帯域グループのための第2の利得トランジスタとを備え、前記複数のカスコードトランジスタは、前記第1の帯域グループのための第1のカスコードトランジスタと前記第2の帯域グループのための第2のカスコードトランジスタとを備える、請求項1に記載の装置。

- 前記第1の利得トランジスタと回路接地との間で結合され、前記第2の利得トランジスタに結合されたタップを備える、インダクタ

をさらに備える、請求項9に記載の装置。 - 前記第1のカスコードトランジスタに結合された前記第1の帯域グループのための第1の変圧器と、

前記第2のカスコードトランジスタに結合された前記第2の帯域グループのための第2の変圧器と、

をさらに備える、請求項9に記載の装置。 - 前記第1の変圧器は、伝導レイヤ上で形成された第1の1次コイルを備え、前記第2の変圧器は、前記伝導レイヤ上の前記第1の1次コイル内で形成された第2の1次コイルを備える、請求項11に記載の装置。

- 前記少なくとも1つの利得トランジスタは、第3の帯域グループのための第3の利得トランジスタをさらに備え、前記複数のカスコードトランジスタは、前記第3の帯域グループのための第3のカスコードトランジスタをさらに備える、請求項9に記載の装置。

- 前記複数の利得トランジスタは、異なるトランジスタのサイズ、または異なるバイアス電流、または両方を有する、請求項2に記載の装置。

- 前記複数の帯域グループは、低帯域、中間帯域、および高帯域のうちの少なくとも1つを含む、請求項1に記載の装置。

- 増幅された信号を取得するために少なくとも1つの利得トランジスタのうちの1つを用いて入力無線周波数(RF)信号を増幅することと、

複数の帯域グループのうちの1つのために出力RF信号を取得するために前記複数の帯域グループのために複数のカスコードトランジスタのうちの1つを用いて前記増幅された信号をバッファリングすることと、

を備える、方法。 - 前記少なくとも1つの利得トランジスタに結合されたインダクタを用いて前記1つの利得トランジスタのソースをデジェネレートすること

をさらに備える、請求項16に記載の方法。 - 増幅されたRF信号を取得するために、前記出力RF信号を前記複数の帯域グループのための複数の変圧器のうちの1つと結合すること

をさらに備える、請求項16に記載の方法。 - 入力無線周波数(RF)信号を受信するように構成された少なくとも1つの増幅する手段と、

前記少なくとも1つの増幅する手段に結合され、複数の帯域グループのうちの1つのための出力RF信号を提供するように構成された、前記複数の帯域グループのための複数のバッファリングする手段と、

を備える、装置。 - 前記少なくとも1つの増幅する手段は、前記複数の帯域グループのための複数の増幅する手段を備え、前記装置は、

前記複数の増幅する手段と回路接地とに結合された複数のタップを備えるソースデジェネレーション手段

をさらに備える、請求項19に記載の装置。 - 前記複数のバッファリングする手段に結合された複数の変圧する手段をさらに備え、前記複数の変圧する手段の各々は、前記複数の帯域グループのうちの1つのために使用される、請求項19に記載の装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/677,017 | 2012-11-14 | ||

| US13/677,017 US9603187B2 (en) | 2012-11-14 | 2012-11-14 | Omni-band amplifiers |

| PCT/US2013/069752 WO2014078333A2 (en) | 2012-11-14 | 2013-11-12 | Omni-band amplifiers |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015534420A true JP2015534420A (ja) | 2015-11-26 |

| JP2015534420A5 JP2015534420A5 (ja) | 2016-12-08 |

Family

ID=49725347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015542025A Pending JP2015534420A (ja) | 2012-11-14 | 2013-11-12 | 全帯域増幅器 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9603187B2 (ja) |

| EP (2) | EP2920879B1 (ja) |

| JP (1) | JP2015534420A (ja) |

| KR (1) | KR20150084908A (ja) |

| CN (1) | CN104798299B (ja) |

| WO (1) | WO2014078333A2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019142526A1 (ja) * | 2018-01-19 | 2019-07-25 | ソニーセミコンダクタソリューションズ株式会社 | 増幅回路および受信回路 |

| JP2019528657A (ja) * | 2016-08-31 | 2019-10-10 | スカイワークス ソリューションズ, インコーポレイテッドSkyworks Solutions, Inc. | デジェネレーションスイッチングブロック及び低損失バイパス機能を有するマルチ入力増幅器 |

| WO2022153926A1 (ja) * | 2021-01-13 | 2022-07-21 | 株式会社村田製作所 | 高周波回路および通信装置 |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9473336B2 (en) * | 2014-05-16 | 2016-10-18 | Qualcomm Incorporated | Radio frequency (RF) front end having multiple low noise amplifier modules |

| US9723560B2 (en) | 2014-05-22 | 2017-08-01 | Qualcomm Incorporated | Multi-stage amplifier with RC network |

| US9479131B2 (en) | 2014-05-23 | 2016-10-25 | Qualcomm Incorporated | Carrier aggregation amplifier with dual gain control |

| US9300264B2 (en) | 2014-08-22 | 2016-03-29 | Mediatek Inc. | Receiver arrangement and method of performing operations of receiver |

| US9369097B2 (en) * | 2014-09-05 | 2016-06-14 | Qualcomm Incorporated | Multi-band low noise amplifier |

| US20160079946A1 (en) * | 2014-09-12 | 2016-03-17 | Qualcomm Incorporated | Multi-band low noise amplifier with a shared degeneration inductor |

| US9431963B2 (en) | 2014-09-19 | 2016-08-30 | Qualcomm Incorporated | Dual stage low noise amplifier for multiband receiver |

| US10211861B2 (en) * | 2015-03-17 | 2019-02-19 | Skyworks Solutions, Inc. | Multi-mode integrated front end module |

| US9608569B2 (en) | 2015-04-01 | 2017-03-28 | Qualcomm Incorporated | Linearizing scheme for baseband filter with active feedback |

| US9712195B2 (en) | 2015-05-13 | 2017-07-18 | Qualcomm Incorporated | Radio frequency low noise amplifier with on-chip matching and built-in tunable filter |

| CN106330099B (zh) * | 2015-06-30 | 2019-03-26 | 展讯通信(上海)有限公司 | 一种射频前端电路 |

| US9774303B1 (en) * | 2015-08-25 | 2017-09-26 | Marvell International Ltd. | Low-noise amplifier for intra-band non contiguous carrier agregation |

| US10177722B2 (en) | 2016-01-12 | 2019-01-08 | Qualcomm Incorporated | Carrier aggregation low-noise amplifier with tunable integrated power splitter |

| GB2605901B (en) * | 2016-08-31 | 2023-02-08 | Skyworks Solutions Inc | Amplifer with improved return loss and mismatch over gain modes |

| US9800273B1 (en) | 2017-03-01 | 2017-10-24 | Qualcomm Incorporated | Wideband high linearity LNA with intra-band carrier aggregation support |

| US11881828B2 (en) | 2017-04-04 | 2024-01-23 | Psemi Corporation | Tunable effective inductance for multi-gain LNA with inductive source degeneration |

| US10038418B1 (en) | 2017-04-04 | 2018-07-31 | Psemi Corporation | Optimized multi gain LNA enabling low current and high linearity including highly linear active bypass |

| EP3461004B1 (en) * | 2017-09-20 | 2021-04-28 | Nxp B.V. | An amplifier and a wireless signal receiver comprising said amplifier |

| US10797738B2 (en) * | 2018-10-26 | 2020-10-06 | Analog Devices, Inc. | Segmented receiver for wireless communications |

| CN110719074B (zh) * | 2019-09-23 | 2023-06-20 | 航天科工微电子系统研究院有限公司 | 一种可调谐的宽带低噪声放大器 |

| CN115459793A (zh) * | 2021-06-08 | 2022-12-09 | 开元通信技术(厦门)有限公司 | 一种射频装置 |

| US20230142523A1 (en) * | 2021-11-11 | 2023-05-11 | Samsung Electronics Co., Ltd. | Low noise amplifier and receiver |

| CN114553155B (zh) * | 2022-04-22 | 2022-08-16 | 成都嘉纳海威科技有限责任公司 | 一种覆盖基频的超宽带射频放大器 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080096516A1 (en) * | 2006-10-17 | 2008-04-24 | Samsung Electronics Co., Ltd. | Multi-band low noise amplifier and multi-band radio frequency receiver including the same |

| US7474158B1 (en) * | 2006-04-10 | 2009-01-06 | Rf Micro Devices, Inc. | Dynamic match low noise amplifier with reduced current consumption in low gain mode |

| JP2009010826A (ja) * | 2007-06-29 | 2009-01-15 | Sony Corp | マルチバンド低雑音増幅器および無線通信装置 |

| US20090195316A1 (en) * | 2008-02-01 | 2009-08-06 | Silicon Motion, Inc. | Re-configurable low noise amplifier utilizing feedback capacitors |

| JP2010141673A (ja) * | 2008-12-12 | 2010-06-24 | Renesas Technology Corp | 電力増幅回路 |

| WO2011143504A1 (en) * | 2010-05-13 | 2011-11-17 | Qualcomm Incorporated | Area efficient concurrent matching transceiver |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5015968A (en) * | 1990-07-27 | 1991-05-14 | Pacific Monolithics | Feedback cascode amplifier |

| JP3563321B2 (ja) * | 2000-03-22 | 2004-09-08 | 日本電信電話株式会社 | マルチバンド高周波増幅回路 |

| US7023272B2 (en) | 2004-04-19 | 2006-04-04 | Texas Instruments Incorporated | Multi-band low noise amplifier system |

| US7508260B2 (en) * | 2005-08-24 | 2009-03-24 | Freescale Semiconductor, Inc. | Bypassable low noise amplifier topology with multi-tap transformer |

| TWI327416B (en) | 2006-10-27 | 2010-07-11 | Nat Univ Tsing Hua | Cascode low noise amplifier with a source coupled active inductor |

| KR20080072383A (ko) | 2007-02-02 | 2008-08-06 | 삼성전자주식회사 | 실리콘 튜너 및 그 신호 처리 방법 |

| WO2010082235A1 (ja) * | 2009-01-13 | 2010-07-22 | パナソニック株式会社 | 可変利得増幅器およびそれを備えた高周波信号受信装置 |

| US8022772B2 (en) * | 2009-03-19 | 2011-09-20 | Qualcomm Incorporated | Cascode amplifier with protection circuitry |

| KR20110060735A (ko) * | 2009-11-30 | 2011-06-08 | 한국전자통신연구원 | 고주파 변압기를 이용한 다중 대역 전력증폭기 |

| US8680940B2 (en) * | 2010-01-15 | 2014-03-25 | Wispry, Inc. | Tunable matching network circuit topology devices and methods |

| US8310314B2 (en) * | 2010-09-06 | 2012-11-13 | Mediatek Inc. | Signal amplification circuits for receiving/transmitting signals according to input signal |

| KR101214761B1 (ko) * | 2011-09-19 | 2013-01-09 | 삼성전기주식회사 | 다중대역 증폭기 및 다중대역 증폭방법 |

| US8742853B2 (en) * | 2011-10-25 | 2014-06-03 | Marvell World Trade Ltd. | Low-stress cascode structure |

| US9154356B2 (en) | 2012-05-25 | 2015-10-06 | Qualcomm Incorporated | Low noise amplifiers for carrier aggregation |

| US9543903B2 (en) | 2012-10-22 | 2017-01-10 | Qualcomm Incorporated | Amplifiers with noise splitting |

-

2012

- 2012-11-14 US US13/677,017 patent/US9603187B2/en active Active

-

2013

- 2013-11-12 KR KR1020157015072A patent/KR20150084908A/ko not_active Application Discontinuation

- 2013-11-12 EP EP13802154.8A patent/EP2920879B1/en active Active

- 2013-11-12 JP JP2015542025A patent/JP2015534420A/ja active Pending

- 2013-11-12 EP EP22205538.6A patent/EP4164123A3/en active Pending

- 2013-11-12 WO PCT/US2013/069752 patent/WO2014078333A2/en active Application Filing

- 2013-11-12 CN CN201380059119.XA patent/CN104798299B/zh active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7474158B1 (en) * | 2006-04-10 | 2009-01-06 | Rf Micro Devices, Inc. | Dynamic match low noise amplifier with reduced current consumption in low gain mode |

| US20080096516A1 (en) * | 2006-10-17 | 2008-04-24 | Samsung Electronics Co., Ltd. | Multi-band low noise amplifier and multi-band radio frequency receiver including the same |

| JP2009010826A (ja) * | 2007-06-29 | 2009-01-15 | Sony Corp | マルチバンド低雑音増幅器および無線通信装置 |

| US20090195316A1 (en) * | 2008-02-01 | 2009-08-06 | Silicon Motion, Inc. | Re-configurable low noise amplifier utilizing feedback capacitors |

| JP2010141673A (ja) * | 2008-12-12 | 2010-06-24 | Renesas Technology Corp | 電力増幅回路 |

| WO2011143504A1 (en) * | 2010-05-13 | 2011-11-17 | Qualcomm Incorporated | Area efficient concurrent matching transceiver |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019528657A (ja) * | 2016-08-31 | 2019-10-10 | スカイワークス ソリューションズ, インコーポレイテッドSkyworks Solutions, Inc. | デジェネレーションスイッチングブロック及び低損失バイパス機能を有するマルチ入力増幅器 |

| US11563460B2 (en) | 2016-08-31 | 2023-01-24 | Skyworks Solutions, Inc. | Amplifying radio-frequency signals using variable impedance stages and bypass blocks |

| WO2019142526A1 (ja) * | 2018-01-19 | 2019-07-25 | ソニーセミコンダクタソリューションズ株式会社 | 増幅回路および受信回路 |

| WO2022153926A1 (ja) * | 2021-01-13 | 2022-07-21 | 株式会社村田製作所 | 高周波回路および通信装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20150084908A (ko) | 2015-07-22 |

| WO2014078333A2 (en) | 2014-05-22 |

| US9603187B2 (en) | 2017-03-21 |

| EP2920879A2 (en) | 2015-09-23 |

| EP4164123A3 (en) | 2023-06-14 |

| CN104798299A (zh) | 2015-07-22 |

| WO2014078333A3 (en) | 2014-07-17 |

| CN104798299B (zh) | 2018-01-26 |

| EP4164123A2 (en) | 2023-04-12 |

| EP2920879B1 (en) | 2022-12-21 |

| US20140134960A1 (en) | 2014-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2920879B1 (en) | Omni-band amplifiers | |

| US9837968B2 (en) | Amplifier circuits | |

| US9166852B2 (en) | Low noise amplifiers with transformer-based signal splitting for carrier aggregation | |

| JP6046279B2 (ja) | 複数の出力と構成可能ディジェネレーションインダクタとをもつ増幅器 | |

| US9106185B2 (en) | Amplifiers with inductive degeneration and configurable gain and input matching | |

| US9154087B2 (en) | Amplifiers with configurable mutually-coupled source degeneration inductors | |

| US9331720B2 (en) | Combined directional coupler and impedance matching circuit | |

| US9124228B2 (en) | Amplifiers with boosted or deboosted source degeneration inductance | |

| US9548709B2 (en) | Independent gain control for multiple receive circuits concurrently processing different transmitted signals |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161019 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161019 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171027 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171128 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20180228 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20180501 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180518 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181030 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20190528 |