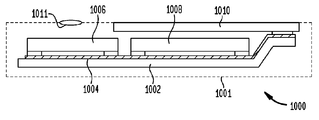

KR20150040998A - 두 개 이상의 다이에 대한 다중 다이 페이스-다운 적층 - Google Patents

두 개 이상의 다이에 대한 다중 다이 페이스-다운 적층 Download PDFInfo

- Publication number

- KR20150040998A KR20150040998A KR1020157005424A KR20157005424A KR20150040998A KR 20150040998 A KR20150040998 A KR 20150040998A KR 1020157005424 A KR1020157005424 A KR 1020157005424A KR 20157005424 A KR20157005424 A KR 20157005424A KR 20150040998 A KR20150040998 A KR 20150040998A

- Authority

- KR

- South Korea

- Prior art keywords

- microelectronic

- extending

- opening

- substrate

- dimension

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/13—Mountings, e.g. non-detachable insulating substrates characterised by the shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05555—Shape in top view being circular or elliptic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

- H01L2224/0613—Square or rectangular array

- H01L2224/06134—Square or rectangular array covering only portions of the surface to be connected

- H01L2224/06136—Covering only the central area of the surface to be connected, i.e. central arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/4824—Connecting between the body and an opposite side of the item with respect to the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/4905—Shape

- H01L2224/4909—Loop shape arrangement

- H01L2224/49095—Loop shape arrangement parallel in plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Wire Bonding (AREA)

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201213565613A | 2012-08-02 | 2012-08-02 | |

| US13/565,613 | 2012-08-02 | ||

| US13/741,890 | 2013-01-15 | ||

| US13/741,890 US9013033B2 (en) | 2011-04-21 | 2013-01-15 | Multiple die face-down stacking for two or more die |

| PCT/US2013/053240 WO2014022675A1 (en) | 2012-08-02 | 2013-08-01 | Multiple die face-down stacking for two or more die |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150040998A true KR20150040998A (ko) | 2015-04-15 |

Family

ID=50028532

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157005424A Ceased KR20150040998A (ko) | 2012-08-02 | 2013-08-01 | 두 개 이상의 다이에 대한 다중 다이 페이스-다운 적층 |

Country Status (5)

| Country | Link |

|---|---|

| EP (1) | EP2880685A1 (enExample) |

| JP (1) | JP2015523742A (enExample) |

| KR (1) | KR20150040998A (enExample) |

| CN (1) | CN104718619A (enExample) |

| WO (1) | WO2014022675A1 (enExample) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114040579B (zh) * | 2021-11-08 | 2023-12-22 | 艾科微电子(深圳)有限公司 | 电子器件及其制造方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02174255A (ja) | 1988-12-27 | 1990-07-05 | Mitsubishi Electric Corp | 半導体集積回路装置 |

| US5679977A (en) | 1990-09-24 | 1997-10-21 | Tessera, Inc. | Semiconductor chip assemblies, methods of making same and components for same |

| US5148265A (en) | 1990-09-24 | 1992-09-15 | Ist Associates, Inc. | Semiconductor chip assemblies with fan-in leads |

| US5861666A (en) | 1995-08-30 | 1999-01-19 | Tessera, Inc. | Stacked chip assembly |

| JP2004063767A (ja) * | 2002-07-29 | 2004-02-26 | Renesas Technology Corp | 半導体装置 |

| US7462936B2 (en) | 2003-10-06 | 2008-12-09 | Tessera, Inc. | Formation of circuitry with modification of feature height |

| US7061121B2 (en) * | 2003-11-12 | 2006-06-13 | Tessera, Inc. | Stacked microelectronic assemblies with central contacts |

| JP4579258B2 (ja) * | 2007-01-18 | 2010-11-10 | 力成科技股▲分▼有限公司 | Bga型パッケージ |

| JP2008277660A (ja) * | 2007-05-02 | 2008-11-13 | Powertech Technology Inc | Lga半導体実装構造 |

| KR101479461B1 (ko) * | 2008-10-14 | 2015-01-06 | 삼성전자주식회사 | 적층 패키지 및 이의 제조 방법 |

| US8553420B2 (en) * | 2010-10-19 | 2013-10-08 | Tessera, Inc. | Enhanced stacked microelectronic assemblies with central contacts and improved thermal characteristics |

| KR101061531B1 (ko) * | 2010-12-17 | 2011-09-01 | 테세라 리써치 엘엘씨 | 중앙 콘택을 구비하며 접지 또는 배전을 개선한 적층형 마이크로전자 조립체 |

-

2013

- 2013-08-01 KR KR1020157005424A patent/KR20150040998A/ko not_active Ceased

- 2013-08-01 JP JP2015525599A patent/JP2015523742A/ja active Pending

- 2013-08-01 CN CN201380051357.6A patent/CN104718619A/zh active Pending

- 2013-08-01 EP EP13750213.4A patent/EP2880685A1/en not_active Withdrawn

- 2013-08-01 WO PCT/US2013/053240 patent/WO2014022675A1/en not_active Ceased

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015523742A (ja) | 2015-08-13 |

| WO2014022675A1 (en) | 2014-02-06 |

| CN104718619A (zh) | 2015-06-17 |

| EP2880685A1 (en) | 2015-06-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI479638B (zh) | 兩個或兩個以上晶粒之多晶粒面向下堆疊 | |

| US9437579B2 (en) | Multiple die face-down stacking for two or more die | |

| US9281295B2 (en) | Embedded heat spreader for package with multiple microelectronic elements and face-down connection | |

| KR102005830B1 (ko) | 플립-칩, 페이스-업 및 페이스-다운 센터본드 메모리 와이어본드 어셈블리 | |

| KR101925427B1 (ko) | 적층가능 마이크로전자 패키지 구조 | |

| US9875955B2 (en) | Low cost hybrid high density package | |

| US9312239B2 (en) | Enhanced stacked microelectronic assemblies with central contacts and improved thermal characteristics | |

| US10622289B2 (en) | Stacked chip-on-board module with edge connector | |

| KR20150040998A (ko) | 두 개 이상의 다이에 대한 다중 다이 페이스-다운 적층 | |

| TW201428933A (zh) | 適用於二個或多個晶粒之多晶粒面朝下堆疊 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20150302 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20180727 Comment text: Request for Examination of Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20190829 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20200218 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20190829 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |