KR20150008428A - 명령어 트레이스 기능을 갖춘 프로세서 디바이스 - Google Patents

명령어 트레이스 기능을 갖춘 프로세서 디바이스 Download PDFInfo

- Publication number

- KR20150008428A KR20150008428A KR1020147033473A KR20147033473A KR20150008428A KR 20150008428 A KR20150008428 A KR 20150008428A KR 1020147033473 A KR1020147033473 A KR 1020147033473A KR 20147033473 A KR20147033473 A KR 20147033473A KR 20150008428 A KR20150008428 A KR 20150008428A

- Authority

- KR

- South Korea

- Prior art keywords

- trace

- trigger signal

- event

- breakpoint

- trigger

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3177—Testing of logic operation, e.g. by logic analysers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/36—Preventing errors by testing or debugging software

- G06F11/362—Software debugging

- G06F11/3636—Software debugging by tracing the execution of the program

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/36—Preventing errors by testing or debugging software

- G06F11/362—Software debugging

- G06F11/3648—Software debugging using additional hardware

Abstract

디버그 기능들을 갖는 프로세서 디바이스는, 중앙 처리 유닛; 및 트레이스 모듈 및 외부 인터페이스를 포함하는 디버그 회로부를 구비하며, 여기서 상기 트레이스 모듈은 실행된 명령어들에 관한 정보를 포함하는 트레이스 스트림을 생성하고, 상기 트레이스 스트림은 상기 외부 인터페이스를 통해 출력되고; 그리고 상기 트레이스 모듈은 또한 트리거 신호를 검출하도록 동작 가능하고, 검출시 트레이스 패킷을 상기 생성된 트레이스 스트림 내에 삽입하도록 동작 가능하다.

Description

본 출원은, "PROCESSOR DEVICE WITH INSTRUCTION TRACE CAPABILITIES"라는 명칭으로 2012년 5월 7일 출원된 미국 가출원 번호 61/643,690 호의 이익을 주장하며, 상기 미국 가출원은 그 전체가 본 출원에 통합된다.

본 개시는 프로세서 디바이스들에 관한 것으로, 특히 집적된 디버그 기능들을 구비한 마이크로컨트롤러 디바이스들에 관한 것이다.

현대의 마이크로프로세서들 및 마이크로컨트롤러들은 임베디드 개발자가 소위 회로 내 디버거 또는 에뮬레이터 디바이스에 의해 실행중인 프로그램을 효율적으로 분석할 수 있게 하는 회로부를 포함한다. 이를 위해, 마이크로컨트롤러 또는 마이크로프로세서는 디버깅 기능들을 지원하는 내부의 회로부, 및 예를 들어 디버그 인터페이스로서 동작하기 위해 디바이스의 다수의 기능 핀들을 프로그래밍함으로써 활성화될 수 있는 특정 인터페이스를 제공한다. 보통 이러한 인터페이스는 실제 디바이스와 외부 디버거 또는 에뮬레이터 사이의 빠른 통신을 가능하게 하기 위해 고속 직렬 인터페이스로 구성될 수 있다. 따라서, 상기 디바이스 자체는 이 인터페이스를 활성화하지 않아 연관된 핀들이 다른 목적들에 사용될 수 있는 정상 동작 모드로 동작될 수 있고, 또한 외부 호스트 컴퓨터로부터 동작될 수 있고 그리고 이 외부 호스트 컴퓨터에 의해 동작될 수 있는 디버거들 또는 에뮬레이터들과 같은 각각의 외부 디바이스들과 데이터를 교환하기 위해 이 인터페이스를 이용하는 디버그 동작 모드로 동작될 수 있다. 상기 디버거들 또는 에뮬레이터들은 또한 프로그래머들로서 동작될 수 있으며, 여기서 프로그램은 동일한 디버그 인터페이스를 통해 타겟 디바이스 내로 전송된다. 이와 함께, 외부 디버거 또는 에뮬레이터를 갖는 호스트 컴퓨터는 저렴한 분석 및 디버깅 시스템을 형성한다.

현대의 프로세서들 및 마이크로컨트롤러들은 각각의 디바이스 내부에 확장 세트의 디버그 기능들을 제공한다. 예를 들어, 다수의 브레이크포인트(breakpoint)들이 디바이스 내에 설정될 수 있어 디바이스가 실제로 실시간으로 동작할 수 있게 하는데, 이 실시간 동작은 고속 직렬 인터페이스만을 이용할 때에는 외부 디버거를 사용해서는 불가능할 것이고, 따라서 본드-아웃(bond-out) 칩들 및 값비싼 디버그 회로부를 필요로 할 것이다. 그러나, 이 내부 디버그 회로부들의 기능성이 물론 실리콘 점유 면적의 제한된 양이나 다른 이유들로 인해 어느 정도 제한된다.

예를 들어, 트레이스 백(trace back) 기능들은, 종종 외부의 회로 내 디버거들에 의해 지원되지 않으며, 또한 훨씬 더 복잡한 회로 내의 에뮬레이터들은 디버그 모드에 있을 때 트레이스 기능을 충분히 지원할 수 없다.

따라서, 향상된 회로 내 디버그 시스템이 필요한데, 특히 향상된 회로 디버깅 성능들을 갖는 독립형 프로세서 디바이스가 필요하다. 예를 들어, 다양한 실시예들에 따른 프로세서 디바이스에 의해서, 상기 디바이스의 디버그 유닛에 공급되는 외부 트리거는, 예를 들어 외부 핀을 통해, 디바이스 동작을 달리 정지시키지 않고 트레이스 데이터 패킷을 생성할 수 있다.

일 실시예에 따르면, 디버그 기능들을 갖는 프로세서 디바이스는, 중앙 처리 유닛; 및 트레이스 모듈 및 외부 인터페이스를 포함하는 디버그 회로부를 포함할 수 있으며, 여기서 상기 트레이스 모듈은 실행된 명령어들에 관한 정보를 포함하는 트레이스 스트림을 생성하고, 상기 트레이스 스트림은 상기 외부 인터페이스를 통해 출력되고; 그리고 상기 트레이스 모듈은 또한 트리거 신호를 검출하도록 동작 가능하고, 검출시 트레이스 패킷을 상기 생성된 트레이스 스트림 내에 삽입하도록 동작 가능하다.

추가 실시예에 따르면, 상기 트리거 신호는 상기 프로세서에 외부로부터 인가된 트리거 신호일 수 있다. 추가 실시예에 따르면, 상기 트리거 신호는 내부 이벤트에 의해 생성될 수 있다. 추가 실시예에 따르면, 상기 내부 이벤트는 브레이크포인트, 마스터 클리어, 인터럽트, 예외적 실행 조건, 디버거 오버플로우 조건 중 적어도 하나를 포함할 수 있다. 추가 실시예에 따르면, 상기 트레이스 스트림은 패킷 기반일 수 있다. 추가 실시예에 따르면, 상기 트레이스 패킷은 트리거 소스에 관한 정보를 포함할 수 있다. 추가 실시예에 따르면, 상기 정보는 조건부로 제공될 수 있으며, 여기서 조건은 사용자에 의해 정의될 수 있다. 추가 실시예에 따르면, 상기 프로세서 디바이스는 다수의 기능 핀들을 가질 수 있고, 하나의 핀은 상기 외부 트리거 신호를 위한 트리거 입력단으로서 동작하도록 할당될 수 있다. 추가 실시예에 따르면, 상기 데이터 패킷은 상기 트리거 신호의 수신시에 보고된 명령어의 실행과 일치하는 시간인, 상기 트레이스 스트림 내의 한 지점에서 상기 트레이스 스트림 내에 삽입될 수 있다. 추가 실시예에 따르면, 상기 디버그 회로부는 복수의 이벤트들을 결합하도록 동작 가능한 이벤트 결합기를 더 포함할 수 있으며, 여기서 이벤트는 브레이크포인트 및 상기 외부 트리거 신호 중 적어도 하나에 의해 생성될 수 있다. 추가 실시예에 따르면, 상기 트레이스 데이터는 상기 이벤트를 발생시킨 상기 브레이크포인트 또는 브레이크포인트들을 확인할 수 있다. 추가 실시예에 따르면, 상기 트리거 신호는 상기 디버그 회로부 내에서 시스템 클록에 동기화되는 비동기 신호일 수 있다. 추가 실시예에 따르면, 상기 프로세서 디바이스는 상기 외부 트리거 신호를 수신하는 외부 핀과 결합된 노이즈 거부 필터를 더 포함할 수 있다. 추가 실시예에 따르면, 상기 트레이스 모듈은 상기 외부 트리거 신호의 포지티브 에지 또는 네거티브 에지를 검출하도록 프로그램 가능할 수 있다.

또 하나의 실시예에 따르면, 프로세서 디바이스 내에서 실행된 코드를 디버깅하기 위한 방법은: 중앙 처리 유닛(CPU)에 의해 코드를 실행하는 단계; 상기 CPU에 의해 실행된 명령어들의 트레이스 스트림을 생성하는 단계; 및 트리거 신호의 결정시, 외부 트리거 신호를 확인하는 트레이스 패킷을 상기 트레이스 스트림 내에 삽입하는 단계를 포함할 수 있다.

상기 방법의 추가 실시예에 따르면, 상기 트리거 신호는 상기 프로세서에 외부로부터 인가된 트리거 신호일 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 트리거 신호는 내부 이벤트에 의해 생성될 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 내부 이벤트는 브레이크포인트, 마스터 클리어, 인터럽트, 예외적 실행 조건, 디버거 오버플로우 조건 중 적어도 하나를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은, 요청에 따라 디버그 인터페이스를 통해 상기 트레이스 스트림을 출력하는 단계를 더 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 데이터 패킷은 상기 트리거 신호의 수신시에 보고된 명령어의 실행과 일치하는 시간인, 상기 트레이스 스트림 내의 한 지점에서 상기 트레이스 스트림 내에 삽입될 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 트레이스 스트림은 패킷 기반일 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 트레이스 패킷은 트리거 소스에 관한 정보를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 정보는 조건부로 제공될 수 있으며, 여기서 조건은 사용자에 의해 정의될 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은 브레이크포인트 및 상기 외부 트리거 신호 중 적어도 하나에 의해 이벤트를 생성하는 단계; 및 디버그 기능을 생성하기 위해 복수의 이벤트들을 결합하는 단계를 더 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 트레이스 데이터는 상기 이벤트를 발생시킨 상기 브레이크포인트 또는 브레이크포인트들을 확인할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 디버그 기능은 트리거 출력 신호 또는 홀트(halt)일 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 트리거 신호는 상기 디버그 회로부 내에서 시스템 클록에 동기화되는 비동기 신호일 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은 외부 핀과 결합된 노이즈 거부 필터에 의해 상기 외부 트리거 신호를 필터링하는 단계를 더 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은 상기 외부 트리거 신호의 포지티브 에지 또는 네거티브 에지를 검출하기 위해 상기 트레이스 모듈을 프로그래밍하는 단계를 더 포함할 수 있다.

본 발명에 따라, 향상된 회로 내 디버그 시스템이 제공되는데, 특히 향상된 회로 디버깅 성능들을 갖는 독립형 프로세서 디바이스가 제공된다.

도 1은 다양한 실시예들에 따른 집적된 디버그 모듈의 블록도를 도시한다.

도 2는 도 1의 하드웨어 브레이크포인트 블록도를 보다 상세하게 도시한다.

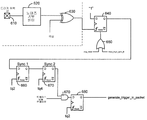

도 3은 도 1의 이벤트 결합기 블록도를 보다 상세하게 도시한다.

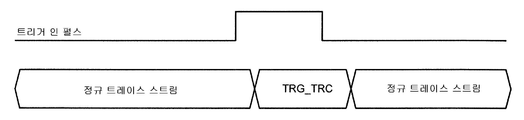

도 4는 트리거-인(trigger-in) 펄스로 인하여 트리거 패킷이 트레이스 데이터에서 어떻게 송신되는가를 나타내는 도면이다.

도 5는 트레이스 기능성을 갖는 프로세서 디바이스 내의 디버그 유닛의 가능한 구현의 세부사항들을 도시한다.

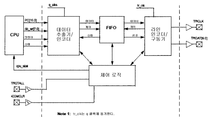

도 6은 도 1에 도시된 트레이스 블록(120)의 단순화된 블록도를 도시한다.

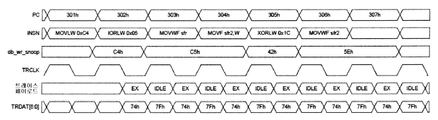

도 7은 프로세서 실행 및 트레이스 데이터 판독의 타이밍도를 도시한다.

도 8은 도 6에 도시된 트레이스 서브(sub) 시스템의 실시예를 도시한다.

도 9는 마이크로프로세서로의 인터페이스를 보여주는, 제안된 트레이스 복구 하드웨어의 블록도를 도시한다.

도 10은 마이크로컨트롤러 내부 클록킹(clocking) 신호들의 타이밍도를 보여준다.

도 11은 트레이스 클록과 데이터와의 관계를 도시한다.

도 12는 다양한 실시예들에 따른 내장된 디버그 유닛을 갖는 마이크로컨트롤러 및 외부의 회로 내 디버그(in circuit debug; ICD) 제어기를 이용하는 시스템의 블록도를 도시한다.

도 2는 도 1의 하드웨어 브레이크포인트 블록도를 보다 상세하게 도시한다.

도 3은 도 1의 이벤트 결합기 블록도를 보다 상세하게 도시한다.

도 4는 트리거-인(trigger-in) 펄스로 인하여 트리거 패킷이 트레이스 데이터에서 어떻게 송신되는가를 나타내는 도면이다.

도 5는 트레이스 기능성을 갖는 프로세서 디바이스 내의 디버그 유닛의 가능한 구현의 세부사항들을 도시한다.

도 6은 도 1에 도시된 트레이스 블록(120)의 단순화된 블록도를 도시한다.

도 7은 프로세서 실행 및 트레이스 데이터 판독의 타이밍도를 도시한다.

도 8은 도 6에 도시된 트레이스 서브(sub) 시스템의 실시예를 도시한다.

도 9는 마이크로프로세서로의 인터페이스를 보여주는, 제안된 트레이스 복구 하드웨어의 블록도를 도시한다.

도 10은 마이크로컨트롤러 내부 클록킹(clocking) 신호들의 타이밍도를 보여준다.

도 11은 트레이스 클록과 데이터와의 관계를 도시한다.

도 12는 다양한 실시예들에 따른 내장된 디버그 유닛을 갖는 마이크로컨트롤러 및 외부의 회로 내 디버그(in circuit debug; ICD) 제어기를 이용하는 시스템의 블록도를 도시한다.

다양한 실시예들에 따르면, 타겟 디바이스 내의 디버그 유닛은, 내부 이벤트들 및/또는 외부 디바이스들이 임의로 브레이크포인트를 비동기적으로 발생시킬 수 있게 하는 트리거 입력부를 가질 수 있고, 브레이크포인트 엔트리는 트레이스 데이터 출력부에 기록된다. 그러나, 몇몇 경우들에서, 외부 트리거는 프로세서의 실행을 중지시킬 수 없는데, 이는 실행 중지가 바람직하지 않은 동작 조건 또는 심지어 위험한 동작 조건을 생성할 수 있기 때문이다. 몇몇 실시예들에 따르면, 상기 트리거 입력부는 외부 이벤트가 실행중인 명령어들과 상관될 수 있게 하는 (또는 역으로도 가능한) 특정한 트레이스 기록을 발생시킨다.

트레이스에서(out of trace) 명령어 데이터를 기록할 때에는, 사용자가 버튼을 눌렀을 때와 코드가 그 당시 수행하고 있는 것 사이에 연결점(joint)이 없다. 그래서 근본적으로 트리거-인(trigger-in) 펄스로 트레이스 패킷을 생성함으로써, 그것에 의해서, 사용자는 CPU가 코드 실행 스트림 내에 있었던 위치를, 트리거 인 펄스가 트레이스 스트림을 분석할 때 발급되었던 시간과 정렬할 수 있다.

다양한 실시예들에 따르면, 명령어 데이터 스트림의 주변 트레이싱과 결합함으로써, 트리거-인 펄스가 검출될 때에는 발생된 트리거-인 펄스를 표시하는 특정 패킷이 스트림에 나타난다.

도 1은 일 실시예에 따라 마이크로컨트롤러 내에 집적될 수 있는 회로 내 디버그 모듈의 블록도를 도시한다. 그러나, 위에 설명된 바와 같은 일반적인 개념은 다른 유형들의 온-칩 디버그 회로부에 구현될 수 있다. 상기 블록도는 예를 들어 마이크로컨트롤러에 구현될 수 있고 그리고 다음과 같은 5개의 기본 블록들로 이루어질 수 있는 모듈을 보여준다:

● 브레이크포인트 비교 로직(135)

● 스톱-워치(Stop-Watch) 사이클 카운터 로직(150)

● 제어 및 상태 머신 로직(145)

● 트레이스 로직(120)

● 이벤트 결합기 로직(125)

CPU(110)는 내부 버스를 통해 하드웨어 브레이크포인트 유닛(135), 이벤트 검출 유닛(140), 제어 로직 유닛(145) 및 백그라운드 인터페이스(155)와 결합된다. 멀티플렉서(160)는 전용 디버그 클록 및 데이터 핀들(165)을 통해 디버그 유닛의 외부 디버거와의 결합을 가능하게 하는데 사용된다. 제어 로직(145)은 하나 이상의 외부 핀들과 결합될 수 있다. 도 1은 예시적인 TRGIN 핀(185)을 보여준다. 이러한 핀은 다른 기능이 전혀 없는 전용 핀일 수 있다. 그러나, 특히 로우(low)-핀 디바이스들에서, 이러한 핀은 프로그램 제어 하에 서로 다른 주변 디바이스들에 할당될 수 있는 다중-기능 핀일 수 있으며, 따라서 그의 프로그래밍된 할당에 따라 서로 다른 기능들을 수행할 수 있다. 예를 들어, 이러한 핀은 기능적으로 트레이스 트리거에 부가되도록 구성 레지스터에 의해 프로그래밍되어, 직렬 인터페이스 클록 핀, 디지털 I/O 핀, 아날로그 입력 핀 등으로서 동작할 수 있다. 도 1에 도시된 바와 같이, 제어 로직은 또한 핀(185)의 다중-기능 핀과 유사할 수 있는 트리거 출력 핀(190)을 제공한다. 트레이스 모듈(120)은 트레이스 스톨(stall) 입력 핀(115)과 트레이스 클록 및 데이터 출력 핀들(175)과 결합된다. 도 1은 또한 제어 로직(145)을 통해 구성 가능한 펄스 거부 필터들(170 및 180)을 도시한다. 이러한 필터들을 통한 신호 라우팅은 도 1에 도시되지 않았다. 몇몇 실시예들에 따르면, 브레이크포인트 디버깅은 "제로 스키드(zero skid)" 동작으로 불리는 명령어가 실행되기 전에 실행이 정지(halt)되도록 구현된다. 다른 디버거 실시예들에 따르면, 이것이 적용되지 않아서 프로세서가 정지되기 전에 코드가 중지하거나 '스키드'하는 곳에서 명령어를 실행 가능하게 하는 문제들을 유발할 수 있다. 외부 이벤트들은 (정의상) 명령어 실행 스트림과 비동기적이다. 이를테면, 그들의 동작은 제로 스키드 개념들과 비교될 수 없다.

내부 신호 debug_en = 1일 때, 상기 모듈은 활성화되고, 모든 "HALT" 이벤트들을 모니터링하고, 이벤트들을 생성하고, 데이터 캡처를 수행하는 등을 행한다. 상기 내부 신호 debug_en = 0이면, 모든 디버그 로직은 비활성화되고, 상기 모듈은 최소의 전력 모드를 소비하도록 구성된다.

디버깅을 덜 침입적(invasive)으로 행하기 위해서는, 실시간으로 디바이스의 외부로 데이터를 스트리밍하는 수단을 구비하는 것이 유용할 수 있다. 트레이스 모듈(120)은 판독되거나 특정 어드레스에 기록되는 데이터를 획득하여 트레이스 포트 외부로 송신하는 방법을 지원한다. 이는 실시간 워치포인트(watchpoint)라고 말할 수 있다. 상기 디바이스의 정상 동작은 워치포인트를 사용할 때 인터럽트되지 않는다.

데이터 캡처는 하드웨어 브레이크포인트를 생성하는데 사용되는 것과 동일한 하드웨어를 사용하여 수행될 수 있다. 홀트(halt) 생성과 동시에 데이터 캡처를 위한 브레이크포인트를 사용함으로써, 두 동작들 모두를 발생시킬 수 있을 것이다. 그러나, 데이터 캡처 및 데이터 매칭을 동시에 활성화하는 것은, 특히 하나보다 많은 브레이크포인트 카운트들에 대해서는, 예기치 않은 결과들을 발생시킬 수 있다. 데이터 캡처 및 데이터 비교가 동일한 물리 레지스터를 사용함에 따라, 비교 값은 모든 캡처에서 업데이트될 것이다. 이를 위해, 내부 이벤트들 및 외부 이벤트들 중 어느 하나는, 프로세서의 디버깅 회로부가 각각의 데이터 패킷을 트레이스 데이터 스트림에 삽입하게 하는 트리거를 생성할 수 있다. 외부 이벤트는 트리거 인 입력단 TRGIN(185)에 인가되는 외부 신호일 수 있다. 내부 이벤트는 브레이크포인트/워치포인트, 마스터 클리어, 인터럽트, 예외적 실행 조건, 디버거 오버플로우 조건과 같은 임의의 이벤트일 수 있다. 예외적 조건들은 인터럽트들, 슬립(sleep) 모드 진입 또는 종료, 스택 오버플로우/언더플로우, 불법의(illegal) 어드레스들로부터 명령어들의 페치(fetch)를 포함할 수 있다. 표 1 및 표 2는 가능한 이벤트들의 리스트를 보여준다. 이 표들은 포괄적이거나 배타적이지 않으며, 트리거 이벤트들의 예시들로서 고려되어야 한다. 다른 내부 이벤트들 또는 이벤트들의 결합들은 특정 데이터 패킷을 트레이스 스트림에 삽입하기 위한 트리거 신호를 생성하는데 사용될 수 있다.

도 2는 하드웨어 브레이크포인트 유닛(135)을 보다 상세하게 도시한다. 하드웨어 브레이크포인트들은 프로그램 및 데이터 메모리 중 어느 하나의 어드레스들의 매칭시 정지시키도록(break on) 구성될 수 있다. 이를 위해, 각각의 비교기들(220 및 230) 및 디코딩 유닛들(240)이 도 2에 도시된 바와 같이 제공된다. 브레이크포인트가 데이터 메모리 상에서 동작하도록 선택될 때, 상기 브레이크포인트는 부가적으로 데이터 값 및 마스크로 자격을 얻을 수 있어, 특정 값들만이 브레이크포인트 이벤트를 생성할 수 있게 한다. 또한, 데이터 브레이크포인트들은 단지 판독이나 기록 사이클들을 정지시키도록 임의로 설정될 수 있다. 모든 경우들에서, 브레이크포인트들은, 브레이크포인트 이벤트가 생성되기 전에 특정 이벤트가 N번 발생해야 하도록, 카운터(210)를 구비한다. 이 카운터(210)는 몇몇 실시예들에 따라, 예를 들어 1부터 256번까지의 임의의 값이 설정될 수 있다.

도 2의 블록도는 단일 브레이크포인트에 대해 도시되었다. 그러나, 구현된 브레이크포인트들의 수는 다양한 실시예들에 따라 가변적이고, 많은 브레이크포인트들이 존재할 수 있다. 도 2는 다양한 파라미터들이 브레이크포인트를 위한 트리거 요구사항들을 정의하도록 프로그래밍될 수 있게 하는 예시적인 실시예를 보여준다. 다른 실시예들에 따르면, 보다 많거나 보다 적은 이러한 파라미터들이 사용될 수 있다. 예를 들어, 브레이크포인트를 발생시키는데 필요한 브레이크포인트 발생 횟수는 카운터(210)의 BPxCNT 파라미터에 의해 설정될 수 있다. 각각의 브레이크포인트 모듈은 동일한 레지스터들을 가질 수 있다.

브레이크포인트들은 이벤트 채널 정의들 사이에 나열되며, 사이클 카운터(150)를 개시하거나 중지하는데, 이벤트 결합기 스테이지(125)를 설정하거나 재설정(리셋)하는데, 트레이스 유닛(120)을 개시하거나 중지하는데, 또는 스택 스냅샷(stack snapshot)을 획득하는데 사용될 수 있다.

일 실시예에 따르면, 브레이크포인트가 활성화되기 위해서는 제어 레지스터 ICDBFxCON의 비트 BPEN이 설정되어야 한다. 이 비트가 소거되면, 이 특정 브레이크포인트에 대한 모든 회로부는 비활성화되고, 어떠한 브레이크포인트 이벤트도 생성되지 않을 것이다. 브레이크포인트는 자격 조건들의 모든 N번째 발생시에 소정 동작을 단지 트리거하도록 구성될 수 있다. 예를 들어, 매 세 번째 발생마다 트리거하도록 브레이크포인트를 설정하기 위해, 카운터(210)는 BPxCNT = 2로 설정된다. 각각의 제어 레지스터들은 그 값을 재로딩(reloading)하고/하거나 현재 상태를 모니터링하기 위해 카운터(210)와 결합하여 사용될 수 있다.

또한, 브레이크포인트들은 예를 들어 연관된 구성 레지스터의 각각의 비트들을 설정함으로써 실행 컨텍스트(메인 라인 코드, 인터럽트 핸들러, 또는 둘 다)를 기반으로 자격이 부여될 수 있다. 브레이크포인트는 이후 프로그램이 선택된 컨텍스트로부터 실행중일 때에만 발생할 수 있다.

구성 레지스터의 각각의 비트들을 설정함으로써, 프로그램 카운터(PC 실행 어드레스)를 모니터링할 수 있게 하는 다른 또 하나의 브레이크포인트 파라미터가 사용될 수 있다. 프로그램 메모리 브레이크들은 제로 스키드이며, 동작이 실행되기 전에 발생한다. PC는 트리거 명령어의 어드레스를 표시할 것이다.

각각의 제어 비트가 소거될 때, 예를 들어 BPAREN = '0'이면, 브레이크는 PC가 소정 어드레스와 동일할 때 트리거된다. BPAREN = '1'이면, 브레이크는 PC가 어드레스들의 소정 포함 범위에 들어갈 때 트리거된다.

몇몇 실시예들에 따르면, 실행된 명령어들만이 브레이크포인트를 생성할 수 있다. PC가 실행되지 않는 어드레스에 있다면, 브레이크포인트는 트리거하지 않는다. 이는 다음을 포함한다:

● 흐름 변경 명령어들(CALL, RETURN 등),

● 스킵 명령어들(per BTFSS, BTFSC), 또는

● PCL, FSR 또는 다른 두 사이클 명령어들 이후의 다음 페치.

또 하나의 제어 비트 필드가 제어 레지스터에서 01, 10, 또는 11로 설정될 때, 브레이크포인트는 데이터 액세스들, 즉 어드레스 및 값 둘 다를 모니터링한다. 연관된 비트들의 세 가지 상태들은 판독 또는 기록 사이클들이 브레이크포인트를 결정하는데 사용되는지의 여부를 선택한다.

데이터가 (적용되는 것처럼) 판독되거나 기록된 후, 데이터 브레이크포인트들은 명령어 실행의 끝에서 필연적으로 브레이크를 일으킨다. 모든 경우들에서, 명령어는 완료될 때까지 실행된다. 따라서, "브레이크"는 실제로 다음 명령어 실행시 발생하고, 그리고 PC는 트리거 명령어 다음에 오는 명령어를 표시할 것이다. 또한, 브레이크는 메모리 어드레스와 데이터 값의 자격요건(qualifier)들이 둘 다 충족되었을 때 트리거될 수 있다.

사이클 카운터(150)는 사용자 코드가 프로파일될 수 있도록, 스톱워치 기능을 제공하는데 사용되는 카운터이다. 사이클 카운터는 각각의 제어 레지스터들에 의해 제어된다. 카운터(150)는 네 개의 8-비트 카운터/레지스터들로 이루어질 수 있다. 카운터(150)는 CPU의 매 Q-사이클의 끝에서 증분될 수 있으며; 멀티-사이클 명령어들(예컨대, GOTO)은 여러 번 카운트한다.

다수의 기능들이 특정 이벤트들에 의해 제어될 수 있도록 하기 위해, 가능한 모드 소스들은 하나의 이벤트 버스로 결합될 수 있다. 이는 사이클 카운터(150), 트레이스 유닛(120), 및 이벤트 결합기 유닛(125)이 이들의 동작들을 선택하기 위해 동일한 설정값들(settings)을 사용할 수 있게 한다.

도 3에 도시된 바와 같은 이벤트 결합기(300)는 다수의 이벤트 입력들(320)을 모니터링하고, 그리고 그 입력들의 결합들 및 시퀀스들에 기초하여 정지(halt) 또는 트리거 출력(190)을 생성할 수 있다. 이벤트 결합기(300)는 각각의 제어 비트가 설정될 때 활성화된다. 비활성화된 결합기들(300)은 출력 이벤트들을 생성하지 않는다. 이벤트 결합기들(300)은 이벤트 채널 정의들 사이에 나열되고, 그리고 사이클 카운터(150)를 개시하거나 중지하는데, 이벤트 결합기 스테이지(310)를 설정하거나 재설정하는데, 트레이스 유닛(120)을 개시하거나 중지하는데, 또는 스택 스냅샷을 획득하는데 사용될 수 있다. 이벤트 결합기 스테이지들(310)은 그 스테이지에 대한 각각의 제어 비트들이 연관된 제어 레지스터들 내에 설정될 때 독립적으로 활성화된다. 스테이지의 현재 출력은 연관된 상태 비트에 반영될 것이다. 스테이지들(310)은 도 3에 도시된 바와 같이 묵시적인 순서를 가지며, 다음과 같은 다수의 방식들로 결합될 수 있다:

● 스테이지는 하나의 이벤트에 의해 개별적으로 활성화될 수 있다,

● 스테이지는 다음의 낮은 스테이지가 활성인 동안 이벤트에 의해 활성화될 수 있다,

● 스테이지는 하나의 이벤트에 의해 개별적으로 비활성화될 수 있다,

● 스테이지는 하나의 이벤트에 의해 또는 다음의 낮은 스테이지가 비활성화될 때 비활성화될 수 있다.

각각의 제어 비트를 설정함으로써, 결합된 이벤트(들)의 N+1번째 발생만이 출력 이벤트에 신호를 보낼 것이다. N은 0부터 255까지 설정될 수 있다. 결합된 트리거 조건들이 충족되면, 레지스터는 1씩 감분된다. 결합된 트리거 조건들이 충족되면, 이벤트 결합기 이벤트가 생성되고 그리고 카운터는 미리 설정된 값으로 재로딩(reloading)된다. 또한, 임의의 시간에 새로운 카운트 값이 각각의 제어 레지스터에 기록되고, 상기 카운터의 값은 재로딩된다. 예를 들어, 3번째 발생시에 트리거하도록 브레이크포인트를 설정하기 위해, 각각의 카운터 값은 2로 설정되어야 한다.

게다가 몇몇 실시예들에 따르면, 핀 TRGIN(185)에 공급된 외부 신호는, 사용자 입력이 트레이스 스트림에 삽입될 트레이스 패킷들을 생성할 수 있게 하고, 정지들을 생성할 수 있게 하고 또한 임의로 트리거 TRGOUT 신호들을 생성할 수 있게 한다. "극성" = 0일 때(도 6), 트리거 입력은 액티브 하이(high)이고 상승 에지(edge)들은 이벤트들을 일으킨다. "극성" = 1일 때, 트리거 입력은 액티브 로우(low)이고 하강 에지들이 이벤트들을 일으킨다. 또 하나의 제어 비트는, 예를 들어 입력이 인식되기 위해, 최소 시간 동안 액티브 상태에 있어야 함을 정의하기 위해 필터를 제어하는데 사용될 수 있다. 이후 보다 짧은 펄스들이 무시된다.

TRGIN 이벤트는 이벤트 채널 정의들 사이에 리스트될 수 있고, 그리고 사이클 카운터(150)를 개시하거나 중지하는데, 이벤트 결합기 스테이지(310)를 설정하거나 재설정하는데, 트레이스 유닛(120)을 개시하거나 중지하는데, 또는 스택 스냅샷을 획득하는데 사용될 수 있다. 트리거 입력의 변화들은 트레이스가 활성화되면 트레이스 패킷을 생성할 것이다.

브레이크포인트 같은 이벤트가 인에이블된 트리거에 의해 발생할 때, TRGOUT 핀(195)에 펄스가 생성된다. 기본 트리거 출력 신호 동작은 각각의 제어 비트들을 설정함으로써 구성된다. 이 제어 비트들은 예를 들어, 트리거 출력이 대략 트리거 이벤트의 지속기간 동안 어서트(assert)되는 것을 제어할 수 있다. 인접하거나 혹은 중첩하는 이벤트들은 신호를 어서트된 상태로 유지할 수 있다. 상기 제어 비트들은 또한 출력이 최소 시간 주기로 스트레칭(stretching)되는지의 여부를 제어할 수 있다. TRGOUT 원샷이 트리거되면, 시간 주기 내에 발생하는 더 많은 이벤트들이 무시될 것이다. 상기 원샷이 타임 아웃되고 TRGOUT가 제로(zero)로 귀환한 후, 그것은 또 하나의 이벤트에 의해 다시 트리거될 수 있다. 상기 원샷은 에지 트리거되고, 그리고 이벤트 신호가 지속되더라도 소정 시간 주기 이후 소거될 것이다.

소프트웨어는 각각의 제어 비트를 설정함으로써 트리거 아웃을 일으킬 수 있다. 디바이스가 깨어 있으면, 비트는 1 사이클 이후 하드웨어에 의해 소거된다. TRGOUT는 또한 각각의 제어 비트를 기록함으로써 소거될 수 있거나, 또는 디바이스가 깨어나면 자동으로 소거될 것이다.

도 4는 외부적으로 어서트된 "트리거 인(in)" 신호에 따른 정규의 트레이스 스트림을 도시한다. "트리거 인" 펄스가 트레이스 명령어 스트림의 도중에 발생할 때, 그 시점에서 스트림에 트리거가 발생했음을 나타내기 위해 "TRG_TRC" 패킷이 정규 트레이스 스트림에 삽입된다. 트리거 입력의 변화들은 각각의 제어 비트가 설정되어 있는 경우 트레이스 패킷을 생성할 것이다. 극성 비트 = 0이면, 이벤트는 상승 에지에서 트리거할 것이다. 극성 비트 = 1이면, 이벤트는 하강 에지에서 트리거할 것이다. 도 4에 도시된 바와 같이, 트리거 트레이스 패킷의 삽입을 일으키는 외부적으로 인가된 신호는 명령어들의 실행과 비동기이다. 내부 이벤트들에 의해 생성된 트리거 트레이스 패킷들은 대개 동기식이다. 그러나, 트레이스 데이터 스트림으로의 삽입에 관해서는 동일한 원리가 적용된다.

도 5는 트리거 핀으로부터 트레이스 패킷 쓰기 클록 및 데이터로의 개념 구현의 단순화된 다이어그램이다. 다양한 실시예들에 따른 특정 신호들이 보여지고 있지만, 패킷을 송신하는 트레이스 모듈의 일부분들 및 트레이스 기능성의 일부는 많은 서로 다른 방법들로 실현될 수 있고, 이에 따라 도시되지는 않았다.

도 5에 도시된 실시예에 따르면, 트리거 신호는 외부 핀(610)을 통해 비동기식으로 입력되고 있으며, 예를 들어 노이즈 거부 필터(620)에 의해 약간의 필터링을 거치게 된다. 그러나, 이러한 필터는 또한 생략될 수 있거나, 또는 구현될 경우에는 아날로그 필터 혹은 디지털 필터 또는 두 필터들의 결합으로서 구현될 수 있다. 게다가, 극성 선택 유닛(630)이 몇몇 실시예들에 따라 구현될 수 있다. 이를 위해, 노이즈 거부 필터(620)의 출력을 수신하거나 트리거 신호를 직접 수신하는 간단한 XOR 게이트(630)가 제공될 수 있다. XOR 게이트(630)의 제 2 입력은 극성 제어 신호를 수신한다. 따라서, 입력되는 트리거 신호는 반전되거나 반전되지 않는다. 그러므로, 사용자는 디바이스를 제어하여, 트리거 펄스의 극성이 무엇이든 항상 포지티브 펄스를 내부에 생성할 수 있다. 그러나, 외부 신호의 다른 처리가 적용될 수 있고, 따라서 "트리거 인" 기능성 자체가 중요하지는 않다. 점선은 "트리거 인" 신호의 트레이스 사용으로부터 "트리거 인" 섹션을 분리한다.

포지티브 트리거 인 펄스는 디바이스 내에서 비동기식이다. 포지티브 트리거 인 펄스는, 이벤트를 검출하고 포지티브 트리거 인 펄스를 등록하는 트레이스 모듈용의 제 1 플립 플롭(640)으로 진행한다. 그 제 1 플립 플롭(640)은 또한 클록 신호로서의 트리거 인 펄스의 연결 때문에 비동기식이다. 등록된 비동기 신호 플립 플롭 출력 Q는 이후 2개의 다음 내부 클록들 - 각각 트레이스 클록 tq2 및 tq4임 - 을 통해 동기화된다. 몇몇 실시예들에 따르면, 이 내부 클록들은 명령어 클록과 동기화되지만 내부 시스템 클록의 실제 명령어 클록에 대응하지 않을 수 있는데, 왜냐하면 몇몇 실시예들에서 시스템 클록이 실제로 쿼드러처 클록, 예컨대 4 q-클록을 사용하여 하나의 명령어 사이클을 실행할 수 있기 때문이다. 도 10은 명령어 실행에 관하여 시스템 클록 clkin 및 관련 쿼드러처 신호들의 예시적인 타이밍도를 도시한다. 이 실시예에서는, clkin으로부터 유도된 4개의 클록들(q1, q2, q3, q4)이 하나의 명령어를 실행하는데 사용된다. 트레이스 클록들은 내부 클록들(q1, q2, q3, q4)로부터 유도될 수 있거나, 또는 이 클록들과 동일할 수 있다.

도 5에 도시된 바와 같이, 두 개의 플립-플롭들(660 및 670)이 직렬로 결합되고 tq2 및 tq4 내부 클록 신호에 의해 클록킹된다. 이후 플립-플롭(670)의 출력 Q는 동기화된 트리거 신호를 제공한다. 플립-플롭(670)의 출력 Q는 트레이스 모듈 인에이블 기능을 제공하도록 구현되는 AND 게이트(670)와 결합될 수 있다.

이 동기화된 신호는 예를 들어 디버그 유닛의 트레이스 모듈 내부의 AND 게이트(670)를 통해 이제 안전하게 사용될 수 있다. 상기 동기화된 신호는 쓰기 클록을 효과적으로 생성할 "아웃밴드(outband)" 쓰기 플립 플롭(680)으로 진행하며, 여기서 "아웃밴드"는 명령어를 의미하지 않는다. 기록될 데이터는 다음과 같이 구현될 수 있다:

begin

if(.....)

else if (....)

else if (generate_trigger_in_packet)

data = TRIGIN PACKET

else

end;

따라서, 플립-플롭(680)은 동기화된 쓰기 클록 신호를 생성하고, 디버그 유닛은 정규 트레이스 스트림에 삽입될 데이터로 실제 데이터 패킷을 생성한다. 삽입될 데이터는 미리 결정될 수 있거나, 또는 이벤트 의존 데이터를 포함하는 미리 결정되고 동적인 부분을 가질 수 있다.

위에 보여진 바와 같이, 이 패킷을 생성하기 위한 메커니즘은 예를 들어, 무엇을 전송해야 할 지의 우선 순위가 주어지는 빅(big) if-elseif-else 문일 수 있다. 패킷 데이터의 생성은 위에 보여진 바와 같이 우선 순위화될 수 있으며, 여기서 여러 "if-elseif" 단계들은 다른 출력 신호들의 생성을 가능하게 하고, 따라서 소정 순서 또는 우선순위를 생성한다. 몇몇 실시예들에 따르면, 트리거-인 트레이스 패킷은 위의 예에서 보여진 바와 같은 오버플로우 에러들이나 다른 유사한 이벤트들과 같은 다른 것들에 비해 상대적으로 낮은 우선순위를 가질 수 있다.

몇몇 실시예들에 따르면, 실제 "트리거 인" 쓰기 신호가 동기화되는 동안 실제 트레이스 트리거 데이터가 생성될 수 있다. 따라서, 이 데이터가 여기서 패킷을 만들고(develope), 쓰기 클록이 올 때 "트리거 인" 쓰기 신호가 트리거 데이터를 트레이스 스트림에 삽입될 수 있는 패킷 내에 기록할 것이라는 점에서 하나의 개념이 이해될 수 있다. "트리거 인" 쓰기 신호는 다른 가공하지 않은 트레이스 패킷들과 상호작용하고, 따라서 우선 순위들 등이 필요하다.

다음 절에서는, 특정 실시예에 따른, 디바이스와 외부 디버그 툴 사이의 트레이스 데이터 인터페이스를 상세히 설명한다. 다른 실시예들은 또 다른 구현들을 이용할 수 있다. 도 6에 예를 들어 도시된 바와 같은 트레이스 서브시스템은, 디버그 툴에 의해 캡처되고 분석될 수 있는 명령어 실행 스트림의 실시간 기록을 제공한다. 트레이스 동작은 디버그 툴이 소스 코드 및 프로그램 메모리 콘텐츠에 액세스하였고 그리고 CPU 동작의 몇몇 양상들을 추론할 수 있다고 가정한다.

명령어가 PCL에 (직접 또는 INDx를 통해) 기록할 때, 새로운 PC는 프로그램 메모리에 어디든지 있을 수 있다. 이 경우, 명령어 패킷은 소위 전체 프로그램 카운터(full program counter; FPC) 패킷으로 대체된다. 도 6에 도시된 바와 같은 FIFO는 코어 데이터 레이트를 (TRSTALL에 의해 지배되는) 디버그 툴 데이터 레이트와 매칭시키는데 사용될 수 있다. FIFO는 CPU 인코더로부터 채워지고, 도 6에 도시된 바와 같이, 데이터 인코더에 의해 비워진다. FIFO는 최대 4096 명령어 패킷들을 보유하지만, 효과적인 운영 사이즈는 각각의 제어 비트들에 의해 선택될 수 있다. WATCH 이벤트 패킷들은 또한 FIFO 내에 배치되어서, 실제 인플라이트(in-flight) 명령어 패킷들의 수는 보통 적을 것이다. 도 11은 서로 다른 구성 설정들(A, B, C 및 D)에 따른 트레이스 클록과 데이터의 관계를 도시한다. 토글링할 때, TRCLK 출력은 각각의 클록 에지에 따라 하나의 데이터 워드를 출력한다. 출력 클록 레이트는 항상 CPU 명령어 레이트에 링크되고, 그리고 소프트웨어가 SYSCLK를 변경시키거나 리셋이 SYSCLK를 변경시키면 변화할 것이다. 각각의 구성에 따르면, 출력 레이트는 항상 명령어 주기당 두 개의 트레이스 워드들일 수 있다. 상기 레이트는 명령어당 1 및 1/2로 감소할 수 있지만, 이로써 FIFO 오버플로우를 야기시킬 것이다. TRCLK 출력은, TRCPS 제어 비트들의 설정에 따라, 데이터 변화들과 같은 위상이거나 다른 위상이도록 선택될 수 있다. FIFO 내 인코딩은 라인 인코딩과 상이할 수 있어서, 각각의 FIFO 위치는 TRDAT 인터페이스 내에 무려 3개나 되는 데이터 워드들을 나타낼 수 있다. 몇몇 실시예들에 따르면, 트레이스 서브시스템 내의 FIFO의 오버플로우는 또한, 트리거 트레이스 패킷을 삽입하기 위한 트레이스 트리거 신호를 생성하기 위한 이벤트로서 사용될 수 있다.

트레이스 스톨(stall) 기능이 구현될 수 있으며, 여기서 구성 비트는 TRSTALL 입력이 효과를 나타내는지의 여부를 결정할 수 있다. 예를 들어, 제어 비트 TRXSE = 1이고 신호 TRSTALL = 1일 때, 트레이스 FIFO는 페이로드 경계(payload boundary)에서 비우기를 중지하고 클록을 중단할 것이다. TRSTALL(tr_stall_pin)이 '0'으로 귀환할 때, 클록킹은 재개될 것이고 FIFO는 데이터를 다시 비우기 시작할 것이다. 트레이스가 인에이블되고 FIFO가 비어있을 때, IDLE 또는 SLEEP 패킷들은 디바이스의 슬립(sleep) 상태에 따라 전송된다. 몇몇 실시예들에 따라 FIFO는 또한 강제로 비워질 수 있고, 트레이스는 비활성화될 수 있다. FIFO가 가득 차게 되면, 시스템 응답은 각각의 제어 설정에 의존할 수 있다. 여하튼, (스톨된(stalled) 또는 데이터를 포스팅(posting)하지 않는) 오버플로우 상태는, FIFO가 각각의 제어 레지스터에 의해 선택된 대로 25% 또는 75%로 가득 찰 때까지 지속될 것이다. 몇몇 실시예들에 따라, 트레이스 구현에 관한 다른 기능들이 부가될 수 있고, 그리고 개시된 바와 같은 몇몇 기능들은 구현되지 않을 수 있다. 전형적인 트레이스 신호 타이밍도가 도 7에 도시되어 있다. 트레이스 페이로드 패킷들은, CPU 코어가 실행하는 명령어들 및 선택된 데이터 이벤트들을 인코딩하고, 또한 트레이스 스트림 동기화를 제공한다. 일 실시예에 따르면, 대부분의 패킷들은 1개 또는 2개의 7-비트 워드들로 이루어질 수 있고, 또는 소위 전체 프로그램 카운터(FPC) 패킷에 대해서는 3개의 워드들로 이루어질 수 있다. 일반적으로 말해서, 패킷들은 "워드 1" 및 임의의 "워드 2"로 이루어진다. 그러나, 또 다른 실시예들에 따라 다른 포맷들이 사용될 수 있다. 특정 실시예에 따르면, "워드 1"의 값은 패킷을 확인하고, "워드 2"가 존재하는지의 여부를 암시한다. (EX, EXD, 및 RESET과 같은) 명령어 실행과 동기하는 패킷들 및 비동기 "이벤트" 패킷들은 아래에 보다 상세히 개시되는 바와 같이 WATCH, RESET, 및 TRIGGER를 포함한다.

동기화 패킷들은 실행 순서대로 방출된다. 이벤트 패킷들은 이벤트 시간 부근의 스트림에 나타나지만, 다수의 이벤트들이 동시에 일어나면, 몇몇 보고들은 지연될 것이다. 몇몇 경우들에서는, FPC가 동기화 보고이지만, 다른 때에는 FPC가 이벤트이다. 전송 층(transport layer; TR) 패킷들(RESYNC, IDLE 및 END)은 필요에 따라 삽입되어 인터페이스 데이터 스트림의 여러 상태들을 관리하고 확인한다. TR 패킷들(RESYNC 및 IDLE)은 명령어 트레이스를 분석할 때 버려질 수 있다.

RESYNC 패킷들은 각각의 제어 비트들에 의해 특정된 대로 주기적으로 삽입되고, 그래서 수신기는 RESYNC 패킷들이 올바르게 동기화되어 있는지 확인할 수 있다. 때때로 소정 시간 간격에 대략 대응하고, 그리고 어떠한 다른 FPC도 상기 간격 내에서 전송되지만 않았다면, FPC는 상기 스트림에 부가될 것이다. 이는 수신기가 올바르게 명령어 스트림을 추적하고 있다는 체크를 제공한다. 삽입된 FPC들은 항상, 다음에 오는 명령어의 어드레스를 표시한다. 패킷 내의 워드들의 수는 패킷 워드 1의 값에 의해 결정된다. RESYNC가 "워드 2"에 대해 틀린 값을 갖는 워드 1로서 수신되면, 스트림은 아웃 오브 싱크(out of sync)이고 에러는 플래그되어야 한다.

표 3은 RESYNC가 다음에 오는, 제 2 워드가 0x7D인 2-워드 패킷을 포함하는 최악의 경우의 상황을 나타낸다. 수신기가 적당히 동기화되면, 수신된 워드 #3는 워드 1일 것이고, 워드 #4는 워드 2일 것이고, 패킷 #2로서 도시되는 완전한 RESYNC 쌍을 형성할 것이다. 패킷 #3은 워드 #5로 시작되고, 올바르게 해석될 것이다.

표 4는, 제 1 워드를 복제하고 수신기를 아웃 오브 싱크로 만드는 클록-바운스(clock-bounce)를 갖는 동일한 데이터를 보여준다. 워드 #1 및 워드 #2는 데이터=0x71를 갖는 EXD 패킷으로서 수신되고(하지만 이는 틀린 해석이다), 워드 #3 및 워드 #4는 RESYNC 쌍처럼 나타난다. 워드 #5는 새로운 RESYNC 패킷의 워드 1로서 취해지지만, 워드 #6은 0x7D가 아니고, 동기화되지 않은 상태로 나타난다. 워드 #6은 새로운 패킷을 개시한다.

트레이싱이 개시될 때, 또는 디버그 실행을 위해 일시 중단된 후 트레이싱이 재개할 때, 전송된 제 1 패킷은 항상 FPC일 것이다. 전체 프로그램 카운터(FPC) 패킷은 스트림에 나타나는 다음 명령어의 절대 주소를 보고한다. 트레이스의 개시, 오버플로우 후의 재개, 및 디버그 후의 재개의 이 상황들에서의 FPC 보고는 단순히 다음 명령어의 주소를 표시한다.

FPC의 다른 모든 이용들은 명령어가 실행되었음을 표시하고, 몇몇 경우들에서는 그 명령어에 대해 보고되었어야 할 패킷을 대신한다. FPC가 분기(branch) 또는 프로그램 카운터 변경 명령어들의 실행을 나타낼 때, 보고된 값은 분기 타겟 주소이다. FPC 다음에 오는 명령어 패킷은 FPC가 가리키는 명령어의 실행을 나타낸다.

GOTO 및 CALL 명령어들은, 프로그램 카운터 PC[10:0]의 최하위 비트들이 (어셈블리 코드의) 디버그 환경에 알려져 있고, 새로운 PC의 상위 4 비트들만이 상부 일부분 프로그램 카운터(upper partial program counter; UPC) 패킷에 보고된다고 가정한다. 그러나, 다른 실시예들은 보다 많거나 보다 적은 정보를 보고할 수 있다. 보고된 값은 0x0F & (PCLATH >> 3)일 수 있고, 여기서 PCLATH는 프로그램 카운터의 상위 비트들을 래칭(latching)하는 구현 특정 레지스터를 나타낸다. 관련 브랜치(BRA)들의 목적지가 소스 코드에 알려져 있기 때문에, 명령어는 단순히 EX로서 보고된다. 매우 다양한 트레이스 페이로드들이 구현될 수 있다. 표 5는 서로 다른 페이로드 신호들의 예를 보여준다.

표 6은 실제 트레이스의 예를 보여준다.

도 8은 트레이스 서브(sub) 시스템(700)의 단순화된 블록도를 도시한다. 서브시스템(700)은 코어 및 WATCH 이벤트 신호들로부터 명령어 코드들을 수신하고, TRDAT 신호들 상의 전달을 위해 이 데이터를 포맷한다. 시퀀스 제어기(710)는 명령어 및 WATCH 데이터를 FIFO에 로딩할 책임이 있다. 각각의 데이터 패킷은 단일 16-비트 워드로서 인코딩된다. q34동안, WATCH 신호들은 샘플링되고, 가장 높은 우선 순위의 신호가 인코딩되고, 로딩되고 그리고 리셋된다. 2 이상의 신호가 어서트되면, 가장 높은 우선순위의 신호만이 로딩되고, 나머지 다른 신호들은 이후의 q34 기회들을 기다려야 한다. 보고 우선순위가 브레이크포인트 넘버를 기반으로 하기 때문에, 이벤트들은 순서와 다르게 보고될 수 있다. q12 동안에는 이전 명령어로부터의 데이터가 인코딩되고 로딩된다(q3에서는 연산 코드가 인코딩되고, 버스 데이터는 안정적인 q3-q3이고, 그리고 모두는 상승 q1에서 유효하다). 일반적으로 말해서, 이것은 모든 명령어 주기에서 발생한다. 분기 및 호출 명령어들에 대해서는, 인터럽트 사이클들뿐만 아니라, 제 1 사이클 동안에는 아무것도 로딩되지 않으며, 패킷은 제 2 사이클 동안 인코딩되어(소위 "강제된 NOP"), UPC 및 FPC가 정확한 PC 값으로 방출될 수 있게 한다. 결과적으로, 두 WATCH 패킷들은 분기 동안 로딩될 수 있다. SKIP 및 STALL은 현재의 코어 동작을 기반으로 인코딩된다.

시퀀스 제어기(710)는 명령어 사이클마다 두 번 로딩할 수 있고 스트림 관리자(730)는 명령어 사이클마다 두 번 언로딩(unloading)할 수 있어, 명령어 사이클마다 최대 4개의 메모리 사이클들을 필요로 할 수 있다. FIFO 제어기(720)는 시퀀스 제어기(710)에 의해 제공된 데이터를 관리한다. 데이터는 스트림 관리자(730)에 의해 요청될 때 동일한 순서로 전달된다. 스트림 관리자(730)는 16-비트 FIFO 워드들을 TRDAT 신호들 상에서 송신되는 데이터 워드들 내에 재포맷한다. 일부 패킷들(예컨대, EX)은 각각의 FIFO 워드에 대해 단일 TRDAT 워드를 생성하지만, 다른 패킷들(예컨대, FPC)은 그보다 많이 생성한다. 필요에 따라, 전송 관리 패킷들(RESYNC, IDLE 및 END)이 스트림에 삽입되고, 그리고 판독 동작은 TRSTALL 입력에 따라 일시 정지된다. 각각의 명령어 사이클 주기 동안에는, 2개의 TRDAT 워드들이 전송된다. TRCLK 신호는 시스템 리셋 동안 (사이클의 스트레치(stretch) 부분을) 일시 정지할 것이다(데이터는 손실되지 않을 것이다).

도 9는 트레이스 수신기로서 동작하는 디버그 툴(820)과 결합된 다양한 실시예들에 따른 마이크로컨트롤러(810)를 갖는 시스템(800)을 도시한다. 디버그 툴은 예를 들어, 출원인에 의해 제조된 회로 에뮬레이터의 리얼(Real)-ICE일 수 있다. 수신기(820)는 트레이스 동기화를 수행하고, 모든 IDLE 및 전송 패킷들을 버리고, 남은 패킷들의 번들(bundle)들을 원격 호스트(830) - 예를 들어, 패킷 스트림 해석이 수행되는 퍼스널 컴퓨터 또는 워크 스테이션 - 로 송신한다.

● 워드 1 분석 ― 패킷들을 3-워드 폭의 데이터 버스로 변환한다.

● 더블릿(doublet)들(RESYNC, OVERFLOW 등)을 검사하고, 그리고 (a) 더블릿들이 연속적인 워드들에 없을 때, 또는 (b) 미구현된 워드 1 코드 값이 나타날 때, 동기화 에러들을 플래그(flag)한다.

● IDLE 및 다른 전송 패킷들을 버리고, 그리고 남은 값들을 FIFO에 스택(stack)한다.

● 전체 패킷들을 원격 호스트에 송신한다.

TRSTALL을 어서트할 때, 수신기(820)는 재동기화 파이프라인에 인큐잉(en-queueing)될 수 있는 2개의 워드들을 더하여 최대 6개 더 많은 TRDAT 워드들(2개의 연속적인 FPC 패킷들의 상당물)을 받아들이도록 준비된다. TRSTALL을 해제할 때, 패킷 워드 1 정렬이 보장된다. IDLE 패킷들의 스트링으로부터, 대부분이 또는 때때로 모두가 버려져서 원격 호스트에 발송되지 않아 대역폭을 줄일 수 있다. 미구현된 연산 코드들 및 FPC 워드 3(7'h5x)은 또한 동기화 에러들로서 플래그되어야 하고 1-워드 패킷들로서 취급되어야 한다.

FPC의 제 3 워드는 단일-워드 패킷의 스타일(예컨대, 코드 7'h5x)로 인코딩된다. 동기화 여부에 상관없이, 예를 들어 7'h5x의 임의의 워드 다음에 오는 워드는 새로운 패킷의 워드 1이라고 가정될 수 있다. 워드 1을 추적하는 목적을 위해, OVERFLOW, RESYNC, SLEEP 및 END 패킷들은 1-워드 패킷들로서 취급되어야 한다. 7'h7D가 1-워드 패킷으로서 취급될 때, 이후 다음의 패킷은 또 하나의 7'h7D(한 쌍의 RESYNC 워드)이더라도 항상 워드 1의 값일 것이다. 워드 1-정렬 (의사(pseudo)) 데이터는 더블릿 분석에 전달되고, 더블릿 분석에서는 두 RESYNC가 스트림에 연속적으로 나타나지 않을 때 동기화 실패가 인식된다. 이와 마찬가지로, OVERFLOW(7'h77)는 수신기가 아웃 오브 싱크일 때 나타날 수 있으며, 제 2 워드가 매칭되지 않더라도 정확히 해석되어야 한다. 이는 또한 동기화 에러를 플래그할 수 있다. 유사한 추론이 SLEEP 및 END 패킷들에 적용될 수 있는데, 왜냐하면 수신기가 아웃 오브 싱크이면, 단지 하나의 7'h7C 또는 7'h7F가 끝에 나타날 수 있고, 수신기가 제 2 값을 대기하는 동안 중단되는(hanging) 것이 부적합할 것이기 때문이다. 이와는 정반대로, 3개의 동일한 워드들이 나타날 수 있는데, 어느 것도 수신기를 혼동하지 말아야 한다.

완벽한 분석을 위해, 호스트(830)는, 트레이스 데이터를 마이크로프로세서를 프로그래밍하는데 사용된 오리지널 소스 코드와 비교해야 한다. 대부분의 명령어들에 대해, 트레이스 데이터는 실행이 발생했음을 선언하지만, 동작 세부 사항들은 포함되지 않는다. 분기(branch)들이 EX 패킷들(TRFPCB = 0)만을 생성할 때, 분기 목적지는 단지 소스 코드를 검사함으로써 결정될 수 있다. 유사하게, 특정 실시예에 따르면, PCLATH에의 기록은 단지 부분적인 데이터만을 방출하고, 그리고 평가를 완료하기 위해 소스 지식을 필요로 한다. 동작에 의존하여, STALL 패킷들은 영향을 받는 명령어에 선행하거나 뒤따를 수 있다. STALL 패킷들은 사용자의 디스플레이 상에 강조 표기법을 써서, 비전형적인 동작이 일어났다는(예컨대, 파일 선택 레지스터(file select register; FSR)가 비휘발성 메모리에 기록함) 암시로 보여질 수 있다. WATCH 보고들은 많은 패킷들에 의해 트리거링 명령어를 지연시킬 수 있다. 밀집도가 높은 워치들은, 동일한 워치가 판독이 발생하기 전에 트리거하면 실제로 손실될 수 있다. 워치포인트들이 데이터 어드레스만을 확인하기 때문에, 트레이스 분석은 데이터 액세스 포인터 값들이 (BSR 및 연산 코드의 지식을 필요로 하는) 직접-어드레싱 모드들로부터의 값들이든 (FSR들의 지식을 필요로 하는) 간접 모드들로부터의 값들이든 간에, 이 데이터 액세스 포인터 값들을 재구성할 수 있어야 한다. 워치 데이터는 항상 가장 최근 발생한 워치 이벤트로부터의 데이터이어야 한다. 몇몇 FPC 패킷들은 명령어들(예컨대, RETURN 명령어들)이 실행되었음을 암시하지만, 다른 경우들은 단순히 정보임을 주의한다.

도 12는 개발 프로그램을 실행하고 그리고 예를 들어 USB 인터페이스를 통해 외부 디버거/프로그래밍 유닛(520)과 연결되는 퍼스널 컴퓨터와 같은 호스트를 갖는 전형적인 디버깅/프로그래밍 시스템(500)을 도시한다. 외부 디버거 프로그래밍 유닛(520)은 디버거/프로그래머(520)의 내부에 생성된 전원 전압을 공급할 수 있는 전용 인터페이스를 제공한다. 그러나, 다른 실시예들은 전용 전원을 통해 공급 전압을 제공할 수 있거나, 또는 타겟 시스템은 자체 전원이 공급될 수 있다. 실제 디버그/프로그래밍 인터페이스는 동기식 직렬 인터페이스에 의해, 디버거/프로그래밍 유닛(520)에 의해 제공된 단방향 클록 신호(ICDCLK) 및 양방향 데이터 라인(ICDData)이 제공될 수 있다. 따라서, 최소 3개의 연결 라인들에서, ICDCLK, ICDData 및 기준 포텐셜(GND)이 디버거/프로그래밍 유닛(520)을 타겟 시스템(510)과 결합시키는데 사용될 수 있으며, 최소한 상기 타겟 시스템(510)은 위에 개시한 바와 같은 다양한 실시예들에 따른 디버깅/프로그래밍 인터페이스를 갖는 마이크로컨트롤러일 수 있다. 게다가, 위에 개시한 바와 같은 신호(540)의 외부 트리거가 도 12에 도시된 바와 같이 타겟 시스템(510)에 구현될 수 있거나 또는 회로 내 디버거/프로그래머(520)에 구현될 수 있고, 그리고 트레이스 신호들은 타겟 디바이스(510)에 의해, 전용 신호 라인들(550)을 통해 회로 내 디버거/프로그래머에 전송된다.

이러한 시스템은 사용자가 호스트 상에 실행되는 디버깅 프로그램을 프로그래밍할 수 있게 하여, 위에 설명한 바와 같은 조건들을 갖는 여러 브레이크포인트들을 설정하고, 그리고 프로그램이 실시간 실행되고 있는 동안에 트레이스 정보를 수신한다. 디버깅 소프트웨어가 소스 코드 내의 브레이크포인트들의 위치에 관련하여 여러 브레이크포인트들의 추적을 유지하는 동안, 디버거/프로그래머(520)는 브레이크포인트 정보를, 각각의 브레이크포인트들을 설정하고 그 연관된 레지스터들을 구성하는 타겟 디바이스에 전달한다. 또한, 트레이스 기능들의 설정 및 구성은 디버거/프로그래머(520)에 의해 타겟 디바이스(510)에 전달된다. 예를 들어, 메모리에 저장된 데이터 값의 매치에 의해 트리거되는 특정 브레이크포인트가 설정될 수 있다. 이후 사용자는 호스트 PC(530) 상에 실행되는 디버거 소프트웨어를 통해 타겟 디바이스(510)의 소프트웨어의 실행을 개시한다. 타겟 소프트웨어의 실행은 단지 브레이크포인트가 검출될 때 중지된다. 그러나, 트레이스 정보는 타겟 프로그램의 실행 동안 계속적으로 전송된다. 호스트 컴퓨터(530)는 이 트레이스 데이터를 평가할 수 있고, 그리고 트레이스 데이터를 텍스트 형성 및 그래픽 디스플레이의 사용 중 어느 하나의 경우에 사용할 수 있게 한다.

본 실시예들은 위에 논의된 바와 같은 특징들을 구현함으로써 트레이스 스트림의 더 좋은 분석을 가능하게 한다. 그러므로, 다양한 실시예들은 온(on)-칩 디버그 기능들의 기술 상태를 향상시키고, 그리고 더 많은 다른 사용자들에게 첨단 디버깅 기능들을 가져다줄 것이다.

Claims (29)

- 디버그 기능들을 갖는 프로세서 디바이스로서,

중앙 처리 유닛; 및

트레이스 모듈 및 외부 인터페이스를 포함하는 디버그 회로부를 포함하고,

상기 트레이스 모듈은 실행된 명령어들에 관한 정보를 포함하는 트레이스 스트림을 생성하고, 상기 트레이스 스트림은 상기 외부 인터페이스를 통해 출력되고; 그리고

상기 트레이스 모듈은 또한 트리거 신호를 검출하도록 동작 가능하고, 검출시 트레이스 패킷을 상기 생성된 트레이스 스트림 내에 삽입하도록 동작 가능한, 프로세서 디바이스. - 제 1 항에 있어서,

상기 트리거 신호는 상기 프로세서에 외부로부터 인가된 트리거 신호인, 프로세서 디바이스. - 제 1 항에 있어서,

상기 트리거 신호는 내부 이벤트에 의해 생성되는, 프로세서 디바이스. - 제 3 항에 있어서,

상기 내부 이벤트는 브레이크포인트, 마스터 클리어, 인터럽트, 예외적 실행 조건, 디버거 오버플로우 조건 중 적어도 하나를 포함하는, 프로세서 디바이스. - 제 1 항에 있어서,

상기 트레이스 스트림은 패킷 기반인, 프로세서 디바이스. - 제 1 항에 있어서,

상기 트레이스 패킷은 트리거 소스에 관한 정보를 포함하는, 프로세서 디바이스. - 제 6 항에 있어서,

상기 정보는 조건부로 제공되며, 여기서 조건은 사용자에 의해 정의될 수 있는, 프로세서 디바이스. - 제 2 항에 있어서,

상기 프로세서 디바이스는 다수의 기능 핀들을 가지며, 하나의 핀은 상기 외부 트리거 신호를 위한 트리거 입력단으로서 동작하도록 할당될 수 있는, 프로세서 디바이스. - 제 1 항에 있어서,

상기 데이터 패킷은 상기 트리거 신호의 수신시에 보고된 명령어의 실행과 일치하는 시간인, 상기 트레이스 스트림 내의 한 지점에서 상기 트레이스 스트림 내에 삽입되는, 프로세서 디바이스. - 제 2 항에 있어서,

상기 디버그 회로부는 복수의 이벤트들을 결합하도록 동작 가능한 이벤트 결합기를 더 포함하고, 여기서 이벤트는 브레이크포인트 및 상기 외부 트리거 신호 중 적어도 하나에 의해 생성될 수 있는, 프로세서 디바이스. - 제 10 항에 있어서,

상기 트레이스 데이터는 상기 이벤트를 발생시킨 상기 브레이크포인트 또는 브레이크포인트들을 확인하는, 프로세서 디바이스. - 제 1 항에 있어서,

상기 트리거 신호는 상기 디버그 회로부 내에서 시스템 클록에 동기화되는 비동기 신호인, 프로세서 디바이스. - 제 2 항에 있어서,

상기 외부 트리거 신호를 수신하는 외부 핀과 결합된 노이즈 거부 필터를 더 포함하는 프로세서 디바이스. - 제 2 항에 있어서,

상기 트레이스 모듈은 상기 외부 트리거 신호의 포지티브 에지 또는 네거티브 에지를 검출하도록 프로그램 가능한, 프로세서 디바이스. - 프로세서 디바이스 내에서 실행된 코드를 디버깅하기 위한 방법으로서,

중앙 처리 유닛(CPU)에 의해 코드를 실행하는 단계;

상기 CPU에 의해 실행된 명령어들의 트레이스 스트림을 생성하는 단계; 및

트리거 신호의 결정시, 외부 트리거 신호를 확인하는 트레이스 패킷을 상기 트레이스 스트림 내에 삽입하는 단계를 포함하는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 트리거 신호는 상기 프로세서에 외부로부터 인가된 트리거 신호인, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 트리거 신호는 내부 이벤트에 의해 생성되는, 실행된 코드 디버깅 방법. - 제 17 항에 있어서,

상기 내부 이벤트는 브레이크포인트, 마스터 클리어, 인터럽트, 예외적 실행 조건, 디버거 오버플로우 조건 중 적어도 하나를 포함하는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

요청에 따라 디버그 인터페이스를 통해 상기 트레이스 스트림을 출력하는 단계를 더 포함하는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 데이터 패킷은 상기 트리거 신호의 수신시에 보고된 명령어의 실행과 일치하는 시간인, 상기 트레이스 스트림 내의 한 지점에서 상기 트레이스 스트림 내에 삽입되는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 트레이스 스트림은 패킷 기반인, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 트레이스 패킷은 트리거 소스에 관한 정보를 포함하는, 실행된 코드 디버깅 방법. - 제 22 항에 있어서,

상기 정보는 조건부로 제공되며, 여기서 조건은 사용자에 의해 정의될 수 있는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

브레이크포인트 및 상기 외부 트리거 신호 중 적어도 하나에 의해 이벤트를 생성하는 단계; 및

디버그 기능을 생성하기 위해 복수의 이벤트들을 결합하는 단계를 더 포함하는, 실행된 코드 디버깅 방법. - 제 24 항에 있어서,

상기 트레이스 데이터는 상기 이벤트를 발생시킨 상기 브레이크포인트 또는 브레이크포인트들을 확인하는, 실행된 코드 디버깅 방법. - 제 25 항에 있어서,

상기 디버그 기능은 트리거 출력 신호 또는 홀트(halt)인, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 트리거 신호는 상기 디버그 회로부 내에서 시스템 클록에 동기화되는 비동기 신호인, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

외부 핀과 결합된 노이즈 거부 필터에 의해 상기 외부 트리거 신호를 필터링하는 단계를 더 포함하는, 실행된 코드 디버깅 방법. - 제 15 항에 있어서,

상기 외부 트리거 신호의 포지티브 에지 또는 네거티브 에지를 검출하기 위해 상기 트레이스 모듈을 프로그래밍하는 단계를 더 포함하는, 실행된 코드 디버깅 방법.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201261643690P | 2012-05-07 | 2012-05-07 | |

| US61/643,690 | 2012-05-07 | ||

| US13/888,357 | 2013-05-06 | ||

| US13/888,357 US9377507B2 (en) | 2012-05-07 | 2013-05-06 | Processor device with instruction trace capabilities |

| PCT/US2013/039944 WO2013169773A1 (en) | 2012-05-07 | 2013-05-07 | Processor device with instruction trace capabilities |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150008428A true KR20150008428A (ko) | 2015-01-22 |

Family

ID=48570433

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147033473A KR20150008428A (ko) | 2012-05-07 | 2013-05-07 | 명령어 트레이스 기능을 갖춘 프로세서 디바이스 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9377507B2 (ko) |

| EP (1) | EP2847683B1 (ko) |

| JP (1) | JP6397815B2 (ko) |

| KR (1) | KR20150008428A (ko) |

| CN (1) | CN104272271B (ko) |

| WO (1) | WO2013169773A1 (ko) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103885845A (zh) * | 2012-12-21 | 2014-06-25 | 祥硕科技股份有限公司 | 集成电路的除错系统及其除错方法 |

| US10216616B2 (en) * | 2016-07-02 | 2019-02-26 | Intel Corporation | Cooperative triggering |

| KR20180054364A (ko) | 2016-11-15 | 2018-05-24 | 삼성전자주식회사 | 트레이스 데이터를 생성하는 스토리지 장치 및 상기 스토리지 장치의 동작 방법 |

| CN107609187A (zh) * | 2017-10-09 | 2018-01-19 | 郑州云海信息技术有限公司 | 一种统计文件系统中异步操作的方法、系统及相关装置 |

| US10754759B1 (en) * | 2018-02-05 | 2020-08-25 | Xilinx, Inc. | Breakpointing circuitry that evaluates breakpoint conditions while running clock to target circuit |

| US11237946B2 (en) * | 2018-05-03 | 2022-02-01 | Sap Se | Error finder tool |

| CN110515754B (zh) * | 2018-05-22 | 2021-01-26 | 深圳云天励飞技术有限公司 | 神经网络处理器的调试系统及方法 |

| GB2605796B (en) * | 2021-04-13 | 2023-06-28 | Advanced Risc Mach Ltd | Apparatus and method for generating debug information |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07104800B2 (ja) * | 1987-05-25 | 1995-11-13 | 日本電気株式会社 | プログラム評価装置 |

| JP3116706B2 (ja) * | 1994-02-04 | 2000-12-11 | 横河電機株式会社 | トリガ入力回路 |

| JPH08179965A (ja) * | 1994-12-26 | 1996-07-12 | Mitsubishi Denki Semiconductor Software Kk | イベント検出回路 |

| EP0869434A3 (en) * | 1997-03-31 | 1999-09-15 | Hewlett-Packard Company | Method for outputting trace information of a microprocessor |

| JPH1124959A (ja) * | 1997-07-02 | 1999-01-29 | Hewlett Packard Japan Ltd | マイクロプロセッサのトレース情報出力方法 |

| US5978902A (en) * | 1997-04-08 | 1999-11-02 | Advanced Micro Devices, Inc. | Debug interface including operating system access of a serial/parallel debug port |

| US6094729A (en) | 1997-04-08 | 2000-07-25 | Advanced Micro Devices, Inc. | Debug interface including a compact trace record storage |

| JP2002202900A (ja) * | 2000-12-28 | 2002-07-19 | Seiko Epson Corp | デバッグ装置 |

| US7231339B1 (en) * | 2002-03-28 | 2007-06-12 | Cypress Semiconductor Corporation | Event architecture and method for configuring same |

| US6948155B2 (en) | 2002-11-22 | 2005-09-20 | Texas Instruments Incorporated | Little offset in multicycle event maintaining cycle accurate tracing of stop events |

| US7325169B2 (en) | 2002-12-17 | 2008-01-29 | Texas Instruments Incorporated | Apparatus and method for trace stream identification of multiple target processor events |

| TW200401188A (en) * | 2003-09-16 | 2004-01-16 | Via Tech Inc | Debug device and method thereof |

| US7219265B2 (en) * | 2003-12-29 | 2007-05-15 | Agere Systems Inc. | System and method for debugging system-on-chips |

| US7627784B1 (en) * | 2005-04-06 | 2009-12-01 | Altera Corporation | Modular processor debug core connection for programmable chip systems |

| CN1851668A (zh) * | 2006-06-01 | 2006-10-25 | 北京天碁科技有限公司 | 片上系统芯片、片上系统芯片的跟踪调试系统及方法 |

| US20080082801A1 (en) * | 2006-09-29 | 2008-04-03 | Mips Technologies, Inc. | Apparatus and method for tracing instructions with simplified instruction state descriptors |

| JP2008191788A (ja) * | 2007-02-01 | 2008-08-21 | Ricoh Co Ltd | 情報処理装置 |

| KR101090556B1 (ko) * | 2007-02-14 | 2011-12-08 | 닛본 덴끼 가부시끼가이샤 | 반도체 집적 회로, 디버그·트레이스 회로, 및 반도체 집적 회로 동작 관측 방법 |

| CN101751327B (zh) * | 2008-12-04 | 2012-04-18 | 北京中电华大电子设计有限责任公司 | 嵌入式处理器的跟踪调试方法 |

| JP2011013867A (ja) * | 2009-06-30 | 2011-01-20 | Panasonic Corp | データ処理装置、性能評価解析システム |

| US8566645B2 (en) * | 2010-12-02 | 2013-10-22 | Advanced Micro Devices, Inc. | Debug state machine and processor including the same |

-

2013

- 2013-05-06 US US13/888,357 patent/US9377507B2/en active Active

- 2013-05-07 EP EP13726615.1A patent/EP2847683B1/en active Active

- 2013-05-07 CN CN201380023766.5A patent/CN104272271B/zh active Active

- 2013-05-07 WO PCT/US2013/039944 patent/WO2013169773A1/en active Application Filing

- 2013-05-07 JP JP2015511624A patent/JP6397815B2/ja active Active

- 2013-05-07 KR KR1020147033473A patent/KR20150008428A/ko not_active Application Discontinuation

Also Published As

| Publication number | Publication date |

|---|---|

| EP2847683B1 (en) | 2019-07-03 |

| US20130318408A1 (en) | 2013-11-28 |

| JP2015516100A (ja) | 2015-06-04 |

| JP6397815B2 (ja) | 2018-09-26 |

| CN104272271A (zh) | 2015-01-07 |

| CN104272271B (zh) | 2017-12-26 |

| WO2013169773A1 (en) | 2013-11-14 |

| EP2847683A1 (en) | 2015-03-18 |

| US9377507B2 (en) | 2016-06-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2847682B1 (en) | Processor device with reset condition trace capabilities | |

| KR20150008428A (ko) | 명령어 트레이스 기능을 갖춘 프로세서 디바이스 | |

| KR101430218B1 (ko) | 디버그 상태 기계 및 이를 포함하는 프로세서 | |

| US7720670B2 (en) | Saving resources by deducing the total prediction events | |

| KR20150008447A (ko) | 인터럽트 상태에 기초한 구성 가능한 브레이크포인트를 갖는 디바이스 | |

| US7721263B2 (en) | Debug event instruction | |

| US20060255972A1 (en) | Trace Receiver Data Compression | |

| US20070285288A1 (en) | High Speed Data Recording With Input Duty Cycle Distortion | |

| US7797685B2 (en) | Method for generating timing data packet | |

| US20190303166A1 (en) | Operating a pipeline flattener in a semiconductor device | |

| US20060255976A1 (en) | Distributed Depth Trace Receiver | |

| US7681084B2 (en) | TOD or time stamp inserted into trace recording stream | |

| US7721267B2 (en) | Efficient protocol for encoding software pipelined loop when PC trace is enabled | |

| US20060255978A1 (en) | Enabling Trace and Event Selection Procedures Independent of the Processor and Memory Variations | |

| US7676697B2 (en) | Using a delay line to cancel clock insertion delays | |

| US20060255977A1 (en) | Recording Control Point in Trace Receivers | |

| US20060273944A1 (en) | System With Trace Capability Accessed Through the Chip Being Traced | |

| US7613951B2 (en) | Scaled time trace | |

| Matraszek et al. | FrankenTrace: Low-Cost, Cycle-Level, Widely Applicable Program Execution Tracing for ARM Cortex-M SoC |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |