KR20120081663A - 패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 - Google Patents

패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 Download PDFInfo

- Publication number

- KR20120081663A KR20120081663A KR1020100137131A KR20100137131A KR20120081663A KR 20120081663 A KR20120081663 A KR 20120081663A KR 1020100137131 A KR1020100137131 A KR 1020100137131A KR 20100137131 A KR20100137131 A KR 20100137131A KR 20120081663 A KR20120081663 A KR 20120081663A

- Authority

- KR

- South Korea

- Prior art keywords

- mask

- region

- photosensitive

- forming

- pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/26—Phase shift masks [PSM]; PSM blanks; Preparation thereof

- G03F1/32—Attenuating PSM [att-PSM], e.g. halftone PSM or PSM having semi-transparent phase shift portion; Preparation thereof

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/0045—Photosensitive materials with organic non-macromolecular light-sensitive compounds not otherwise provided for, e.g. dissolution inhibitors

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/0047—Photosensitive materials characterised by additives for obtaining a metallic or ceramic pattern, e.g. by firing

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Nonlinear Science (AREA)

- Ceramic Engineering (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mathematical Physics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Optics & Photonics (AREA)

- Liquid Crystal (AREA)

Abstract

Description

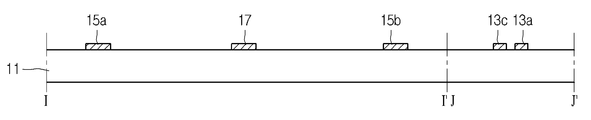

도 2는 실시예에 따른 박막 트랜지스터 어레이 기판을 도시한 평면도이다.

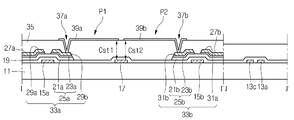

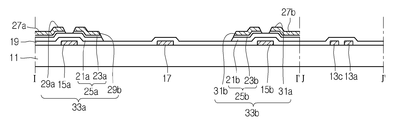

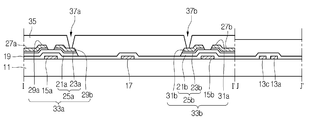

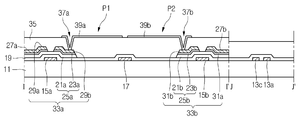

도 3은 도 1의 박막 트랜지스터 어레이 기판을 도시한 단면도이다.

도 4a 내지 도 4d는 도 1의 박막 트랜지스터 어레이 기판의 제조 공정을 도시한 도면이다.

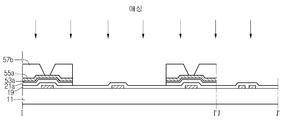

도 5a 내지 도 5d는 도 4a의 게이트 패턴 그룹의 제조 공정을 도시한 도면이다.

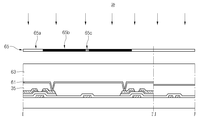

도 6a 내지 도 6e는 도 4b의 데이터 패턴 그룹의 제조 공정을 도시한 도면이다.

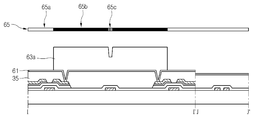

도 7a 내지 도 7d는 도 4d의 화소 전극의 제조 공정을 도시한 도면이다.

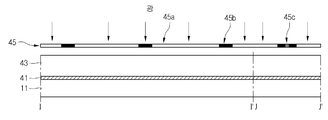

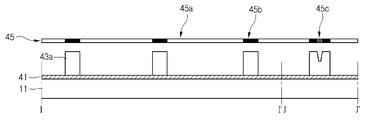

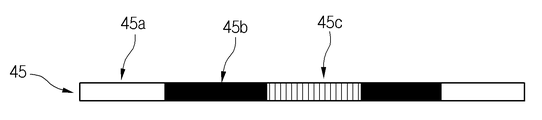

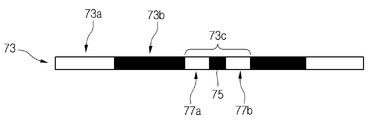

도 8a 내지 도 8c는 실시예에 적용되는 노광용 마스크를 도시한 도면이다.

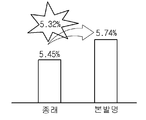

도 9는 도 1의 박막 트랜지스터 어레이 기판에 의한 개구율 향상을 보여주는 도면이다.

13a, 13b, 13c: 게이트 라인 15a, 15b: 게이트 전극

17: 공통 전극 17a: 연결 전극

19: 게이트 절연막 21a, 21b: 활성층

23a, 23b: 오믹 콘택층 25a, 25b: 반도체층

27a, 27b, 27c: 데이터 라인 29a, 31a: 소스 전극

29b, 31b: 드레인 전극 35: 보호막

37a, 37b: 콘택홀 39a, 39b; 화소 전극

Claims (11)

- 기판 상에 제1 및 제2 패턴을 형성하기 위한 박막을 형성하는 단계;

상기 박막 상에 감광막을 형성하는 단계;

상기 제1 및 제2 패턴 사이의 간격이 최소화되도록 상기 제1 및 제2 패턴 사이의 간격에 대응하는 반투과 영역을 포함하는 마스크를 정렬하는 단계;

상기 마스크에 광을 조사하여 상기 반투과 영역에 대응하는 상기 감광막의 상부 영역을 제거한 제1 감광 패턴을 형성하는 단계;

애싱 공정을 수행하여 상기 박막이 노출되도록 상기 반투과 영역에 대응하는 상기 제1 감광 패턴을 제거한 제2 감광 패턴을 형성하는 단계; 및

상기 제2 감광 패턴을 식각용 마스크로 하여 상기 박막을 패턴하여 상기 제1 및 제2 패턴을 형성하는 단계

를 포함하는 패턴 형성 방법. - 제1항에 있어서,

상기 마스크는 하프톤 마스크, 그레이 톤 마스크 및 비대칭 하프톤 마스크 중 하나인 패턴 형성 방법. - 기판 상에 게이트 라인 및 게이트 전극을 포함하는 게이트 패턴 그룹을 형성하는 단계;

상기 기판 상에 게이트 절연막을 형성하는 단계;

상기 게이트 절연막 상에 반도체층과 데이터 라인, 소스 전극 및 드레인 전극을 포함하는 데이터 패턴 그룹을 형성하는 단계;

상기 기판 상에 콘택홀을 포함하는 보호막을 형성하는 단계; 및

상기 보호막 상에 화소 전극을 형성하는 단계를 포함하고,

상기 게이트 라인 사이의 제1 간격, 상기 소스 전극과 드레인 전극 사이의 제2 간격 및 상기 화소 전극 사이의 제3 간격 중 적어도 하나 이상의 간격을 최소화하기 위해 상기 적어도 하나 이상의 간격에 대응하는 반투과 영역을 포함하는 마스크를 이용하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 마스크는 하프톤 마스크, 그레이 톤 마스크 및 비대칭 하프톤 마스크 중 하나인 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 반투과 영역은 다수의 슬릿을 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 반투과 영역은 슬릿과 상기 슬릿의 양측에 제1 및 제2 투과홀을 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 반투과 영역은 다수의 슬릿을 포함하는 제1 슬릿군, 다수의 슬릿을 포함하고 상기 제1 슬릿군과 상이한 폭을 갖는 제2 슬릿군 및 상기 제1 및 제2 슬릿군 사이의 투과홀을 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 반투과 영역은 다수의 슬릿을 포함하는 제1 슬릿군, 다수의 슬릿을 포함하고 상기 제1 슬릿군과 상이한 폭을 갖는 제2 슬릿군 및 상기 제1 및 제2 슬릿군에 포함된 슬릿보다 큰 폭을 갖고 상기 제1 및 제2 슬릿군 사이에 배치된 하나의 슬릿을 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 게이트 패턴 그룹을 형성하는 단계는,

상기 기판 상에 상기 게이트 라인 및 상기 게이트 전극을 형성하기 위한 제1 금속막과 제1 감광막을 형성하는 단계;

상기 제1 감광막 상에 상기 게이트 라인 사이의 간격에 대응하는 반투과 영역을 포함하는 제1 마스크를 정렬하는 단계;

상기 제1 마스크에 광을 조사하여 상기 반투과 영역에 대응하는 상기 제1 감광막의 상부 영역을 제거한 제1 감광 패턴을 형성하는 단계;

애싱 공정을 수행하여 상기 제1 금속막이 노출되도록 상기 반투과 영역에 대응하는 상기 제1 감광 패턴을 제거한 제2 감광 패턴을 형성하는 단계; 및

상기 제2 감광 패턴을 식각용 마스크로 하여 상기 제1 금속막을 패턴하여 상기 게이트 라인 및 상기 게이트 전극을 형성하는 단계

를 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 반도체층과 상기 데이터 패턴 그룹을 형성하는 단계는,

상기 게이트 절연막 상에 비정질막, 불순물을 포함하는 비정질막, 상기 데이터 라인, 상기 소스 전극 및 상기 드레인 전극을 형성하기 위한 제2 금속막 및 제2 감광막을 형성하는 단계;

상기 제2 감광막 상에 상기 소스 전극과 상기 드레인 전극 사이의 간격에 대응하는 반투과 영역을 포함하는 제2 마스크를 정렬하는 단계;

상기 제2 마스크에 광을 조사하여 상기 반투과 영역에 대응하는 상기 제2 감광막의 상부 영역을 제거한 제1 감광 패턴을 형성하는 단계;

상기 제1 감광 패턴을 제1 식각용 마스크로 하여 상기 제2 금속막, 상기 불순물을 포함하는 비정질막 및 상기 비정질막을 패턴하여 상기 데이터 라인과 상기 반도체층의 활성층을 형성하는 단계;

애싱 공정을 수행하여 상기 제1 금속막이 노출되도록 상기 반투과 영역에 대응하는 상기 제1 감광 패턴을 제거한 제2 감광 패턴을 형성하는 단계; 및

상기 제2 감광 패턴을 제2 식각용 마스크로 하여 상기 제1 금속막과 상기 불순물을 포함하는 비정질막을 패턴하여 상기 반도체층의 오믹 콘택층, 상기 소스 전극 및 상기 드레인 전극을 형성하는 단계

를 포함하는 박막 트랜지스터 어레이 기판의 제조 방법. - 제3항에 있어서,

상기 화소 전극을 형성하는 단계는,

상기 보호막 상에 상기 화소 전극을 형성하기 위한 도전막과 제3 감광막을 형성하는 단계;

상기 제3 감광막 상에 상기 화소 전극 사이의 간격에 대응하는 반투과 영역을 포함하는 제3 마스크를 정렬하는 단계;

상기 제3 마스크에 광을 조사하여 상기 반투과 영역에 대응하는 상기 제3 감광막의 상부 영역을 제거한 제1 감광 패턴을 형성하는 단계;

애싱 공정을 수행하여 상기 제3 금속막이 노출되도록 상기 반투과 영역에 대응하는 상기 제1 감광 패턴을 제거한 제2 감광 패턴을 형성하는 단계; 및

상기 제2 감광 패턴을 식각용 마스크로 하여 상기 도전막을 패턴하여 상기 화소 전극을 형성하는 단계

를 포함하는 박막 트랜지스터 어레이 기판의 제조 방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100137131A KR20120081663A (ko) | 2010-12-28 | 2010-12-28 | 패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100137131A KR20120081663A (ko) | 2010-12-28 | 2010-12-28 | 패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20120081663A true KR20120081663A (ko) | 2012-07-20 |

Family

ID=46713702

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100137131A Ceased KR20120081663A (ko) | 2010-12-28 | 2010-12-28 | 패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20120081663A (ko) |

-

2010

- 2010-12-28 KR KR1020100137131A patent/KR20120081663A/ko not_active Ceased

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4607418B2 (ja) | 液晶ディスプレイ装置用アレー基板及びその製造方法 | |

| JP4343510B2 (ja) | 液晶表示装置、液晶表示装置用薄膜トランジスタ基板及びその製造方法 | |

| KR100816333B1 (ko) | 액정 표시 장치용 색 필터 기판 및 박막 트랜지스터 기판및 이들의 제조 방법 | |

| KR101264722B1 (ko) | 액정표시장치의 제조방법 | |

| TWI494677B (zh) | 液晶顯示器的陣列基板及其製造方法 | |

| US20170092658A1 (en) | Array substrate, display device, and method for manufacturing the array substrate | |

| CN101369588B (zh) | Tft阵列电路板 | |

| EP3187929A1 (en) | Array substrate and manufacturing method therefor, and display apparatus | |

| WO2017133097A1 (zh) | 阵列基板及其制造方法以及显示面板 | |

| US8203674B2 (en) | Manufacturing thin film transistor array panels for flat panel displays | |

| KR101450803B1 (ko) | 어레이 기판 및 어레이 기판의 제조방법 | |

| KR100978260B1 (ko) | 액정표시장치 및 그 제조방법 | |

| US7855033B2 (en) | Photo mask and method of fabricating array substrate for liquid crystal display device using the same | |

| KR101682432B1 (ko) | 프린지 필드 스위칭 모드 액정표시장치용 어레이기판 및 이의 제조 방법 | |

| KR20060001165A (ko) | 수평 전계 인가형 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100679516B1 (ko) | 액정 표시 장치 및 그의 제조 방법 | |

| JP4567589B2 (ja) | 液晶表示装置用アレイ基板及びその製造方法 | |

| CN108363252B (zh) | 液晶显示装置及tft阵列基板的制造方法 | |

| KR20120081663A (ko) | 패턴 형성 방법 및 박막 트랜지스터 어레이 기판의 제조 방법 | |

| KR20070082090A (ko) | 표시 기판 및 이의 제조 방법 | |

| US8435722B2 (en) | Method for fabricating liquid crystal display device | |

| KR20080059801A (ko) | 액정표시장치 및 그 제조 방법 | |

| KR101856209B1 (ko) | 액정표시장치의 박막트랜지스터 및 그 제조방법 | |

| KR101141535B1 (ko) | 전극패턴의 형성방법 및 이를 이용한 액정표시장치의제조방법 | |

| JP2007213075A (ja) | 薄膜トランジスタ基板の製造方法、薄膜トランジスタ基板、及びそれを有する表示パネル |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20101228 |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20151210 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20101228 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20170704 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20171219 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20170704 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |