KR20080098609A - 데이터 처리 시스템을 테스트하기 위한 방법 및 장치 - Google Patents

데이터 처리 시스템을 테스트하기 위한 방법 및 장치 Download PDFInfo

- Publication number

- KR20080098609A KR20080098609A KR1020087020067A KR20087020067A KR20080098609A KR 20080098609 A KR20080098609 A KR 20080098609A KR 1020087020067 A KR1020087020067 A KR 1020087020067A KR 20087020067 A KR20087020067 A KR 20087020067A KR 20080098609 A KR20080098609 A KR 20080098609A

- Authority

- KR

- South Korea

- Prior art keywords

- test

- processor

- signature

- stop

- scan

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318533—Reconfiguring for testing, e.g. LSSD, partitioning using scanning techniques, e.g. LSSD, Boundary Scan, JTAG

- G01R31/318544—Scanning methods, algorithms and patterns

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318533—Reconfiguring for testing, e.g. LSSD, partitioning using scanning techniques, e.g. LSSD, Boundary Scan, JTAG

- G01R31/318536—Scan chain arrangements, e.g. connections, test bus, analog signals

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318533—Reconfiguring for testing, e.g. LSSD, partitioning using scanning techniques, e.g. LSSD, Boundary Scan, JTAG

- G01R31/318552—Clock circuits details

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/22—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing

- G06F11/2205—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested

- G06F11/2236—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested to test CPU or processors

Landscapes

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Quality & Reliability (AREA)

- Tests Of Electronic Circuits (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

Abstract

Description

Claims (25)

- 처리기의 적어도 하나의 로직 블록(logic block)을 테스트하는 방법에 있어서:상기 처리기에 의한 사용자 애플리케이션의 실행 동안, 상기 처리기는 상기 정지 및 테스트 표시자를 발생시키고, 상기 정지 및 테스트 표시자의 발생에 응답하여 상기 사용자 애플리케이션의 실행을 정지시키고, 필요한 경우, 상기 처리기의 상기 적어도 하나의 로직 블록의 상태를 저장하는 단계; 및상기 처리기의 상기 적어도 하나의 로직 블록을 테스트하는 테스트 스티뮬러스(test stimulus)를 적용하는 단계를 포함하는, 로직 블록 테스트 방법.

- 제 1 항에 있어서,상기 정지 및 테스트 표시자를 발생시키기 위해 상기 처리기에 의해 정지 및 테스트 명령을 디코딩하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 2 항에 있어서,상기 테스트 스티뮬러스를 적용하기 전에 스캔 체인 구성을 결정하기 위해 상기 정지 및 테스트 명령을 디코딩하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 1 항에 있어서,상기 테스트 스티뮬러스를 적용하는 단계는 복수의 클록 사이클들에 대한 적어도 하나의 스캔 체인으로 상기 테스트 스티뮬러스를 시프트 인하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 4 항에 있어서,상기 적어도 하나의 스캔 체인은 상기 처리기의 상기 적어도 하나의 로직 블록에 대응하는, 로직 블록 테스트 방법.

- 제 4 항에 있어서,상기 테스트 스티뮬러스를 시프트 인(shift in)하기 전에 상기 처리기의 상기 적어도 하나의 로직 블록을 리셋하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 4 항에 있어서,테스트 결과들의 제 1 세트에 대응하는 제 1 시그니처를 생성하기 위해, 상기 적어도 하나의 스캔 체인 밖으로 제 1 검사 지점에 대응하는 상기 테스트 결과들의 제 1 세트를 시프트 아웃(shift out)하고, 시그니처 분석기(signature analyzer)로 상기 테스트 결과들의 제 1 세트를 수신하는 단계로서, 상기 제 1 검사 지점은 제 1 복수의 클록 사이클들에 대응하는, 상기 시프트 아웃 및 수신 단 계, 및 상기 제 1 시그니처를 제 1 예상된 시그니처와 비교하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 7 항에 있어서,테스트 결과들의 제 2 세트에 대응하는 제 2 시그니처를 생성하기 위해, 상기 적어도 하나의 스캔 체인 밖으로 제 2 검사 지점에 대응하는 상기 테스트 결과들의 제 2 세트를 시프트 아웃하고 상기 시그니처 분석기로 상기 테스트 결과들의 제 2 세트를 수신하는 단계로서, 상기 제 2 검사 지점은 제 2 복수의 클록 사이클들에 대응하는, 상기 시프트 아웃 및 수신 단계, 및 상기 제 2 시그니처를 제 2 예상 시그니처와 비교하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 4 항에 있어서,상기 적어도 하나의 스캔 체인은 적어도 제 1 메모리 소자, 메모리 소자들의 체인, 및 제 2 메모리 소자를 포함하고, 상기 제 1 메모리 소자의 출력은 상기 메모리 소자들의 체인의 입력 및 적어도 하나의 로직 게이트의 입력에 접속되고, 상기 적어도 하나의 로직 게이트의 출력은 상기 제 2 메모리 소자의 입력에 접속되는, 로직 블록 테스트 방법.

- 제 9 항에 있어서,상기 적어도 하나의 로직 게이트는 배타적-OR 게이트 또는 배타적-NOR 게이 트 중 적어도 하나인, 로직 블록 테스트 방법.

- 제 1 항에 있어서,상기 테스트 스티뮬러스를 이용하여 상기 처리기의 상기 적어도 하나의 로직 블록을 작동하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 1 항에 있어서,인터럽트의 수신에 응답하여, 상기 처리기에서 상기 사용자 애플리케이션을 실행하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 12 항에 있어서,상기 사용자 애플리케이션을 실행하는 단계는 복원 벡터(restore vector)에서 시작하는 상기 사용자 애플리케이션을 실행하는 단계를 포함하는, 로직 블록 테스트 방법.

- 제 13 항에 있어서,상기 사용자 애플리케이션 실행 단계는, 상기 처리기의 상기 적어도 하나의 로직 블록의 상태가 저장된 경우 상기 처리기의 상기 적어도 하나의 로직 블록의 상태를 복원하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 1 항에 있어서,상기 복수의 클록 사이클들은 미리 결정된 최대값 및 미리 결정된 최소값 중 적어도 하나를 갖는, 로직 블록 테스트 방법.

- 제 1 항에 있어서,테스트 결과들에 대응하는 적어도 하나의 시그니처를 생성하기 위해 상기 적어도 하나의 스캔 체인 밖으로 테스트 결과들을 시프트 아웃하고 시그니처 분석기로 상기 테스트 결과들을 수신하는 단계를 더 포함하는, 로직 블록 테스트 방법.

- 제 16 항에 있어서,상기 적어도 하나의 시그니처를 대응하는 예상된 시그니처와 비교하는 단계를 더 포함하는, 로직 블록 테스트 방법.

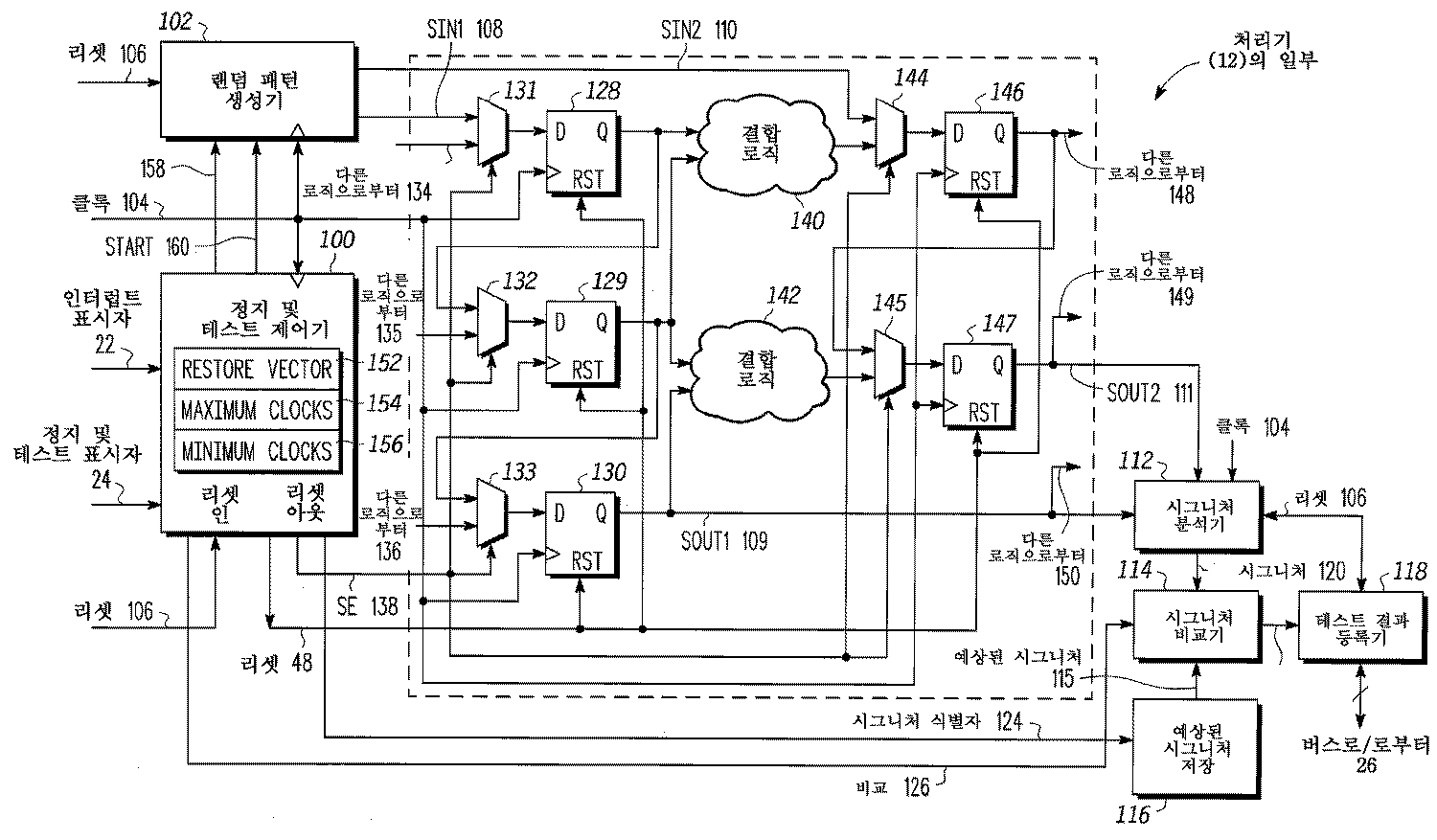

- 처리기의 적어도 하나의 로직 블록을 테스트하는 장치에 있어서:상기 처리기에 의한 사용자 애플리케이션의 실행 동안, 정지 및 테스트 표시자를 발생시키고, 상기 정지 및 테스트 표시기의 발생에 응답하여, 상기 사용자 애플리케이션의 실행을 정지하고, 필요한 경우 상기 처리기의 상기 적어도 하나의 로직 블록의 상태를 저장하도록 구성된 테스트 제어기;적어도 하나의 스캔 체인으로서, 상기 테스트 제어기는 또한 상기 처리기의 상기 적어도 하나의 로직 블록을 테스트하기 위해 복수의 클록 사이클들에 대한 상 기 적어도 하나의 스캔 체인으로 테스트 스티뮬러스를 입력하고 상기 적어도 하나의 스캔 체인 밖으로 테스트 결과들을 출력하도록 구성되는, 상기 적어도 하나의 스캔 체인;상기 테스트 스티뮬러스를 발생시키도록 구성되는 패턴 생성기; 및상기 출력 결과들에 대응하는 적어도 하나의 시그니처를 발생시키도록 구성되고 상기 적어도 하나의 시그니처를 대응하는 예상된 시그니처와 비교하는 시그니처 분석기를 포함하는, 로직 블록 테스트 장치.

- 제 18 항에 있어서,테스트의 성공 및 실패를 표시하는 적어도 하나의 값을 저장하도록 구성된 테스트 결과 레지스터를 더 포함하는, 로직 블록 테스트 장치.

- 제 19 항에 있어서,상기 테스트 결과 레지스터는 또한 상기 복수의 클록 사이클들을 정량하는 값을 저장하도록 구성되는, 로직 블록 테스트 장치.

- 제 19 항에 있어서,상기 테스트 결과 레지스터는 또한 마지막 완료된 검사 지점에 대한 다수의 클록 사이클들에 대응하는 값을 저장하도록 구성된, 로직 블록 테스트 장치.

- 제 18 항에 있어서,테스트 성공 또는 실패 표시하는 복수의 값들을 저장하도록 구성되는 테스트 결과 레지스터를 더 포함하고, 상기 복수의 값들의 각각의 값은 검사 지점에 대응하는, 상기 로직 블록 테스트 장치.

- 제 18 항에 있어서,상기 테스트 제어기는 또한 상기 적어도 하나의 시그니처가 상기 대응하는 예상된 시그니처에 매칭하지 않게 하는 강제된 에러 신호(forced error signal)를 발생시키도록 구성되는, 로직 블록 테스트 장치.

- 제 23 항에 있어서,상기 강제된 에러 신호는 상기 패턴 생성기의 출력에 변동을 일으키는, 로직 블록 테스트 장치.

- 제 18 항에 있어서,상기 정지 및 테스트 표시자의 발생 전에 상기 처리기의 상기 적어도 하나의 로직 블록의 레지스터들을 미리 결정된 값으로 설정하는 단계를 더 포함하는, 로직 블록 테스트 장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/355,681 | 2006-02-16 | ||

| US11/355,681 US7444568B2 (en) | 2006-02-16 | 2006-02-16 | Method and apparatus for testing a data processing system |

| PCT/US2007/060660 WO2007103591A2 (en) | 2006-02-16 | 2007-01-18 | Method and apparatus for testing a data processing system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080098609A true KR20080098609A (ko) | 2008-11-11 |

| KR101318697B1 KR101318697B1 (ko) | 2013-10-16 |

Family

ID=38475623

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087020067A Expired - Fee Related KR101318697B1 (ko) | 2006-02-16 | 2007-01-18 | 데이터 처리 시스템을 테스트하기 위한 방법 및 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7444568B2 (ko) |

| JP (1) | JP5373403B2 (ko) |

| KR (1) | KR101318697B1 (ko) |

| TW (1) | TWI403744B (ko) |

| WO (1) | WO2007103591A2 (ko) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7797599B2 (en) * | 2006-09-27 | 2010-09-14 | Verigy (Singapore) Pte. Ltd. | Diagnostic information capture from logic devices with built-in self test |

| US20080098269A1 (en) * | 2006-09-29 | 2008-04-24 | Bhavsar Dilip K | Mechanism for concurrent testing of multiple embedded arrays |

| US20090228751A1 (en) * | 2007-05-22 | 2009-09-10 | Tilman Gloekler | method for performing logic built-in-self-test cycles on a semiconductor chip and a corresponding semiconductor chip with a test engine |

| US7721176B2 (en) * | 2007-12-06 | 2010-05-18 | International Business Machines Corporation | Method, system, and computer program product for integrated circuit recovery testing using simulation checkpoints |

| US8086925B2 (en) * | 2008-05-20 | 2011-12-27 | International Business Machines Corporation | Method and system for LBIST testing of an electronic circuit |

| WO2010038096A1 (en) * | 2008-09-30 | 2010-04-08 | Freescale Semiconductor, Inc. | Method and apparatus for handling an output mismatch |

| US8522085B2 (en) * | 2010-01-27 | 2013-08-27 | Tt Government Solutions, Inc. | Learning program behavior for anomaly detection |

| WO2010120737A1 (en) * | 2009-04-13 | 2010-10-21 | Telcordia Technologies, Inc. | Learning program behavior for anomaly detection |

| US8312331B2 (en) * | 2009-04-16 | 2012-11-13 | Freescale Semiconductor, Inc. | Memory testing with snoop capabilities in a data processing system |

| US8136001B2 (en) * | 2009-06-05 | 2012-03-13 | Freescale Semiconductor, Inc. | Technique for initializing data and instructions for core functional pattern generation in multi-core processor |

| US9874870B2 (en) * | 2009-08-26 | 2018-01-23 | Fisher-Rosemount Systems, Inc. | Methods and apparatus to manage testing of a process control system |

| US20110087861A1 (en) * | 2009-10-12 | 2011-04-14 | The Regents Of The University Of Michigan | System for High-Efficiency Post-Silicon Verification of a Processor |

| US8458543B2 (en) * | 2010-01-07 | 2013-06-04 | Freescale Semiconductor, Inc. | Scan based test architecture and method |

| US8438442B2 (en) * | 2010-03-26 | 2013-05-07 | Freescale Semiconductor, Inc. | Method and apparatus for testing a data processing system |

| US8335881B2 (en) * | 2010-03-26 | 2012-12-18 | Freescale Semiconductor, Inc. | Method and apparatus for handling an interrupt during testing of a data processing system |

| US8527826B2 (en) * | 2011-11-07 | 2013-09-03 | International Business Machines Corporation | Logic corruption verification |

| US9281079B2 (en) * | 2013-02-12 | 2016-03-08 | International Business Machines Corporation | Dynamic hard error detection |

| US9404969B1 (en) * | 2013-11-01 | 2016-08-02 | Cadence Design Systems, Inc. | Method and apparatus for efficient hierarchical chip testing and diagnostics with support for partially bad dies |

| US9285424B2 (en) | 2014-07-25 | 2016-03-15 | Freescale Semiconductor,Inc. | Method and system for logic built-in self-test |

| US10031181B1 (en) * | 2015-06-18 | 2018-07-24 | Marvell Israel (M.I.S.L.) Ltd. | Integrated circuit package receiving test pattern and corresponding signature pattern |

| US9891282B2 (en) | 2015-12-24 | 2018-02-13 | Intel Corporation | Chip fabric interconnect quality on silicon |

| US10578672B2 (en) * | 2015-12-31 | 2020-03-03 | Stmicroelectronics (Grenoble 2) Sas | Method, device and article to test digital circuits |

| US10452493B2 (en) * | 2016-05-24 | 2019-10-22 | Virginia Tech Intellectual Properties, Inc. | Microprocessor fault detection and response system |

| US10249380B2 (en) | 2017-01-27 | 2019-04-02 | Qualcomm Incorporated | Embedded memory testing with storage borrowing |

| JP2019158749A (ja) * | 2018-03-15 | 2019-09-19 | 株式会社東芝 | 画像処理装置及び画像処理方法 |

| US11204849B2 (en) * | 2020-03-13 | 2021-12-21 | Nvidia Corporation | Leveraging low power states for fault testing of processing cores at runtime |

| CN115356620B (zh) * | 2022-08-17 | 2025-07-25 | 地平线(上海)人工智能技术有限公司 | 片上系统的数字逻辑自测试方法、装置、电子设备和介质 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3671940A (en) * | 1970-03-19 | 1972-06-20 | Burroughs Corp | Test apparatus for digital computer |

| US3839705A (en) * | 1972-12-14 | 1974-10-01 | Gen Electric | Data processor including microprogram control means |

| US4042914A (en) * | 1976-05-17 | 1977-08-16 | Honeywell Information Systems Inc. | Microprogrammed control of foreign processor control functions |

| US4679194A (en) * | 1984-10-01 | 1987-07-07 | Motorola, Inc. | Load double test instruction |

| JP2644798B2 (ja) * | 1988-01-29 | 1997-08-25 | 株式会社日立製作所 | 信号処理回路の自己診断方式 |

| JPH0455778A (ja) * | 1990-06-26 | 1992-02-24 | Toshiba Corp | 半導体装置のテスト方法 |

| US5672966A (en) * | 1992-07-23 | 1997-09-30 | Xilinx, Inc. | High speed post-programming net packing method |

| US5617021A (en) * | 1992-07-23 | 1997-04-01 | Xilinx, Inc. | High speed post-programming net verification method |

| KR960000616B1 (ko) * | 1993-01-13 | 1996-01-10 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치 |

| JPH0764817A (ja) * | 1993-08-30 | 1995-03-10 | Mitsubishi Electric Corp | 故障検出システム |

| US5485467A (en) * | 1993-09-24 | 1996-01-16 | Vlsi Technology, Inc. | Versatile reconfigurable matrix based built-in self-test processor for minimizing fault grading |

| US5900757A (en) * | 1996-05-01 | 1999-05-04 | Sun Microsystems, Inc. | Clock stopping schemes for data buffer |

| US5841867A (en) * | 1996-11-01 | 1998-11-24 | Xilinx, Inc. | On-chip programming verification system for PLDs |

| US6442723B1 (en) * | 1999-05-12 | 2002-08-27 | International Business Machines Corporation | Logic built-in self test selective signature generation |

| US20070168736A1 (en) * | 2005-12-19 | 2007-07-19 | Ottavi Robert P | Breakpoint groups |

-

2006

- 2006-02-16 US US11/355,681 patent/US7444568B2/en not_active Expired - Fee Related

-

2007

- 2007-01-18 KR KR1020087020067A patent/KR101318697B1/ko not_active Expired - Fee Related

- 2007-01-18 JP JP2008555430A patent/JP5373403B2/ja not_active Expired - Fee Related

- 2007-01-18 WO PCT/US2007/060660 patent/WO2007103591A2/en not_active Ceased

- 2007-01-25 TW TW096102861A patent/TWI403744B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US7444568B2 (en) | 2008-10-28 |

| WO2007103591A3 (en) | 2008-12-04 |

| TW200817704A (en) | 2008-04-16 |

| US20070260950A1 (en) | 2007-11-08 |

| TWI403744B (zh) | 2013-08-01 |

| KR101318697B1 (ko) | 2013-10-16 |

| JP2009527821A (ja) | 2009-07-30 |

| JP5373403B2 (ja) | 2013-12-18 |

| WO2007103591A2 (en) | 2007-09-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101318697B1 (ko) | 데이터 처리 시스템을 테스트하기 위한 방법 및 장치 | |

| EP1872146B1 (en) | Simultaneous core testing in multi-core integrated circuits | |

| US7644333B2 (en) | Restartable logic BIST controller | |

| US6665817B1 (en) | Apparatus and method for implementing a wireless system-on-a-chip with a reprogrammable tester, debugger, and bus monitor | |

| Vermeulen | Functional debug techniques for embedded systems | |

| RU2579814C2 (ru) | Интегральная схема с программируемым логическим анализатором с расширенными возможностями анализа и отладки и способ | |

| KR100217535B1 (ko) | 이벤트 한정 검사 아키텍춰 | |

| US8438442B2 (en) | Method and apparatus for testing a data processing system | |

| US9097762B2 (en) | Method and apparatus for diagnosing an integrated circuit | |

| US20040216061A1 (en) | Embeddable method and apparatus for functional pattern testing of repeatable program instruction-driven logic circuits via signal signature generation | |

| US8677196B1 (en) | Low cost production testing for memory | |

| JPH09508992A (ja) | 集積回路試験装置及び試験法 | |

| CN112154336B (zh) | 确定性星体内建自测 | |

| US20170205462A1 (en) | Power-on self-test and in-system test | |

| US8335881B2 (en) | Method and apparatus for handling an interrupt during testing of a data processing system | |

| KR100727975B1 (ko) | 시스템 온 칩의 고장 진단 장치 및 방법과 고장 진단이가능한 시스템 온 칩 | |

| US7577876B2 (en) | Debug system for data tracking | |

| US7089473B2 (en) | Method and apparatus for testing a circuit using a die frame logic analyzer | |

| Floridia et al. | Hybrid on-line self-test architecture for computational units on embedded processor cores | |

| JP2013242746A (ja) | 故障検出システムと方法並びに半導体装置 | |

| US8429615B2 (en) | Semiconductor integrated circuit | |

| De Carvalho et al. | Increasing fault coverage during functional test in the operational phase | |

| CN112585486A (zh) | 扩展jtag控制器和使用扩展jtag控制器进行功能复位的方法 | |

| Dutta et al. | Design techniques and tradeoffs in implementing non-destructive field test using logic BIST self-test | |

| EP4042173B1 (en) | System and method for access control of a plurality of instruments embedded in a semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| A201 | Request for examination | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20161011 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20161011 |